- アプリケーション

- テスト装置と計測機器 (T&M) ソリューション

- 半導体自動テスト装置 (ATE)

次世代の SoC テスト装置は、今後さらに複雑化、高速化するさまざまな I/O プロトコルをテストする必要があります。業界最高クラスの SerDes および HSSIO 技術は、ハイボリューム SoC、ミックスド シグナル、レーダー/カメラ センサーやメモリ テスト装置の実現にあたり、最適なコストで最高の柔軟性を提供します。メモリ コントローラーやチップ間インターコネクト用の統合されたハード IP を利用することで、リソースとコストを抑えた効率的な実装が可能になります。

| デザイン サンプル | 説明 | デバイス サポート |

|---|---|---|

クリックして拡大表示 |

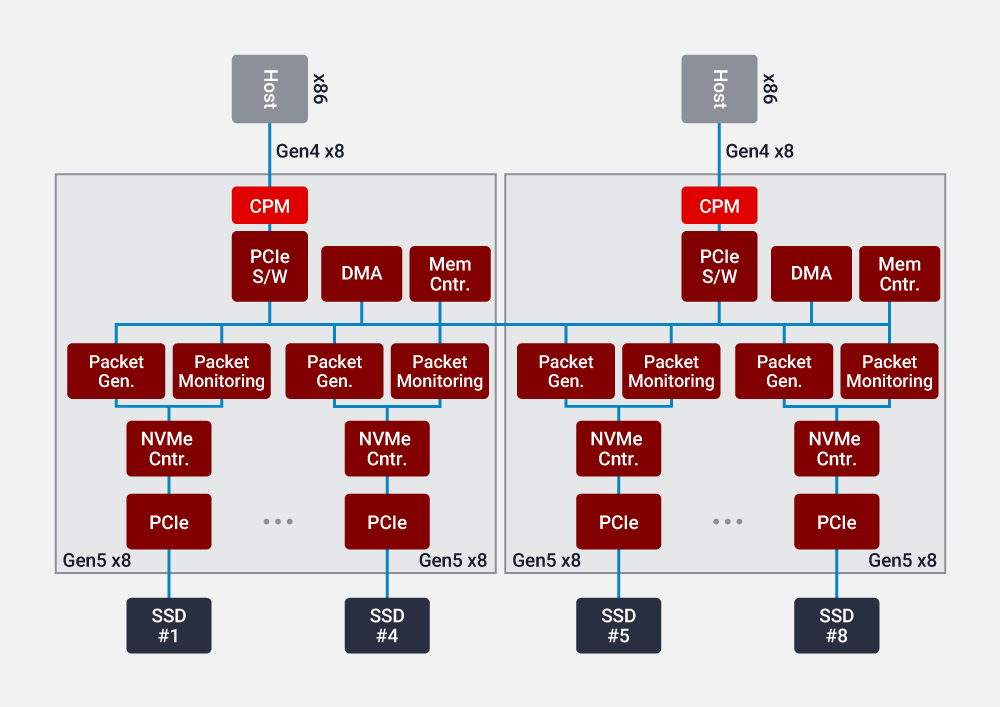

SoC およびストレージ テスター 革新的な Versal™ アーキテクチャは、ほかのデバイス ソリューションでは得られない性能、柔軟性、電力効率に最適化されたハード IP を提供します。Versal プレミアム ACAP に搭載された AI エンジンと DSP エンジンは、広帯域のオン/オフチップ メモリを使用することでこれまでにない信号処理能力を発揮します。適応型エンジンを構成する 750 万個のシステム ロジック セルは、カスタム IP、トラフィック生成、モニタリング機能に柔軟に対応できるため、ATE 開発に最適です。スケーラブルな 112G PAM4 トランシーバーと、600G Ethernet MAC、400G 高速暗号化エンジン、DDR メモリ コントローラー、PCIe® Gen5 統合ブロックなどの電力効率に最適化されたハード IP は、一般的なインターフェイス規格に対応できるように設計されており、幅広い機能と性能オプションを提供します。 |

Versal プレミアム アダプティブ SoC |

クリックして拡大表示 |

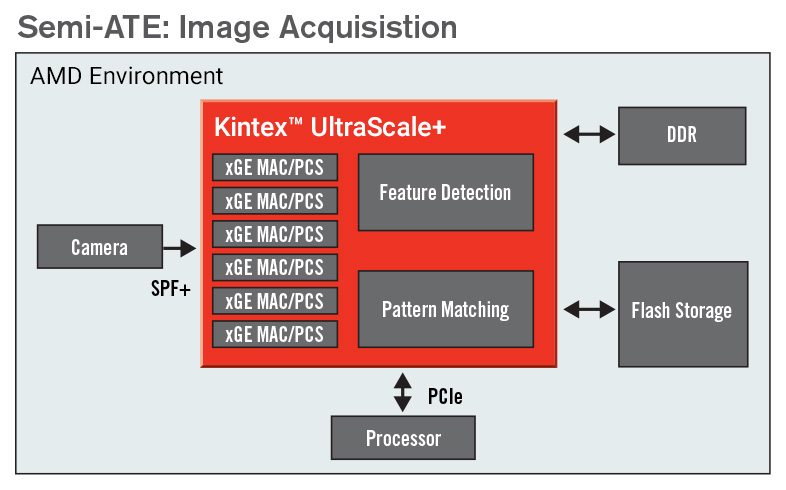

半導体 ATE: 画像の取り込み 画像取り込み機能には、高性能なトランシーバーと DSP 機能が必要で、さらにコスト重視アプリケーションでは消費電力を抑えてデバイス コストを削減する必要があります。Kintex™ UltraScale+™ は、32Gbps トランシーバー、6.3 TeraMAC の DSP 演算性能、2.6Gbs DDR4、および PCIe Gen4x8 サポートなど、ハイエンド性能の実現に最も費用対効果の高いソリューションを提供します。 |

|

クリックして拡大表示 |

半導体 ATE: ピン エレクトロニクス ピン エレクトロニクスの実現には、ベクトル信号の生成および解析用にコスト効果の高い FPGA が求められており、またパラレル インターフェイスを使用して多数の ASSP と接続するための多数の高性能 I/O が必要です。リンク速度が 1Gbps+ で、好ましくないチャネルと少ない基準クロックを使用した場合、I/O バッファーおよびクロック生成/分配機能は、PVT の影響を受ける複数レーン間のスキューに十分対応できる能力が必要になります。Kintex UltraScale+ FPGA には、信号調整機能、PLL/DLL ベースのクロック生成および分配リソース、さらにはスキュー調整機能が付いた高性能で高機能な SelectIO™ トランシーバーが搭載されています。つまり、Kintex UltraScale+ FPGA は、ピン エレクトロニクス アプリケーションに最適なソリューションと言えます。 |