検証とデバッグ

概要

検証とハードウェア デバッグは、最終的な FPGA 実装デザインの機能性、性能、信頼性を確保するために重要です。Vivado の検証機能ではデザインの効率的な検証をサポートし、包括的なデバッグ機能では複雑な FPGA デザインの問題をエンジニアがすばやく特定して解決できるようサポートします。

機能

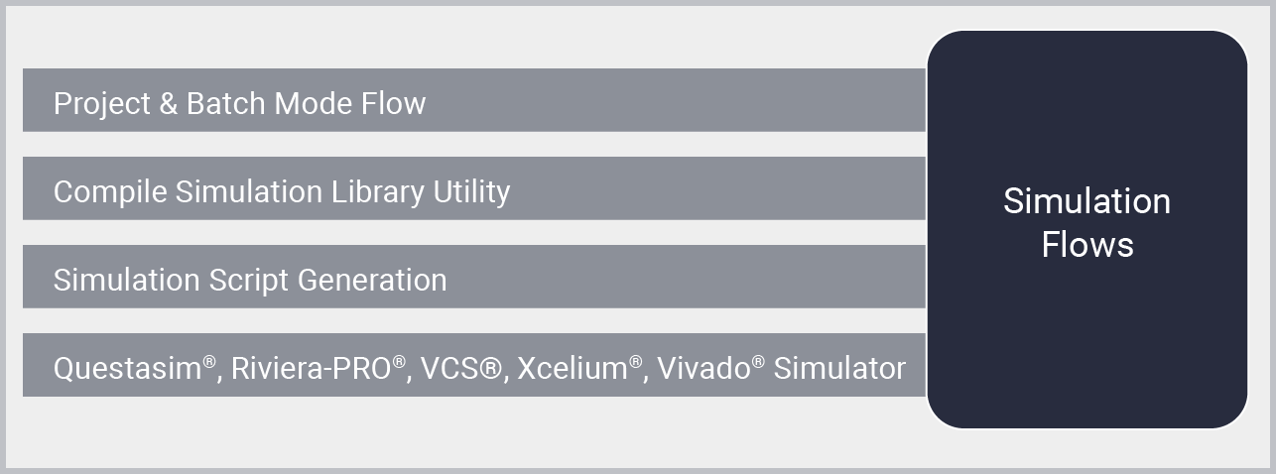

シミュレーション フロー

Vivado™ Design Suite は、デザイン入力、タイミング解析、ハードウェア デバッグ、シミュレーションなどの機能を提供する最先端の統合設計環境 (IDE) です。このフローは、Vivado 統合環境に統合されている検証機能とサードパーティの検証機能の両方に対応します。

Vivado 環境では、 統合されたシミュレータおよびサードパーティ HDL シミュレータによるシミュレーション (合成後またはインプリメンテーション後の論理シミュレーションおよびタイミング シミュレーション) をサポートしています。設計の早い段階でシミュレーションを行うことにより、早期に問題を解決でき、フローの最終段階で行う場合よりも開発時間を大幅に削減できます。

ユーザー検証環境に柔軟に対応できるように、Vivado では統合環境のサポートはもちろんのこと、外部の検証環境でも使用できるスクリプトを生成できます。

Vivado IDE は、インタラクティブ シミュレーション ユーザー向けの統合モードとアドバンス検証エンジニア向けのスクリプト モードのすべての主要シミュレータをサポートしています。

Aldec - Active-HDL® & Riviera-PRO®、Cadence Xcelium® Simulator、Siemens EDA – ModelSim® & Questasim®、Synopsys VCS®、AMD Vivado Simulator

主な特長

- シミュレーション フローは、ユーザーの環境でサポートされているシミュレータ用にシミュレーション ライブラリをコンパイルし、コンパイル済みライブラリの再利用を可能にします。

- ビヘイビアー シミュレーションや合成後の論理/タイミング シミュレーション、インプリメンテーション後の論理/タイミング シミュレーションなど、さまざまな設計段階でデザイン インテグリティをシミュレーションし、検証できます。

- すべてのシミュレータで一貫した 3 つのプロセス (コンパイル、エラボレート、シミュレーション) を使用する統合シミュレーション環境

- サードパーティ シミュレータ用のシミュレーション スクリプトを生成して、ユーザー独自の環境で検証できます。

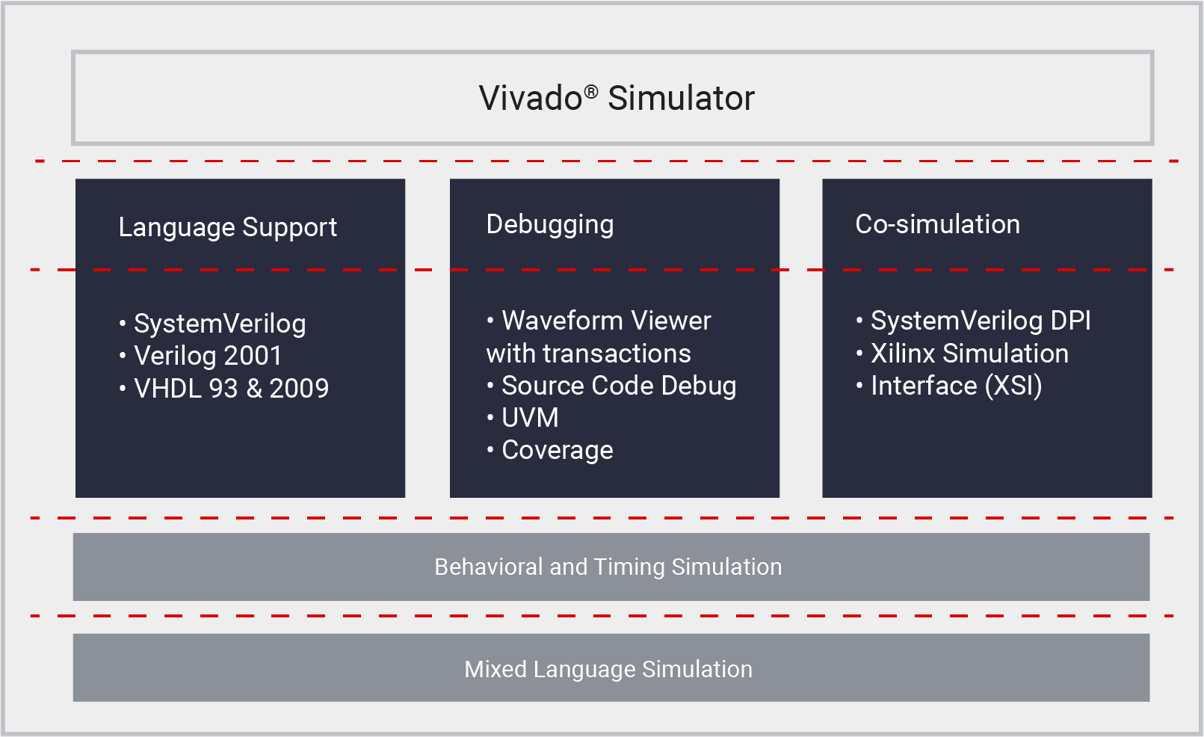

Vivado シミュレータ

Vivado™ シミュレータは、豊富な機能を備えた Verilog、SystemVerilog および VHDL 言語に対応する混合言語シミュレータです。Vivado の一部として含まれており、追加料金は不要です。デザイン サイズ、インスタンス、または行数の制限がないため、1 つの Vivado ライセンスで無制限のインスタンスの混合言語シミュレーションを実行できます。

Vivado Simulator は、Windows® および Linux の両方のオペレーティング システムをサポートし、AMD のお客様の検証ニーズに対応するための強力なデバッグ機能を備えています。

Vivado シミュレータは、ハードウェア記述言語 (HDL) のイベントドリブン シミュレータで、単一言語および混合言語デザインのビヘイビアーおよびタイミング シミュレーションをサポートします。

主な特長

- SystemVerilog (制約のランダムと機能範囲を含む)

- Verilog 2001

- VHDL 93 および VHDL 2008

- デジタル/アナログ波形とトランザクション ビューをサポートする高度な波形ビューアー

- ブレークポイント、サブプログラムのデバッグ、クロスプローブなどに対応できる包括的なデバッグツール

- UVM 1.2 ライブラリをサポート

- 機能カバレッジ

- GUI および script モードの両方をサポート

- ダイレクト プログラミング インターフェイス (DPI)

- ザイリンクス シミュレーション インターフェイス (XSI)

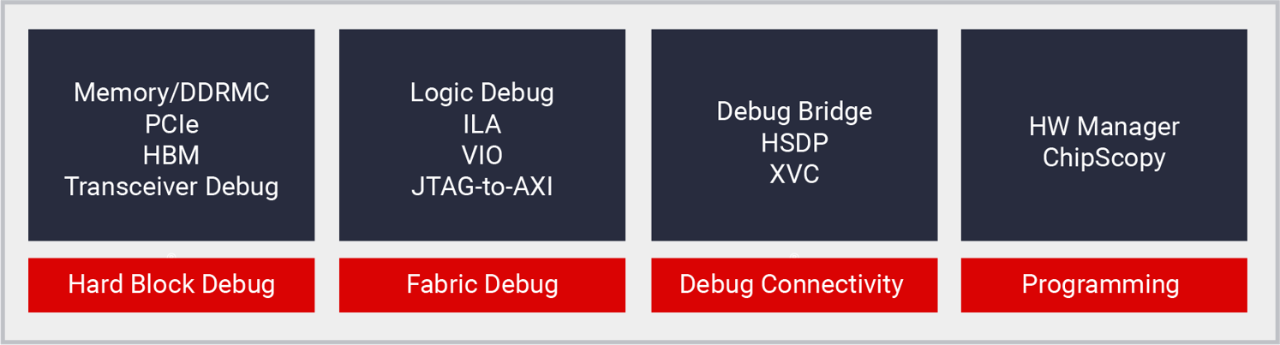

プログラミングおよびデバッグ

Vivado™ デバッグは、すばやく簡単かつ効率的にデバッグするためのさまざまなソリューションを提供します。これらのソリューションには、ハードウェア上ではユーザー デザインの動作を続けた状態で、ロジックからシステム レベルのデバッグまでのさまざまな機能を実行するツール、IP、およびフローが含まれます。

さらに Vivado は統合設計環境を提供するため、インターフェイスに統一性があり、互いに情報交換ができる 1 つの IDE 内で、異なるデバッグ タスクを実行できます。

利点

Vivado IDE のハードウェア マネージャーを使用することで、デバイスをプログラムし、ビットストリーム生成後にデザインをデバッグすることが可能になります。ハードウェア マネージャーを使用すると、ユーザーは 1 つまたは複数の FPGA デバイスを含むハードウェア ターゲットを接続してプログラミングし、Tcl または GUI インターフェイスを介してロジック アナライザー、シリアル I/O アナライザー、メモリ キャリブレーション デバッグなどのデザイン内のデバッグ IP と相互作用できます。

- FPGA 用デバイス プログラマ、コンフィギュレーション メモリ デバイス、eFUSE AES キー/レジスタ

- Tcl スクリプトのサポートによりデバッグが自動化

- hw_server とザイリンクス仮想ケーブル (XVC) を使用するネットワーク経由のリモート デバッグ (XVC)

Vivado は、実装済みデザインのインシステム ロジック デバッグを簡単に実行できるさまざまなデバッグ IP およびツールを提供します。

- ILA –イベントでトリガーを生成し、内部信号からのデータをキャプチャするために使用

- System ILA - AXI インターフェイスのトランザクションレベル デバッグに使用

- VIO – 内部信号の監視および駆動に使用

- JTAG-to-AXI – Tcl による AXI インターフェイスとの直接相互作用に使用

Vivado は、FPGA トランシーバーをすばやくかつ簡単にデバッグおよび最適化する方法を提供します。カスタマイズ可能なデバッグ IP (IBERT) や Vivado シリアル I/O 解析ツールがあり、これらを併用することで、複数チャネル上のビット誤り率 (BER) 測定や 1D/2D アイ スキャンを実行でき、またシリアル I/O チャネルがシステム内のその他の機能と相互作用中にリアルタイムにトランシーバー パラメーターを調整できます。

トランシーバーの PMA 評価機能とデモンストレーション用に設計された IBERT コアには、データ パターン ジェネレーターおよびチェッカー機能も含まれており、トランシーバー DRP ポートへのアクセスもサポートされています。FPGA 内に IBERT コアが実装されると、Vivado シリアル I/O 解析が IP と相互に作用するため、ユーザーはリンク (ボード上のチャネルに類似) を確立し、スキャンを実行して結果をグラフィカルに表示することによって、リンクのマージンを解析できます。

メモリ キャリブレーション デバッグ ツールを使用すると、メモリ インターフェイス (DDR4/3、RLDRAM3、QDRII+、および LPDDR3) のキャリブレーションまたはデータ エラーをすばやくデバッグできます。ユーザーは、ハードウェア上で動作中のデザインのコア コンフィギュレーション、キャリブレーション ステータス、メモリ インターフェイスのデータ マージンをいつでも表示して解析できます。

ザイリンクス仮想ケーブル (XVC) ソリューションは、JTAG ケーブルのように機能し、物理ケーブルを使用せずに FPGA または SoC デザインにアクセスしてデバッグを可能にする TCP/IP ベースのプロトコルです。XVC ソリューションは、ハードウェア コンポーネントとソフトウェア コンポーネントで構成されています。

ChipScopy は、デバイスのプログラミング、通信、およびデバッグを可能にする Versal 専用の Python API です。高水準の Python 関数を使用して、TCF サーバーの接続、デバイスのプログラミング、メモリの読み出し/書き込み、ILA データのトリガー/キャプチャ、VIO レジスタの読み出し/書き込みが可能です。また、IBERT スキャンおよびスイープの実行、システムモニター データの読み取り、NOC の性能監視、DDR の性能メトリクス レポートも可能です。

Verification IP

Verification IP (VIP) ポートフォリオにより、シミュレーション環境でのデザインの検証とデバッグを容易に、迅速に、より効果的に実行できます。Verification IP コアは、適切な相互運用性とシステム動作を確保することを目的とした検証モデルです。DA 業界の企業は、規格ベース インターフェイス (AXI、PCIe、SAS、SATA、USB、HDMI、ENET など) に対応する VIP を開発しています。VIP を使用するメリットには、デザインの品質向上、再利用によるスケジュールの短縮などがあります。

AMD の VIP コアは、ARM ライセンスのアサーションを使用する完全 AXI プロトコル チェック機能を提供する SystemVerilog ベースのシミュレーション モデルで、主要シミュレータをすべてサポートし、Vivado に含まれる無償のコアです。AMD は、AXI コンポーネント レベル (AXI-MM、AXI_Stream) を使用するデザインやプロセッシング システム (Zynq™ 7000) デザインで使用するための VIP を提供しています。

主な特長

- AXI4、AXI4-Stream、AXI4-Lite 用 AXI トラフィック ジェネレーター

- AXI & AXI Stream プロトコル チェッカーを完全サポート

- Zynq 7000 および Zynq US+ MPSoC をベースとするアプリケーションの論理シミュレーションをサポート

- CIPS (Control, Interface and Processing System) IP の論理シミュレーションをサポート

リソース

資料ポータル

HTML ベースの技術資料などを効率的に検索およびナビゲーションするためのオンライン ツール。

デザイン ハブ

特定のデザイン タスク、デバイス、ツールに関する最新の技術資料やリソースを提供。

トレーニング

さまざまなテーマのトレーニング情報を集めたライブラリ。

サポート コミュニティ

専門家によるサポート、デザイン アドバイザリ、既知の問題およびコミュニティ。