# Xcell journal

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

## Virtex-5 特集号

### INSIDE

Virtex-5 FPGA を使って

システム レベル性能を向上

Virtex-5 の使用率や

パフォーマンス、消費電力を

最適化するための HDL の

コーディング & 設計手法

幅広い用途をカバーする

マルチ ギガビットトランシーバ

Virtex-5 PCI Express

エンドポイント ブロック

Virtex-5 FPGA で

先進的メモリインターフェイス

デザインへの挑戦

**XILINX®**

[japan.xilinx.com/xcell/](http://japan.xilinx.com/xcell/)

# Xcell journal

|                   |                                           |

|-------------------|-------------------------------------------|

| 発行人               | Forrest Couch<br>forrest.couch@xilinx.com |

| 編集                | Charmaine Cooper Hussain                  |

| アートディレクター         | Scott Blair                               |

| デザイン/制作           | Teie, Gelwicks & Associates               |

| テクニカル<br>コーディネーター | Greg Lara                                 |

| 日本語版統括            | 澤田 修<br>osamu.sawada@xilinx.com           |

| 制作進行              | 竹腰 美優紀<br>miyuki.takegoshi@xilinx.com     |

| 制作                | オフオフ京都 (offoff-kyoto)                     |

| 広告                | 有限会社エイ・シー・シー                              |

| 印刷                | ノップス株式会社                                  |

japan.xilinx.com/xcell/

Xcell Journal 58・59 合併号

2007 年 3 月 1 日発行

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400

**ザイリンクス株式会社**

〒141-0032

東京都品川区大崎 1-2-2

アートヴィレッジ大崎セントラルタワー 4F

©2007 Xilinx, Inc. All Right Reserved.

XILINX や、Xcell のロゴ、その他本書に記載の商標は、米国およびその他の国々の Xilinx 社の登録商標です。PowerPC は、米国またはその他の国における IBM 社の商標です。ほかすべての名前は、各社の登録商標または商標です。

本書は、米国 Xilinx, Inc. が発行する英文季刊誌を、ザイリンクス株式会社が日本語に翻訳して発行したものです。

米国 Xilinx, Inc. および Xilinx, Inc. 株式会社は、本書に記載されたデータの使用に起因する第三者の特許権、他の権利、損害における一切の責任を負いません。

本書の一部または全部の無断転載、複写は、著作権法に基づき固く禁じます。

Printed in Japan

本誌 Xcell Journal 58・59 合併号では、ザイリンクスの Virtex™-5 FPGA をさまざまな角度で紹介する多彩な記事をお届けします。本号は、ザイリンクス経営陣や業界各社の見解に加え、エンジニアリングソリューションやデザインチャレンジ、設計ツール、カスタマーサクセスストーリー、そして、パーティカル市場に関するさまざまな記事をご紹介します。また、アプリケーションノートやボード、IP をカバーするテクニカルリファレンスも掲載しています。

## Xcell Publications が APEX 2006 Award of Excellence を受賞

この度、Xcell Publications のフラッグシップである Xcell Journal と I/O Magazine が、APEX 2006 Award of Excellenceにおいて、マガジンおよびジャーナルのデザイン/レイアウト、ならびにカスタム出版のマガジンおよびジャーナルの 2 部門で受賞しました。

APEX 2006 (18 th Annual Awards for Publication Excellence) は、企業のニュースレターやマガジン、年次報告書、ブローシャ、Web サイトなどの優秀な出版物に対して賞を授与する国際的なコンテストです。APEX の審査員によると、2006

年度のコンテストは例年になく競争が激しく約 5,000 ものエントリがありました。グラフィック デザインの秀逸さや編集内容の品質、メッセージの伝達と全体的なコミュニケーション効果などが選考基準とされました。

ザイリンクスのワールドワイド マーケティング担当バイス プレジデント、Sandeep Vij は、「APEX 審査員により、Xcell のマガジンが出版分野において名だたる企業と共に賞をいただけたのは大変名誉なことです」と述べています。「過去 18 年間、ザイリンクスの出版物は、火星探査機から民生機器のハンドセット、フラットパネル ディスプレイ、オートモーティブ向けインフォテインメント システムにいたるまで、多種多様な電子機器のデザインに、ザイリンクスのプログラマブル チップを使用している数多くのエンジニアへ “ハウツー” 情報を提供するための基本ツールとして貢献してきましたが、業界最高ランクのマガジンとして賞をいただけたことで、改めてその価値と品質が証明されました」。

カスタム出版のマガジンおよびジャーナル部門では、Blue Cross Blue Shield、CMP Media/Digital Connect、DaimlerChrysler、IBM Journal of Research and Development、Mac Publishing、National Football League、National Foundation for Advancement in the Arts、Penton Custom Media、および Time Inc. Strategic Communications といった各業界の企業が受賞しており、ザイリンクスはこのそうしたるリストに名を連ねることになりました。

*Forrest Couch*

Forrest Couch

発行人

# Xcell journal

## VIEWPOINT

|                                     |   |

|-------------------------------------|---|

| 遂に登場 65nm Virtex-5 FPGA             | 2 |

| 偏在するシリアル I/O ソリューション「トリブルプレイ」への挑戦   | 6 |

| Virtex-5 が実現するシリアル コネクティビティ ソリューション | 7 |

## PERFORMANCE

|                                                        |    |

|--------------------------------------------------------|----|

| Virtex-5 FPGA を使ってシステム レベル性能を向上                        | 10 |

| Virtex-5 の使用率やパフォーマンス、消費電力を最適化するための HDL のコーディング & 設計手法 | 14 |

| Virtex-5 FPGA から最良の結果を引き出す設計手法                         | 19 |

| Virtex-5 FPGA のパフォーマンスを最大限にするデザイン技法                    | 24 |

| Virtex-5 デバイスにおけるクロック管理                                | 28 |

## POWER

|                          |    |

|--------------------------|----|

| Virtex-5 FPGAによる 消費電力の削減 | 30 |

| コンパクト熱モデルへの適応            | 34 |

## SERIAL CONNECTIVITY

|                                               |    |

|-----------------------------------------------|----|

| 幅広い用途をカバーするマルチ ギガビット トランシーバ                   | 39 |

| Virtex-5 PCI Express エンドポイント ブロック             | 42 |

| PCI Express 市場のトレンド                           | 46 |

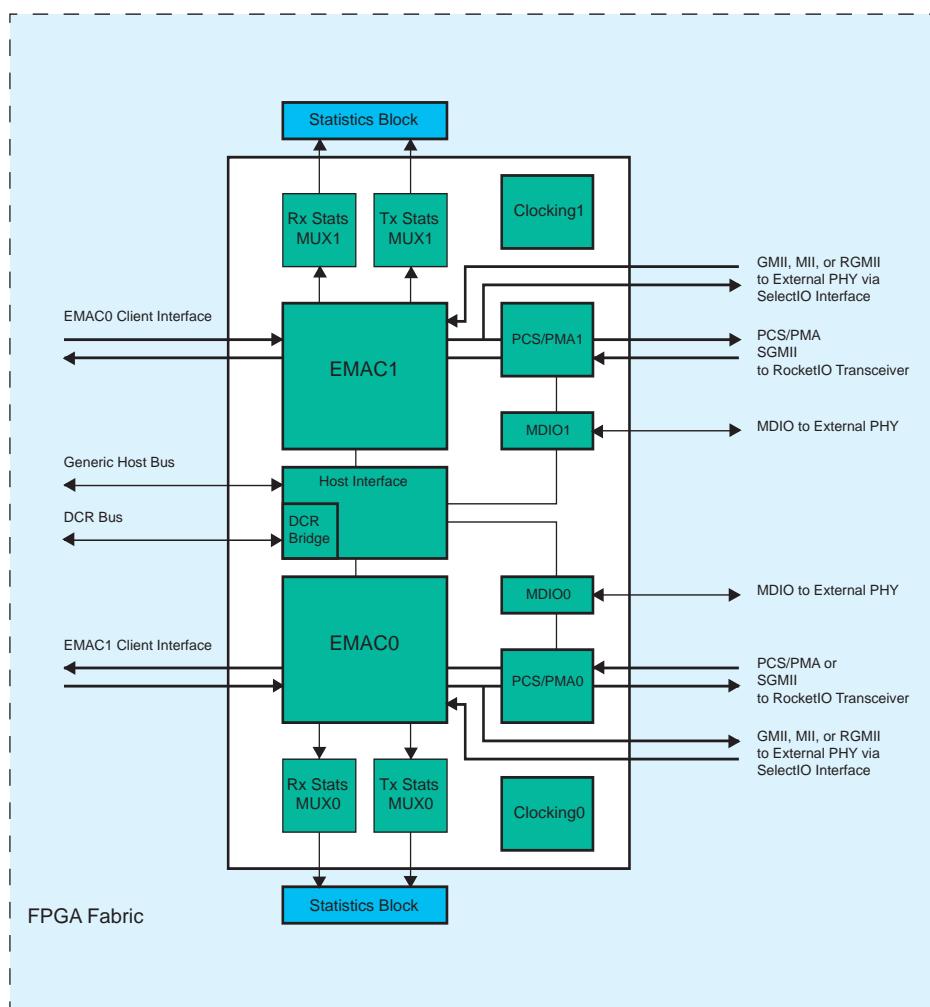

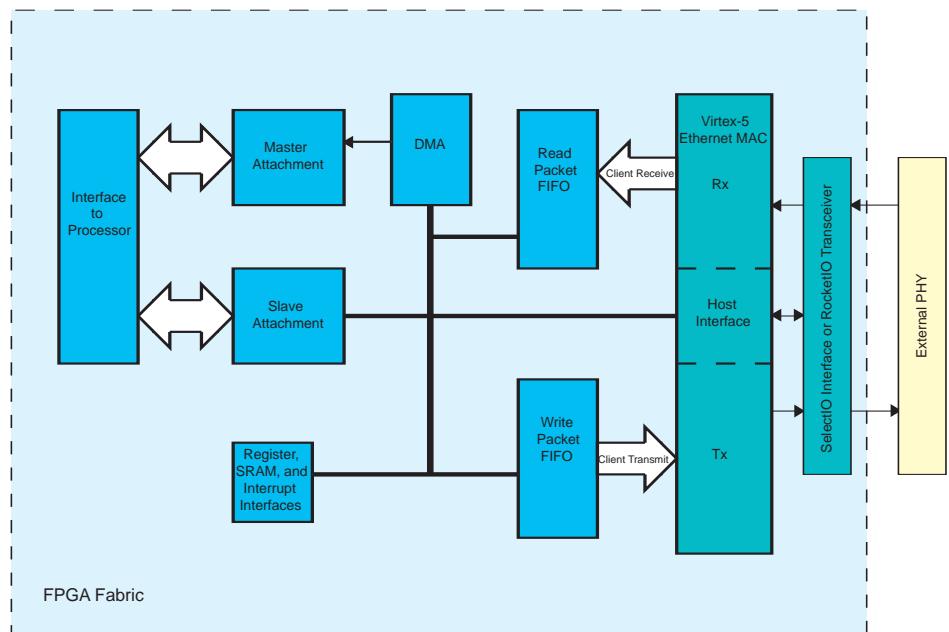

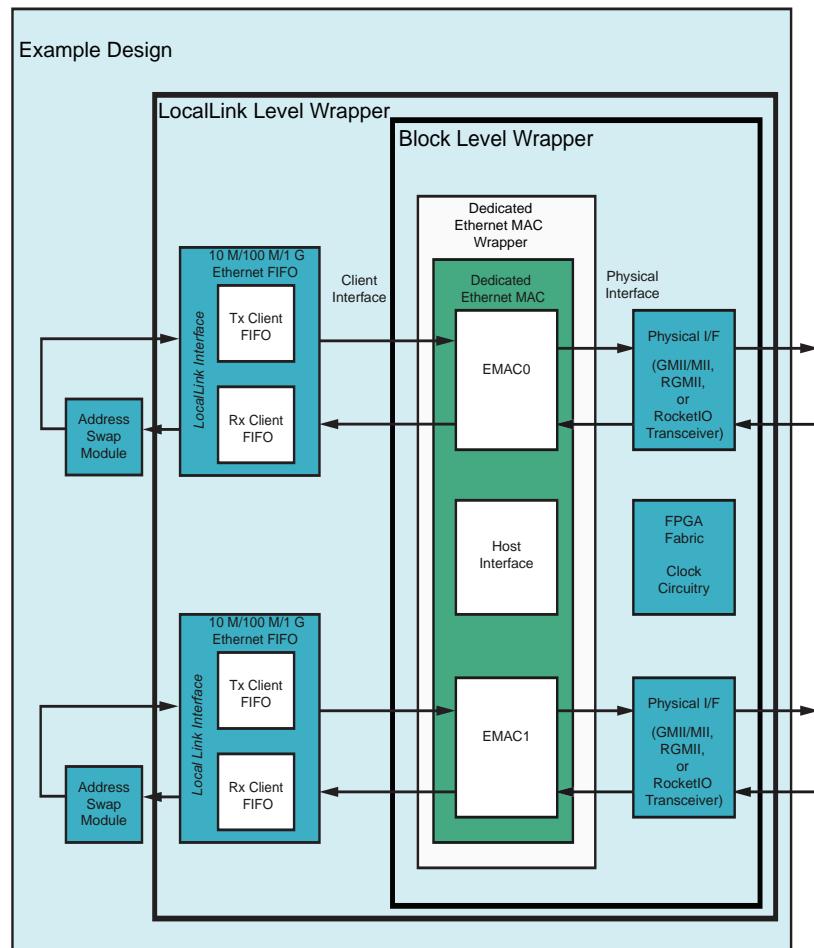

| Virtex-5 の新しいイーサネット MAC 機能を使ったデザイン            | 51 |

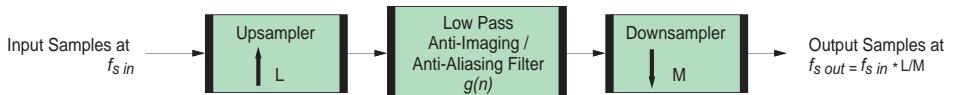

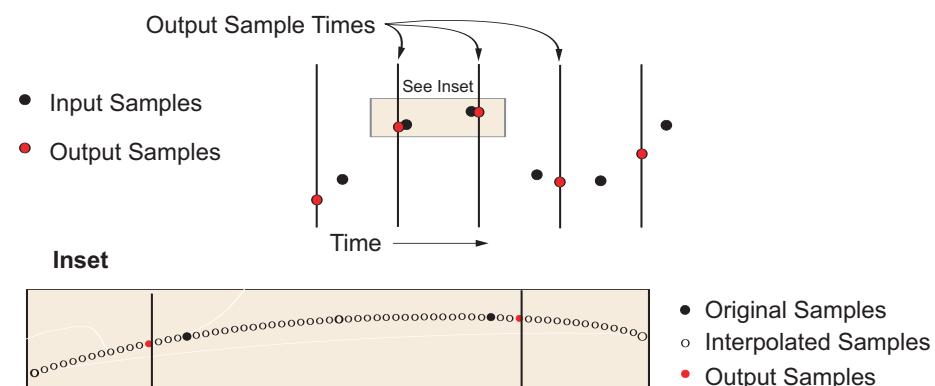

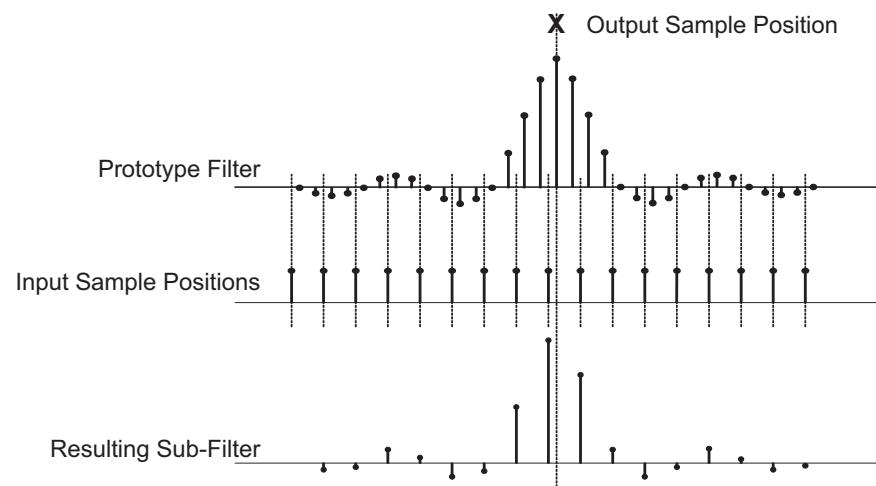

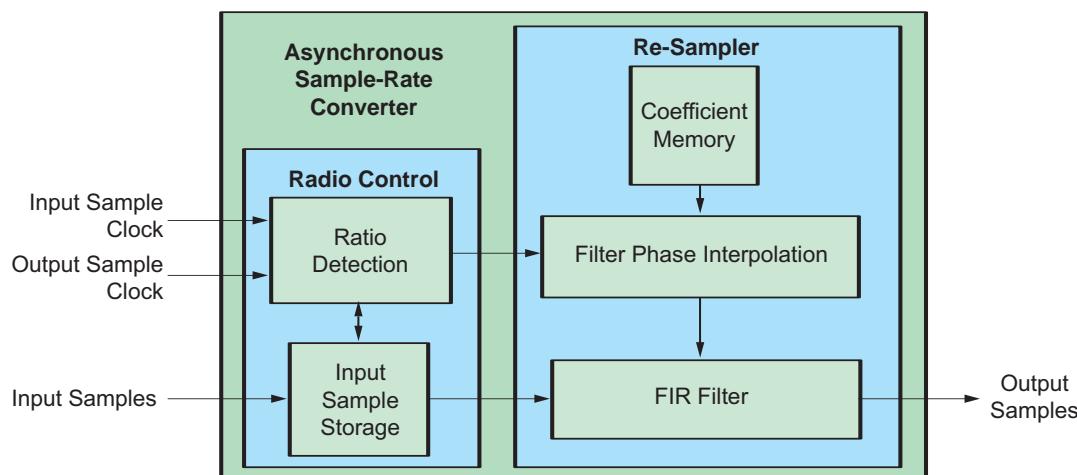

| AES オーディオ ストリーム間の非同期サンプルレートの変換                | 55 |

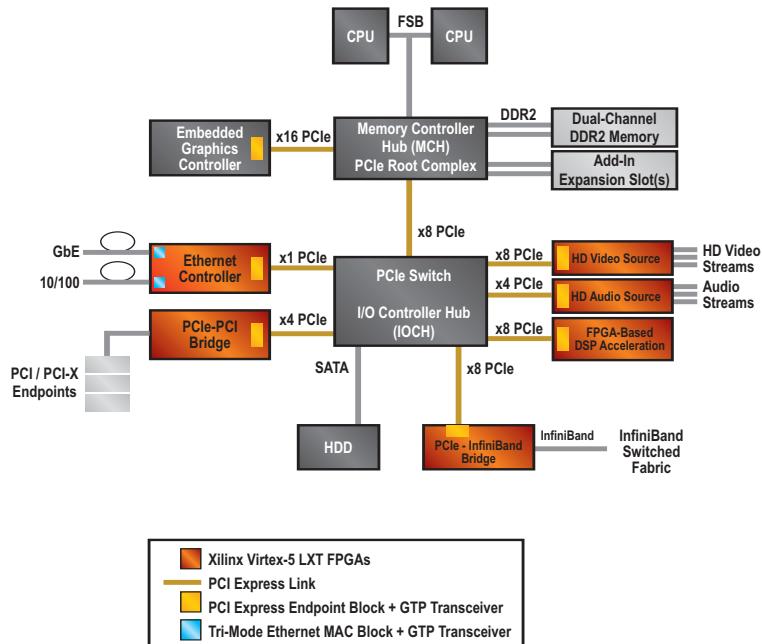

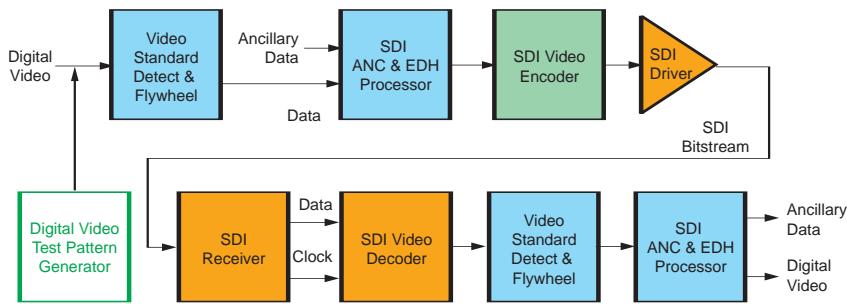

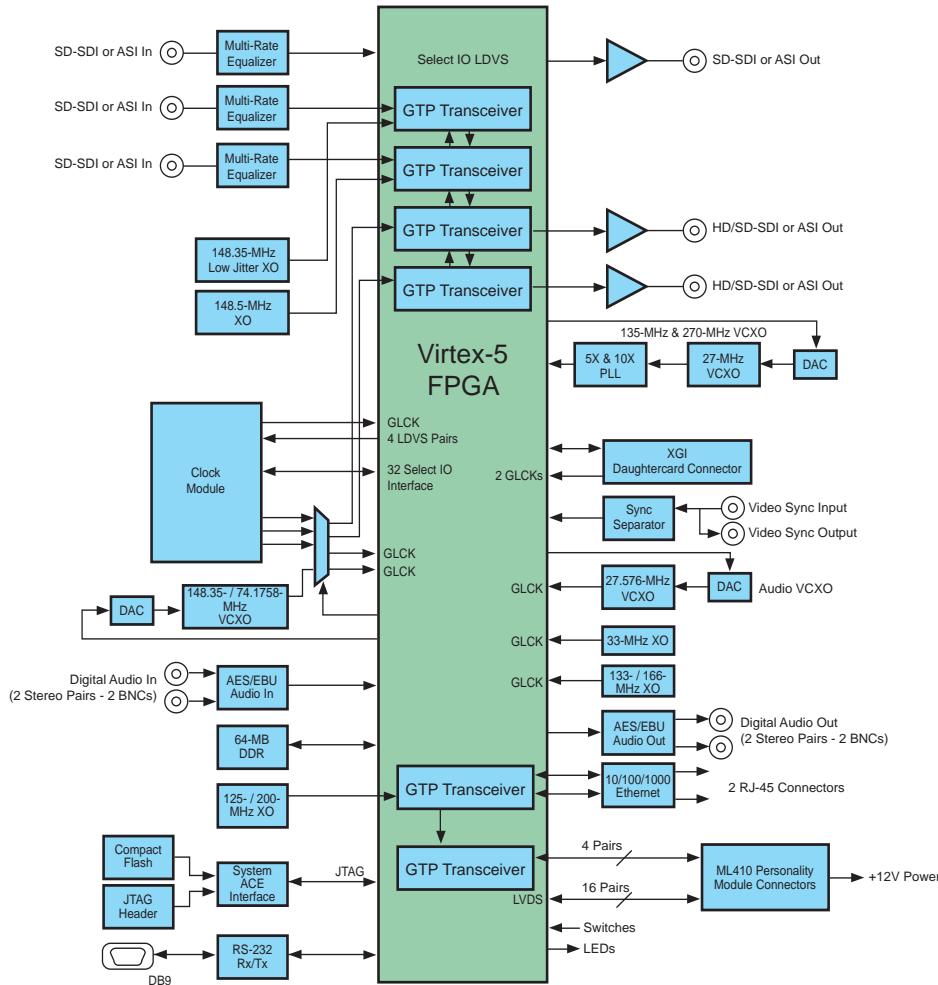

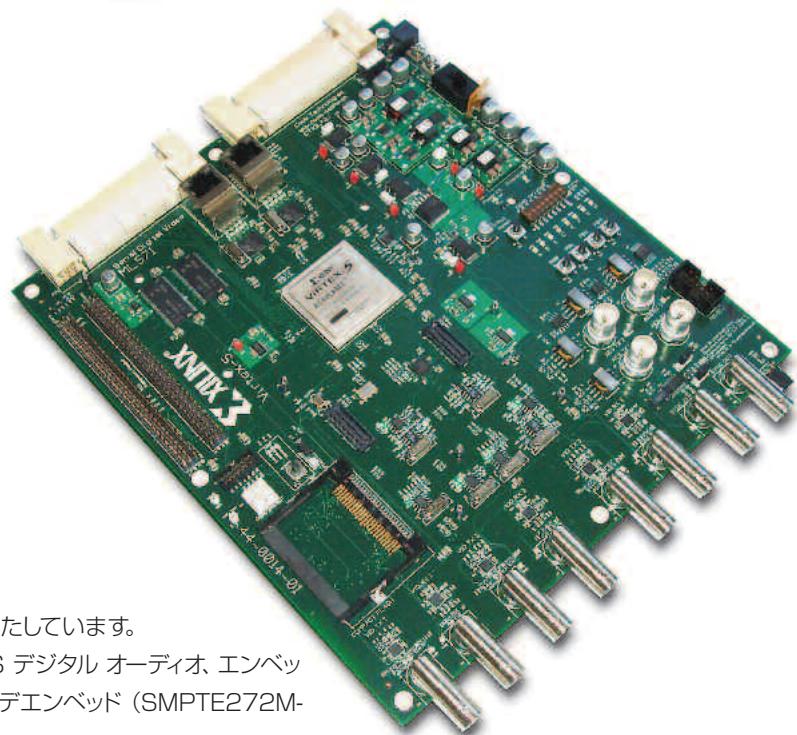

| Virtex-5 LXT デバイスによる統合ビデオ コネクティビティ ソリューションの実装 | 59 |

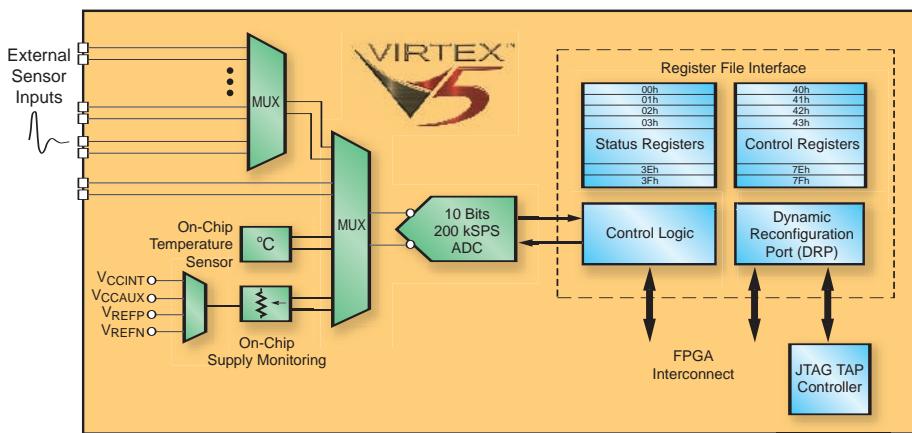

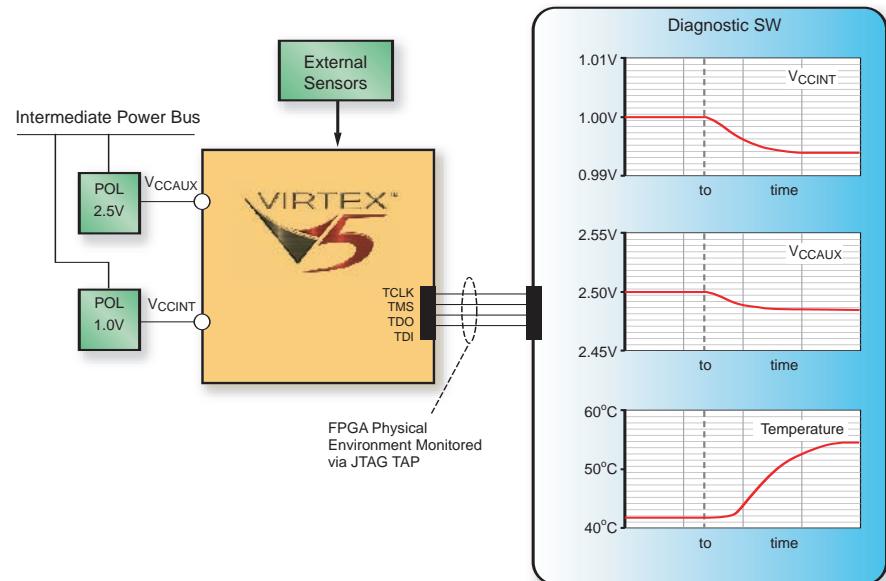

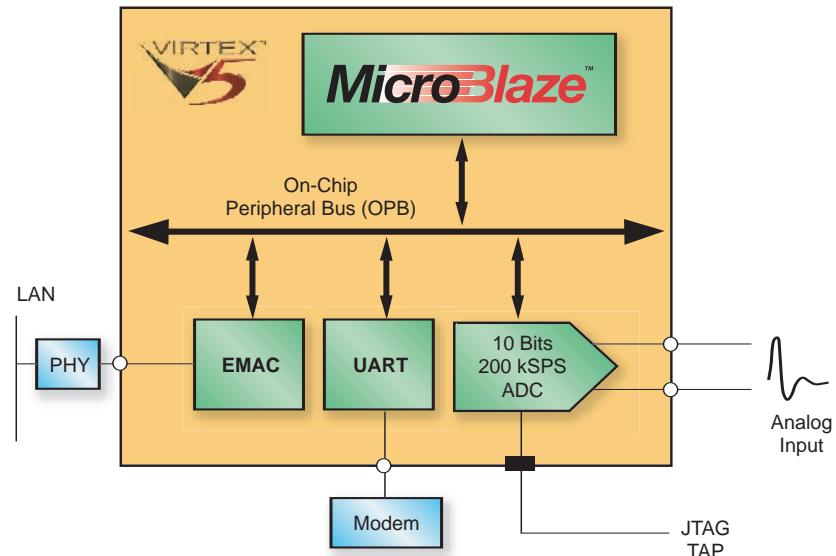

| Virtex-5 System Monitor によるシステム管理と 問題診断機能の拡張  | 63 |

## MEMORY INTERFACE

|                                                |    |

|------------------------------------------------|----|

| Virtex-5 FPGA のメモリ                             | 66 |

| Virtex-5 FPGA で先進的メモリ インターフェイス デザインへの挑戦        | 70 |

| メモリ インターフェイス ジェネレータ (MIG) ツール によるメモリ コントローラの実装 | 73 |

| Micron のメモリ インターフェイス                           | 76 |

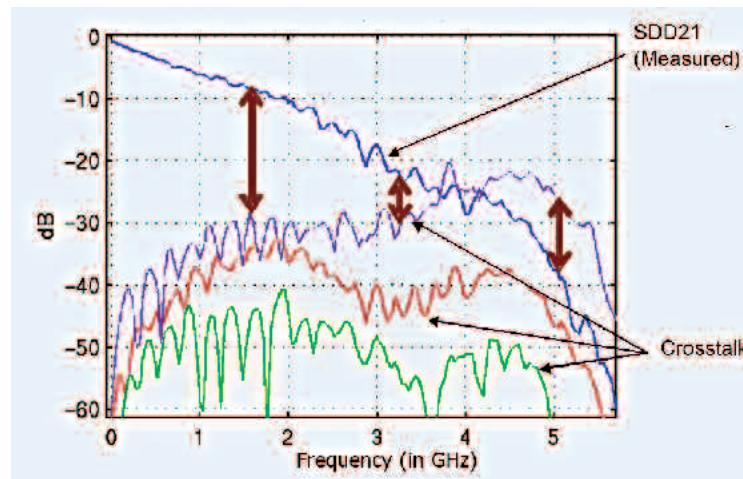

| シグナル インテグリティのための Virtex-5 DDR2 メモリ インターフェイスの設計 | 79 |

## VERTICAL MARKET SOLUTION

|                                                            |    |

|------------------------------------------------------------|----|

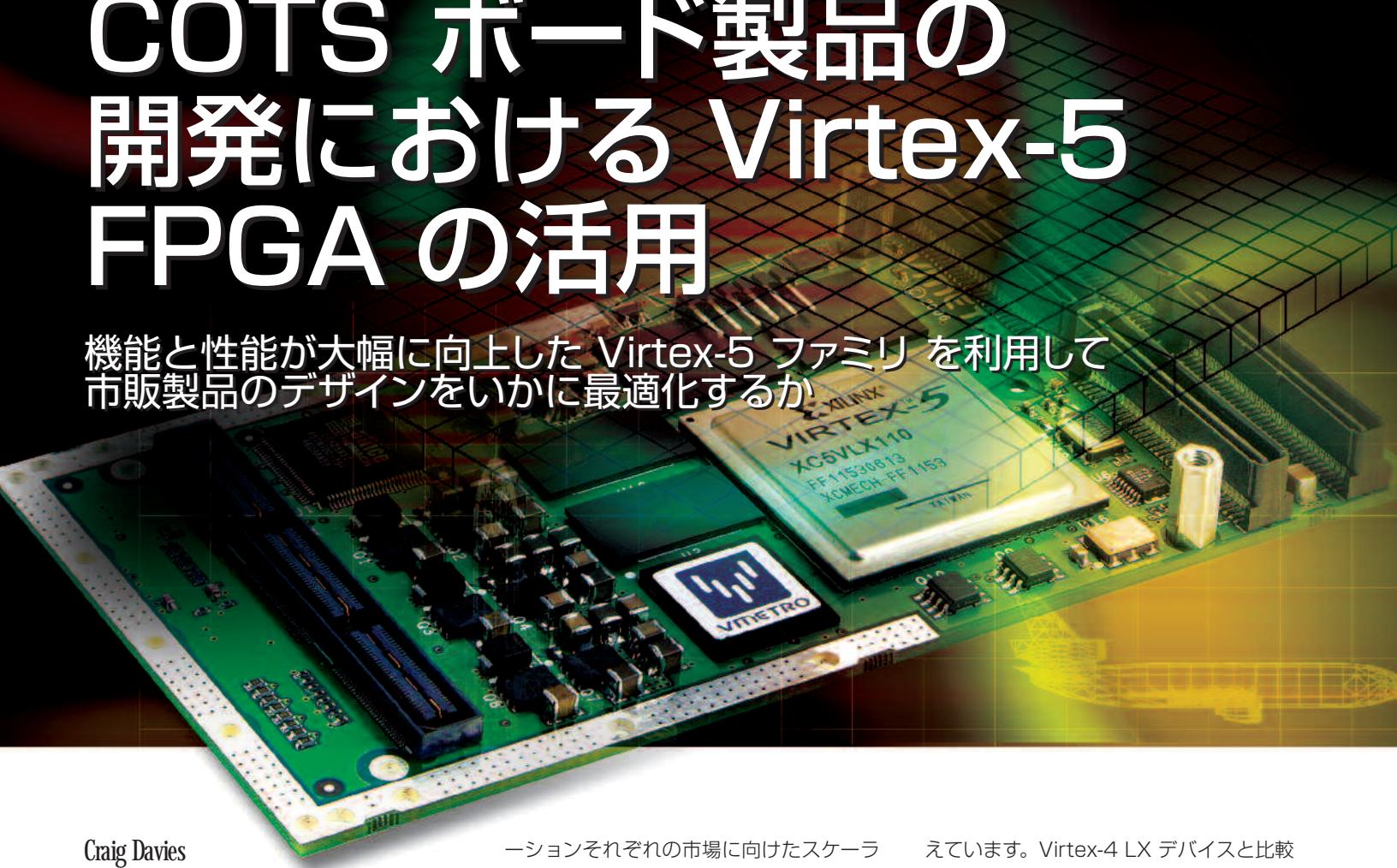

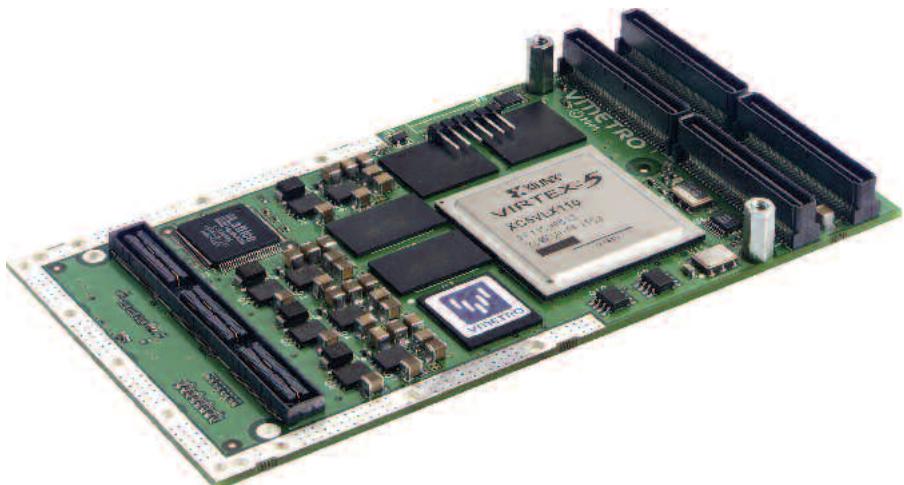

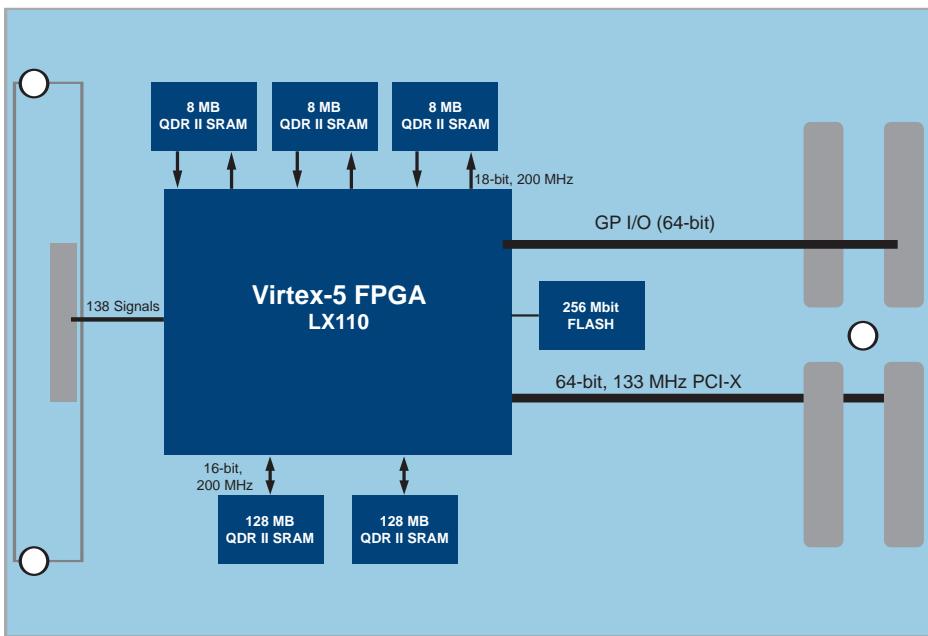

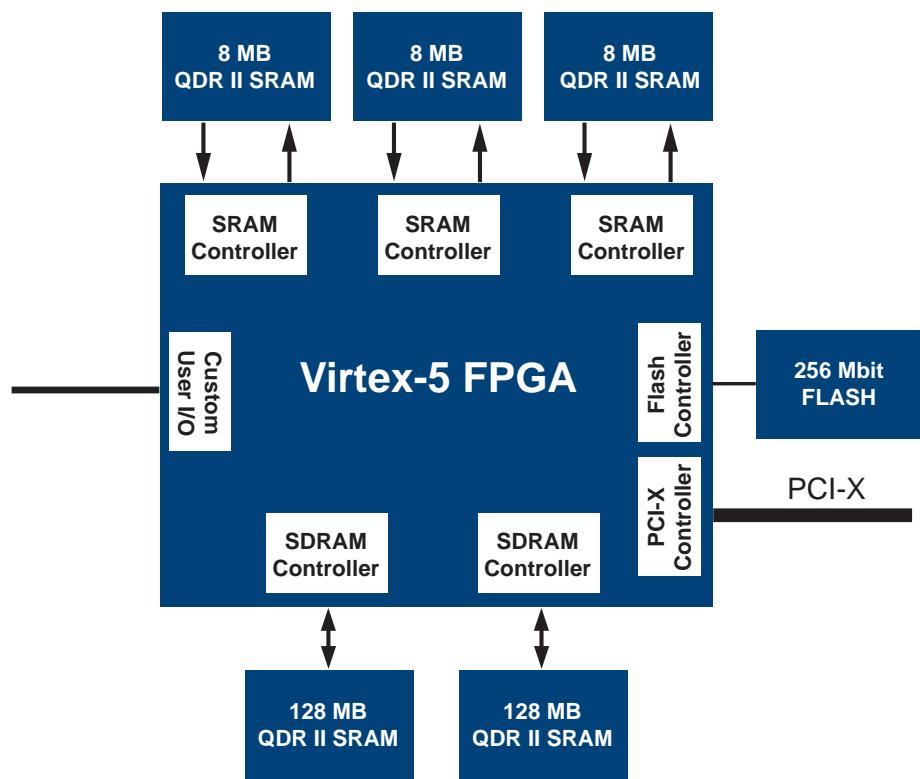

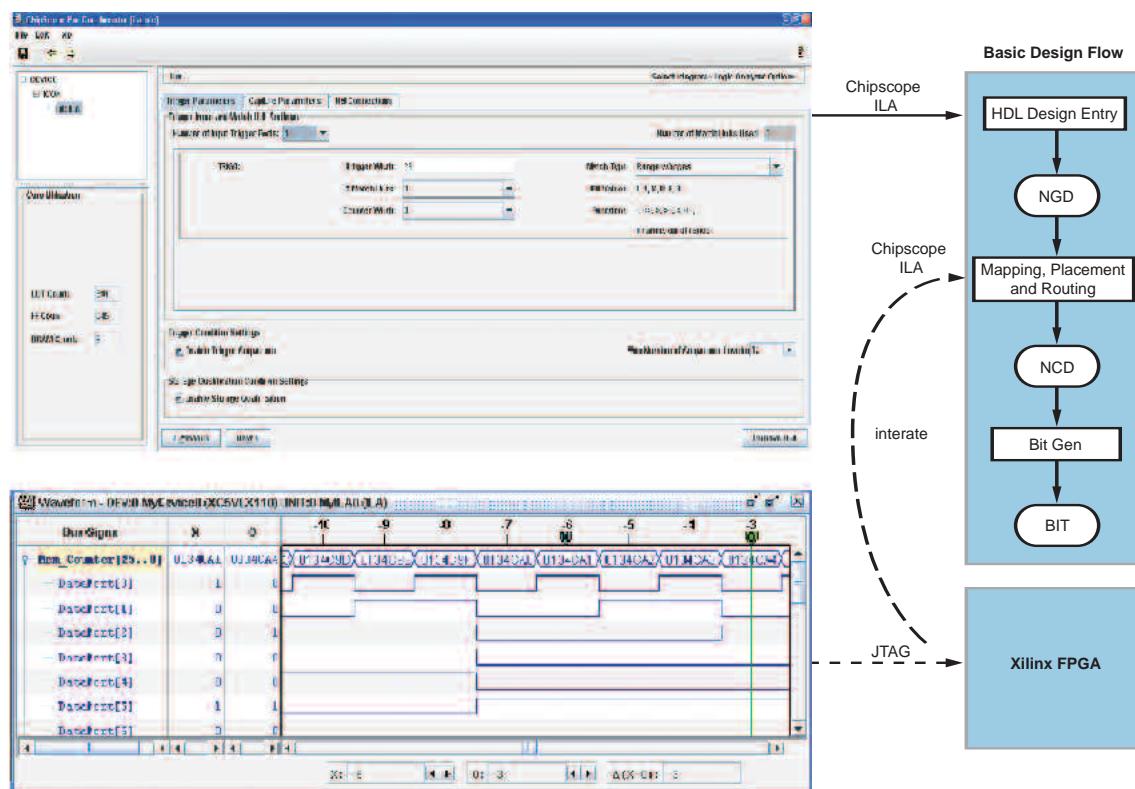

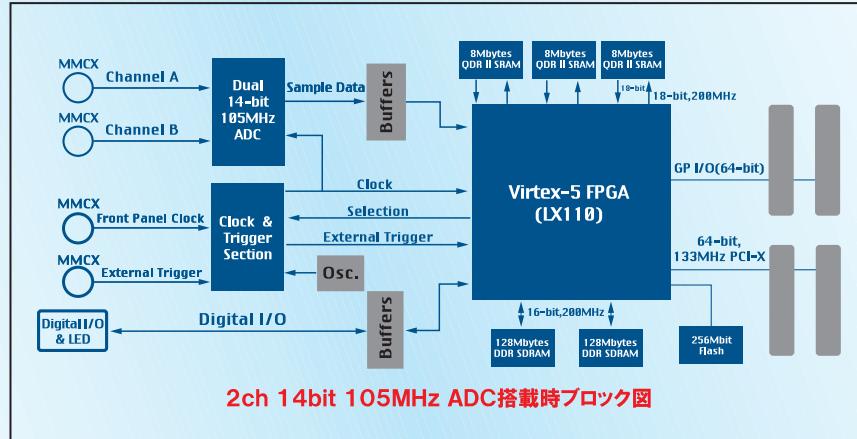

| COTS ボード製品の開発におけるVirtex-5 FPGAの活用                          | 82 |

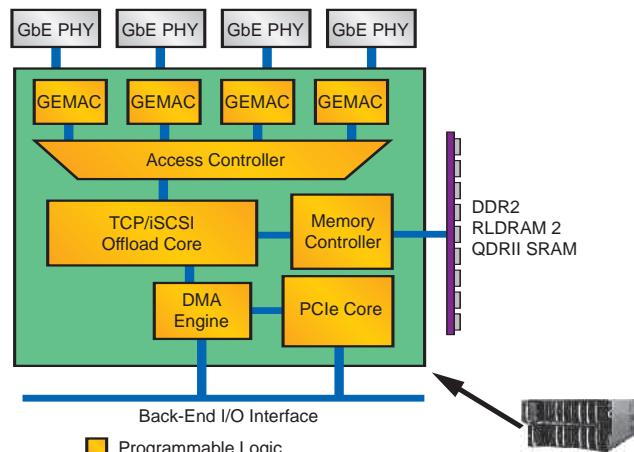

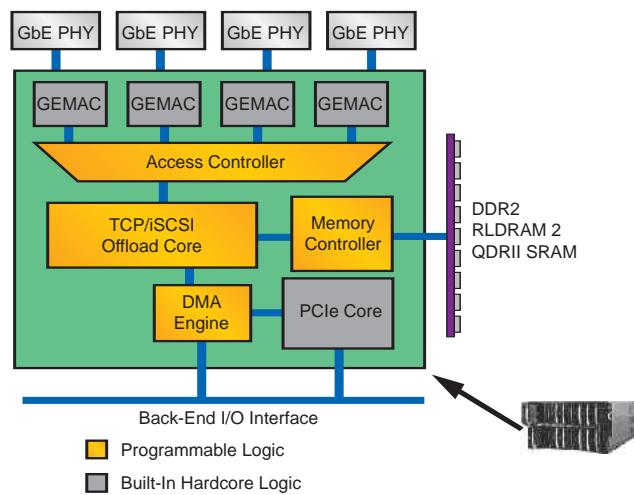

| マルチポート 1Gbps/10Gbps ベースでの TCP/iSCSI プロトコル オフロード ソリューションの実現 | 90 |

| Virtex-5 LXT プラットフォームでの暗号化アルゴリズムの実装                        | 93 |

## GENERAL

|                        |    |

|------------------------|----|

| Virtex-5 EasyPath FPGA | 96 |

|------------------------|----|

## REFERENCE

|                          |        |

|--------------------------|--------|

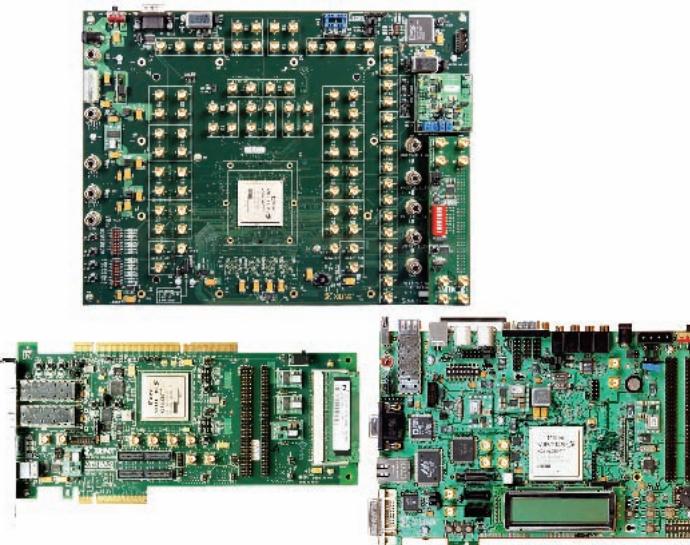

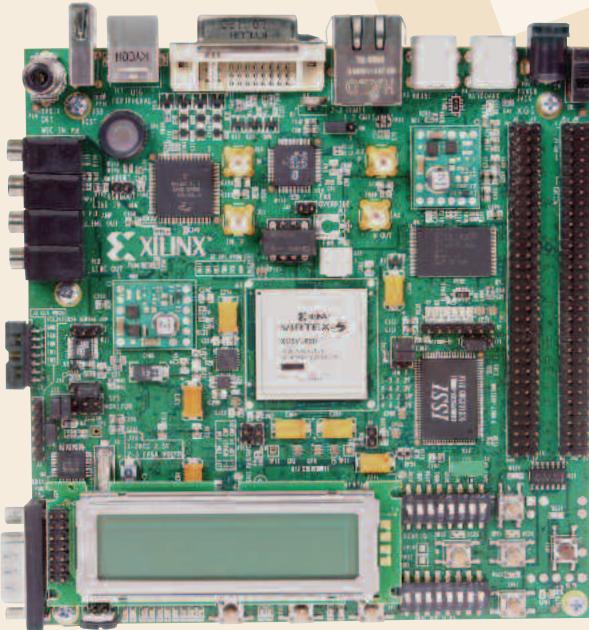

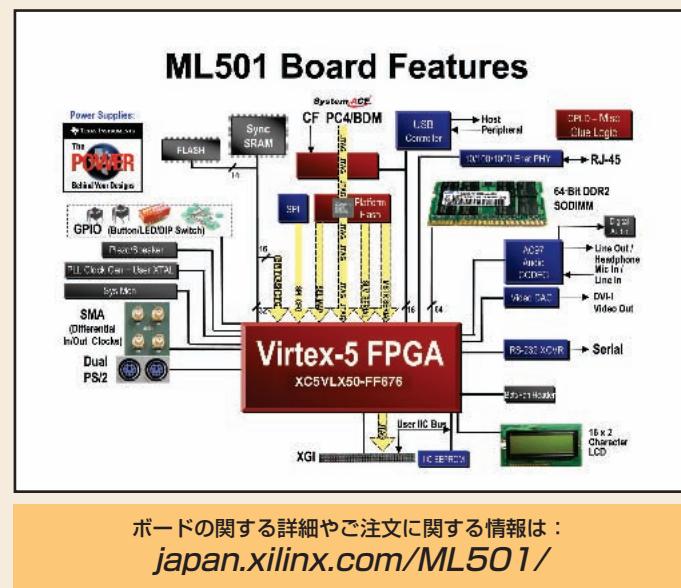

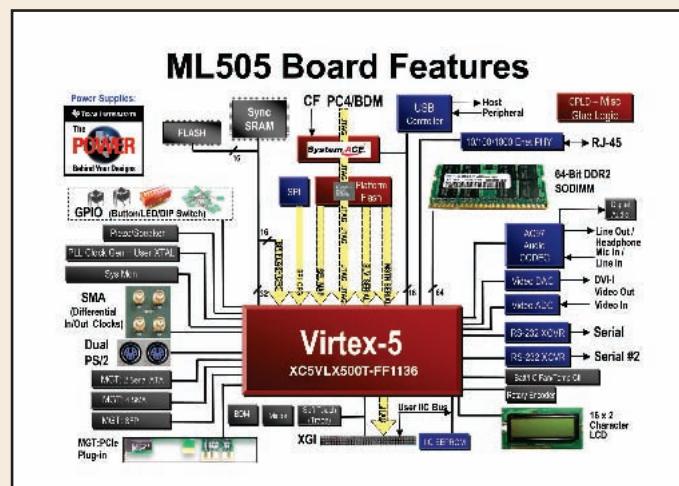

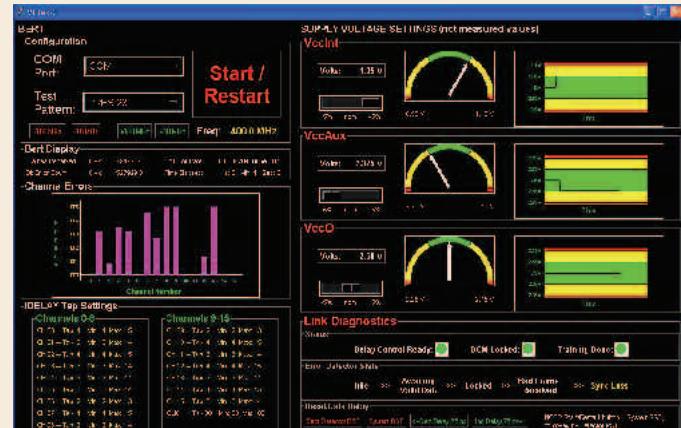

| Virtex-5 ボードおよびキット       | 98     |

| INFORMATION              |        |

| ザイリンクス トレーニング スケジュール     | 13, 18 |

| ザイリンクス販売代理店 オリジナル トレーニング | 69     |

| ザイリンクス ウェブ セミナー          | 104    |

| ザイリンクス イベント カレンダー        | 表 3    |

## 広告索引

|                   |     |

|-------------------|-----|

| 株式会社コンピューテックス     | 9   |

| シンプリシティ株式会社       | 23  |

| 株式会社グレーブシステム      | 62  |

| 株式会社ミッシュインターナショナル | 89  |

| 株式会社ソリトンシステムズ     | 92  |

| 有限会社ヒューマンデータ      | 103 |

Xcell Journalのご送付先住所等の変更は:

<http://japan.xilinx.com/xcell/henko/>

Xcell Journalの新規定期購読のお申込みは:

<http://japan.xilinx.com/xcell/toroku/>

## TABLE OF CONTENTS, 58・59 合併号

### PERFORMANCE

## Virtex-5 FPGA を使ってシステム レベル性能を向上

新しい ExpressFabric™ テクノロジーによる 高パフォーマンスの達成

10

### SERIAL CONNECTIVITY

## 幅広い用途を カバーする マルチ ギガビット トランシーバ

量産用アプリケーションに 多様性と使い易さ、消費電力低減、コスト効果をもたらす Virtex-5 GTP トランシーバ

40

### SERIAL CONNECTIVITY

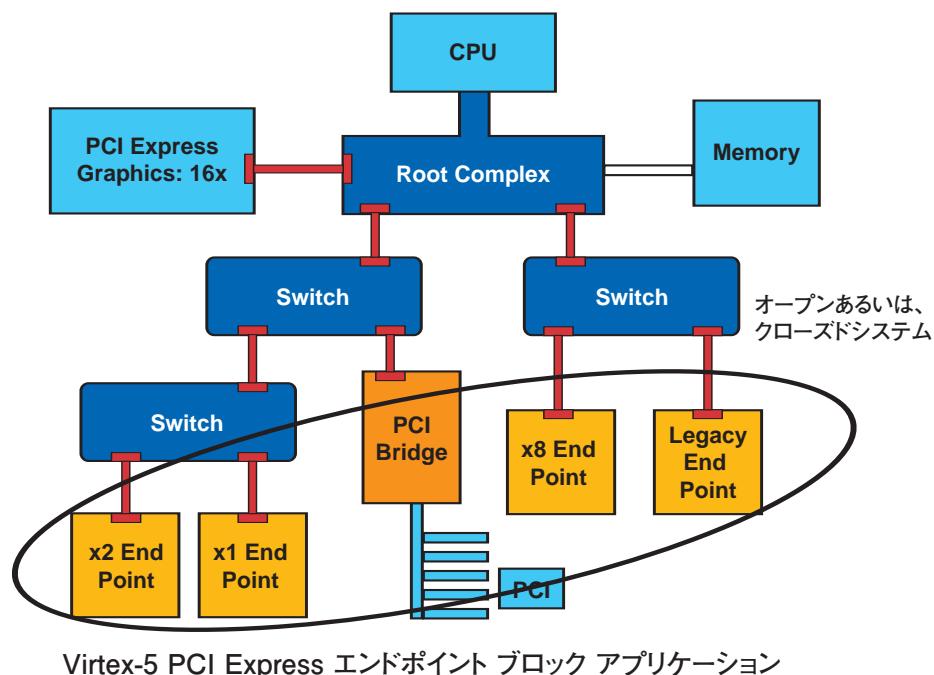

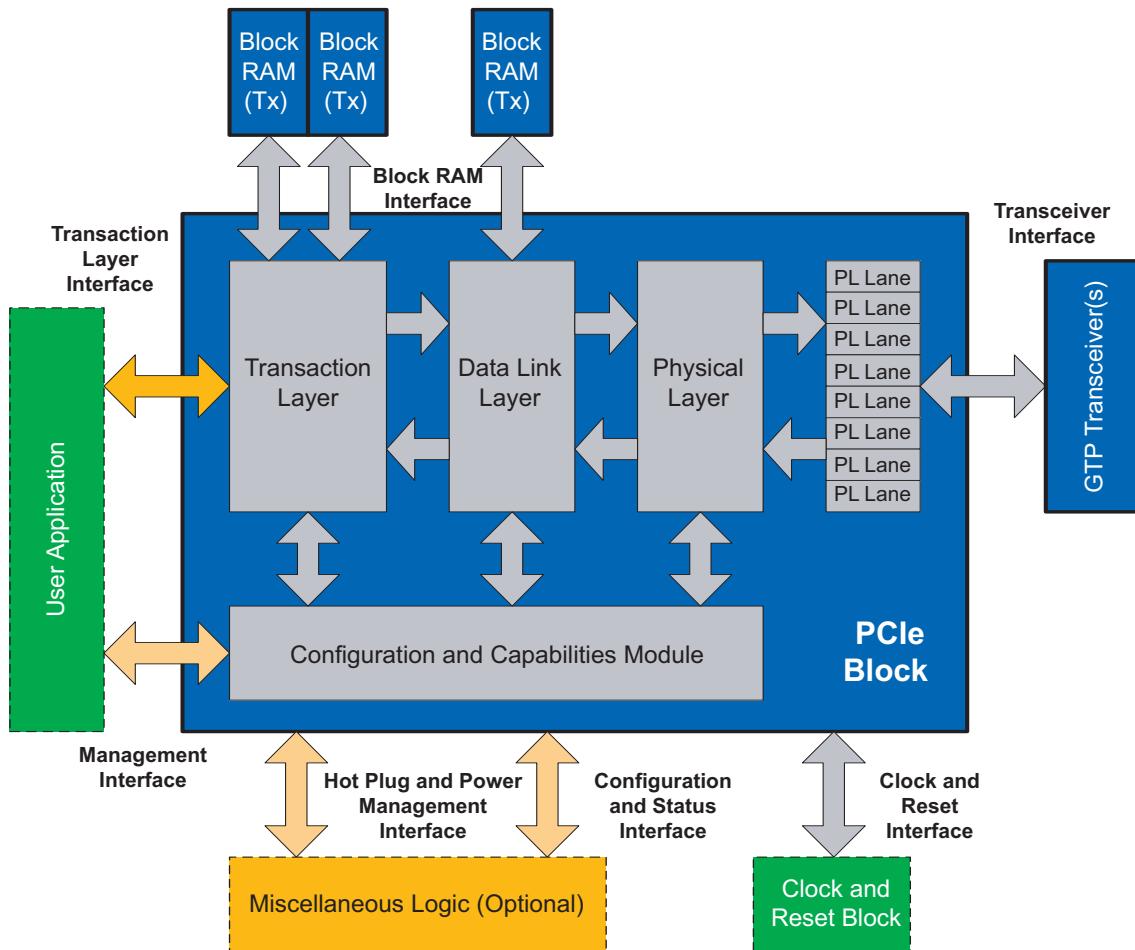

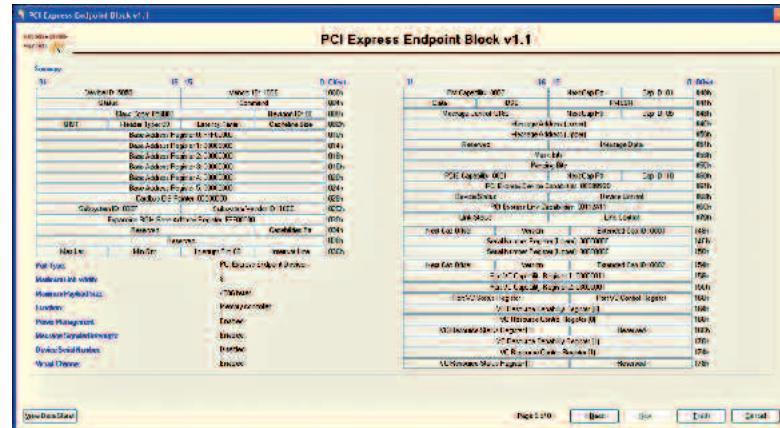

## Virtex-5 PCI Express エンドポイント ブロック

広帯域インターフェクトの標準となりつつある PCI Express の利用により、コンフィギュラブル シングルチップ ソリューションを 可能にする Virtex-5 LXT PCI エンドポイント ブロック

43

### MEMORY INTERFACE

## Virtex-5 FPGA で 先進的メモリ インターフェイス デザインへの挑戦

最先端の最速メモリインターフェイス をサポートする Virtex-5 デバイス

70

# Introducing the Virtex-5 FPGA Family 遂に登場 65nm Virtex-5 FPGA

世界初 65nm FPGA は、パフォーマンス、電力供給、能力、価値に新地平を拓く

Steve Douglass

Vice President

Product Development,

Advanced Product Division

Xilinx, Inc.

[stephen.douglass@xilinx.com](mailto:stephen.douglass@xilinx.com)

Xcell Journal 本号では、Virtex™-5 の特集号としてさまざまな角度でザイリンクス Virtex-5 FPGA をご紹介します。Virtex-5 ファミリは、業界初の 65nm FPGA であるだけでなく、世界最先端のアーキテクチャと最高のパフォーマンスを提供します。ザイリンクスは、歴史的に画期的なテクノロジの開発を行ってきましたが、その歴史を継続しつつ、さまざまな業界の第一線で活躍する設計エンジニアの声にも耳を傾けることで、Virtex-4 FPGA ファミリを成功に導いた次の特徴をベースに開発を行いました。

- ・パフォーマンスの向上

- ・ロジックの高集積度化

- ・消費電力の低減

- ・先進機能の追加

FPGA が元来提供するバリューとして、Time-to-Market の短縮や多機能性、進化を続ける標準規格へのサポート、リスクの軽減、フィールド アップグレード性、システムの総コストの低減が挙げられます。ザイリンクス FPGA は、パフォーマンスやロジック容量、消費電力、コストなどに対してよりいっそうの改善を求めるユーザーに応えるプラットフォームです。

ザイリンクス製品は対象となるアプリケーションを深く理解した上で革新的なデザインを実現していますが、Virtex-5 ファミリは、最先端の 65nm プロセス技術を利用して革新的デザインが結合されています。本稿では、Virtex-5 デバイスの新機能とその基礎をなす技術について説明すると共に、世界をリードする FPGA アーキテクチャが今日のデザインにいたるまでを解説します。

## プロセス技術と 革新的アーキテクチャ

Virtex-5 FPGA は、ザイリンクスの ASMBL (Advanced Silicon Modular Block) アーキテクチャを用いて 65nm トリプル酸化膜技術をベースに構築されており、より高いレベルでシステムの統合を実現しています。この新しいファミリは、より高性能で高集積、低消費電力、そしてシステム全体の総

コストを抑えたプログラマブル システムに対するニーズに応える先進のプラットフォームです。

これらニーズの 1 つか 2 つを提供するのは簡単かもしれません、ザイリンクスが目指したのは、これらすべてを同時に達成することでした。

ザイリンクスは、高度な IC プロセス開発や革新的なアーキテクチャ、回路設計を通して、この課題を克服することに成功しました。Virtex-4 ファミリに採用され既に実証済みの ASMBL チップ レイアウト アーキテクチャにより、必要なデバイス リソース（ロジック メモリ、数値演算、I/O、IP）を最適な形でミックスし、新しいプラットフォームとして次の 4 種類を提供します。

- ・高性能ロジック向けに最適化された LX プラットフォーム

- ・低消費電力のシリアル I/O 内蔵の、高性能ロジック向けに最適化された LXT プラットフォーム

- ・低消費電力のシリアル I/O が内蔵され、膨大な算術演算とメモリを使用する高性能 DSP 向けに最適化された SXT プラットフォーム

- ・エンベデッド プロセッシングと超高速シリアル I/O 向けに最適化された FXT プラットフォーム

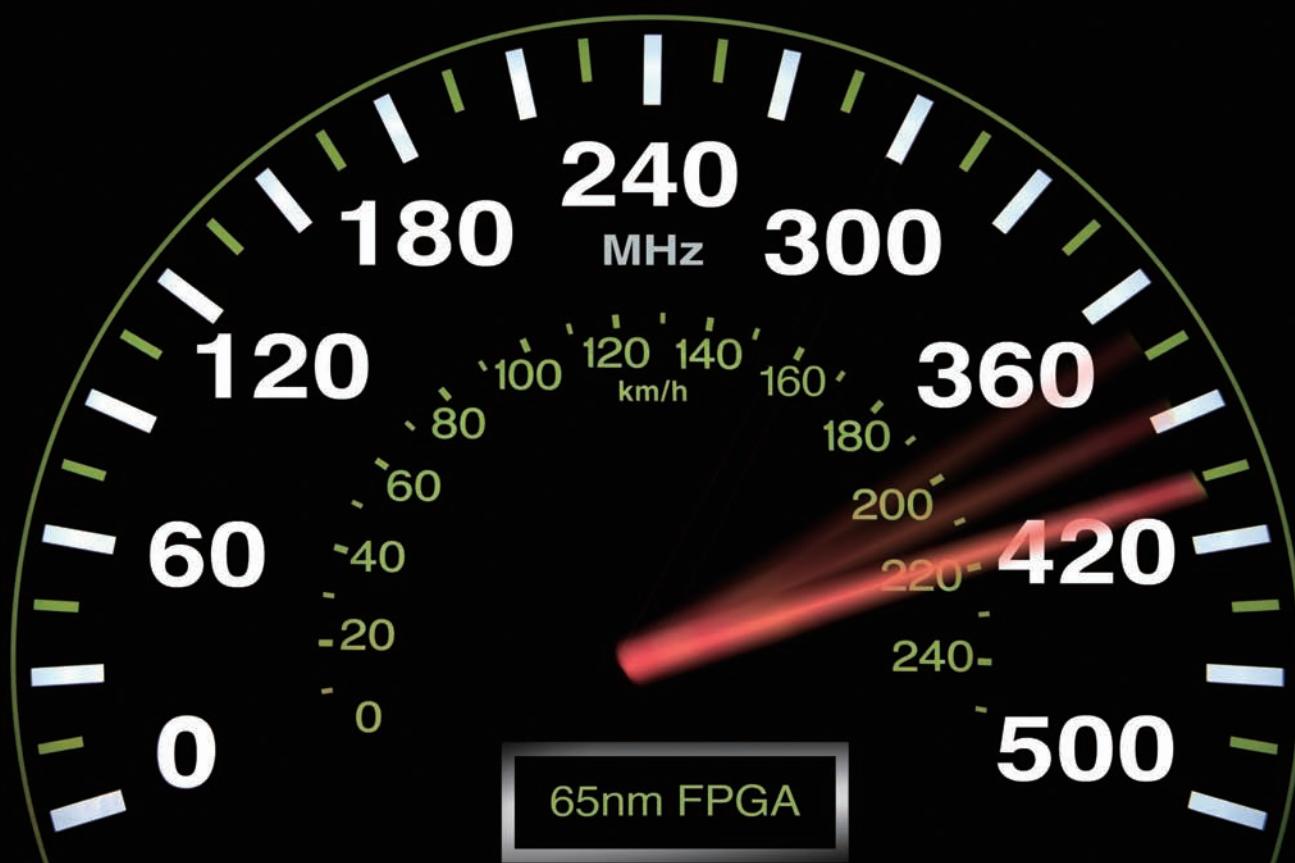

Virtex-4 ファミリと Virtex-5 デバイスとを比較した場合、平均速度は 30% 高速化し、ロジック容量は 65% 増大しています。また、ダイナミック消費電力は 35% 削減され、チップ エリアも 45% 縮小し、ファンクションあたりのコスト低減を実現しています。

## 性能と集積度の向上

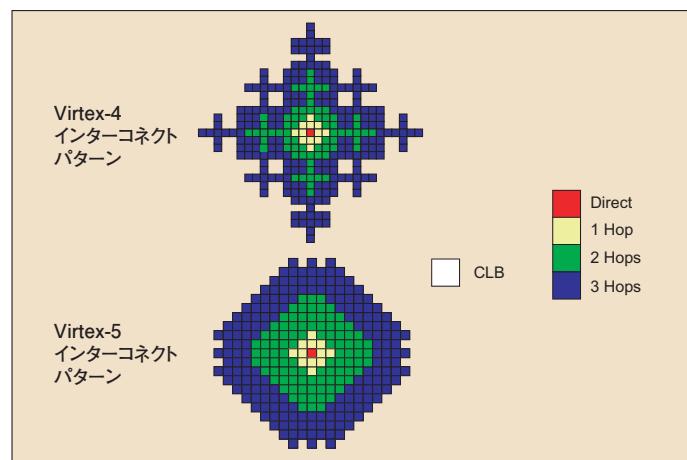

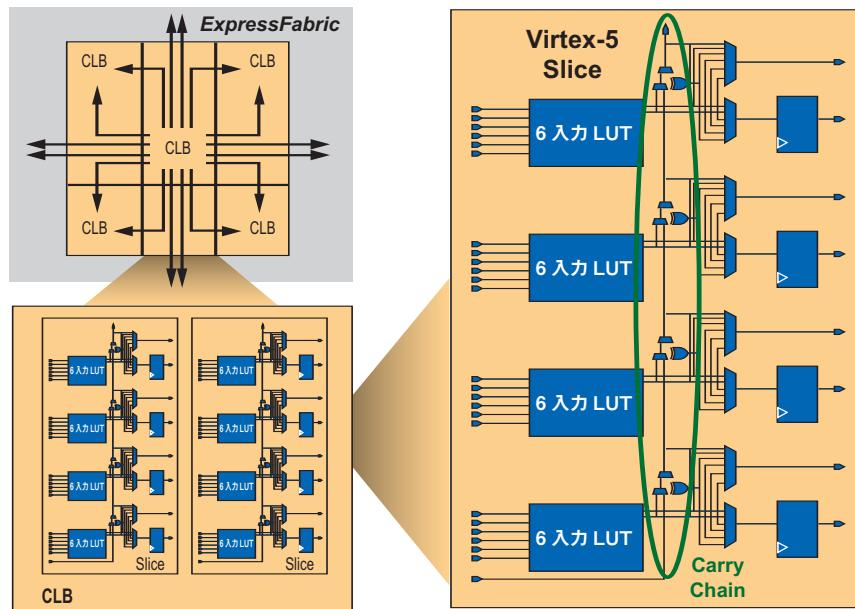

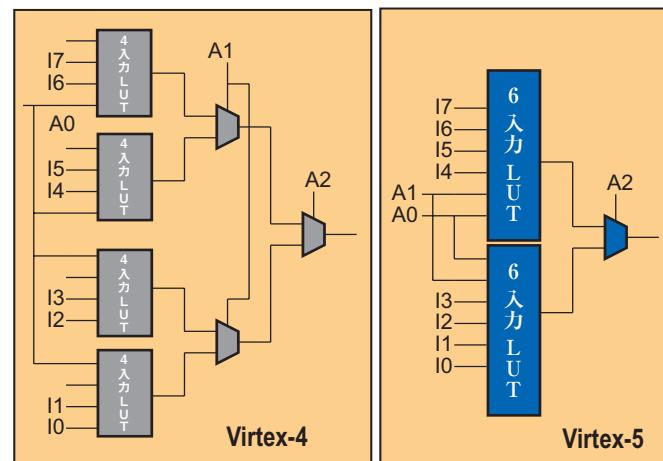

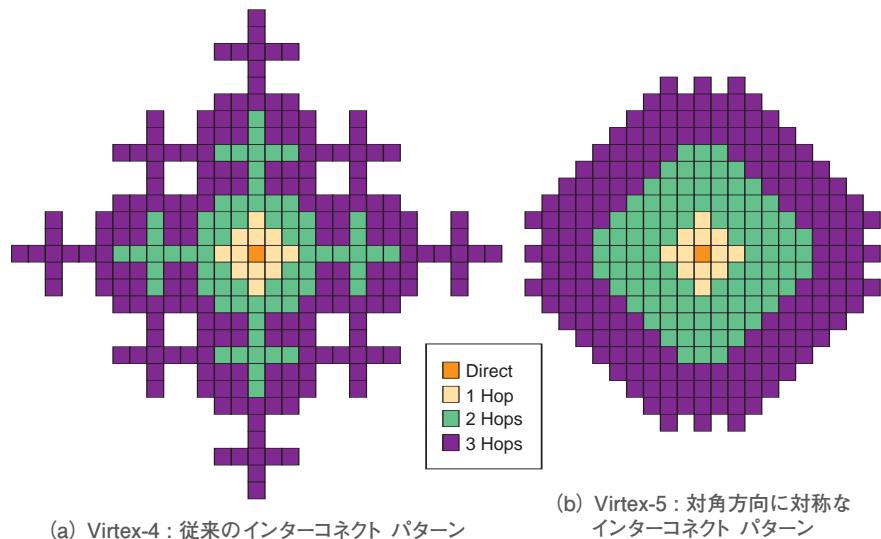

ExpressFabric™ テクノロジでは、ロジックとローカル インターコネクト配線を改善しました。図 1 に示すとおり、このテクノロジは 6 つの独立した入力を備えるルックアップ テーブル（LUT）と、対角方向に対称な新しいインターネット構造を採用しています。ExpressFabric テクノロジは、Virtex-4 アーキテクチャと比較して、より少ない LUT

レベルでコンビネーション ロジックをインプリメントし、隣接するビルディング ブロックにより少ない連結接続を行います。このため、データバスの遅延が減少し、デザインのパフォーマンスが向上されます。

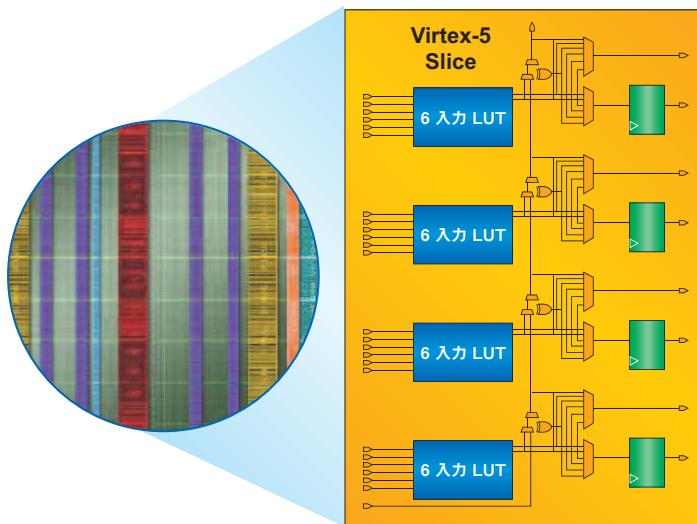

## 先進の 6 入力 LUT ロジック構造

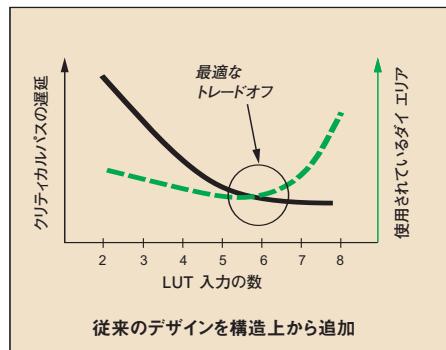

長年、業界標準は 4 入力の LUT でしたが、65nm では LUT はインターネットより縮小率が加速しました。このため、メモリとしてのビット数が 4 倍の 6 入力 LUT では、CLB エリアをわずか 15% 増やすだけで、各 LUT に平均 40% 以上のロジックを詰め込むことができます。このように、ロジックが高集積化されると、一般にカスケード接続した LUT の数は減り、クリティカル パスの遅延が改善されます（図 2）。

ISE™ 8.1i ソ

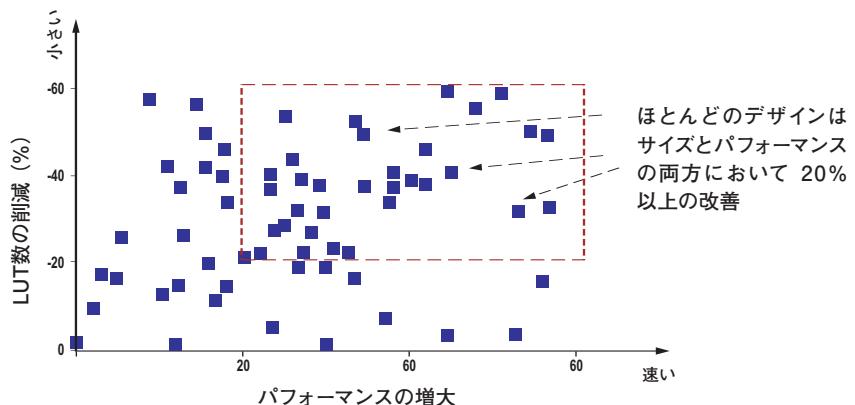

フトウェアを用いてあるカスタマーデザインをインプリメントしてみました。デザインごとに Virtex-4 と Virtex-5 デバイスのインプリメンテーションに使われている LUT の数を比較し、性能改善（メガヘリツ）との相関関係を調べました。図 3 の散布図は、X 軸に性能改善率、Y 軸に LUT 削減によるエリア節約率を示しています。この結果から、新しい 6 入力 LUT ExpressFabric テクノロジは、性能の向上とリソース節約の両方の点でバランスの取れたソリューションであるといえます。

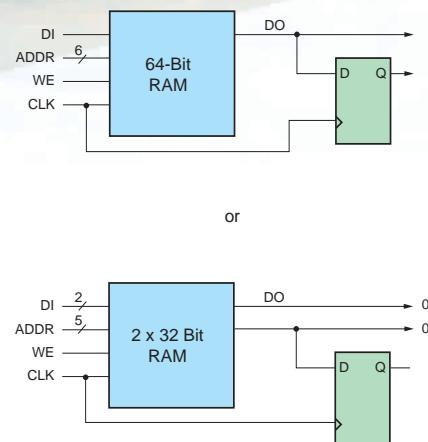

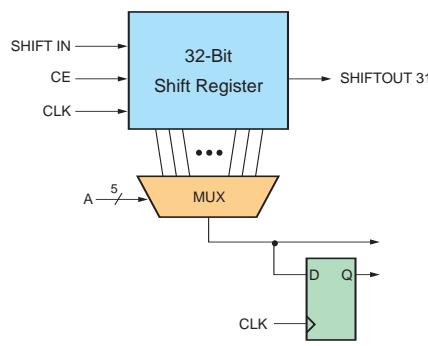

Virtex-5 FPGA は、他社製 FPGA とは異なり、真の 6 入力 LUT を提供しロジックまたは分散メモリとして使用できます。分散メモリとして使う場合、LUT は 64 ビットの分散 RAM (2 ポート、4 ポートも可)、あるいは 32 ビットのプログラマブル シフト レジスタとして使用できます。各 LUT は 2 つの出力を持たせることが可能で、5 つの変数からなる 2 つのロジック ファンクションをインプリメントして 32 X 2 ビットを格納するか、あるいは 16 X 2 ビット シフト レジスタとして機能させることができます。

## 対角方向に対称な新しいインターネット

対角方向に対称な新しいインターネット

図 1 Virtex-5 の ExpressFabric テクノロジ

パターンは、より少ない配線ホップで多くの CLB に到達することが可能で、パフォーマンスの向上を実現します。図 1 は、Virtex-5 および Virtex-4 FPGA のインターフェクト パターン（正方形は CLB を示す）を比較した図です。カラー コードからわかるとおり、Virtex-5 FPGA はパターンが対称的に構成されており、より少ないホップで多くの CLB に到達することができます。配置配線ソフトウェア ツールを使用して、このように良い結果を達成することが可能です。

この機能は Virtex-5 FPGA のユーザーに直接目に見えるものではなく、ISE ソフトウェアによって自動的に処理されます。つまり、簡単な配線で、パフォーマンスの全体的な向上が実現するのです。

## 消費電力を最小限に抑えた先進の FPGA ソリューション

Virtex-5 デバイス ファミリは、11 層の銅配線からなるザイリンクスの先進 65nm トリプル酸化膜 CMOS プロセス技術を採用しています。「トリプル酸化膜」は、厚さの異なる 3 種類のトランジスタ ゲート酸化膜を使用することを意味しています。I/O トランジスタは 3.3V の電圧に耐える必要があるため比較的厚い酸化膜を使いますが、ロジックや他のコア ファンクションに用いられる極めて高速なトランジスタでは非常に薄い酸化膜を使います。

非常に薄い酸化膜と非常に低いスレッショルド電圧では、どうしてもリーク電流が多くなります。

図 2 パフォーマンスとエリアの最適なトレードオフ

つてしまします。FPGA の中には、さほど高速である必要のないトランジスタが多くあります（特にコンフィギュレーション ストレージ セル）。そこでザイリンクスは、Virtex-4 ファミリから、そうしたトランジスタ用に第 3 の中厚酸化膜を採用してきました。トリプル酸化膜の手法により、デバイス回路のパフォーマンスや消費電力を微調整できるようになり、Virtex-5 デバイスではリーク電流とスタティック消費電力を大幅に低減しながら業界最高のパフォーマンスを引き出すことに成功しました。

また、新しい 6 入力 LUT のロジック構造は、LUT あたり従来よりも多くのロジックを組み合わせ、より少ないローカル インターコネクト ノードや、ロジック ファンクション間の高キャパシタンス ノードを使用するため、ロジック数が少なくてすみ、バス遅延が低減されます。さらに、対称型の配線は隣接するロジック間をより直接的に接続するため、これも配線キャパシタンスの低減につながります。

コア電源電圧の VCCINT は 1.0V になりました。これらの要素はいずれも、全体的なダイナミック消費電力の低減に寄与します。ザイリンクスは、多くのエンジニアがパフォーマンスと消費電力をシステム デザインにおける重要な 2 本柱と見ていることを、Virtex-4 ファミリの成功によって熟知しており、高性能と低消費電力の両立が必要であると考えています。

Virtex-5 では、65nm トリプル酸化膜 CMOS プロセスをフルに活用するようロジック ファブリックをリエンジニアリングした結果、システム クロック レートが 550MHz を超える、これまでで最も高性能なファブリックを実現しました。しかも、スタティック消費電力が 90nm の Virtex-4 デバイスと同等のレベルに抑えられ、ダイナミック消費電力は少なくとも 35% 低減されました。Virtex-4 と同様、Virtex-5 ファミリも FPGA ファミリの中で最も消費電力の低いソリューションを提供しているのです。

ループ (PLL) を追加することで、CMT は 2 個のデジタル クロック マネージャ (DCM) と 1 個の PLL から構成されます。したがって、Virtex-5 の CMT は、デジタル クロック マネージャの優れた柔軟性と高精度なインクリメンタル フェーズ シフト、アナログ PLL のジッタ低減という両方の利点を提供します。ファミリ最大のデバイスは、550MHz クロックを生成、操作できる 6 個の CMT を持ち、Virtex-5 のロジックおよびブロック ファンクションのパフォーマンスをサポートします。

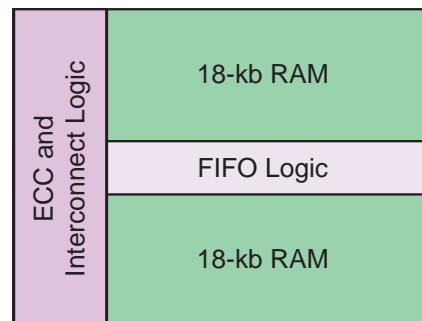

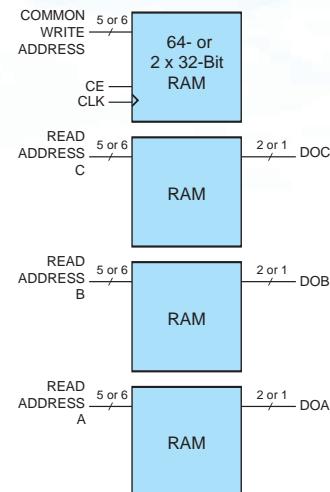

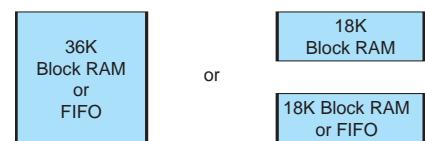

同期デュアル ポート ブロック RAM は重要なファンクションです。各ブロック RAM のサイズは 36Kb に増加されましたが、2 個の独立した 18Kb ブロック RAM として使うことも可能です。データ バス幅は 1 ビットから 36 ビットまでの間でプログラムが可能です。シンプルなデュアル ポート モード（1 ポート書き込み、1 ポート読み出し）の場合、データ バス幅を 72 ビットにすることでデータのバンド幅を 2 倍にすることが可能です。また、未使用の 18Kb ブロックをオフにして、電力を節約することができます。

ブロック RAM には FIFO 制御ロジックが統合されており、ロジック リソースをまったく消費せずに 550MHz で動作する非同期（または同期） FIFO のデザインを容易に作成できます。

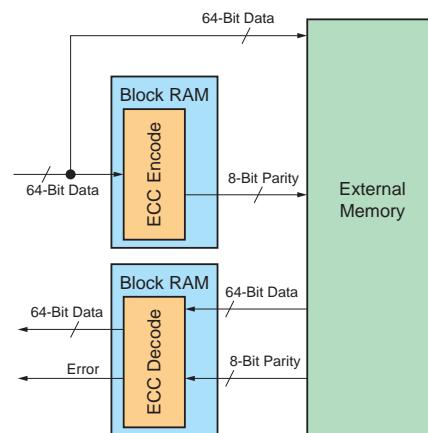

72 ビット幅のブロック RAM には 64 ビットのエラー検出／訂正（ECC）制御ロジックが含まれています。内蔵型の FIFO サポートと同様、内蔵型の ECC はメモリの性能を改善し、従来のファブリック ベースのソリューションに伴うコストを不要にします。また、外部メモリ インターフェイスを補強するため、専用の ECC ロジックを使うこともできます。

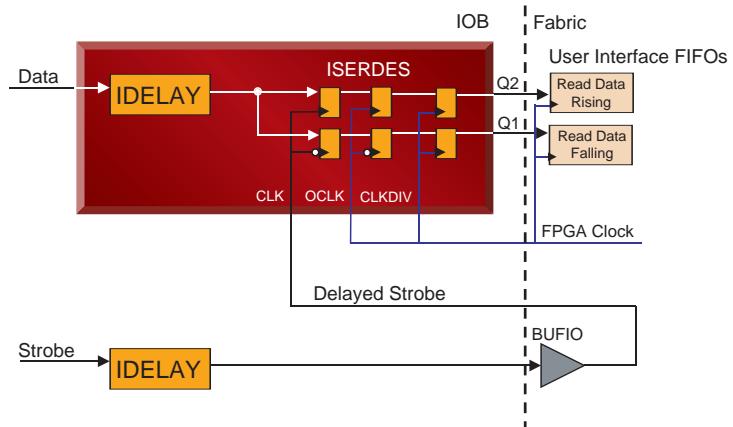

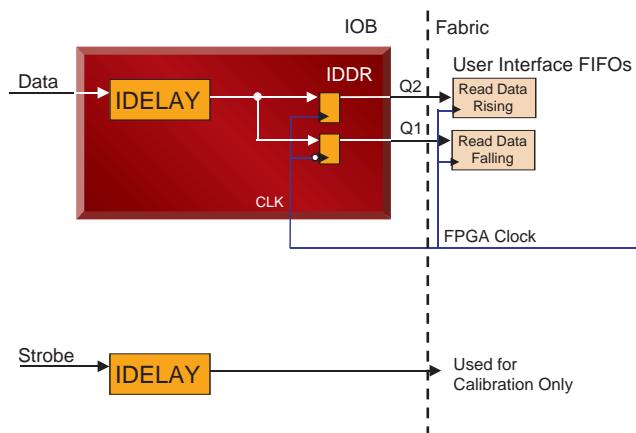

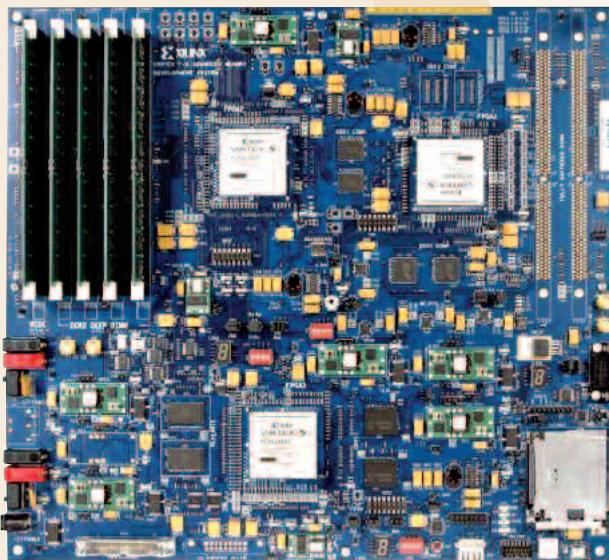

外部デバイスと、DDR や DDR2、QDR II、RLDRAM II といった外部メモリへのインターフェイスは、ザイリンクスの新しい ChipSync™ テクノロジにより格段に向上、簡素化されています。ザイリンクスの LX50T デバイスをベースにしたメモリ開発システム（ML561 開発ボード）には、今日の一般的なメモリ技術に対応したハードウェア実証済みのリファレンス デザインが収められています。

## システム統合のための先進機能

Virtex-5 ファミリでは、各クロック マネジメント タイプ (CMT) にフェーズ ロック

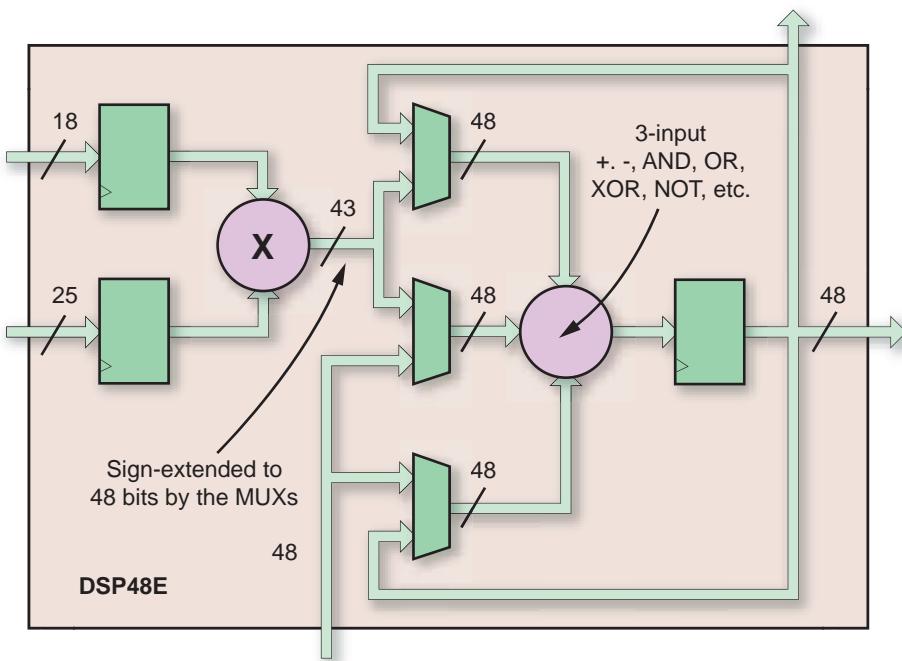

DSP ドメインには、主に浮動小数点のデザイン効率を高めるため、 $25 \times 18$  ビットの乗算器を用意しています。DSP48E スライスは、デジタル フィルタリングやビデオ ブロードキャスト アプリケーションにおける性能を高めるため、直接カスケード接続ができます。直接カスケード接続することで、他社製品と比較して最大 40% の電力節約が実現します。

Virtex-5 の SelectIO™ テクノロジは現在でも業界トップの性能を提供しています。すべてのピンは今日使用されているほとんどの I/O 規格をサポートし、最高 1.25Gbps の LVDS と 800Mbps のシングルエンド I/O パフォーマンスを提供します。

75ps 単位のプログラマブルな入力遅延を提供する IDELAY オプションに加え、新しい ODELAY オプションでは、同様の細かい単位の遅延を FPGA 出力にも実現します。いずれのファンクションも、すべてのデバイス ピン上で個別にプログラムが可能です。

IODELAY ファンクションは、高速なソース同期データやクロックを確実に受け渡すために重要な機能です。アプリケーションとしては、ボード レベルのスキー補正、バス内のビット アライメント、データおよびクロック信号間のアライメントがあります。このファンクションを使うことで、LVDS の I/O は一対のピンあたり最高 1.25Gbps のスピードを達成します。

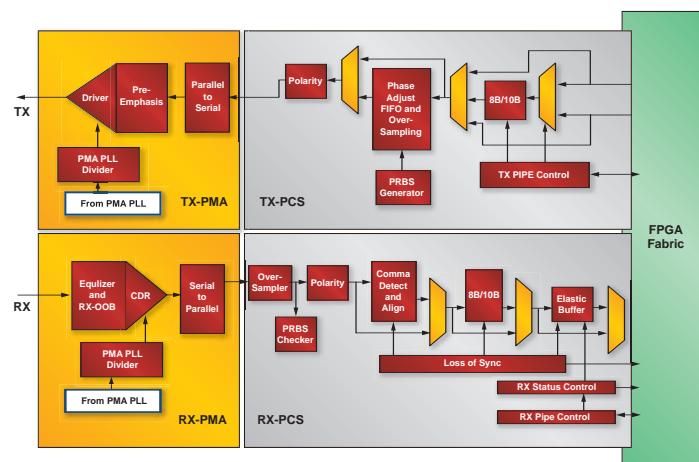

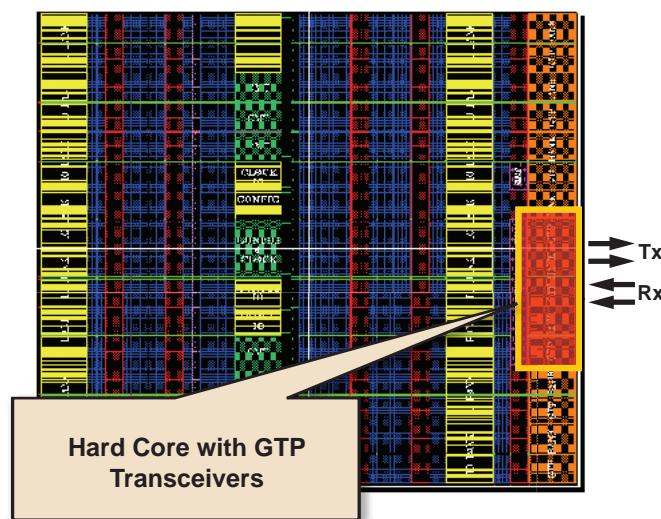

Virtex-5 LXT、SXT、FXT の各デバイスは、エンベデッドシリアルトランシーバを備え、最も大型の LXT デバイスでは最高 24 個を搭載しています。ザイリンクスは、高速シリアルトランシーバの第 4 世代 RocketIO™ テクノロジのデザインにあたり、消費電力の低減に多大な労力を費やしました。最高速度 3.2Gbps を誇る LXT の RocketIO トランシーバは 100mW 未満で動作が可能で、FPGA 製品に搭載されているトランシーバとして最も低い消費電力を実現しています（図 4）。

Virtex-5 LXT の各 RocketIO トランシーバはプログラマブルで、多種多様なスピードとシリアル規格をインプリメントできます。Ethernet、HD/SDI、Serial RapidIO、FibreChannel、Aurora などの規格には、リンク レイヤ IP が利用できます。また、ザイ

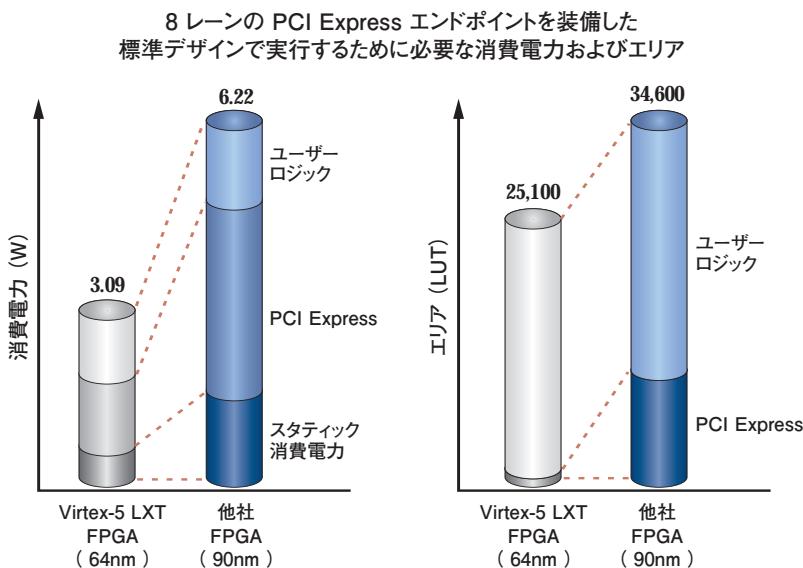

図 3 Virtex-5 FPGA と Virtex-4 FPGA のデザイン ベンチマーク

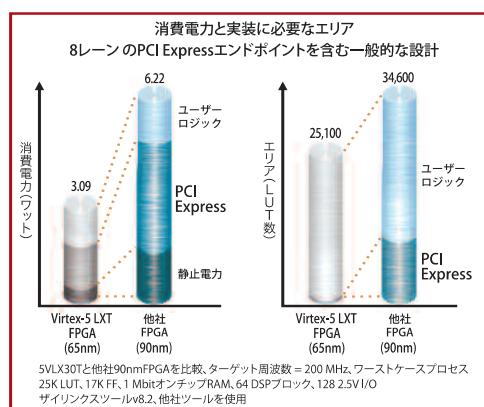

リンクスは、PCI Express® エンドポイント アプリケーションの普及を見込んで、ハード IP として PCI Express エンドポイント プロトコルを内蔵しました。Virtex-5 LXT の PCI Express エンドポイント ブロックは PCI Express 標準仕様バージョン 1.1 にフルに準拠しており、x1、x2、x4、x8 レーンのインプリメンテーションをサポートします。内蔵型のハード IP はロジック リソースを節約し、人気の高まっている PCI Express アプリケーションの性能を改善します。x4 PCI Express レーン インプリメンテーションにおいて、Virtex-5 PCI Express サブシステム ブロックは、ソフト IP でのインプリメンテーションと比較して最大 8,500 LUT を節約します。

Virtex-5 デバイスは、従来と比べて小型の I/O バンクをより多く備えています。外側の I/O バンク

(最も大型のデバイスでは 8 個) も用意されており、PCB の配線が容易になると共に、場合によってはボードのレイヤ数の節約も可能にします。

Virtex-5 デバイスは、すべてにスパース シェブロン ピンアウト スタイルを採用しており、FPGA 業界で最高

の同時スイッチング出力 (SSO) 性能を引き出し、また最高のシグナル インテグリティ (SI) ソリューションを提供します。このピンアウト スタイルは、各 I/O ピンが電源ピンとグランド ピンによって緊密に囲まれ、電流ループのインダクタンスを最小限に抑えて SI を改善します。

## 結論

Virtex-5 デバイスとそのデザイン要素についてご理解いただけたことと思います。この新しいアーキテクチャは、システム エンジニアリングのコミュニティで大変高く評価されています。性能、機能性とも格段に向上した Virtex-5 は、次世代システムに活かされ、複雑なデザイン開発の効率化に大きく貢献することでしょう。

図 4 RocketIO GTP トランシーバ

## Serial Everywhere -The Triple-Play Challenge

# 偏在するシリアル I/O ソリューション -「トリプルプレイ」への挑戦

ザイリンクスはトリプルプレイ競争における次のイノベーションを推進する

Wim Roelandts

CEO and

Chairman of the Board

Xilinx, Inc.

エレクトロニクス業界は、消費者および企業向けに、音声、ビデオ、コンピュータのデータ通信を単一のネットワークで実現したいという飽くなき欲求を満たすため、ソリューションの開発にしのぎを削っており、まさに限界への挑戦を求められています。世界中の放送、通信業界にとって、トリプルプレイは無尽蔵の収益源になりうる半面、フラストレーションの元でもあります。一般ユーザーにトリプルプレイサービスを提供することに成功すれば計り知れない見返りを期待できますが、そこにいたるまでの道のりは遠く、数多くの大きな障害が待ち受けているのです。

中でも最大と思われる障害は、旧来のインフラ機器ではバンド幅の急増に十分対応しきれない点です。本来音声専用だったレガシイインフラストラクチャは、複数のネットワークをクモの巣状に重ね合わせた複雑な形を取っており、サービスプロバイダにとって経済的にも技術的にも負担となっています。つまり、既存の機器のみでトリプルプレイサービスを提供するのは技術的に不可能であり、かといって新しいネットワークに総入れ替えするにはコスト面から非現実的なのです。

さらに、従来のカスタマが既存サービスの中止を受け入れるはずはありませんし、品質の低いサービスに追加料金を払うことも考え

られません。

この巨大なビジネスの食物連鎖を可能にすることで莫大な収益を見込めるところから、エレクトロニクス業界はトリプルプレイの実現に向けてあらゆるレベルでソリューションを発見すべく可能な限りのリソースを結集させてています。当然、半導体業界もシステムメーカーに遅れを取らないよう努力しています。

### キャズム（溝）を超える ザイリンクスの シリアル I/O ソリューション

ザイリンクスは 2002 年、高速シリアルイニシアティブを発表し、Xilinx™ FPGA におけるシリアル I/O ソリューションは格段の進化を遂げました。このイニシアティブの目的は、バンド幅 3.125Gbps～10Gbps、あるいはそれ以上の要件を満たすシステムデザイン向けに新世代のコネクティビティソリューションを提供することで、パラレルから高速シリアル I/O への業界の移行を促すことです。

ザイリンクスは、Virtex-II Pro ファミリへの最大 24 個の 3.125Gbps シリアルトランシーバの追加を皮切りに、多数のシリアル接続規格に適合する IP ソフトコアやリファレンスデザイン、ハードウェア開発プラットフォーム、デザインソフトウェア、特性データ、詳細なデザインサポートプログラムなどを提供してきました。

2005 年には、Virtex-4 FX ファミリに同様の高バンド幅トランシーバを搭載し、622Mbps～6.5Gbps のパフォーマンスや、堅牢な IP とデザインサポートソフトウェ

ア、ハードウェアサービスを提供しました。

Virtex-II Pro および Virtex-4 FX ファミリに高速シリアル I/O ソリューションをパッケージングした主な目的の 1 つは、FPGAユーザーの初期採用企業や革新的企業にカスタム ASIC と ASSP シリアル I/O ソリューションに勝る代替策を用意することでした。

これらの製品ファミリで FPGA ベースのシリアル I/O ソリューションの将来性は実証されたものの、さらなる発展には極めて重要なステップが 1 つ残されていました。キャズム（溝）を超えて大多数の FPGA ユーザーに採用を促し、ザイリンクスのシリアル I/O ソリューションとカスタムソリューションの間に真の等価性を実現するには、完全に検証、統合されたハード IP ベースのターンキーシリアル I/O ソリューションを提供する必要があったのです。

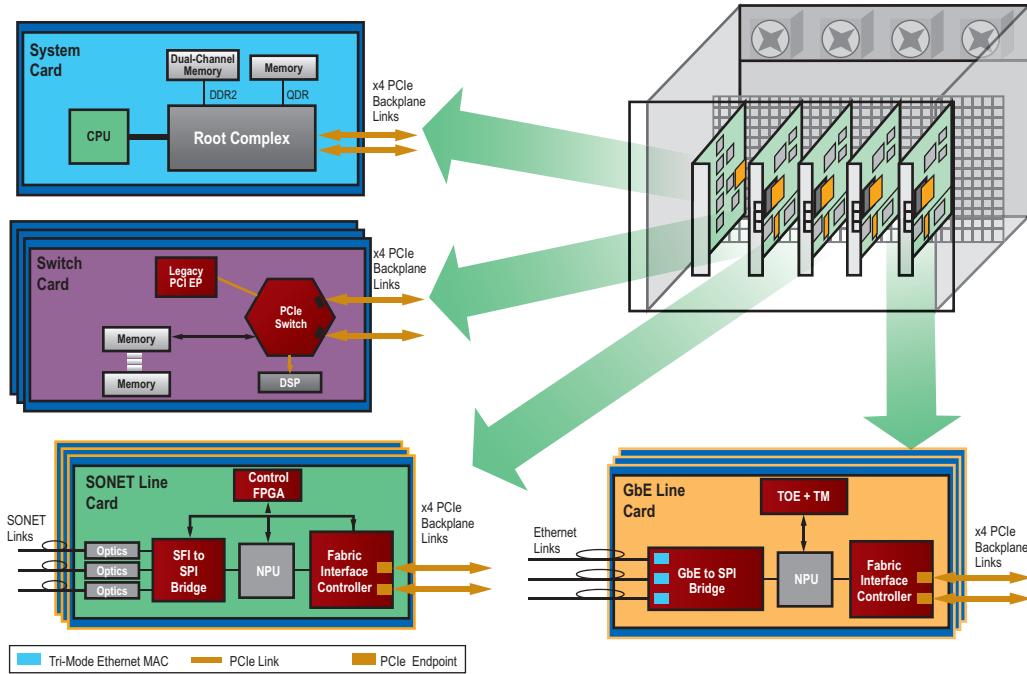

ザイリンクスの最新の 65nm Virtex-5 LXT プラットフォームでは、そのキャズムを超えることができたと確信しています。ハードコード化した PCI Express® エンドポイントとトライモードの Ethernet メディアアクセスコントローラ (MAC) ブロックを搭載する業界初の FPGA を発表したこと、Virtex-5 LXT デバイスはトリプルプレイサービスという新興市場を目指す機器ベンダーのバンド幅、消費電力、コスト面での課題を解消します。Virtex-5 LXT プラットフォームは、プロトコルに完全に準拠した包括的なソリューションを最高の使い勝手で提供することで、幅広いアプリケーションに渡る FPGA 設計者がシリアルコネクティビティを享受できるよう最適化されています。

## Virtex-5 Serial Connectivity Solutions

# Virtex-5 が実現するシリアルコネクティビティ ソリューション

トリプルプレイ市場に向けた柔軟なプロダクト開発が可能に

Sandeep Vij

Vice President,

Worldwide Marketing

Xilinx, Inc.

[sandeep.vij@xilinx.com](mailto:sandeep.vij@xilinx.com)

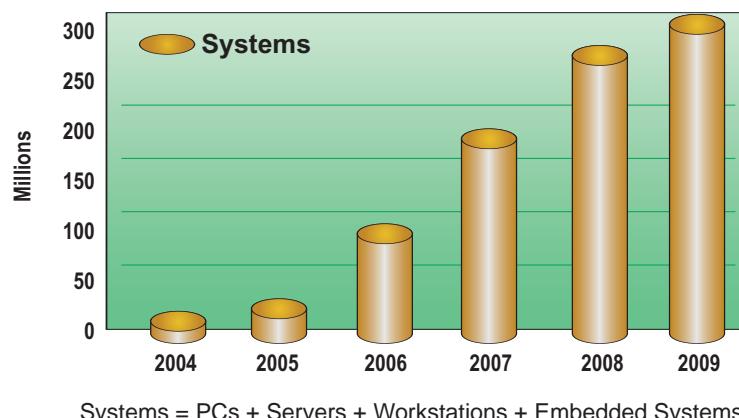

今日「トリプルプレイ」は、半導体業界で最も注目の高いキーワードで成長の牽引役になる可能性を秘めていますが、トリプルプレイの実現に不可欠だったテクノロジの進化やその爆発的成長を支えるさまざまな力、今後表面化する課題、そして、トリプルプレイの製品やサービスを開発・展開するうえでザイリンクスの Virtex™-5 ファミリーが果たす重要な役割について、理解を深めておきましょう。

Virtex-5 プラットフォームは、最新の 2 種類のシリアル I/O 規格であるギガビット Ethernet (GbE) と PCI Express® に対応し高い評価を得ています。この 3 年間で、この 2 種類のインターフェイスがネットワークやコンピューティング アプリケーションの事実上の接続規格になっています。Electronic Trend Publications 社では、2009 年には GbE と PCI Express だけだとポート出荷高の 80% を占めると予測して

います。

### 革新的テクノロジ

テレコム ベンダやサービス プロバイダが Voice over IP、Video over IP、Data over IP (トリプルプレイ) をサポートする All IP ベースのインフラストラクチャへ移行する中、IP がネットワーク市場で最も利用されるプロトコルであることは明らかです。トリプルプレイをサポートするエンド アプリケーションのデザインは、高いパフォーマンスの達成や、QoS (サービス品質) 管理、優れた電力効率が求められるうえ、次々に登場する新しい規格やプロトコルの進化にうまく適応する柔軟性を併せ持つ必要があり、それらは非常に困難です。

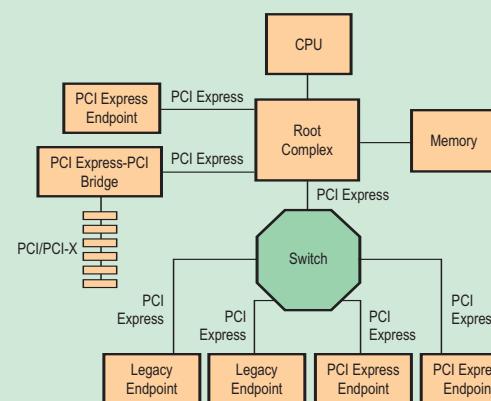

コンピューティング インフラストラクチャ市場では、PCI Express は、従来の PCI バスよりパフォーマンスやスケーラビリティ、信号数の効率面で格段に優れていることから、ネットワーキングやグラフィックス、バックプレーンのコネクティビティに対する独占的なホスト インターフェイスになりました。トリプルプレイ市場のようなネットワークやコンピューティング インフラストラクチャにまたがる製品をデザインするには、この

新分野に精通する必要があり、また、新たなリスクも生じます。ザイリンクスはその対策として、2 年前にプロジェクトを立ち上げ、パフォーマンスや機能性、デバイス集積度を大幅に高めつつ、ゲートあたりのコストを削減する新世代のプラットフォーム FPGA を投入し、デザイン リスクを最小限に抑えることに成功しました。

### 次世代の FPGA

ザイリンクスは、大手 FPGA ベンダとしてのコア コンピタンスを活かし、世界有数のカスタマやパートナーの協力を得ながら Virtex-5 FPGA アーキテクチャを開発しました。LXT ファミリーの投入により、現在の Virtex-5 デバイスはトリプルプレイ市場向けのデザインに理想的なマルチ GbE と PCI Express の統合型コネクティビティ テクノロジを採用しています。

この LXT ファミリーは高速シリアル接続をサポートし、次の機能を備えています。

- GbE MAC を内蔵 – Virtex-5 LXT デバイスは、マルチポートの Ethernet コネクティビティ用に 4 個のハードコア GbE MAC を搭載しています。

- PCI Express ブロックを内蔵 – 1~8つのレーンをサポートし各種標準に準拠する PCI Express エンドポイント ブロックを統合したことで、極めて高いパフォーマンスを要求するアプリケーションに最高 32Gbps の全二重ホスト I/O を提供します。

これらの機能は、リソースの利用率やコネクティビティに関するトラブルシューティング、消費電力の削減、パフォーマンスの最適化に費やす設計者の労力を軽減することから、ユーザーは Virtex-5 FPGA のリソースを存分に活用して、Voice over IP、Video over IP、Data over IP を提供す

るインフラストラクチャやエンド アプリケーションをデザインすることが可能です。

Virtex-5 ファミリはプログラマブル プラットフォームであるため、次のような付加価値の高いトリプレープレイ テクノロジを実現できます。

- QoS – 市場環境に応じて変更できる、階層型サービスを可能にするカスタマ固有のトラフィック マネジメント ソリューション

- デジタル著作権管理 – これら市場の多彩な標準に準拠する、ハードウェア ベースの適応型、エンド ツー エンドのデータ セキュリティを可能にします。

## 結論

柔軟なサービスをいち早く市場に投入することが何よりも重視される非常に変化の速いコンスマーカ市場にあって、企業は、莫大な収益を上げるために、製品とサービスをどのようにミックスすべきかを今なお模索しています。Virtex-5 LXT ファミリは、世界中で評価を得ているプログラマブル ロジック アーキテクチャにエンベデッドシリアル コネクティビティを統合することで、トリプレープレイの新興市場で音声、ビデオ、データを提供するために必要なパフォーマンスや集積度、コネクティビティを提供するものです。

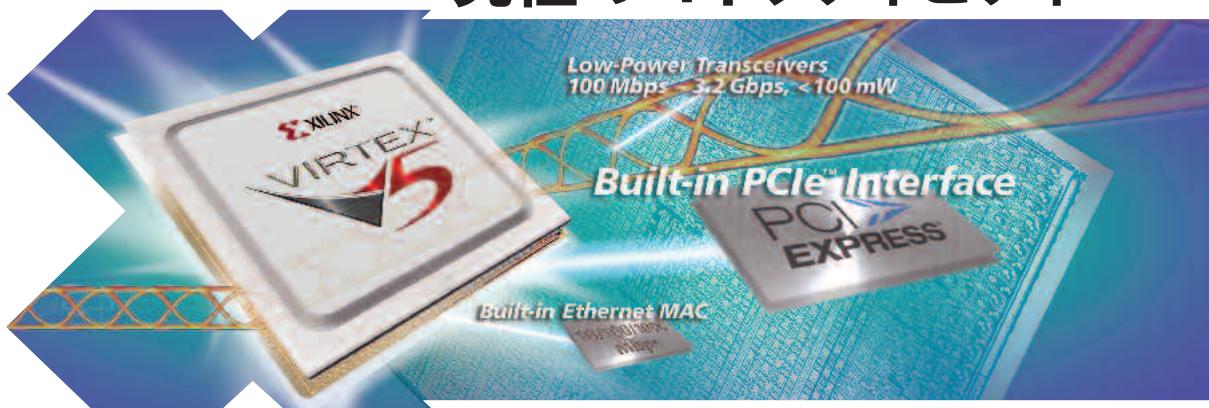

# LOW-POWER TRANSCEIVERS 究極のコネクティビティ…

**VIRTEX™ V5** 世界初の 65nm FPGA で、

シリアル I/O の消費電力、コスト、複雑な

設計を低減します

Virtex-5 LXT FPGA が提供する低消費電力トランシーバ、内蔵PCI Express®およびイーサネットMACブロックの最大24種類のユニークな組み合わせにより、システムの高速動作が可能となります。設計のエキスパートにも初心者にも、ザイリンクスだけが高速シリアル設計を単純化するソリューションを提供することが可能です。

### 最小消費電力、最大エリア効率のシリアルI/Oソリューション

RocketIO™ GTPトランシーバは、最高3.2Gbpsの接続を100mW以下で提供し、困難なパワー/バジェットの達成を可能にします。さらに、組み込みのPCI Expressエンドポイントブロックが、容易な実装、開発期間の削減を確実にします。また、組み込みのUNH認定済みイーサネットMACブロックの実装をシングルチップで可能とします。さらに、開発ツール、デザインキット、IP、キャラクタライゼーションレポートなどお客様の設計をサポートします。

今すぐウェブにアクセスして、究極のコネクティビティに関する詳細をご覧ください。

japan.xilinx.com/virtex5

## 究極のシステム・インテグレーション・プラットフォーム

© 2007, Xilinx, Inc. All rights reserved.ザイリンクスの名称およびロゴ、その他記載のブランド名は米国およびその他各国のザイリンクス社の登録商標または商標です。その他すべての名称は、それぞれの所有者に帰属します。

ザイリンクス社

FPGA内蔵CPU向けデバッガ

# F-Sight

2VP-PPC

MicroBlaze

無償

評価用貸し出し実施中

コンピューテックスでは、より多くの方に

当社製F-Sight(エフサイト)を評価、体験していただくことを目的とした

無償お貸し出しを実施中です。

## FPGAとFPGA内蔵CPUのトータルデバッグ

### FPGA内蔵CPUデバッグ —MicroBlaze・PowerPC—

- ▶ 高級言語レベルデバッグに対応

- ▶ CPU外部フラッシュメモリ対応

- ▶ μITRON対応

- NORTI:ミスボ社製

- PrKERNELv4:イーソル社製

- 組込みLinux対応 (2VP-PPCモデル)

- ▶ 日本語オペレーション

### FPGAの開発時間を 短縮する2つの機能 —FPGAハードウェア・デバッグ—

- ▶ リードバック機能

容易に信号の状態をインスペクト表示。

- ▶ プロービング機能

波形観測したい信号をソース・ファイル上で登録可能。

### FPGAとCPUの 協調デバッグ機能

#### ▶ 協調デバッグ

FPGAハードウェア・デバッグとCPUソフトウェア・デバッグを同時に実行可能。

※現在、2VP-PPCモデルでのみサポート

**Computex®**

株式会社コンピューテックス

お問い合わせ先→営業部・TEL:03-3253-2901 FAX:03-3253-2902

<http://www.computex.co.jp>

上記URLより製品情報、最新情報、リリース予定、サポート情報、各種ダウンロードなどのホットな情報を御覧いただけます。 記載の会社名および商品・製品名は各社の商標または登録商標です。

# Achieve Higher Performance with Virtex-5 FPGAs

# Virtex-5 FPGA を使って システム レベルの性能を向上

新しい ExpressFabric™ テクノロジによる高パフォーマンスの達成

Adrian Cosoroaba

Marketing Manager

Xilinx, Inc.

adrian.cosoroaba@xilinx.com

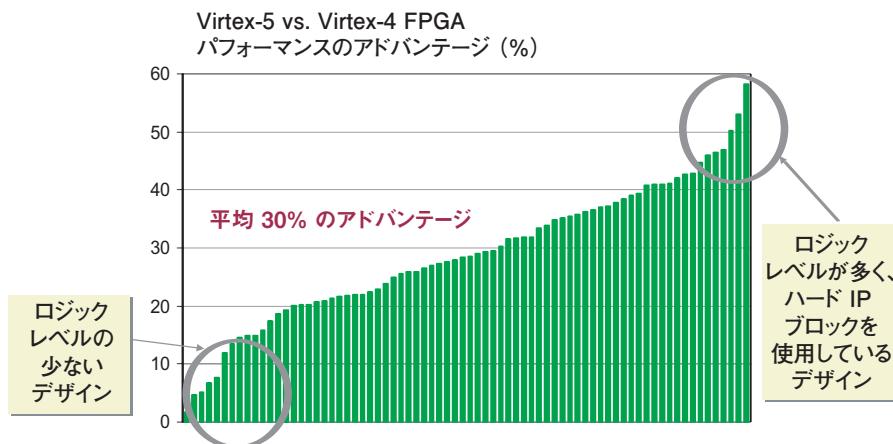

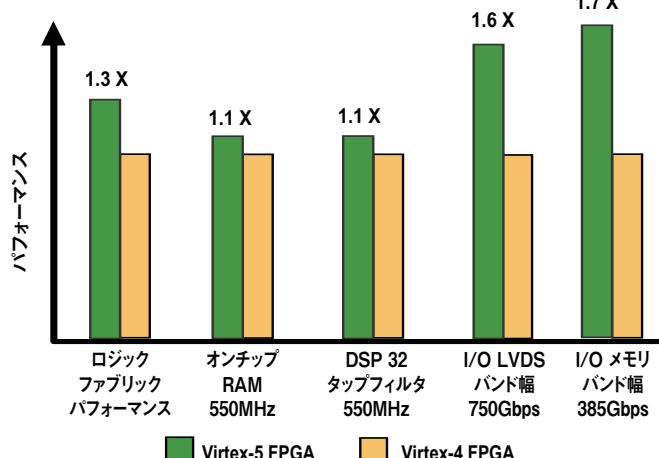

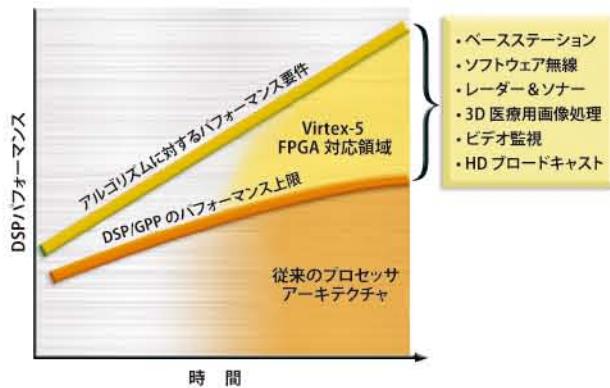

FPGA システムのデザイン性能を最大限に高めるには、ロジック ファブリック、オンチップ メモリ、DSP、I/O バンド幅といった性能効率の高いコンポーネントをバランス良くミックスする必要があります。本稿では、Virtex™ -5 FPGA のビルディング ブロック、特に新しい ExpressFabric™ テクノロジを利用してシステム レベルの性能を高める方法について説明します。ロジックおよび数値演算ファンクションの性能がどれだけ改善されるかを具体的に定量化した例を挙げながら、ExpressFabric アーキテクチャの代表的な機能を掘り下げて解説します。実際のカスタマ デザインで行ったベンチマークから、Virtex-5 の ExpressFabric テクノロジが、旧世代の Virtex-4 FPGA と比較して平均 30% の性能改善を実現することがわかります。

Virtex-5 FPGA は、カウンタや加算器、RAM/ROM ストレージなどのファンクションがインプリメント可能な新しいロジック ファブリックに加え、ハード IP ブロックやメモリ、550MHz の高速クロック レートで動作するよう最適化された DSP を搭載し、高性能デザインに最適なプラットフォームです。

## ExpressFabric の性能

1980 年代に最初の FPGA が発表されて以来、ほとんどの FPGA 向けロジック ファブリックは当時と同じタイプの 4 入力ルックアップ テーブル (LUT) アーキテクチャをベースにしてきました。Virtex-5 ファミリは、入力を共有せずに完全に独立させた真の 6 入力 LUT ファブリックを備える初の FPGA プラットフォームです (図 1)。6 入力 LUT のファブリック アーキテクチャに移行することで、65nm の Virtex-5 FPGA ファミリは、ロジック ファブリックの性能を決定付けるクリティカル パスの遅延とダイサイズの最も効果的なトレードオフを達成しています。

プロセス技術の進化により、インターネットのタイミング遅延がクリティカル パス遅延の 50% 以上を占めることができます。そこでザイリンクスは、より少ない配線ホップでより多くの CLB に到達できるようになります。さらなるパフォーマンスの向上を実現すべく、Virtex-5 FPGA に新しいインターネット パターンを開発しました。この新しいインターネット パターンは、2~3 ホップ以内でより多くのロジックの接続を可能にします。さらに、配線パターンがより規則的になるため、ザイリンクスの ISE™ ソフトウェアが最適なルートを見つけるのが容易になります。インターネットの機能はすべて FPGA 設計者には目に見えるものではなく ISE ソフトウェアにて

自動的に実行されるのですが、全体的なパフォーマンスの向上が実現し、デザインの配線が容易になります。Virtex-5 のパターンは、基本的に距離に基づく高速かつ予測可能な配線を実現します。

新しい 6 入力 LUT 構造やキャリー チェーン、専用マルチブレクサ、フリップ フロップなどの特別なファンクションに加え、これらエレメントを接続するザイリンクス独自の方法によって、ロジックおよび数値演算ファンクションをインプリメントする際のパフォーマンスや効率が飛躍的に向上しました。

ExpressFabric テクノロジのメリットを具体的に示す 1 つの例として、マルチブレクサ (MUX) があります。Virtex-4 アーキテクチャで 4:1 の MUX をインプリメントするには、2 個の 4 入力 LUT と 1 個の MUXF ブロックが必要です。Virtex-5 デバイスでは、同じ 4:1 MUX を 1 個の LUT でインプリメントすることが可能です。同様に、Virtex-4 FPGA では、8:1 MUX をインプリメントするのに 4 個の LUT と 3 個の MUXF ブロックが必要でしたが、Virtex-5 アーキテクチャでは 2 個の 6 入力 LUT だけですみます。この結果、パフォーマンスやロジックの使用率が改善されます (図 2)。

ザイリンクスの旧世代の FPGA ファミリと同じく、Virtex-5 の Slice L (ロジックスライス) は、ロジック ファンクション、レジスタ、専用キャリー チェーンを用いた数値演算ファンクションをインプリメントでき

ます。若干複雑な Slice M（メモリスライス）には、LUT（SRL）内に分散 RAM とシフトレジスタをインプリメントする機能が加えられています。

ExpressFabric アーキテクチャによってさまざまな改善が行われていますが、キャリアーチェーン構造は、数値演算のインプリメントに使用した場合格段のパフォーマンス向上を実現します。特にクリティカルパスの遅延に与える効果は、表 1 の例で示す通りです。

LUT 構造の大型化は、LUT RAM や LUT ROM などの分散メモリファンクションにもメリットがあります。新しく採用されたアスペクト比により、小型のメモリファンクションをいっそう高密度でパッキングすることが可能で、パフォーマンスの大幅な改善につながります（表 2）。

6 入力 LUT アーキテクチャとインターフェクト構造によるロジックファブリックの改善は飛躍的なパフォーマンス向上を約束しますが、これはほんの序章にすぎません。ほとんどのアプリケーションは、LUT ベースの RAM では用意しきれないほど大量のオンチップ RAM を必要とします。Virtex-5 ではブロック RAM を強化したこと、オンチップメモリのパフォーマンスをいっそう改善できるのです。

## ブロック RAM の性能

65nmへの移行に伴い、Virtex-5 のブロック RAM はクロック速度が 10% 向上し、550MHz となりました。しかし、今日のアプリケーションに求められるパフォーマンスを達成するには、ブロック RAM は高

図 1 2 つのスライスから構成される Virtex-5 のコンフィギュアブルロジックブロック（CLB）。各スライスは、ロジックレベルを低減が可能な 4 個の 6 入力 LUT を使用

図 2 Virtex-5 FPGA と Virtex-4 FPGA にインプリメントされている 8:1 マルチプレクサ

| 8:1 マルチプレクサ | Virtex-4 | Virtex-5 | 改善率  |

|-------------|----------|----------|------|

| ロジックレベル     | 2        | 1        | 100% |

| バス遅延        | 1.33 ns  | 1.08 ns  | 23%  |

表 1 Virtex-5 FPGA と Virtex-4 FPGA にインプリメントされている数値演算機能

| 機能              | Virtex-4 FPGA<br>バス遅延 | Virtex-5 FPGA<br>バス遅延 | 改善率 |

|-----------------|-----------------------|-----------------------|-----|

| 64 ビット加算器       | 3.5ns                 | 2.4ns                 | 46% |

| 64 ビット三M元加算器    | 4.3ns                 | 3.0ns                 | 40% |

| 32 ビットバーレルシフタ   | 3.8ns                 | 2.8ns                 | 37% |

| 48 ビットマグニチュード比較 | 2.4ns                 | 1.8ns                 | 34% |

表 2 Virtex-5 FPGA と Virtex-4 FPGA における LUT ベースの RAM/ROM インプリメンテーション

| 機能               |         | Virtex-4 | Virtex-5 | 改善率  |

|------------------|---------|----------|----------|------|

| LUT RAM 64 X 1   | ロジックレベル | 2        | 1        | 100% |

|                  | バス遅延    | 1.76ns   | 1.26ns   | 40%  |

| LUT ROM 128 X 12 | ロジックレベル | 3        | 1        | 200% |

|                  | バス遅延    | 1.84ns   | 1.20ns   | 53%  |

速化だけでなく、さらなる大容量化の実現も求められます。

Virtex-5 のブロック RAM は、36Kb (2 個の 18Kb メモリから構成) に倍増されました。この大型なブロック サイズは、シンプルなデュアル ポート モードで 72 ビットのデータ ワードをサポートし、ブロック RAM のバンド幅を 2 倍にします。さらに、Virtex-5 FPGA は専用のコネクションを持ち、ブロック RAM のカラムの 2 個の隣接する 36Kb ブロック RAM をカスケード接続して、最高 550MHz で動作する 72Kb メモリをインプリメントすることができます。

FPGA の大規模化に伴い、1 個のデバイスにより多くのサブシステムを統合する傾向

が強まり、複数クロック ドメインへのインターフェイスの必要性がますます一般化してきました。Virtex-5 デバイスは、統合型のロジックを提供して、柔軟かつ効率的な FIFO のインプリメンテーションができるだけ簡素化することで、このニーズに応えています。

こうした数々の機能拡張を通して、Virtex-5 のブロック RAM はより多くのオンチップ メモリ、構築しやすい FIFO、より高いバンド幅を実現しています。

## DSP の性能

高性能 DSP のアプリケーションに適したソリューションとして、FPGA の普及が進んでいるのはごく自然なことです。コプロ

セッサとして、あるいは要求の厳しいアプリケーション向けのスタンドアロン ソリューションとして、FPGA はパフォーマンスや消費電力、コストのバランスが最も優れたプラットフォームです。

DSP のパフォーマンスに対する飽くなき要求に応えるべく、ザイリンクスの Virtex-5 DSP はクロック レートと精度の両方の点で業界トップを独走しています。クロック レートは 550MHz まで高速化され、精度も 18 X 18 ビットから 25 X 18 ビットに改善されています。

また、加算器チェーンのインプリメンテーション用に Virtex-5 の DSP48 スライスを最適化しました。これは非常に効率的な高性能フィルタを作成できるパワフルな機能です。各 DSP48 スライス上の入力と出力にある専用の配線リソースを使用すると、1 つのカラム内でスライスをいくつでも連結することが可能です。このように専用の配線を設けたことで、チェーン内のすべての DSP48 スライスは、他社の FPGA のようにファブリックの配線やロジック リソースをいつさい使うことなくフル スピードで動作することが可能です。こうした一連の改善により、一般的な高精度ファンクションのインプリメントに必要なリソース数は約半分ですみます。たとえば、35 X 25 ビットの乗算の場合、Virtex-4 FPGA では 4 つの DSP48 スライスが必要です。Virtex-5 FPGA では、搭載されているよりワイドな DSP ブロックにより、同等の乗算ファンクションのインプリメントには半分のスライスですみます。

## I/O バンド幅の性能

パフォーマンス ベンチマークの場合、FPGA のデータ処理速度は、デバイスの I/O バンド幅、つまり大量のデータをデバイスとの間でやり取りするスピードだけで決定されます。外部のメモリ バッファを使う場合、データを FPGA から書き出してから再度 FPGA に読み戻す必要があるため、インターフェイスはデータ処理速度より少なくとも 2 倍高速である必要があります。

Virtex-5 FPGA は、ピンあたりのデータ

図 3 ISE 8.2i ソフトウェアを用いてインプリメントした 74 種類のカスタマ デザインに基づく比較

図 4 Virtex-5 FPGA のパフォーマンス改善

レートと、より大型化されたパッケージでのI/O 数を両方増やすことで、Virtex-4 のバンド幅をさらに改善しています。たとえば、DDR2 SDRAMなどの一般的なメモリインターフェイスについては、ピンあたりのバンド幅が 534Mbps から 667Mbps に増え、データ I/O の数も SSO の要件を考慮すると 432 個から 576 個に増加しました。

## カスタマ デザインのベンチマーク

Virtex-5 FPGA のロジック ファブリックが実現する性能向上をさらに詳しく評価するため、ザイリンクスの ISE ソフトウェアを用いてカスタマ デザインをインプリメン

トしました。

デザインはすべて VHDL または Verilog で書かれました。メモリや FIFO など、いくつか特定のデザイン ユニットについてはライブラリ コンポーネントの直接的なインスタンシエーションや合成推論を用いてインプリメン

トしましたが、多くは ISE ソフト

ウェアの一部である CORE Generator™ ソフトウェアによって生成された EDIF ブロックを用いてインプリメントしました。

このベンチマークについては、パフォーマンスを効果的に測定するため、現実に即したタイトな制約を使用して、Synplicity 社の Synplify Pro でタイミング ドリブンな手法で合成を実行しました。これは、特別な最適化とロジック複製が採用されていることを確認することを目的としたためです。

ISE ソフトウェアでのインプリメンテーションは、配置配線に非常に手間がかかりました。デザインがそのデザインの制約を満たせなくなるまで、クロックを 5% ずつ段階的にタイトにしていきました。

この結果、図 3 に示すとおり、Virtex-4 FPGA にインプリメントしたデザインと比較して平均 30% のパフォーマンス向上を達成しました。

最も改善率の高かったのは、大型のロジック コーンを持つデザインでした。クリティカル パスは、大型で一般的に複雑なロジック

をインプリメントします。たとえば、ASIC プロトタイプ デザインのクリティカル パスには、大量のロジックに対して一般的にごくわずかなレジスタしかありません。このようなデザインは、Virtex-5 の ExpressFabric テクノロジにより大幅に改善されます。

さほど大幅に改善されないデザインは、ロジック レベルが少ないか、もしくはハード IP ブロックやキャリー チェーン構造を使用してもパフォーマンスを改善できる見込みがほとんどないものです。

図 4 は、旧世代の Virtex-4 FPGA と比べて Virtex-5 FPGA の性能がどう改善されたかをカテゴリ別に示します。

## 結論

新たに ExpressFabric テクノロジを採用し、他の高性能なハード IP ブロックと I/O に密接に結合した Virtex-5 FPGA ファミリは、前世代のアーキテクチャと比較して性能が大幅に改善されています。

# ザイリンクス トレーニング スケジュール 【3~4月】

5~6月のスケジュールは18ページをご覧ください。

ザイリンクスでは、大規模、高速 FPGA を対象にした FPGA 設計のための各種トレーニングを各地で開催しております。是非ご利用ください。

| コース名                               | 日 程 |                     | 主 催          | 開 催 地   |

|------------------------------------|-----|---------------------|--------------|---------|

| FPGA 設計実践                          | 3月  | 6 日 (火) ~ 7 日 (水)   | ザイリンクス       | 東京 品川会場 |

|                                    | 3月  | 22 日 (水) ~ 23 日 (金) | ザイリンクス       | 東京 品川会場 |

|                                    | 3月  | 22 日 (木) ~ 23 日 (金) | 新光商事         | 大阪会場    |

|                                    | 4月  | 12 日 (木) ~ 13 日 (金) | 菱洋エレクトロ      | 大阪会場    |

|                                    | 4月  | 17 日 (火) ~ 18 日 (水) | ザイリンクス       | 東京 品川会場 |

|                                    | 4月  | 19 日 (木) ~ 20 日 (金) | 東京エレクトロンデバイス | 大阪会場    |

| アドバンスド FPGA 設計                     | 4月  | 10 日 (火) ~ 11 日 (水) | ザイリンクス       | 東京 品川会場 |

|                                    | 3月  | 27 日 (火) ~ 28 日 (水) | ザイリンクス       | 東京 品川会場 |

|                                    | 4月  | 24 日 (火) ~ 25 日 (水) | ザイリンクス       | 東京 品川会場 |

| エンベデッド システム開発                      | 3月  | 14 日 (水) ~ 15 日 (木) | ザイリンクス       | 東京 品川会場 |

|                                    | 3月  | 19 日 (月) ~ 20 日 (火) | ザイリンクス       | 東京 品川会場 |

|                                    | 4月  | 18 日 (水) ~ 19 日 (木) | 新光商事         | 大阪会場    |

|                                    | 4月  | 19 日 (木) ~ 20 日 (金) | ザイリンクス       | 東京 品川会場 |

| System Generator を使用した DSP デザインフロー | 3月  | 28 日 (水) ~ 29 日 (木) | ザイリンクス       | 東京 品川会場 |

|                                    | 4月  | 26 日 (木) ~ 27 日 (金) | ザイリンクス       | 東京 品川会場 |

| MGT シリアル I/O デザイン                  | 3月  | 15 日 (木) ~ 16 日 (金) | ザイリンクス       | 東京 品川会場 |

|                                    | 4月  | 12 日 (木) ~ 13 日 (金) | ザイリンクス       | 東京 品川会場 |

| シグナル インテグリティと基板設計の基礎               | 3月  | 13 日 (火) ~ 14 日 (水) | ザイリンクス       | 東京 品川会場 |

\*すべてのトレーニングは、ザイリンクス認定インストラクターによるオフィシャルトレーニングです。

\*日程および会場は、都合により変更となる場合もございます。最新情報はザイリンクストレーニングWebサイトをご覧ください。

詳細とご登録はこちらから ▶▶ <http://japan.xilinx.com/support/education-home.htm>

# HDL Coding and Design Practices for Improving Virtex-5 Utilization, Performance, and Power

# Virtex-5 の使用率や パフォーマンス、消費電力を 最適化するための HDL の コーディング & 設計手法

## Virtex-5 でよりよくデザインするための Tips & テクニック

Brian Philofsky

Staff Software Technical Marketing Manager

Xilinx, Inc.

brian.philofsky@xilinx.com

FPGA は、以前からデジタル ロジックを対象とした多様な HDL コーディングやデザイン スタイルを柔軟に受け入れてきました。ザイリンクスの Virtex™-5 デバイスも例外ではありません。Virtex-5 FPGA は、さまざまな手法で書かれた多種多様なデザインを受け入れることができますが、ここで推奨するストラクチャやテクニックを使うことにより、エリア、パフォーマンス、そして消費電力をいっそう最適化することが可能です。

### ターゲットのアーキテクチャと合成ツールを知る

プロジェクトを始める際は、最初にターゲットとなるデバイスのアーキテクチャを理解する必要があります。Virtex-5 FPGA を使用する場合は、コードの 1 行目を書き始める前に、「Virtex-5 User Guide ( <http://japan.xilinx.com/userguides/ug190.pdf> )」

をお読みください。最終的にどのような基本ハードウェアを構築するかについて理解とビジョンを深めておくことにより、デザインやコーディング上の大小さまざまな決定を自信をもって下すことができます。

たとえば、ISERDES 内の Bitslip テクノロジを使って入力データを取り込む回路を組めば、類似の回路を記述してビルドするよりはるかに設計時間や作業量、そしてリソースを節約することができます。

また、DSP48E の構造や機能を理解していると、パイプライン レジスタをいつどこに配置すればよいか、適切な判断を下すことができます。拡張された乗算器やポスト加算器など専用の機能も、エリアやパフォーマンス、消費電力を改善するために役立ちます。

同様に、合成ツールで何ができる、何ができないかを知つければ、的確なプリミティブに置き換えるコーディング スタイルに役立つだけでなく、コンポーネントがどのようにインスタンシエートされるかを適切に判断できます。使用する合成ツールの推奨コーディング スタイルを知るためにも、プロジェクトの開始前に合成ツールのマニュアルやアプリケーション ノート、その他の関連資料に

目を通してください。

また、合成ツールや ISE™ ツールの最新版へのアップデートも行ってください。従来の合成ツールでも Virtex-5 アーキテクチャはサポートされますが、最新のリリースでは最適化がよりいっそう改善されています。ソフトウェアの最新版をインストールすることは、エリアやパフォーマンス、消費電力をより最適化したデザインにするための 1 つの簡単な手段でもあります。

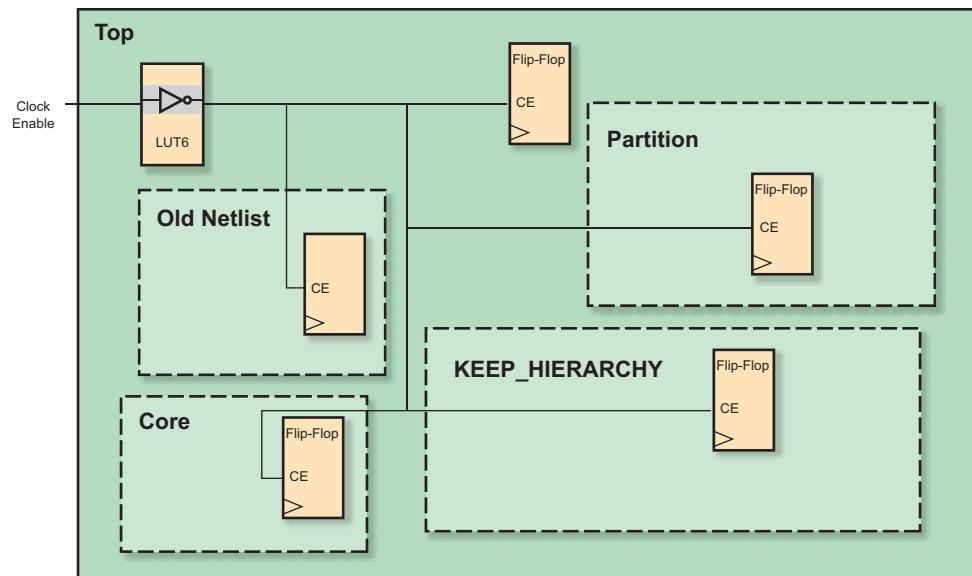

### 制御信号の極性

Virtex-5 アーキテクチャでは、制御信号の異なる極性をサポートします（クロックイネーブル、リセット、セット）。ただし、デザインを最適にするには、常にアクティブ high の制御信号を使うことを推奨します。Virtex-5 のスライス制御ロジックはアクティブ high で、コードに同じように記述しておくことにより、単純な信号反転のために追加の LUT リソースを使う必要がなくなるからです。

信号が外部ピンから送られアクティブ low の極性を必要とする場合は、トップレベル コードの信号を反転させて、その信号を必要と

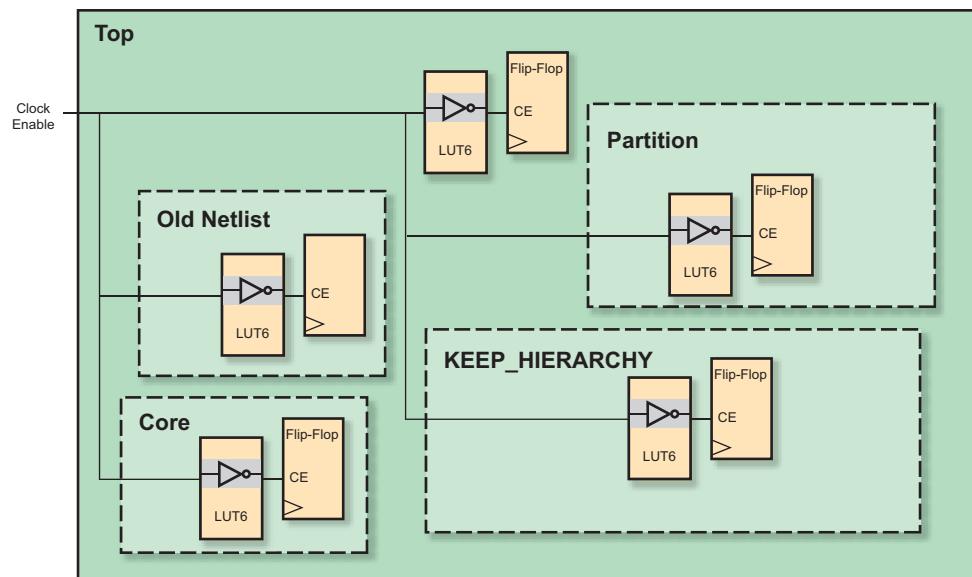

するすべてのプロセスとサブモジュールに正の極性を使ってください。これは、複数のコアを持っているデザインや、ボトムアップの合成テクニックを使っているもの、KEEP\_HIERARCHY の制約を持っているもの、パーティションを採用しているデザインには不可欠です（図 2）。

この種のデザインでは、制御信号の反転という目的だけでコアやネットリスト、階層、パーティションあたりに追加の LUT を使用しがちで、余分な LUT リソースを費やすことになるばかりか、パフォーマンスやスライスパッキングにマイナスの影響を与えることがあるからです。

一般に、セット、リセット、イネーブルは、必ずアクティブ high (ロジック 1 でアクティベート) の極性を用いてコーディングしてください。

## リセットの使用

デザインを初期化するには、ソース HDL コードにグローバルな非同期リセットを使うのが一般的です。しかし、その場合の多くは、追加のリソースを消費することになります。非同期ではなく、ローカルで同期リセットを組むと良いでしょう。デザインのうち、定期的にリセットを必要としない部分には、同期セット／リセットロジックを記述してください。このような部分については、HDL コードに registerd として定義された信号を宣言することで（たとえば、Verilog で reg、あるいは VHDL で信号を定義するとき）初期化することができます。この方法を使うことにより、パッキング密度が改善され、タイミング解析が容易になると同時にパフォーマンスの向上、エリアリソースの改善が行えます。

FPGA の特性として、コードにグローバルリセットを記述しなければ、コンフィギュレーションサイクルの完了時に GSR（グローバルセット／リセット）が起こり、すべてのレジスタを既知の指定値に初期化します。これと同様のサイクルは、FPGA の場合と同一の既知の初期値を与えることで、ゲートレベルのシミュレーションネットリストにシミュレートできます。

RTL レベルのシミュレーションに関しては、コードでレジスタを初期化することで、適切な RTL またはビヘイビアシミュレーションを行うことができます。この初期化は合成ツールにより抽出され、インプリメントしたデザインに適用されます。したがって、どの段階のシミュレーションでもグローバルリセットは冗長であるため、必要ありません。

タイミング制約が正しく満たされていれば、その同期信号は自動的に解析されその動作が確定されるため、同期式では同期リセットを使用することで、リセットのアサート時

あるいはリリース時に回路がどのような状態となるかを正しく予測することが可能です。このように、グローバルでない同期リセットを用いることで、ロジックの最適化やパフォーマンスのさらなる改善が実現できるのです。

同期制御信号を使う場合、ロジックファンクションの一部をフリップフロップの同期セットまたは同期リセットで実現することができるですが、これは非同期信号では不可能です。必要な部分だけにリセットを記述することで、合成ツールは、インプリメンテーショ

図 2 クロック イネーブルの極性がデザイン内の LUT 使用率に与える影響

ンに SRL (シフト レジスタ LUT) や、分散 RAM (LUT ベースの RAM) メモリ、ブロック RAM といった代替リソースを選択することができます。これも非同期信号では不可能、もしくは不適切です。合成ツールは、記述されたコードに対して最良のリソースを選択する非常に柔軟なツールなのです。

## パイプライン化

従来の FPGA と同様、パフォーマンスを最大限に引き出し消費電力を最小限に抑えるには、デザインを正しくパイプライン化することが必要です。Virtex-5 アーキテクチャの発表に伴い、新しいロジック構造では、パイプライン化のタイミングや方法について若干異なるルールを定めています。

Virtex-5 デバイスは、従来の FPGA ファミリに採用されていた 4 入力 LUT ではなく、より高度な 6 入力 LUT を備え、最高のパフォーマンスを維持しながらパイプライン レジスタ間によりワイドなロジック ファンクションをインプリメントできるようになっています。レジスタ間にあるロジック ファンクションをHDL コーディングする際、ロジック ファンクションに 6 つの入力を持たせた場合に最適なパイプライン化と LUT のリソース管理が実現できます。これは必ず覚えておいてください。

しかし、特定のロジック ファンクションにちょうど 6 つの入力を持たせるのが実用的ではない、あるいは不可能な場合でも、よりワイドな入力の 6 入力 LUT は、ロジックの段数が低減され、より少ないパイプラインステージで実現できるため、従来の FPGA アーキテクチャと同等、もしくはそれ以上のパフォーマンスを達成できる良好なパフォーマンスを引き出すことができるようになっているのです。

目標としては、I/O やレジスタ、同期ブロック（ブロック RAM や DSP48E）間のロジック ファンクションへの入力数は 10 本未満とすることを推奨します。こうすることで、ロジック ファンクションは一般には 2 段のロジック レベルとなります。このことから、高パフォーマンスや低消費電力の達成を目的として、デザイン パスに 10 本以上

の多くの入力を必要とする場合でも、そのレイテンシを満たすために可能な範囲でそのロジック ファンクションへの入力を減らしてみると良いでしょう。

## メモリのコーディング

Virtex-5 アーキテクチャに採用した多数の技術革新のうち、ブロック RAM メモリと分散 RAM メモリは、その容量と機能性がいっそう拡張されています。これら貴重なリソースを最大限活用するには、デザイン プロセスの初期段階やコーディング中に、さまざまな決定を下す必要があります。

一般的なガイドラインとして、容易なコード変更、高速なシミュレーション、移植の容易なコードを実現するには、どの種類の RAM が選択されるかを予想しておいてください。また、ビヘイビア モデルで RAM を記述するような場合でも、いくつかの重要な点を頭に入れておく必要があります。まず、RAM の容量について考慮してください。Virtex-5 デバイスでは、ブロック RAM の基本メモリ ブロックが 36Kb のメモリ ストレージ スペースに増加されています。このブロックは、よりワイドで浅い 512 X 72、より深いシングル ビットの 32 Kb X 1、あるいはその中間のコンフィギュレーションに変更できます。また、2 つの 36Kb RAM をカスケード接続して 64Kb X 1 のコンフィギュレーションにしたり、36Kb RAM を 2 つの別々の 18Kb RAM に分割して 512 X 36 ~ 16Kb X 1 のさまざまなコンフィギュレーションにしたりすることも可能です。

分散 RAM は大型になった LUT 構造により、エリアやパフォーマンスを犠牲にすることなく 64 ビットの深さを効率的に実現できるようになりました。Virtex-5 デバイスでは、このタイプの RAM には 64 ビットが最も適したサイズですが、他のサイズにすることも可能です。デバイス内の限られた RAM リソースを最も効率良く使い、最高のパフォーマンスを達成するためには、最適なメモリを選択し、コーディングの際に RAM の基本サイズを覚えておくことが大切です。

ブロック RAM や分散 RAM には他にも機能を提供しますが、これらの機能を利用するにはコーディングやデザインにそれぞれ異なるアプローチが必要です。パフォーマンスについては、出力レジスタを正しく使用することが最も重要でしょう。ブロック RAM については、できるだけブロック RAM の出力レジスタをイネーブルことです。出力レジスタをイネーブルすることで、RAM からの clock-to-out (クロックから出力まで) が低減され、RAM から出力されるデータのタイミングが改善されます。ただし、読み込み中に別途クロック サイクルのレイテンシが追加されることを考慮に入れる必要があります。

同様に、分散 RAM を使う際は、RAM の出力が非同期な場合がありますが、これを同期的にコーディングしておくと同一スライス内でレジスタを使用することが可能になり、タイミング特性が改善されると共に、RAM がタイミングのボトルネックになる可能性が低減されます。

ブロック RAM には、FIFO や ECC (エラー訂正コード) など、さらに進んだ機能も搭載されています。分散 RAM には、新しい機能として 4 ポート コンフィギュレーションなどが可能になりました。場合によっては、これら機能を合成時に自動的に利用することができず、マニュアルでインスタンシエーションを行う必要があります。その場合は、ザイリンクスの CORE Generator ソフトウェア内でコアを生成することでその RAM をインスタンシエートするか、基本プロミティブをインスタンシエートすると良いでしょう。これらの先進機能を利用することで、RAM とロジック リソースを節約できるうえ、エリアやパフォーマンス、消費電力を改善することができます。

## 一般的なガイドライン

次に、コーディングやデザインの改善につながる一般的なガイドラインをいくつか紹介しましょう。まず、デザインに取り掛かるとき、各ブロックの設計の階層をうまく選択することです。階層をどう選択するかで、合成ツールやインプリメンテーション ツールが

図2 正しいFPGAコーディング法

### Verilog Coding Example

```

'timescale 1ns / 1ps

// Company: Xilinx

// Engineer: Brian Philofsky

//

// Create Date: 07:42:58 08/12/2006

// Design Name: good_design

// Module Name: good_code

// Project Name: HDL Coding and Design Practices for Improving Virtex 5

// Utilization, Performance and Power

// Target Devices: Virtex 5

// Tool versions: ISE 8.2i

// Description: This is example code employing some good coding practices

// when targeting a Virtex 5 device.

//

// Revision 0.01 - File Created

//

/////////////////////////////////////////////////////////////////

module good_code #(

parameter data_width = 16,

parity_width = 2

) (

input [data_width-1:0] DATA_IN,

input DATA_STORE,

input CLK, RST,

input READ_DATA,

output [data_width+parity_width-1:0] DATA_OUT,

output reg RW_ERROR = 1'b0,

output DATA_VALID, FULL

);

// Always initialize registers to known values

reg [data_width-1:0] data_in_reg = (data_width(1'b0));

reg [data_width-1:0] data_in_reg2 = (data_width(1'b0));

reg [2:0] data_store_delay = 3'b000;

reg [2:0] data_valid_delay = 3'b000;

reg [parity_width-1:0] parity = (parity_width(1'b0));

wire read_error, write_error;

// Use resets only where necessary and make them synchronous

// Make resets and clock enables active high

always @(posedge CLK)

if (RST)

data_in_reg <= (data_width(1'b0));

else if (DATA_STORE)

data_in_reg <= DATA_IN;

// Do not use resets where not necessary

// In this case an SRL can be used due to the fact no reset is described.

always @(posedge CLK) begin

data_store_delay <= (data_store_delay[1:0], DATA_STORE);

data_in_reg2 <= data_in_reg;

data_valid_delay <= (data_valid_delay[1:0], READ_DATA);

RW_ERROR <= read_error | write_error;

parity[1] <= ~data_in_reg[15:8];

parity[0] <= ~data_in_reg[7:0];

end

// In general, RAMs should be inferred however in this case, a FIFO is needed

// and synthesis can not yet infer the dedicated Virtex 5 FIFO.

// FIFO18: 16k+2k Parity Synchronous/Asynchronous BlockRAM FIFO

// Virtex-5

// Xilinx HDL Language Template, version 8.2.2i

FIFO18 #(

.ALMOST_FULL_OFFSET(12'h080), // Sets almost full threshold

.ALMOST_EMPTY_OFFSET(12'h080), // Sets the almost empty threshold

.DATA_WIDTH(18), // Sets data width to 4, 9 or 18

.DO_REG(1), // Must be 1 if EN_SYN = FALSE

.EN_SYN("TRUE"), // Specifies FIFO as Asynchronous ("FALSE") or Synchronous ("TRUE")

.FIRST_WORD_FALL_THROUGH("FALSE") // Sets the FIFO FWFT to "TRUE" or "FALSE"

) FIFO18_inst (

.ALMOSTEMPTY(), // 1-bit almost empty output flag

.ALMOSTFULL(), // 1-bit almost full output flag

.DO(DATA_OUT[15:0]), // 16-bit data output

.DOP(DATA_OUT[17:16]), // 2-bit parity data output

.EMPTY(), // 1-bit empty output flag

.FULL(FULL), // 1-bit full output flag

.RD(RD), // 12-bit read count output

.RDERR(read_error), // 1-bit read error output

.WR(WR), // 12-bit write count output

.WRERR(write_error), // 1-bit write error output

.DI(data_in_reg2), // 16-bit data input

.DIP(parity[1:0]), // 2-bit parity input

.RDCLK(CLK), // 1-bit read clock input

.RDEN(READ_DATA), // 1-bit read enable input

.RST(RST), // 1-bit reset input

.WRCLK(CLK), // 1-bit write clock input

.WREN(data_store_delay[2]) // 1-bit write enable input

);

// End of FIFO18_inst instantiation

endmodule

```

### VHDL Coding Example

```

-- Company: Xilinx

-- Engineer: Brian Philofsky

--

-- Create Date: 07:42:58 08/12/2006

-- Design Name: good_design

-- Module Name: good_code2

-- Project Name: HDL Coding Practices for Improving Virtex 5 Utilization,

-- Performance and Power

-- Target Devices: Virtex 5

-- Tool versions: ISE 8.2i

-- Description: This is an example code employing some good coding practices

-- when targeting a Virtex 5 device.

--

-- Revision 0.01 - File Created

--

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_arith.all;

library UNISIM;

use UNISIM.Vcomponents.all;

entity good_code2 is

generic (

data_width : integer := 16;

parity_width : integer := 2

);

port (

DATA_IN : in std_logic_vector(data_width-1 downto 0);

DATA_STORE: in std_logic;

CLK, RST: in std_logic;

READ_DATA;

DATA_OUT : out std_logic_vector(data_width+parity_width-1 downto 0);

RW_ERROR : out std_logic := '0';

DATA_VALID, FULL : out std_logic

);

end good_code2;

architecture XILINX of good_code2 is

begin

-- Always initialize registers to known values

signal data_in_reg: std_logic_vector(data_width-1 downto 0) := (others => '0');

signal data_in_reg2: std_logic_vector(data_width-1 downto 0) := (others => '0');

signal data_store_delay: std_logic_vector(2 downto 0) := "000";

signal data_valid_delay: std_logic_vector(2 downto 0) := "000";

signal parity: std_logic_vector(parity_width-1 downto 0) := (others => '0');

signal read_error, write_error: std_logic;

begin

-- Use resets only where necessary and make them synchronous

-- Make resets and clock enables active high

process (CLK)

begin

if (CLK'event and CLK='1') then

if RST='1' then

data_in_reg <= (others => '0');

elsif (DATA_STORE='1') then

data_in_reg <= DATA_IN;

end if;

end if;

end process;

-- Do not use resets where not necessary

-- In this case an SRL can be used due to the fact no reset is described.

process (CLK)

begin

if (CLK'event and CLK='1') then

data_store_delay <= (data_store_delay(1 downto 0) & DATA_STORE);

data_in_reg2 <= data_in_reg;

data_valid_delay <= (data_valid_delay(1 downto 0) & READ_DATA);

RW_ERROR <= read_error OR write_error;

parity(1) <= (data_in_reg(15) XOR data_in_reg(14)) XOR data_in_reg(13) XOR

data_in_reg(12) XOR data_in_reg(11) XOR data_in_reg(10) XOR

data_in_reg(9) XOR data_in_reg(8);

parity(0) <= (data_in_reg(7) XOR data_in_reg(6)) XOR data_in_reg(5) XOR

data_in_reg(4) XOR data_in_reg(3) XOR data_in_reg(2) XOR

data_in_reg(1) XOR data_in_reg(0);

end if;

end process;

-- In general, RAMs should be inferred however in this case, a FIFO is needed

-- and synthesis can not yet infer the dedicated Virtex 5 FIFO.

-- FIFO18: 16k+2k Parity Synchronous/Asynchronous BlockRAM FIFO BlockRAM Memory

-- Virtex-5

-- Xilinx HDL Language Template version 8.2.2i

FIFO18_inst : FIFO18

generic map (

ALMOST_FULL_OFFSET => X"080", -- Sets almost full threshold

ALMOST_EMPTY_OFFSET => X"080", -- Sets the almost empty threshold

DATA_WIDTH => 18, -- Sets data width to 4, 9 or 36

DO_REG => 1, -- Enable output register (0 or 1)

EN_SYN => TRUE, -- Must be 1 if the EN_SYN = FALSE

FIRST_WORD_FALL_THROUGH => FALSE -- Specifies FIFO as Asynchronous (FALSE) or Synchronous (TRUE)

)

port map (

ALMOSTEMPTY => open, -- 1-bit almost empty output flag

ALMOSTFULL => open, -- 1-bit almost full output flag

DO => DATA_OUT(15 downto 0), -- 32-bit data output

DOP => DATA_OUT(17 downto 16), -- 2-bit parity data output

EOP=> open, -- 1-bit empty output flag

FULL=> open, -- 1-bit full output flag

RD=> open, -- 12-bit read count output

RDERR=> read_error, -- 1-bit read error output

WR=> open, -- 12-bit write count output

WRERR=> write_error, -- 1-bit write error output

DI=> data_in_reg2, -- 16-bit data input

DIP=> parity, -- 2-bit parity input

RDCLK=> CLK, -- 1-bit read clock input

RDEN=> READ_DATA, -- 1-bit read enable input

RST=> RST, -- 1-bit reset input

WRCLK=> CLK, -- 1-bit write clock input

WREN=> data_store_delay(2) -- 1-bit write enable input

);

-- End of FIFO18_inst instantiation

end XILINX;

```

ロジック パスをどれだけ最適化できるかが決定するためです。

また、タイミング パスが階層の境界を複数またがないよう注意してください。これを許すと、ツールによるロジック最適化が制限されるばかりか、デザインのインプリメンテーションやデバッグの選択肢も限られてしまいます。たとえば、特定の階層でパーティションや KEEP\_HIERARCHY を使用できなくなることがあります。

コードの一部または大部分が Virtex-5 FPGA 以外のアーキテクチャ用に作成されたデザインについては、Virtex-5 アーキテクチャへのスムーズなインプリメントが可能か、コードをよくレビューして判断してください。この時点ではほんの数分をかけて不適切なコードを識別して修正しておくことにより、あの数時間を節約することができます。

デザインに過去のアーキテクチャからのコアやプリコンパイルされたネットリスト (EDIF または NGC ファイル) が含まれてい

る場合、Virtex-5 デバイス用にこれらネットリストを再生成する必要があります。再生成を行わなければ、以前のアーキテクチャに最適化されたネットリストは、Virtex-5 アーキテクチャをターゲットにしてもうまく適合しないことが多いからです。

最後のガイドラインとして、ISE ツール内の HDL 言語テンプレートを使うと良いでしょう。これらのテンプレートを利用すると VHDL や Verilog コードの生成を加速化することが可能になるうえ、FPGA 向けにより最適なコードを作成するのに役立ちます。さらに、シンタックス エラーなどのありがちな単純ミスや、HDL コードのテストと検証に遅れが生じることはなくなります。

図 3 は、ここで解説したガイドラインに従って記述した Verilog コードと VHDL コードです。

## 結論

コーディングのスタイルは人それぞれです

が、本稿で紹介したガイドラインに従うことにより最適な結果を得られるでしょう。最高の Virtex-5 デザインを達成するには、これらガイドライン以外にも知っておきたい知識はありますが、本稿では少しでもデザインを最適に近づけるために役立つ一般的な手法をいくつか紹介しました。

有効な HDL コードであれば、ほとんどのコードが正常に機能するデザインになりますが、シンプルなガイドラインに従うことで集積度やパフォーマンス、消費電力をさらに改善することが可能で、最終的なデザインの完成にかかる時間を短縮することが可能になります。

詳細は、「合成／シミュレーション デザイン ガイド」([http://toolbox.xilinx.com/doc\\_ssan/xilinx9j/books/docs/sim/sim.pdf](http://toolbox.xilinx.com/doc_ssan/xilinx9j/books/docs/sim/sim.pdf)) または White Paper 231 「デザインパフォーマンス向上のためのHDL コーディング法」([http://japan.xilinx.com/bvdocs/whitepapers/j\\_wp231.pdf](http://japan.xilinx.com/bvdocs/whitepapers/j_wp231.pdf)) をご覧ください。

# ザイリンクス トレーニング スケジュール [5~6月]

3~4月のスケジュールは13ページをご覧ください。

ザイリンクスでは、大規模、高速 FPGA を対象にした FPGA 設計のための各種トレーニングを各地で開催しております。是非ご利用ください。

| コース名                               | 日 程 |               | 主 催     | 開 催 地   |

|------------------------------------|-----|---------------|---------|---------|

| FPGA 設計実践                          | 5月  | 8日(火)～9日(水)   | ザイリンクス  | 東京 品川会場 |

|                                    | 5月  | 29日(火)～30日(水) | ザイリンクス  | 東京 品川会場 |

|                                    | 6月  | 5日(火)～6日(水)   | ザイリンクス  | 東京 品川会場 |

|                                    | 6月  | 19日(火)～20日(水) | ザイリンクス  | 東京 品川会場 |

| アドバンスド FPGA 設計                     | 5月  | 9日(水)～10日(木)  | 新光商事    | 大阪会場    |

|                                    | 6月  | 12日(火)～13日(水) | ザイリンクス  | 東京 品川会場 |

| Virtex-4 デザイン                      | 5月  | 15日(水)～16日(木) | ザイリンクス  | 東京 品川会場 |

|                                    | 6月  | 7日(月)～8日(火)   | 菱洋エレクトロ | 大阪会場    |

| エンベデッド システム開発                      | 5月  | 22日(火)～23日(水) | ザイリンクス  | 東京 品川会場 |

|                                    | 5月  | 10日(木)～11日(金) | ザイリンクス  | 東京 品川会場 |

|                                    | 6月  | 7日(月)～8日(火)   | ザイリンクス  | 東京 品川会場 |

|                                    | 6月  | 20日(水)～21日(木) | ザイリンクス  | 東京 品川会場 |

| アドバンスド エンベデッド システム開発               | 5月  | 24日(木)～25日(金) | ザイリンクス  | 東京 品川会場 |

| System Generator を使用した DSP デザインフロー | 5月  | 17日(木)～18日(金) | 新光商事    | 大阪会場    |

|                                    | 6月  | 26日(火)～27日(水) | ザイリンクス  | 東京 品川会場 |

| MGT シリアル I/O デザイン                  | 5月  | 17日(木)～18日(金) | ザイリンクス  | 東京 品川会場 |

|                                    | 6月  | 14日(木)～15日(金) | ザイリンクス  | 東京 品川会場 |

\*すべてのトレーニングは、ザイリンクス認定インストラクターによるオフィシャルトレーニングです。

\*日程および会場は、都合により変更となる場合もございます。最新情報はザイリンクストレーニングWebサイトをご覧ください。

詳細とご登録はこちらから ►► <http://japan.xilinx.com/support/education-home.htm>

## Getting the Best Results from Virtex-5 FPGAs

# Virtex-5 FPGA から最良の結果を引き出す設計手法

アルゴリズムを全面変更し、Virtex-5に最適化されたシンプリシティのEDAツール「Synplify Pro ソフトウェア」

John Gallagher

Sr. Director Outbound Marketing

Synplicity, Inc.

[johng@synplicity.com](mailto:johng@synplicity.com)

ザイリンクス Virtex™-5 デバイスの革新的機能を十分に引き出すには、それら機能を 100% 活用するための EDA 技術が不可欠です。Synplicity は、FPGA アーキテクチャとそれに対応する EDA デザインツールを並行して開発を行ってきました。旧世代の EDA 開発の歴史は、Virtex-5 デバイスとその旧世代の歴史に似ています。

FPGA として初めて 65nm プロセス テクノロジで開発された Virtex-5 ファミリのドメイン最適化デバイスは、Virtex-4 ファミリよりロジックセルが 65%、I/O ピンが 25% 増加しています。また、Virtex-5 デバイスは、Virtex-4 と比較してパフォーマンスが 30% 向上、ダイナミック消費電力は 35% 低減、シリコン面積は 45% 縮小されています。

Virtex-5 アーキテクチャが革新的な特徴を備えているため、ザイリンクス社は、Synplicity が新しい特徴を活かす合成フローを開発できるよう早い時期から Virtex-5 アーキテクチャを公開してきました。最初の Virtex-5 デバイスが発表される 1 年以上前から、Synplify Pro 合成エンジンの開発に向け、ザイリンクスのエンジニアと協力を重ねてきました。我々は、Virtex-5 を使ったデザインのパフォーマンスとロジック集積度を最大限に高めるため、Synplify Pro ソフトウェアの大幅なアーキテクチャの変更が必要でした。このようなザイリンクス社とのパートナーシップにより、設計者が Virtex-5 デバイスを短期間で展開するためのツールとメソッドを用意できました。

本稿では、Virtex-5 ファミリの特徴をフルに引き出すため、Synplify Pro FPGA 合成エンジンをいかに開発したかを解説します。

## 6 入力 LUT を合成するための新アルゴリズム

FPGA ファブリックの複雑化に伴い、合成アルゴリズムをより一層精巧にする必要が生じました。たとえば、4 入力のルックアップテーブル (LUT) をベースとするファブリックと同じアルゴリズムを 6 入力 LUT ベースのファブリックにそのまま適用したのでは、合成の実行時間が非常に遅くなります。Virtex-5 アーキテクチャの特徴をフルに活用するには、土台となる合成アルゴリズムを微調整するか、場合によっては完全に書き換える必要があったのです。

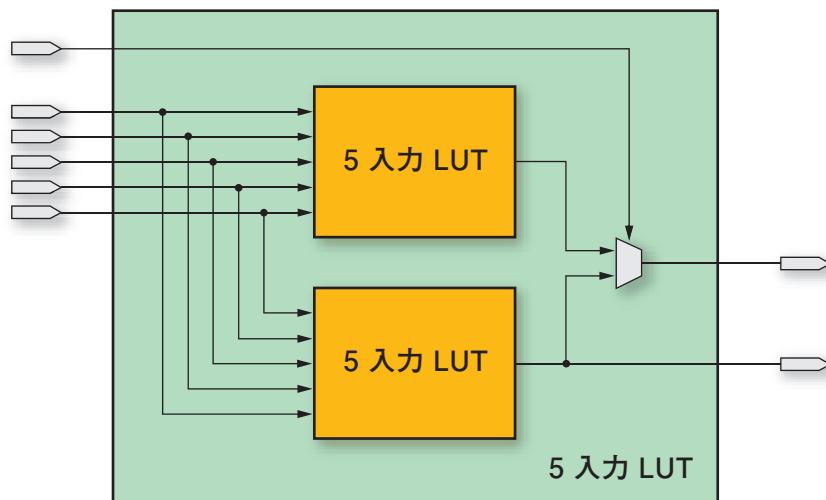

広帯域データバスや DSP などのファンクションをマッピングするうえで必要となるロジックレベルを削減するため、Virtex-5 ファミリの ExpressFabric™ テクノロジは、6 つの独立した入力を持つ LUT を搭載しています（図 1）。これにより、広帯域なファンクションをインプリメントするためのロジックレベルの数と LUT エリアが大幅に削減されます。合成プロセス中は、各論理素子を 1 つの 6 入力 LUT、もしくはそれぞれ 5 つの入力を共有する 2 つの 5 入力 LUT として使用できます。

しかしながら、6 入力 LUT へのマッピングに伴う組み合わせの爆発的増加は、正しく処理されなければ、メモリ使用とランタイムの問題を招く恐れがあります。4 入力 LUT ベースのファブリック向けアルゴリズムを、大幅な変更を加えることなく 6 入力 LUT のファブリックに適用すると、たとえ合成が完了してもその実行時間が数倍長くなってしまいます。さらに、最適なマッピングを見つけようとする際、従来のアルゴリズムでは一ヵ月 ミニマに陥る危険があります。

タイミングドリブンのエンジンと異なり、従来の合成エンジンはそのほとんどが単にロジックレベル数の低減のみを行います。この方法では、入力から出力へのそれぞれのパスが非対称の遅延を持つ LUT アーキテクチャで問題を招きます。図 1 に示すよう

な 5 個の共有入力ピンと 6 番目の独立したピンを考えてみましょう。これらピンの遅延は大きく異なります。

また、Virtex-5 の LUT を 2 つの 5 入力コンフィギュレーションで使用できるという事実は、マッピング動作をさらに複雑化します。合成ツールのベンダは、入力を共有しながら異なるファンクションを実現する構造を保持するために、膨大な研究開発を行う必要があるのです。

ユニークなダイレクトマッピング機能を備える Synplify Pro ソフトウェアは、カット数を最小限に抑え、膨大な容量を処理し、またマッピングとタイミングの複雑なシナリオに対応が可能なさまざまなヒューリスティックアルゴリズムを実装することに成功しました。

### 対角方向に対称なインターネットを使用したタイミングの見積もり

ExpressFabric のもう 1 つの特徴として、より少ないホップでより多くのロケーションに届く対角方向に対称なインターネットがあります（図 2）。これにより、スピードと予測性の改善が可能になります。Express Fabric の 6 入力 LUT と対角方向に対称なインターネットパターンを組み合わせることで、ロジックの性能が Virtex-4 デバイスと比べて平均 30% 向上されました。これは 2 段階スピードグレードの向

上に相当します。

対角方向に対称なインターネットパターンは、タイミング解析を格段に複雑化します。従来の物理合成アルゴリズムは、「マンハッタン配線」つまり 90° 配線のアーキテクチャをベースしていました。90° 配線と対角配線の両方を扱えるよう、新しいアルゴリズムと遅延モデルをカスタムデザインしました。Synplify Pro ツールには、シンプルなワイヤロードモデルではなく、高度なネットリストベースの配線見積もりを採用したのです（配線値が既知の場合はその値も提供）。たとえば、高速キャリーチェーンの場合、配線遅延はよく知られているため、直接「プラグイン」できます。同様に、セルやドライバ、ロード、特定の配線が既知の場合、このバスの正確な配線遅延を配線およびタイミングアルゴリズムにプラグインできます。

## 高速、大容量の RAM ブロックを合成

Virtex-5 ファミリの新しいブロック RAM 構造（パイプライン付き）は、Virtex-4 のコンポーネントの 2 倍に相当する 32Kb に増加しました。これらのブロックは、RAM の bandwidth を 2 倍にするシンプルなデュアルポートモードに加え、FIFO ロジックとして追加のハード IP や、新たに 64 ビットのエラー訂正 (ECC) ロジックを搭載しています（図 3）。このロジックをハード IP としてインプリメ

図 1 Virtex-5 の 6 入力 LUT

ントしたこと、他のリソースを解放し、ダイナミック消費電力を最小限に抑えているのです。

Virtex-5 デバイス内のすべてのハード IP ブロックと同様、これらのブロック RAM は、より高 bandwidth のオンチップ メモリを提供するよう、550MHz の動作速度にチューニングされています。18Mb のブロック RAM は 2 個の 9Mb 物理メモリから成り、ほとんどのコンフィギュレーションで、読み出しありは書き込み動作のいずれか一方で 9Mb サブブロックをイネーブルして消費電力を節約するよう自動制御されます。

一方、Synplify Pro 合成ソフトウェアは、シングル ポートとデュアル ポートのインプリメンテーションや、シングルおよびマルチ クロッキング スキーム、自動リタイミングなど、自動的なメモリ推論を実行できます。自動リタイミングに関しては、Virtex-5 のブロック RAM は本質的に同期です。ただし、デザインの RTL はメモリとレジスタを非同期として記述が可能です。この場合、Synplify Pro ツールはレジスタを RAM に「プッシュ」できます。

同様に、Synplify Pro は潜在的な矛盾を認識し、自動的に所定の矛盾解決ロジックを生成します。たとえば、同じアドレスに 2 つのデータを書き込み、結果が定義されていないデュアル ポート RAM の場合、Synplify Pro ツールは所定のロジックを自動的に挿入し、RTL がシミュレーションするのとまったく同じようにメモリを動作させることでこの問題を解決します。

さらに、Synplify Pro ソフトウェアは、デザインに記述されているメモリを自動的に解析し、それを目的のメモリ リソースにマッピングする際の潜在的な問題点を認識することができます。たとえば、ブロック RAM が必要であるにも関わらず、物理デバイスに用意されている以上のメモリをすでに使用している場合、Synplify Pro は、そのメモリの一部をセレクト RAM に自動的に移します。

## より高速、広帯域な DSP ブロックの最適利用

DSP48E と呼ばれる Virtex-5 のハ

図 2 対角方向に対称なインターネット配線

ド DSP スライスは、Virtex-4 FPGA に採用されている  $18 \times 18$  ビット乗算器ではなく、 $25 \times 18$  ビット乗算器を備えています。ビット数の増加はカスケード ステージの減少につながるため、全体的なパフォーマンスと利用効率が高まります（図 4）。

550MHz の動作にチューニングされたこれらの高精度で高性能、柔軟性の高いスライスを、DSP や算術演算、ロジック ファンクション用にコンフィギュレーションし、加算器 チェーン アーキテクチャ用にカスケード接続することができます。DSP48E スライスは、Virtex-4 FPGA の相当するファンクションと比較して消費電力が 40% 低減されています（トグル レート 38% で 1.38 mW/100MHz）。

DSP スライスが高性能化されたということは、RTL で定義したデータ パスが最適な DSP インプリメンテーション構造にぴったりマッチしなくなるということでもあります。たとえば、まず「a」と「b」、「c」と「d」を加算してからこれら演算の結果を加算することで、「(a + b) + (c + d)」というファンクションをインプリメントするより、「(((a + b) + c) + d)」という式で DSP スライスをカスケード化する方が効率的です。

Synplify Pro ソフトウェアには、極めて高度なマッピング アルゴリズムが採用されています。これらのアルゴリズムは、たくさんのデータ パス マッサージングを実行する

図 3 Virtex-5 ファミリは 10Mb の 550MHz ブロック RAM を搭載

ことで、Virtex-5 SXT デバイスに搭載されている DSP48E スライスに効率的にマッピングすると共に、これらスライスをフルに活用するデータ パス構造を作成します。

図 4 では示されていませんが、DSP 48E スライスには大量のレジスタが含まれています。Synplify Pro ツールは、組み込まれているこれらレジスタ エレメントをフルに活かすため、先進のパイプラインおよびリタイミング テクニックを使用できます。また、これら内蔵レジスタ エレメントは同期リセットだけをサポートしています。したがって、コードに非同期リセットを採用した場合、Synplify Pro ツールは、必要な機能を復元するため自動的に所定のグループ ロジックを挿入します。

図4 25×18乗算器を備えるVirtex-5のDSPスライス

## 高速I/Oの合成

特定デバイスにおけるI/Oの数とタイプは、特にFPGAのアプリケーションがチップもしくはシステムレベルの検証の場合に、デザインのインプリメンテーションに重要な要素です。Certify ASIC RTLプロトタイプやSynplify Pro合成ソリューションといったSynplicity社のツールを使って、信号の統合とI/Oの自動割り当ての両方を考慮し、Virtex-5デバイスのパワフルなI/O機能を最適化します。

Virtex-5 FPGAは、1,200もの汎用入出力(GPIO)ピンを搭載しており、業界標準およびカスタムプロトコルのインプリメンテーションに使用できます。これらピンに用いられるSelectIO™テクノロジは、1.25Gbpsの差動I/Oと800MbpsのシングルエンドI/Oを提供します。

第2世代のChipSync™ソース同期テクノロジにより、プログラム可能な遅延を各入力と各出力に個別に適用することが可能で、さらに、Virtex-5の第2世代スペースシェブロンパッケージングテクノロジのユニークな電源およびグランドピンの配置により、シグナルインテグリティとクロス

トークの影響を最小限に抑えながら回路基板のレイアウトをシンプル化を実現しています。これらのI/Oテクノロジにより、DDR2やQDR IIなどの広帯域幅インターフェイスを高い信頼性で動作させることができます。

Synplify Pro合成ソフトウェアは、差動信号と双方向I/O信号を自動的に処理するようにデザインされています。たとえば、ポートを低電圧差動信号(LVDS)出力ポートとして識別するアトリビュートを適用した場合、Synplify Proツールは1つの入力と2つの出力を用いて所定のLVDSプリミティブを挿入します。

## 次のステップ (超大容量タイミングクロージャタスクフォース)

デバイスがサブミクロンの領域に深く入り込んでいく中、FPGAベンダとEDAベンダの協力関係はますます強まっています。Synplify Pro合成エンジンを拡張するため、1年にわたってザイリンクスのエンジニアと協力し合ってきたことで、デバイスが市場に投入されたと同時に、実デザインでテストさ

れた最高の合成テクノロジを利用できることなど、多大なメリットをもたらしました。

将来のFPGAプラットフォームはますます高集積化、高機能化し、広範囲なアプリケーションドメインで先進のFPGAアーキテクチャを利用できるようになるでしょう。これらの新しいプラットフォームは、なお一層洗練されたデザインフローや合成ソリューションを必要とします。このため、Synplicityとザイリンクスの両社は「Ultra-High-Capacity Timing Closure Task Force(超大容量タイミングクロージャタスクフォース)」を立ち上げました。このプロジェクトの一環として、両社のエンジニアリングチームは、次世代FPGAを用いてインプリメントする超高集積デザインの生産性と結果の品質を最大限高める、新たなデザインフローを定義しインプリメントするため協力していく意向です。

このプロジェクトは当面、デザイン結果の品質と実行時間を大幅に改善することに専念し、デザインに小規模な変更を加えたときに安定した結果を達成することを目指しますが、プロジェクトの最終的な目標は、設計者が超高集積デザインに対して押しボタンに近い感覚で結果を生成し、1日に複数のデザインを反復できるようにすることです。

## 結論

ザイリンクスVirtex-5ファミリは、Synplicity社と最高のデザイン結果を達成するために共同で開発したインプリメンテーションフローを採用しています。この新しいFPGAは、6入力LUTや対角方向に対称なインターフェクトファブリックなど、アーキテクチャ上の多彩な新機能を搭載しています。

Virtex-5に対応するSynplify Proソフトウェアソリューションには、対角方向に対称なインターフェクトに対する新方式のタイミング見積もり、組み合わせの爆発的増加に対処する新たな合成アルゴリズム、専用のRAM推論とI/O処理、ごくわずかなデザイン変更で安定した結果を可能にする数々の改善点が盛り込まれています。是非、Virtex-5デバイスとSynplify Proソフトウェアを併用してこれら新機能を今すぐ体験してください。

## Virtex-5とSynplify Proで複雑な設計の性能を向上

### SynplicityとXilinxがチームを組んで対応

2006年5月、Xilinxは業界初の65nmFPGAであるVirtex-5を発表しました。そして、この発表よりずっと以前から、Xilinxはこの最先端デバイスの性能と集積度を十分に有効活用してもらうためには、革新的な合成ツールが必要であると気づいていました。そこで、XilinxはSynplicityとタッグを組んだわけです。

XilinxとSynplicityのエンジニアは業界をリードするSynplicityの合成ツールで新製品Virtex-5を適切にサポートするために、長い間緊密に協力してきました。

Virtex-5に向けて強化した機能をタイミング・ドリブン合成であるSynplify Proソフトウェアに組み入れることによって、設計者は複雑な設計の性能を向上すると同時にTime-to-Marketの目標を達成することが可能になります。

### 今後の展望

次世代以降のデバイスは既存のデバイスよりさらに集積度と性能が増大し続け、広範なアプリケーションで最先端のFPGAアーキテクチャを活用できるようになるでしょう。そこでSynplicityとXilinxは超大規模なデバイスのタイミング収束に関連するタスクフォースを組織しました。双方のエンジニアが集結し、次世代の65nm FPGAで超高集積なデザインの生産性と質を最大限に向上するための新しいデザイン・フローを構築するのがその目的です。

**複雑な設計の性能を最大限にするために有用となる

Synplicityツールについての詳細は、当社日本語Web

[www.synplicity.jp](http://www.synplicity.jp)をご覧ください。**

# Maximizing Design Performance for Virtex-5 FPGAs

# Virtex-5 FPGA の パフォーマンスを最大限に するデザイン技法

Virtex-5 デザインのタイミング目標の達成を可能にする

ISE ソフトウェア

Michelle Fernandez

Software Technical Marketing Engineer

Xilinx, Inc.

[michelle.fernandez@xilinx.com](mailto:michelle.fernandez@xilinx.com)

FPGA がパフォーマンスの限界に挑む中、デザイン性能を最大限に引き出すには、デバイスのアーキテクチャとデザイン ソフトウェアを熟知している必要があります。ザイリンクスの 65nm Virtex™-5 FPGA ファミリは、ExpressFabric™ テクノロジや対角方向に対称な配線、容量／機能を強化したオンチップ メモリ、DSP スライス、高速 I/O などを備え、業界最高のパフォーマンスを提供します。システム性能を最大化するには、タイミング制約を定義したり、合成と

インプリメンテーションの際にそのデザインに最も適したオプションを選択したりするなど、適切なデザイン テクニックを使う必要があります。本稿では、デザインの反復を極力抑えながらより高速なタイミングを達成する方法について解説します。

## アーキテクチャの理解

Virtex-5 ファミリのような新しい FPGA アーキテクチャを評価するは、ハードウェアの特長を理解するため、ユーザーガイドとデータ シートを熟読することが重要です。

Virtex-5 FPGA ファミリは、さらなる高速化を実現する新しい Express Fabric アーキ

テクチャやロジック段数を低減する新しい 6 入力 LUT 構造、遅延を最小限に抑える対角方向に対称なインターネット構造を採用しています。各 CLB は、複数のコンフィギュレーション方法が可能な 4 個の 6 入力 LUT と 4 個のレジスタを備える 2 つのスライスで構成されます。スライス パッキングを最大限に高めるには、スライスの相互接続についての理解と、共有リソースについての理解も必要です。

Virtex-5 FPGA には、550MHz にチューニングされたエンベデッド メモリ（ブロック RAM）や数値演算ファンクション（DSP48 スライス）といったハード IP が含まれています。クリティカル パスにこれらハード IP ブロックが含まれる場合、次の

図 1 適切なタイミング制約

点に留意しながらデザインしてください。

- ブロックの各機能がデザインに最大限に活かされており、合成ツールがそれら機能を RTL からの予想どおりに推論していることを確認してください。

- エンベデッド ブロック RAM メモリや DSP48E スライスを使う際は、セットアップと Clock-to-Out の遅延を低減するため、可能な限りそれぞれの専用パイプライン レジスタを使うことが重要です。

- デザインにおけるブロック RAM や DSP48E スライスの混用についての

考慮や、専用ブロックを使うべきか、それとも配置の柔軟性を高めるために専用ブロックと同じファンクションをスライスを用いてインプリメントすべきかのトレードオフについて考慮する必要があります。

デザイン性能は、選択するクロック リソースによっても影響を受けます。Virtex-5 FPGA デバイスには、I/O やリージョナル、およびグローバル クロック リソースがあります。Virtex-5 は複数のクロック リージョンに分かれています、最大 4 個のリージョナル クロックと 10 個のグローバル クロックを使用できます。デザインをプランニングする際は、使用予定のクロック リージョンの

図 2 Synplify Pro の推奨設定

図 3 ISE 合成 (XST) の推奨設定

ISE Synthesis の [プロセス プロパティ] ダイアログ

| Property Name           | Value                                                                                  |

|-------------------------|----------------------------------------------------------------------------------------|

| Synthesis Options       | Optimization Effort                                                                    |

|                         | Synthesis Constraint File<br>Create a XCF File (UCF Syntax)<br>NET clock PERIOD = 5 ns |

|                         | Read Cores                                                                             |

| HDL Options             | Resource Sharing                                                                       |

| Xilinx-Specific Options | Register Balancing                                                                     |

|                         | Pack I/O Registers into IOBs                                                           |

数と、1 つのクロック リージョン内に使用するクロックの種類をあらかじめ検討しておくことが重要です。I/O を配置する際、そのインターフェイス ロジックがクロック リージョン内のすべてのクロック リソースを必要としないように配置を行えば、ISE™ ソフトウェアでの配置の柔軟性を大幅に高めることができます。

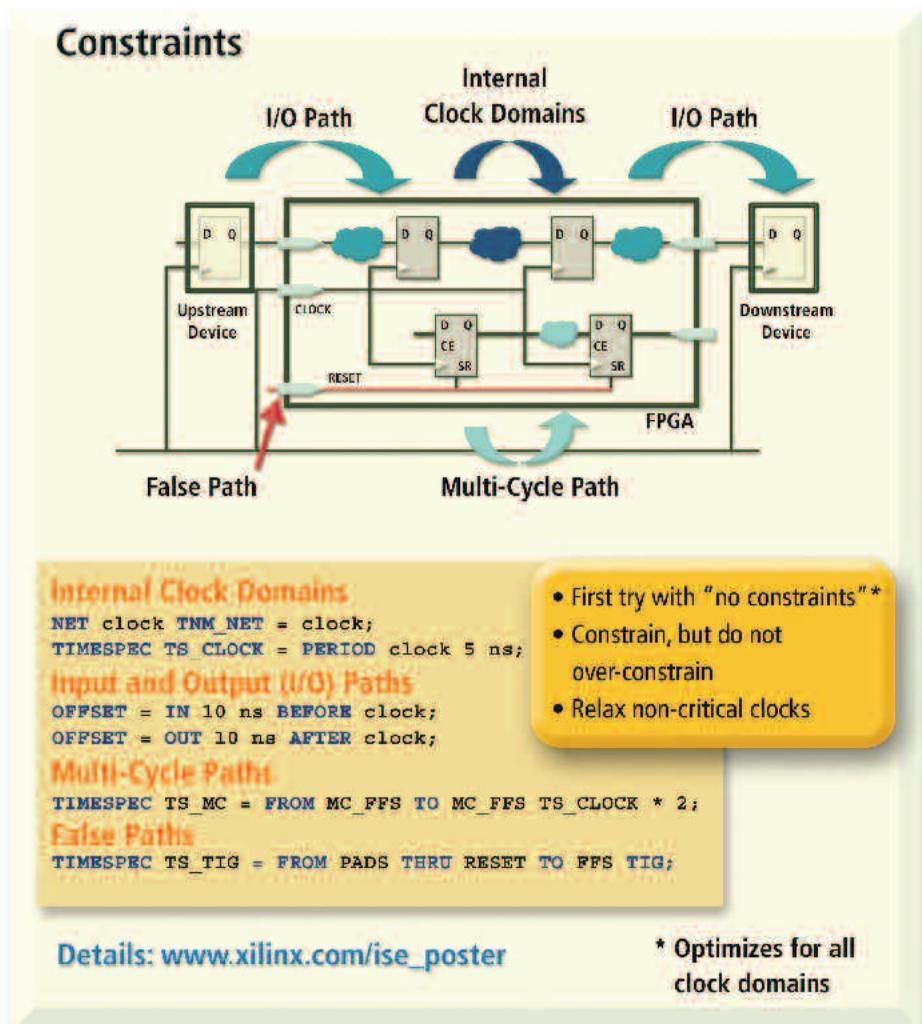

## タイミング要件の定義

合成ツールと ISE™ インプリメンテーション ツールは、内部クロック ドメインや I/O パス、マルチサイクル パス、False パスなど(図 1)に対するタイミング制約で指定するパフォーマンス ゴールを目標に実行され

ます。現実的なタイミング制約を定義することで、長い実行時間を回避できます。

合成レポートで複製されたレジスタをチェックし、元のレジスタに適用されるタイミング制約が複製されたレジスタにも適用されていることを確認してください。タイミング制約を記述する際は、個々のパスを制約する前に、できるだけ多くのパス同じタイミング要件でグループ化して、インプリメンテーションの実行時間とメモリの使用量を最小限に抑えてください。

## 合成の実行

次に、合成ツールから最適な結果を得るためにデザイン上の注意点をみてみましょう。

- 合成による RTL の推論がアーキテクチャの特長を活かすよう、適切なコーディング テクニックを使ってください。

- 下層のネットリストを合成プロジェクトに追加することで、そのネットリストにインターフェイスする HDL の最適化が促進されます。

- インプリメンテーションにおけるクリティカル パスが合成ツール上ではクリティカルとみなされない場合、合成ツールにそのパスを強制的にフォーカスを当てさ

せるため、Synplify Pro の「-route」制約を試してください。

- 合成ツールの設定を調べてください (Synplify と XST [Xilinx Synthesis Technology]の推奨ツール設定については、それぞれ図 2 と図 3 を参照)。合成の最適化に影響を与えるさまざまな属性を使って、再コーディングすることなく合成に変化を与えることができます (表 1)。

Synplify Pro のリタイミングや XST のレジスタ バランシングなど、特定のツール設定がエリアに影響を与えることもあります。デザインがハイ ファンアウト ネットによる影響を受け、合成ツールでそのファンアウトを低減させたい場合、ファンアウト リミットをグローバルに設定するのではなく、そのネットに対してファンアウトの属性を個別に使用してください。クリティカル パスが階層境界を超える場合、階層を維持するのは避けてください。また、インプリメンテーション前に合成レポート内のワーニングを確認してください。

## インプリメンテーション オプションの選択

合成ツールから満足できるタイミング見

積もりが得られたら、インプリメンテーション ツールを使用してデザイン実装後の性能を決定します。ISE は、デフォルトで性能評価モードに設定されており、タイミング目標を指定することなくインプリメンテーション ツールから高性能な結果を導くことができます。

次のステップとして、タイミング ドリブンでマッピング (MAP) と配置配線 (PAR) を実行します。タイミング ドリブンでの MAP は閉ループのパッキングとタイミング ドリブンの配置を実行し、PAR はデザインの配線を実行します。MAP と PAR は共に、最適な結果を得るために、エフオート レベルを High に設定して実行する必要があります。

インプリメンテーションにおける物理合成オプションは、デザインのクリティカル パスに関する情報を基にロジックを再最適化してパッキングできることから、配置配線のさらなる改善を実現します。物理合成のオプションは MAP プロセス中にインプリメントされ、グローバル ネットリストの最適化やローカライズされたロジックの最適化、リタイミング、レジスタの複製、等価なレジスタの除去を行うことができます。各オプションの詳細は、ザイリンクスのホワイトペーパー、「Physical Synthesis and Optimization with ISE 8.1i」(<http://japan.xilinx.com/bvdocs/whitepapers/wp230.pdf>)をご覧ください。

表 1 便利な合成属性\*

|                                    | XST           | Synplify Pro               |

|------------------------------------|---------------|----------------------------|

| ファンアウト制御                           | max_fanout    | syn_maxfan                 |

| ブロック RAM あるいはセレクト RAM への RAM の直接推論 | ram_style     | syn_ramstyle               |

| DSP48E スライスの直接使用                   | use_dsp48     | syn_multstyle/syn_DSPstyle |

| SRL16 の直接使用                        | shreg_extract | syn_srlstyle               |

| ブロック RAM 使用率の制御                    | なし            | syn_allowed_resources      |

| 最適化中のレジスタ インスタンスの保存                | Keep          | syn_preserve               |

| ワイヤの保存                             | Keep          | syn_keep                   |

| 未使用出力のあるブラック ボックスの保存               | Keep          | syn_noprune                |

\* XST に関する資料は、<http://toolbox.xilinx.com/docsan/xilinx82j/books/docs/xst/xst.pdf> をご覧ください。

Synplify Pro のドキュメンテーションは、ツールのヘルプ ドキュメンテーションに用意されています。

## ユーティリティ ツールの Xplorer

Xplorer は、最高のデザイン性能を達成するための各種インプリメンテーション オプションを決定する際に便利なツールです。Xplorer には、タイミング クロージャとベスト パフォーマンスという 2 つのモードがあります。タイミング クロージャ モードは、タイミング制約を評価し、これら目標を達成するためにさまざまなインプリメンテーション オプションの組み合わせを実行します。ベスト パフォーマンス モードでは、フォーカスを当てたいクロック ドメインを指定すると、Xplorer ツールがそのクロックの最高周波数を達成するよう動作します。このモードはデザインの最大性能をベンチマークする際に便利です。

## クリティカル パスの評価

クリティカル パスの特性を理解することで、次のデザイン反復に備えて何を行わべきかの的確な判断を下すことができます。データパスには、ロジック遅延とインターフェクト遅延の両方があります。ロジック遅延を構成する個々のコンポーネントの遅延は、固定で変更することはできません。ロジック遅延は、ロジック段数を減らすか、ロジックの構造を定義しなおすことで低減できます。

インターフェクト遅延はこれよりずっと変動性があり、ロジックの配置によって左右されます。デザインに PAR を実行する前に、MAP 後のタイミング解析を行うことを推奨します。このタイミング レポートでは配線遅延の見積もりしかわかりませんが、インプリメンテーション ツールが扱うクリティカル パスを知る手がかりになります。クリティカル パスが多数のロジック段数を持っている場合、そのクリティカル パスに PAR を実行するのではなく、ロジック段数を低減することに努力した方が良いでしょう。

デザインのロジック段数が多すぎる場合は、次の方法を試みてください。

1. MAP で物理合成オプションを実行する。

2. 合成に戻り、インプリメンテーションで報

告されたクリティカル パスが合成でレポートされたものとマッチしていることを確認する。

3. HDL コードの合成推論を再検討する。

ロジック段数が少ないにもかかわらず特定のデータパスがタイミングを満たしていない場合は、次を試みてください。

1. 遅延の長い配線のファンアウトを評価する。

2. クリティカル パスにブロック RAM や DSP48E スライスなどのハード IP ブロックがある場合、デザインがエンベデッド レジスタをフルに活用していることを確認する。また、このハード ブロックを使うか、スライス ロジックを使うかのトレードオフを理解する。

3. クロック スキューを解析する。

4. ロジックの配置があまりに離れすぎている場合、クリティカル ブロックのフロア プランニングを行う。（フロアプランニングは必要な場所にのみ実行します。）

5. 旧バージョンのソフトウェアで設計された場合や、デザイン変更の前にそのデザインに対してエリア グループを作成していた場合は、それらエリア グループを除去することを考慮する。

6. ブロック RAM や DSP48E スライスなどのハード IP ブロックの配置を考慮する。

## 結論

Virtex-5 FPGA は高性能なデザイン向けに最適化されており、また、ISE ソフトウェアは、デザイン クロージャを素早く達成して生産性を改善し、デザインを効率的に実行するための機能を備えています。ザイリンクスは、デザイン性能を改善する ISE Fmax テクノロジをベースとする包括的なソフトウェア ツール群を提供しています。このような良い条件下でも、事前に効率的なコーディング スタイルを実践し、タイミング制約を定義してリソース プランニングを行うことで、下流工程でのタイミング要件の達成がさらに効率化されます。

# Get on Target

**パートナーの皆様

御社の製品・サービスを

Xcell journal 誌上で

PRしてみませんか？**

Xcell Journal は、プログラマブル ロジックユーザーへ、ザイリンクス製品／ツールの最新情報をはじめ、システム／アプリケーションの解説、サービス／サポート情報、サードパーティ各社のツール情報などをお届けしています。

現在では日本各地の7,000名を超える幅広い分野のエンジニアの皆様に愛読いただいており、ザイリンクスが主催・参加するイベントでも広く配布しています。

貴社製品／ソリューションのプロモーションに非常に効果的なメディアです。

広告掲載に関するお問い合わせ先

**有限会社 エイ・シー・シー**

Xcell 広告係までe-mailでお願いいたします。

e-mail:t.sohyama@jcom.home.ne.jp

# Clock Management in Virtex-5 Devices

# Virtex-5 デバイスにおける クロック管理

デジタル DCM とアナログ PLL の並列実装による柔軟かつ最適な

クロック管理ソリューション

Ralf Krueger

Sr. Staff Applications Engineer

Xilinx, Inc.

[ralf.krueger@xilinx.com](mailto:ralf.krueger@xilinx.com)

FPGA の大規模化に伴い、オンチップ クロック配信の品質がますます重要になっていきます。クロック スキューとクロック遅延はデバイスの性能に影響を与え、これらを従来のクロック ツリーで管理するのは、デバイスが大きくなるほど難しくなります。

従来、ザイリンクスの Virtex™-4 デジタル クロック マネジメント (DCM) やミックスド シグナル フェーズ ロック ループ (PLL) などのソリューションを利用して、クロック ツリーのスキューを除去し、周波数を合成していました。しかし、いずれのソリューションにもそれぞれ長所と短所がありました。

Virtex-5 デバイスは、FPGA で初めて、クロック管理タイル (CMT) にデジタル DCM とアナログ PLL が並んで実装されています。これにより、開発するアプリケーションに合わせて最適なクロック管理ソリューションを選択できるようになりました。

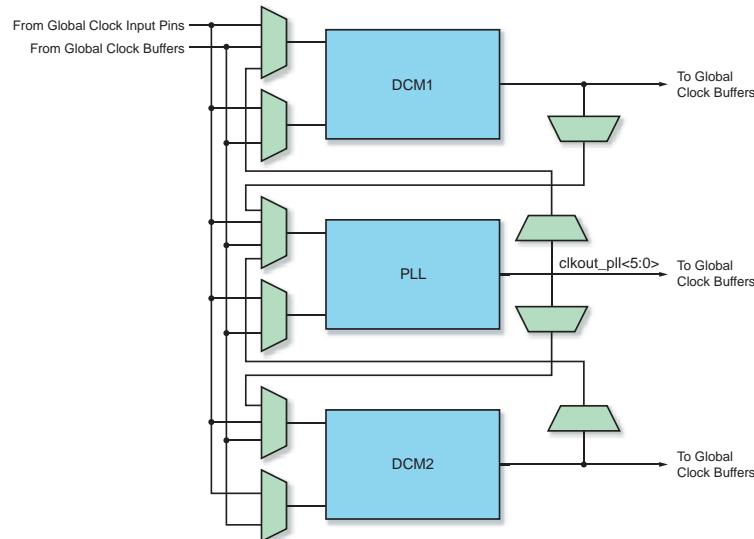

Virtex-5 デバイスは最大 6 個の CMT を装備しています。1 個の CMT には 2 個の DCM と 1 個の PLL があります。2 個の DCM のうちいずれか一方、または PLL を、スタンドアロン モジュールとして使ったり、相互に連携させて使ったりすることができます。スタンドアロン モジュールとして使用する場合は一般的に、アプリケーションに

よってどのクロック管理ソリューションを使うかを決定します。たとえば、DCM は、ファイン位相シフトや動的位相シフト、最大 VCO 周波数に依存しない倍倍／分周機能をサポートします。しかし、PLL は入力クロック ジッタをフィルタリングし、より高周波数の幅広い出力周波数をサポートするうえ、消費電力が低いというメリットがあります。

また、DCM と PLL は相互に連携する設計になっています。PLL は、DCM への入力もしくは出力クロックをクリーンアップするのに役立ちます。各 CMT 内の専用リソースは、お互いに接続しても FPGA クロックのスキューを適切に除去します。CMT は Virtex-5 アーキテクチャの中心コラムに置かれています。ここに配置することで左右の対称性が高まり、すべての DCM や PLL までのクロック ルートを最適にできるためです（図 1）。

## DCM

Virtex-5 の DCM は、ゼロ伝播遅延バッファ、クロック分周／倍倍機能、固定および動的ファイン位相シフト、多重フェーズの入力クロックを提供します。完全な差動グローバルクロック ツリーと出力信号間の低スキューに加え、アプリケーションの各種クロックはデバイス全体に効率的に配信されます。各 DCM は、デバイス内の 32 本のグローバル クロック配線ネットワークのうち、9 本を駆動できます。

グローバル クロックの配信ネットワーク

は、負荷の違いに起因するスキューを最小限に抑えます。DCM 出力クロックのサンプルを監視することで、DLL は配線ネットワーク上の遅延を補正し、外部入力ポートからデバイス内の個々のクロック負荷への遅延を効果的に除去します。

DCM は、ユーザーのソース クロックに対する遅延をゼロにするほか、多重フェーズのソース クロックを提供します。DLL はクロック ダブルとしての役割を果たしたり、ユーザーのソース クロックを最大 16 まで分割することができます。また、DCM はクロック ミラーとして機能することもできます。DCM の出力をオフチップで駆動してから再度オンチップに戻すことで、DCM を使って複数デバイス間のボードレベルのクロックのスキューを除去できます。

もう 1 つのサブモジュールでは、DCM の出力クロックを少しづつ（そのクロック周期の 256 の 1）位相シフトする機能を提供します。この多機能デジタル フェーズ シフト (DPS) は、固定、可変ポジティブ、可変センタ、直接の 4 種類のモードで操作可能で、高い柔軟性を実現しています。DCM のデジタル周波数合成 (DFS) モジュールは、周波数の倍倍および分周により入力プロックから得られる CLKFX と CLKFX180 の 2 つの出力を提供します。有効な乗算 (M) 値と除算 (D) 値を指定することで、DFS モジュールは周波数計算機を通してそれらをインプリメントします。たとえば、M の値 19 と D の値 8 から、ソース クロックの乗数は 2.375 となります。

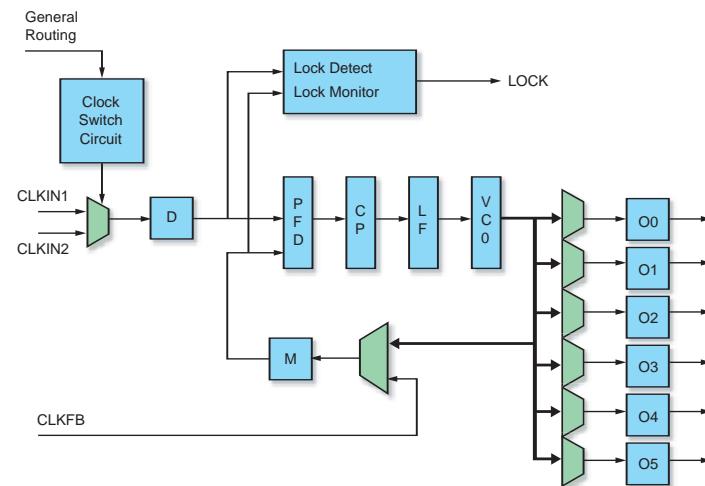

## PLL

CMT の PLL は、クロック ネットワークのスキー除去、周波数合成、ジッタ低減をサポートするミックスド シグナル ブロックです。図 2 の PLL ブロック図は、各コンポーネントの概略図です。

入力マルチプレクサ (MUX) は、グローバルクロック ピンか、グローバル クロック ツリー、または、DCM のいずれか 1 つからリファレンス クロックとフィードバック クロックを選択するために使います。各クロック入力はプログラマブル カウンタを持っています。このカウンタはリファレンス クロックをプリスケールし、広範囲な周波数合成を可能にします。

位相周波数検出器 (PFD) は、入力クロックとフィードバック クロックの位相と周波数の両方を比較します。2 つのクロック間の位相および周波数誤差に比例して信号が生成され、この信号を使用してチャージ ポンプとループ フィルタを駆動することで、VCO への基準電圧を生成します。PFD からの Up 信号または Down 信号により、VCO の動作周波数を高くするか低くするかが決定されます。

PFD が、入力クロックとフィードバック クロックの位相と周波数がアライメントされたと判断すると、ロック信号が立ち上げられ、PLL 出力クロックが有効であることを示します。VCO は電圧や温度の変動を補正し続けます。フィードバック パスの M カウンタは、フィードバック クロックを制御し、VCO 周波数を目的の周波数まで倍増します。VCO 出力クロックは 6 つの出力カウンタを駆動します。各カウンタは、アプリケーション デザインに最適なさまざまな周波数を生成するため、個別にプログラミングすることができます。

また、クロック切り替え（スイッチオーバー）や、位相シフト、多彩なデューティ サイクル、バンド幅の制御もサポートされています。操作前、または操作中に、2 つの入力クロックのどちらか 1 つを動的に選択できます。多くの場合、クロックのフェーズを切り替えて使う必要があります。VCO は、それぞれ  $45^\circ$  の 8 つの位相シフト クロックを備えています。VCO の周波数が高いほど、O カウンタから出力されるクロックの位相シフト

の分解能は小さくなります。

各出力カウンタは、別々に位相シフトしたクロックを用意するため、個別にプログラミングできます。PLL は、各出力カウンタに 50/50 以外のディスクリート デューティ サイクルを生成することもできます。分解能と可能な出力デューティ サイクルは、除算値で決まります。出力除算値が高いほど、出力デューティ サイクルの分解能は高く設定されます。

## 結論

Virtex-5 FPGA では、クロック管理にデジタルとアナログのどちらかを選択することが

可能です。目的のアプリケーションに応じて、いすれかのモジュール、あるいは両方のモジュールを使うことで、これまで以上に選択の幅が広がります。

豊富なクロック ツリー リソースを備える Virtex-5 デバイスは、高いファンアウトと高性能なクロックを必要とするシステムレベルの設計を、大幅に簡素化し改善します。Virtex-5 デバイスは、従来の FPGA にはないパワフルな周波数合成、位相シフト、クロック デスキー機能を備えています。ソフトウェアも包括的にサポートされており、過去の世代の FPGA と比較して、はるかに大規模、高速、複雑なデザインを実現できるのです。

図 1 Virtex-5 CMT ブロック図

図 2 PLL ブロック図

# Reduce Power with Virtex-5 FPGAs

# Virtex-5 FPGA による消費電力の 削減

世界初 65nm FPGAが提供する

パフォーマンスに影響しない低消費電力機能

Derek Curd

Senior Staff Applications Engineer,

Advanced Products Division

Xilinx, Inc.

[derek.curd@xilinx.com](mailto:derek.curd@xilinx.com)

ザイリンクスは、Virtex™-5 ファミリの発表により、FPGA ユーザーに新たなテクノロジと機能を提供し、再び業界の牽引役を果たしています。65nm FPGAへの移行は、コストの削減や高性能化、ロジック容量の増大というプロセス ジオメトリの微細化メリットをいっそく拡大することになります。しかしながら、これらのメリットは先進のシステム設計者にとってエキサイティングなチャンスである半面、65nm プロセス ノードは新たな課題をもたらします。

たとえば、開発するアプリケーションに最適な FPGA を選択する場合、消費電力がますます重要になります。次世代のデザインには、従来とほぼ同じ、あるいはより少ない電力バジェットでより多くの機能、より高い性能を実現することが求められます。

本稿では、消費電力の削減によるメリットについて解説します。また、高パフォーマンスを保つつつ消費電力を最小限に抑える、Virtex-5 デバイスにインプリメントされた多数のプロセスおよびアーキテクチャ上のイノベーションについて紹介します。

## 消費電力低減のメリット

低消費電力の FPGA デザインをインプリメントすることにより、デバイスの熱に関する動作条件を満たすだけでなく、さまざまな利点があります。コンポーネントの仕様を満たすのは性能と信頼性の面で重要なことは言うまでもありませんが、それをいかに達成するかでシステムのコストと複雑さが大きく異なってきます。

第 1 に、FPGA の消費電力を減らすと、部品点数が少なく PCB に占める面積の小さい廉価な電源を使用できます。一般に、高性能な電源システムのインプリメンテーションコストは 1 ワットあたり 0.5 ドルから 1 ドルです。したがって、FPGA の消費電力を低減すれば全体的なシステム コストの削減に直接寄与することになります。

第 2 に、消費電力は熱放散に直接関係するため、低消費電力で動作が可能であればよりシンプルで廉価な熱管理ソリューションを使用できます。デザインがヒート シンクを必要とすることはなく、たとえ必要としても小型

で廉価なヒートシンクで十分です。

最後に、低消費電力で動作するということは、部品点数が少なくデバイスの温度も低いため、システム全体の信頼性が向上します。デバイスの動作温度が10°C下がると部品の寿命が2倍になることからも、高い信頼性が求められるシステムで消費電力と温度を抑えることが、いかに重要なことがわかります。

## 消費電力：課題と解決策

FPGA をはじめとする半導体デバイスの総消費電力は、スタティック消費電力とダイナミック消費電力の合計です。スタティック消費電力は、論理的に「オフ」のときでもトランジスタのソース/ドレイン間から、あるいはそのゲート酸化膜を通して「漏れる」少量の電流、すなわちトランジスタのリーク電流に起します。ダイナミック消費電力は、デバイスのコアや I/O におけるスイッチング中に消費される電力であり、周波数に依存します。

### スタティック消費電力

90nm から 65nm のデバイスに移行するなど、トランジスタの縮小に伴ってリーク電流は増加する傾向があります。また、一般にプロセスノードが新しくなるとチャネル長は短く、ゲート酸化膜は薄くなり、チャネル領域やトランジスタのゲート酸化膜を通して電流がリークしやすくなります。

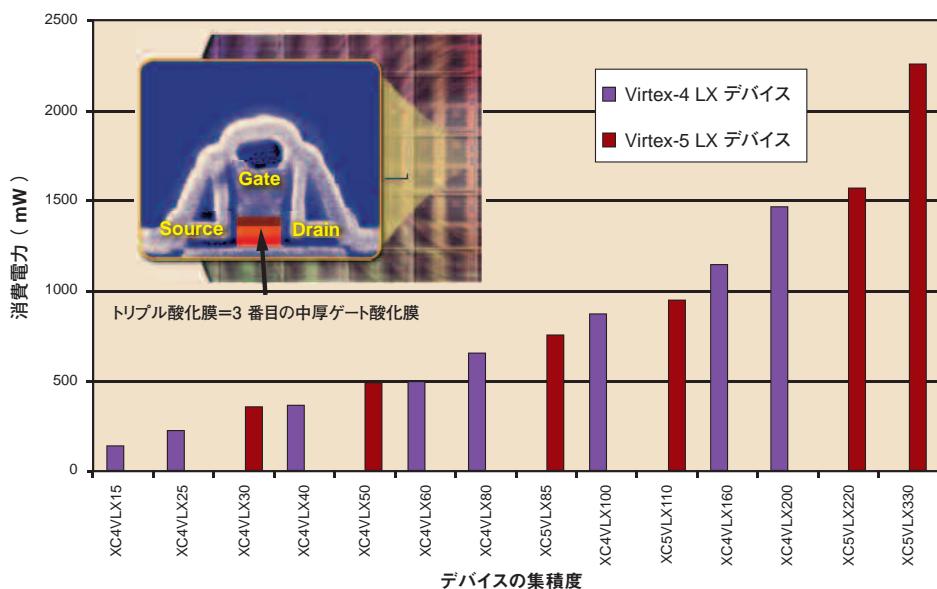

ザイリンクスは、90nm の Virtex-4 ファミリに「トリプル酸化膜」プロセス技術を採用し、ザイリンクスの回路設計者がリーク電流の低減に取り組む際に役立つ素晴らしいツールとなりました。以前の FPGA には、2種類のゲート酸化膜が使用され、薄い酸化膜は FPGA コア内の高性能で低動作電圧のトランジスタに、厚い酸化膜は I/O ブロック内の大型で高電圧に耐えられるトランジスタに用いられました。簡単に言えば、「トリプル酸化膜」とは、薄い酸化膜のコアトランジスタよりはるかにリーク電流の少ない、3番目の中厚ゲート酸化膜トランジスタを追加したもののです。

「中厚酸化膜」トランジスタは、厳しいパ

フォーマンスを求められない回路（例：コンフィギュレーションメモリ）や、ゲートの電圧変動に応えて高速なスイッチング時間を必要としない回路（例：ルーティングパスゲート）用として、デバイスのコアに広範囲に使われています。リーク電流が最も多い薄膜酸化膜のトランジスタは、スピードパスのうち、極めて高速なスイッチング時間を必要とする部分に使用されます。この結果、デバイスの総リーク電流を劇的に低減しつつ、旧世代の FPGA に比べて大幅な性能改善を達成しているのです。

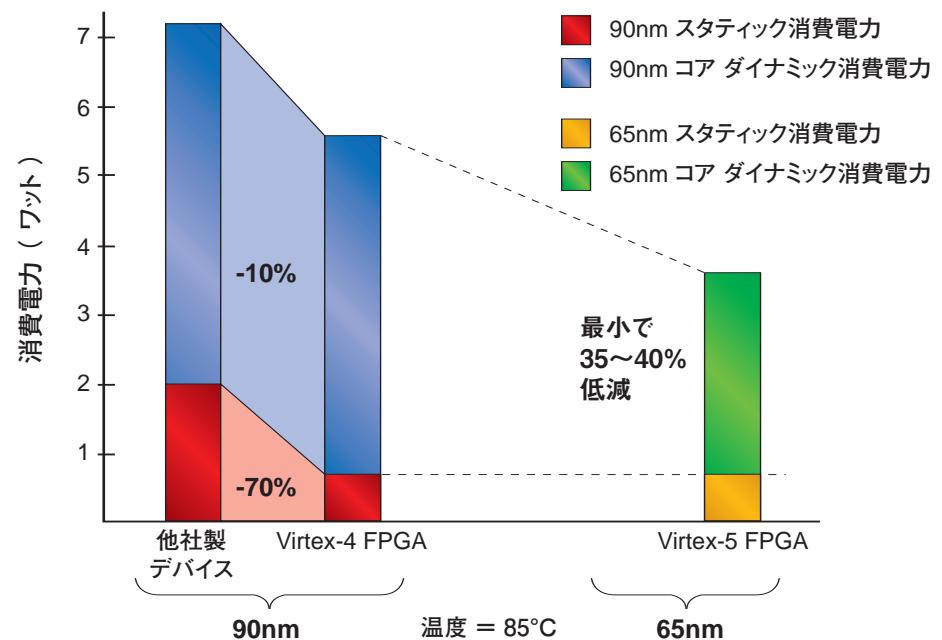

トリプル酸化膜のプロセス技術により、Virtex-4 デバイスは他社製 90nm FPGA と比較して、スタティック消費電力を平均 70% 以上を低減します。Virtex-4 での大成功から、Virtex-5 ファミリでも 65nm プロセスノードのリーク電流を低減させるため、この技術を広範に採用しています。

65nm デバイスはスタティック消費電力が大幅に増えるという業界予測にもかかわらず、トリプル酸化膜プロセスにより、ワーストケース（高温）の動作条件下でも 65nm の Virtex-5 デバイスはほぼ同サイズの 90nm Virtex-4 デバイスに匹敵するスタティック消費電力を達成しています（図 1）。したがって、Virtex-5 ファミリでも他社製の高性能 FPGA よりスタティック消費電力

が格段に優れています。

### ダイナミック消費電力

65nm FPGA には、ダイナミック消費電力の課題もあります。ダイナミック消費電力は次の式で求められます。

$$\text{ダイナミック消費電力} = CV^2f$$

C : ノード スイッチングのキャパシタンス

V : 電源電圧

f : スイッチング周波数

65nm のプロセスノードは、旧来のデバイスより格段に大きなロジック容量とより高い性能を備える FPGA を実現します。つまり、より多くのノードがより高い周波数でスイッチングするわけです。他の条件がすべて同じであれば、これはダイナミック消費電力の増大につながります。

しかし、65nm のダイナミック消費電力については良い点もあります。FPGA のコア電源電圧（V）とノードキャパシタンス（C）は、一般にプロセスノードが新しくなるたびに減少し、旧世代の FPGA よりダイナミック消費電力を大幅に節約できるのです。

Virtex-5 デバイスのコア電源電圧

図 1 85°Cでのスタティック消費電力比較

( $V_{CCINT}$ ) は、Virtex-4 デバイスで使われていた 1.2V から 1.0V に低減されています。また、ノード キャパシタンスは、トランジスタの小型化に伴う寄生キャパシタンスの低下と、ロジック間のより短く容量性の低いインターフェース（相互接続）によって減少する傾向があります。さらに、Virtex-5 デバイスは配線キャパシタンスを最小限に抑えるために、メタル インターフェース レイヤ間に Reduced-K 誘電材料を使用しています。

Virtex-5 デバイスに対する平均ノード キャパシタンスは、Virtex-4 デバイスより 15% 低減されると予想されます。電圧低

を低減させます。

- 従来のデバイスには 4 入力のルックアップ テーブル (LUT) が使われていましたが、Virtex-5 のコンフィギュブル ロジック ブロック (CLB) は、6 入力 LUT のロジック アーキテクチャをベースにしています。つまり、各 LUT 内により多くのロジックがインプリメントされることでロジック段数が少なくなるため、ロジック ファンクション間により高キャパシタンスの配線を行う必要がなくなります。

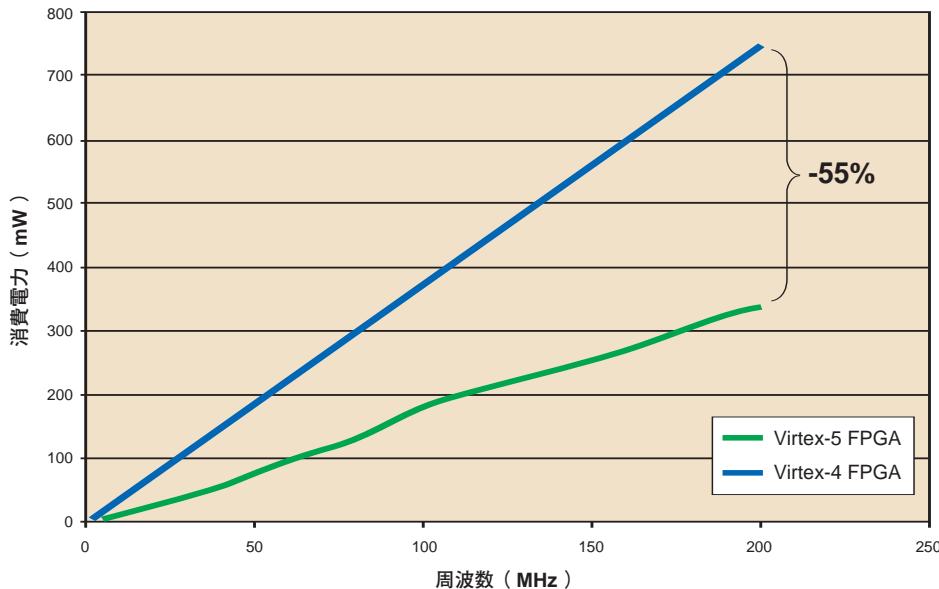

ノード キャパシタンスを減らすことで、コアのダイナミック消費電力を削減します。図 2 は、Virtex-5 デバイスと Virtex-4 デバイスにそれぞれ 1,024 個の 8 ビット カウンタを搭載したベンチマーク デザインから、コアのダイナミック消費電力を測定した図です。シリコンで実際に測定したこれらの値から、プロセスとアーキテクチャのメリットを合わせると、ダイナミック消費電力の低減率は 50% を超えることがわかります。

## ハードIP ブロック

Virtex-5 デバイスは、業界のどの FPGA よりもハードIP ブロック（よく使われるファンクション専用の回路）を多数備えています。ハード化された IP ブロックを使う FPGA デザインは、これらのファンクションを汎用 FPGA ロジックにインプリメントする場合と比較して、消費電力の節約量が大きくなります。

FPGA ファブリックとは異なり、専用ブロックは必要なファンクションをインプリメントするためのトランジスタのみで構成されます。しかもプログラマブル インターフェースがないため、配線キャパシタンスは最小限です。トランジスタの個数が少なくノード キャパシタンスが低いことから、静态消費電力とダイナミック消費電力の両方にメリットがあります。専用ブロックは、汎用 FPGA ファブリックを使用した同等のインプリメンテーションと比べて、わずか 10 分の 1 の消費電力で同じファンクションを実行できます。

Virtex-5 デバイスでは、新タイプの専用ブロックを追加しただけでなく、新機能によってパフォーマンスを改善し消費電力を低減させるため、Virtex-4 デバイスに存在した多くのブロックのデザインを変更しました。たとえば、Virtex-4 ファミリの 18Kb ブロック RAM メモリは、Virtex-5 デバイスでは 36Kb ブロック RAM に拡張されています。ブロック RAM はそれぞれ、Virtex-4 デザインへの下位互換性を考慮し、2 個の独立した 18Kb メモリに分割できます。

また、消費電力の観点から、18Kb のサブブロックはそれぞれ 2 個の 9Kb 物理メモリアレイから構成されています。ほとんどのブ

図 2 カウンタ ベンチマーク デザインのダイナミック消費電力比較

減のメリットと合わせると、Virtex-5 デバイスに対するコア ダイナミック消費電力は、少なくとも 35~40% 低減されることになります。

65nm への「プロセス縮小」だけでもダイナミック消費電力は 35~40% 低減しますが、Virtex-5 デバイスの革新的アーキテクチャにより、あらゆるデザインに対して消費電力がさらに節約されます。ダイナミック消費電力につながるノード キャパシタンスのほとんどは、ロジック ファンクション間の配線またはインターフェースに起因します。Virtex-5 の新しいアーキテクチャは、基本的に次の 2 通りの方法で配線キャパシタンス

- Virtex-5 の配線アーキテクチャは、対角方向の対称配線を持ち、すべての CLB は対角方向の隣接 CLB を含むあらゆる隣接 CLB に「ワン ホップ」で直接接続することが可能です。ロジック ファンクション間に接続が必要な場合、従来の配線アーキテクチャは、接続するのに 2 つ以上のホップを必要としたましたが、Virtex-5 ではより低容量の「ワン ホップ」接続ですみます。

6 入力 LUT アーキテクチャと配線パターンの改善により、純粋に 65nm プロセスへの移行によって達成されるレベル以上に平均

ロック RAM コンフィギュレーションでは、ブロック RAM への読み出しまだ書き込み要求が一度にアクセスするのは、1 つの 9Kb 物理メモリのみです。したがって、もう一方の 9Kb メモリは、アクセスされていない間、「電源オフ」の状態にできます。その結果、65nm プロセスへの移行に伴う消費電力の低減に加え、さらに 50% 近くを低減させることができます。このような「ピンポン式」の 9Kb ブロックへのアクセスは、新型ブロック RAM アーキテクチャに固有のものであり、この機能を活用するためにユーザーやソフトウェアによる制御は必要ありません。これはダイナミックかつ自動的に行われ、ブロック RAM を使うすべてのデザインに対して、ブロック パフォーマンスを損なうことなく消費電力を劇的に減らす効果があります。

Virtex-5 デバイス内の専用 DSP エレメントも、デザインを全面的に見直し、高性能化と低消費電力を実現しています。スライス単位でみた場合、新しい Virtex-5 の DSP スライスは、Virtex-4 の DSP スライスと比較してダイナミック消費電力が約 40% 低減されています。これは主に、前述の 65nm プロセスの電圧とキャパシタンスのスケーリング係数によるものです。

また、Virtex-5 の DSP スライスの機能向上とインターフェイス幅の拡張によって、多くの DSP 動作でダイナミック消費電力がさらに低減されます。一般に、新しい DSP スライスの機能をフルに利用することで、ダイナミック消費電力を最高 75% 低減できます。DSP アプリケーションのデザインでなくとも、さまざまな標準ロジック ファンクション（カウンタ、加算器、バレル シフタ）に DSP スライスを使うことで、標準的な FPGA ロジックにインプリメントする場合より大幅に消費電力を抑えられることを覚えておいてください。

デザインを改良した専用ブロックの最後の例として、Virtex-5 ファミリの LXT プラットフォームは 3.125Gbps で動作する統合型のマルチギガビット シリアル トランシーバを備えています。これらの「SERDES」ブロックは、消費電力を削減することに重点を置いてインプリメントされています。Virtex-5 LXT デバイスの全二重トランシーバは、そ

図 3 代表的なデザインに対する FPGA 間の消費電力比較

れぞれ 3.125Gbps で総消費電力はわずか 100mW 以下であり、Virtex-4 のシリアル トランシーバと比べておよそ 75% 低減されています。

ック消費電力は 50% 以上低減されます。さらに、これまでにない多数の専用ブロックを活用すれば、消費電力をいっそう低減させることができます。

Virtex-5 デバイスの低消費電力をフルに活用する方法は、<http://japan.xilinx.com/power/> をご覧ください。

## 結論

ザイリンクスは、20 年以上前に最初の FPGA を開発して以来、長年にわたり技術革新に努めてきました。ザイリンクスがディープサブミクロン技術における消費電力の低減を最優先課題にした初の FPGA メーカーとなったのはごく自然なことです。Virtex-4 ファミリと同様、Virtex-5 デバイスはプロセスとアーキテクチャに多数の革新的技術を採用し、パフォーマンスを 30% 以上改善しながら、消費電力を最小限に低減しています。

図 3 からわかるとおり、Virtex-5 ファミリのスタティック消費電力は Virtex-4 デバイスに匹敵するレベルで、また、他社 FPGA より優れていることも明らかです。また、業界唯一の 65nm FPGA である Virtex-5 デバイスは、他社の高性能 FPGA より、コア ダイナミック消費電力が最低でも 35~40% 低減されます。新しい 6 入力 LUT と対角方向の対称配線など、アーキテクチャ面でのイノベーションにより、実際のコア ダイナミ

## Xilinx Power Estimator (XPE)

2006 年 1 月に発表されたスプレッドシートベースの消費電力見積もりツール、Xilinx Power Estimator (XPE) は、Virtex™-4 に加え、現在は Virtex-5 と Spartan™-3E FPGA ファミリをサポートしています。XPE は、デザイン前の消費電力見積もりツールとして Web Power ツールに継ぐツールであり、ザイリンクスの新しい FPGA ファミリすべてに利用可能です。XPE は、従来の消費電力見積もりツールよりユーザーインターフェイスが改善され、精度を向上し、重要データをよりわかりやすく表示するように改善されています。

XPE のサマリ ページでは、まずリソース タイプごとに、次に電源電圧ごとに電力使用量に関する完全なサマリが表示されます。サマリ ページのナビゲーション ボタンを使って、詳しい情報を容易に閲覧することができます。XPE はまた、電力消費量をグラフィカルに認識できるように、自動的にグラフの作成・表示を行います。

ザイリンクスは、XPE の最初のリリース後、何度か新バージョンを発表し、機能の追加と精度の向上を繰り返してきました。すべてのバージョンは、<http://japan.xilinx.com/power/> から入手が可能です。

POWER

# Applying Compact Thermal Models コンパクト熱モデル への適応

ザイリンクスが提供する FPGA 热管理用の各種ツール

Abu Eghan

Principal Engineer

Xilinx, Inc.

[abu.eghan@xilinx.com](mailto:abu.eghan@xilinx.com)

ザイリンクスは、FPGA のスタティック消費電力とダイナミック消費電力を低減させるため、シリコン レベルで飛躍的な進歩を遂げてきました。しかし、上位ファミリに移行するたびに、トランジスタの集積度や性能を高めるため機能を小型化したこと、最上位モデルでは熱の問題が生じます。FPGA デバイスでは、消費電力の低減は重要課題のひとつです。

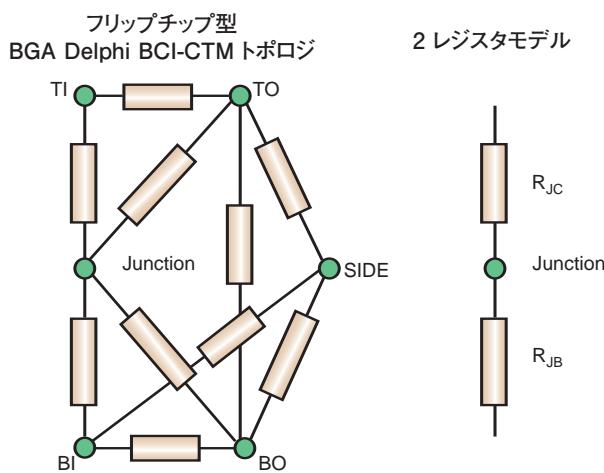

消費電力が高く熱バジェットのマージンが低い場合、温度予測が不正確だと設計者は期待どおりのデザインを作成できません。高性能 FPGA に採用されているフリップチップ パッケージは複数の熱流路を持ち、熱効率に優れています。温度を見積もる際、熱抵抗の基本的な「ワン レジスタ」の数値、シータ ja ( $\Theta_{ja}$ ) を使うだけでは、パッケージの熱効率を正しく予測できません。

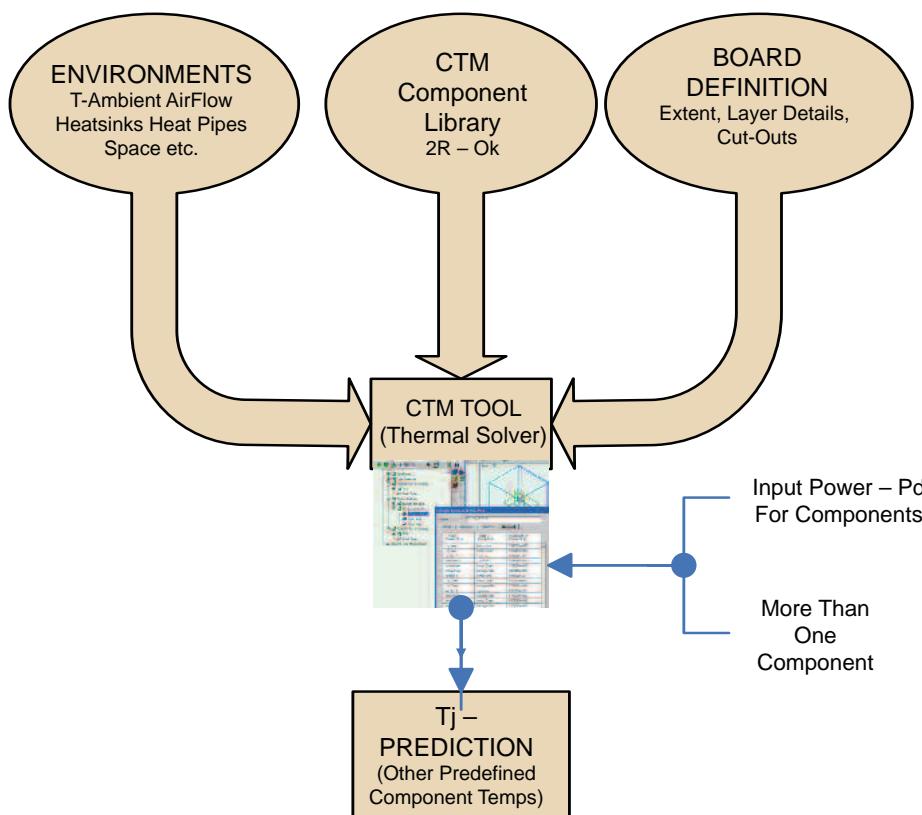

したがって、エンドユーザー環境でのコンポーネントの  $T_j$  予測値を得るには、もっと別のより正確な方法が必要です。そこで便利なのが、境界条件非依存型コンパクト熱モデル (BCI-CTM) です。このモデルは、より速く正確に  $T_j$  を予測することが可能です。

本稿では、さらに高速化、高集積化する FPGA コンポーネントの温度をシステム環境で予測する、より正確な方法について解説します。また、システム設計者とコンポーネント選定者が、デザイン前やインプリメンテーション段階で温度を見積もることを支援する、Virtex™-4 と Virtex-5 デバイスに対するコンパクト熱モデルのアベイラビリティおよびサポートについても紹介します。

## より正確な予測モデルの必要性

システム インプリメンテーションによつては、コンポーネントの実際の  $T_j$  は公表  $\Theta_{ja}$  を用いて算出した予測値と異なる場合があります。予測値は、システム内の環境と周囲の条件に依存するためです。この関係は次の等式で表されます。

$$\Theta_{ja} = \frac{T_j - Ta}{P}$$

これを  $T_j$  の予測式に変換すると次のようにになります。

$$T_j = Ta + P * \Theta_{ja}$$

$\Theta_{ja}$  はデバイスのジャンクション温度と周辺温度間の熱抵抗です。

$T_j$  = デバイスのジャンクション温度

$T_a$  = 周囲温度

$P$  = パッケージの消費電力

## $\Theta_{ja}$ - 誤解の多いモデル

$\Theta_{ja}$  は、既知の  $T_a$  を用いてコンポーネントの  $T_j$  を見積もる際、ほとんどのエンジニアが使ったがる熱パラメータです。しかし、周囲に他のコンポーネントがある大規模なマルチレイヤ システム ボードに採用されているワット数の高いコンポーネントに対しては、この方法では  $T_j$  の予測を誤ることがあります。

熱バジェットのマージンに余裕のあるデザインでは、公表  $\Theta_{ja}$  データを用いた単純予測ではほぼ問題ありません。実際、一般的なボードのほとんどは標準的な最大サーマルボードより効率的であるため、シス

図 1 Analysis Tech 社による  $\Theta_{ja}$  標準環境のインプレメンテーション

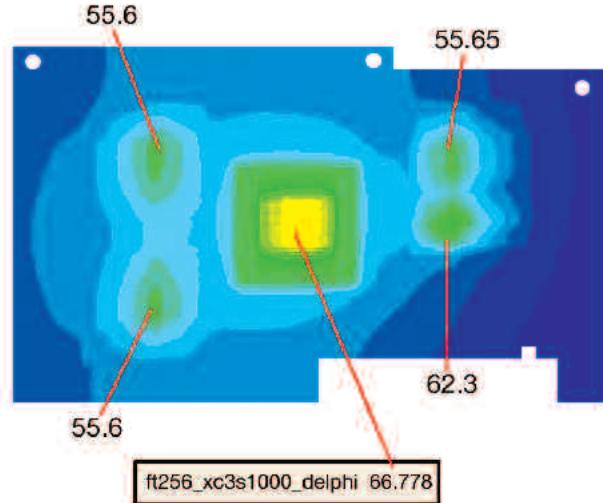

表 1 各種ボードにおける FF1136-XC5VLX50T の  $T_j$  マトリックス

| Xilinx 35 x 35mm<br>FF1136-5VLX50T* |    | ボードサイズ      |               |               |

|-------------------------------------|----|-------------|---------------|---------------|

| ボードの<br>レイヤ数**                      | 4  | 4" x 4" ボード | 10" x 10" ボード | 20" x 20" ボード |

|                                     | 4  | 68.2 °C     | 64.3 °C       | -             |

|                                     | 8  | 63.0 °C     | 50.9 °C       | 48.3 °C       |

|                                     | 12 | 60.4 °C     | 47.0 °C       | 45.7 °C       |

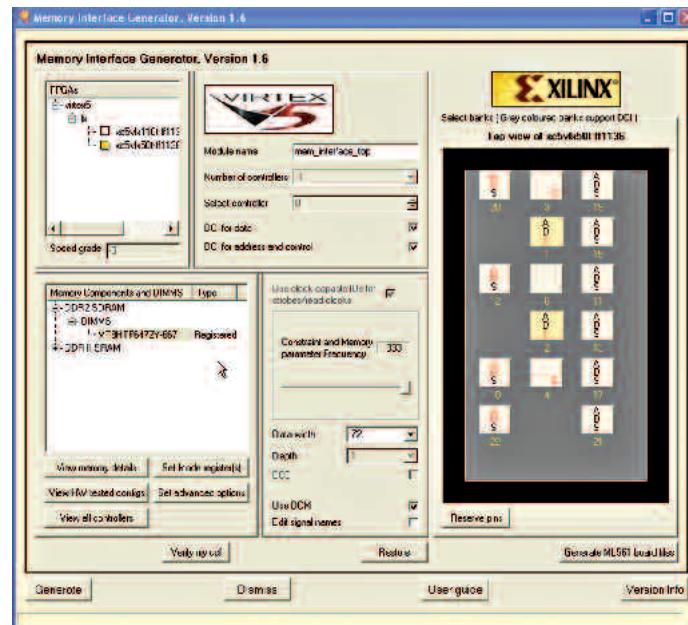

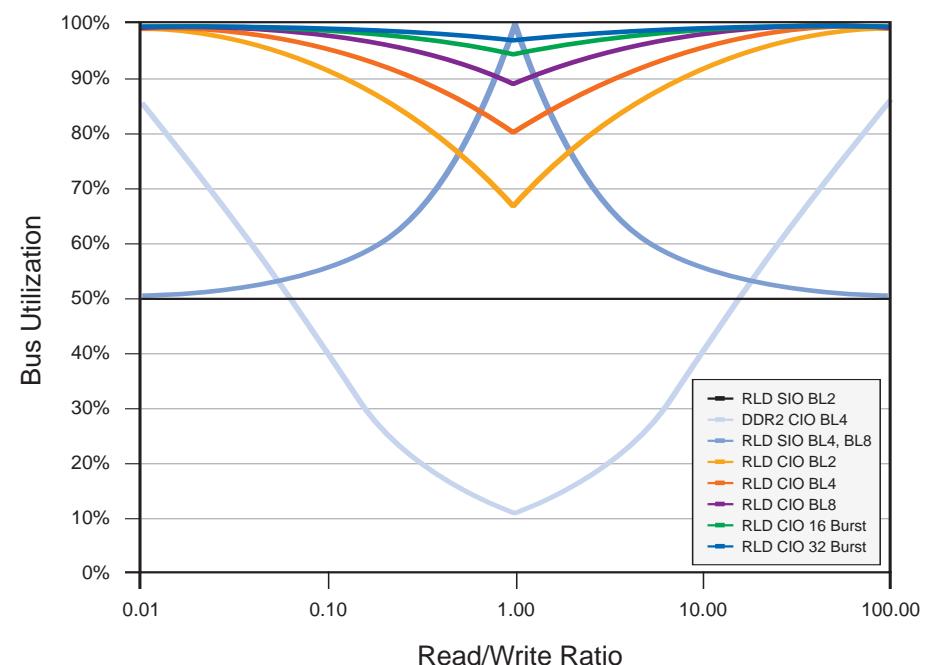

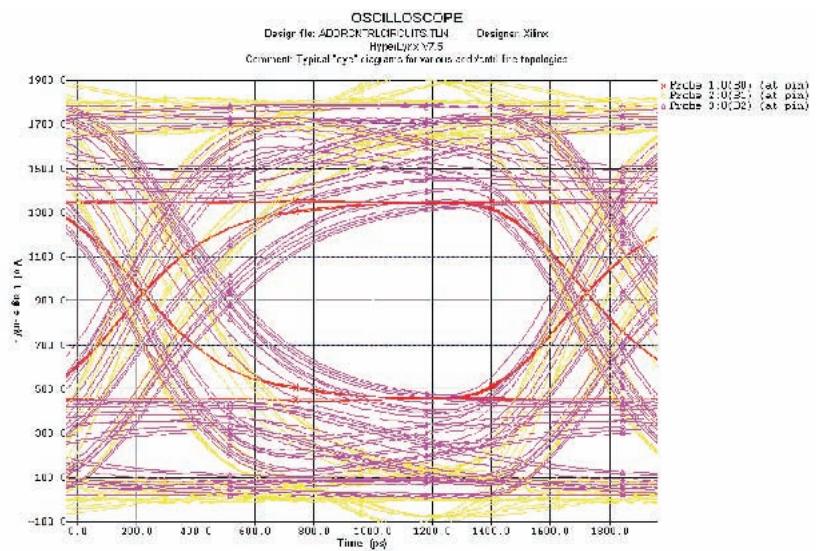

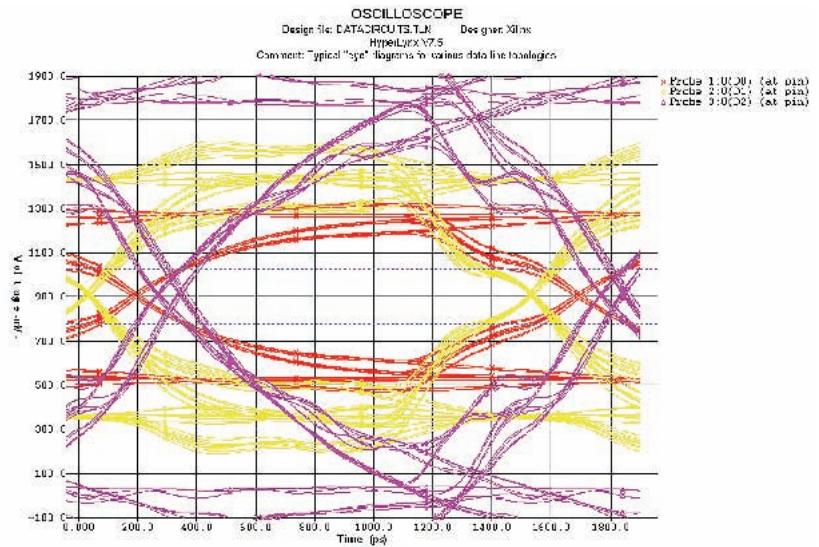

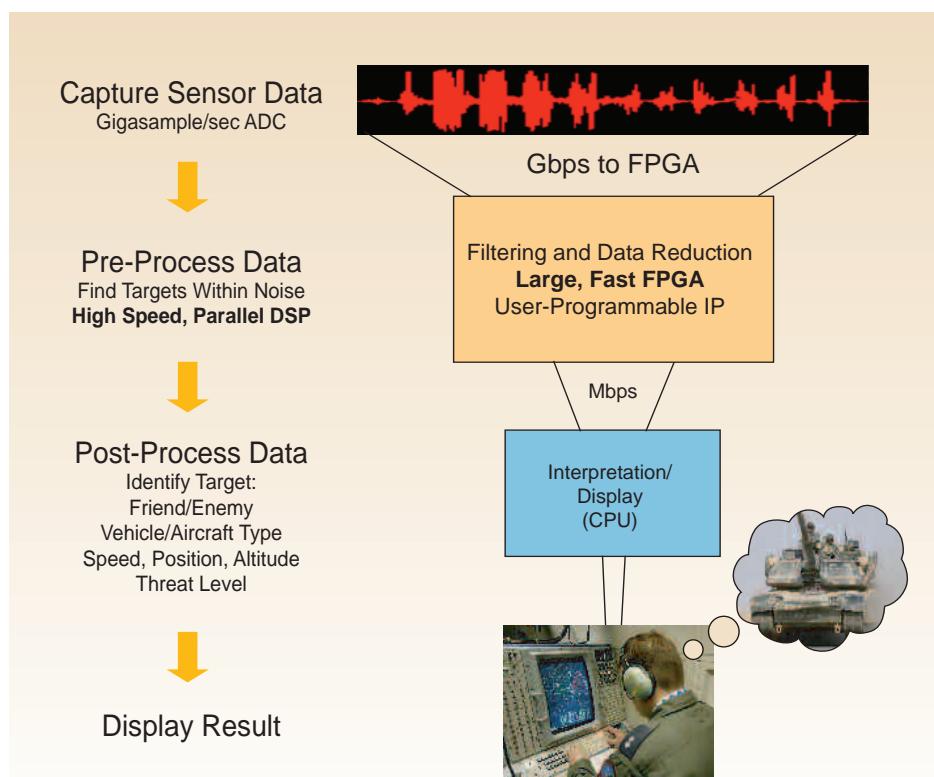

|                                     | 16 | 59.1 °C     | 46.6 °C       | 44.9 °C       |