# Xcell journal

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

ネットワークの

エッジを

ターゲット

**Targeting the Edge

of the Network**

## INSIDE

量産アプリケーション向けの

プログラマブルロジック

FPGA アーキテクチャ

における消費電力

ここまできた

インクジェット プリンタ

Spartan-3A と

Spartan-3AN が実現する

低成本 セキュリティ

ソリューション

Spartan-3A FPGA を

使用した低価格 DDR2 の

インプリメント

**XILINX®**

[japan.xilinx.com/xcell/](http://japan.xilinx.com/xcell/)

## Xcelljournal

|                   |                                           |

|-------------------|-------------------------------------------|

| 発行人               | Forrest Couch<br>forrest.couch@xilinx.com |

| 編集                | Charmaine Cooper Hussain                  |

| アートディレクター         | Scott Blair                               |

| デザイン/制作           | Teie, Gelwicks & Associates               |

| テクニカル<br>コーディネーター | Kevin Kitagawa                            |

| 日本語版統括            | 澤田 修<br>osamu.sawada@xilinx.com           |

| 制作進行              | 竹腰 美優紀<br>miyuki.takegoshi@xilinx.com     |

| 制作                | オフオフ京都 (offoff-kyoto)                     |

| 広 告               | 有限会社エイ・シー・シー                              |

| 印 刷               | ノップス株式会社                                  |

japan.xilinx.com/xcell/

Xcell Journal 60 号

2007 年 8 月 22 日発行

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400ザイリンクス株式会社

〒141-0032

東京都品川区大崎 1-2-2

アートヴィレッジ大崎セントラルタワー 4階

©2007 Xilinx, Inc. All Right Reserved.

XILINX や、Xcell のロゴ、その他本書に記載の商標は、米国およびその他の国々の Xilinx 社の登録商標です。PowerPC は、米国またはその他の国における IBM 社の商標です。ほかすべての名前は、各社の登録商標または商標です。

本書は、米国 Xilinx, Inc. が発行する英文季刊誌を、ザイリンクス株式会社が日本語に翻訳して発行したものです。

米国 Xilinx, Inc. および Xilinx, Inc. 株式会社は、本書に記載されたデータの使用に起因する第三者の特許権、他の権利、損害における一切の責任を負いません。

本書の一部または全部の無断転載、複写は、著作権法に基づき固く禁じます。

Printed in Japan

# Xcell Journal が 栄誉ある LACP 2006 Inspire Award を受賞

同業者の方々から評価されることほど嬉しい、またマガジンの信頼性を高めてくれるものは

ありません。

この度、Xcell Journal 59 号は、米国の団体「League of American Communications Professionals」(LACP) が授与する 2006 Inspire Awards Newsletter & Magazine Competition の総合部門で銅賞を受賞しました。このコンテストは、広報活動に関する優れた意見交換の場である LACP のコミュニケーション専門家らによって審査されます。

LACP のマネージング ディレクタ、Christie Kennedy 氏は次のように語りました。「きわめて厳しい競争のなか、Xcell Journal が入賞したのは大変意義のあることです。2006 年の Inspire Awards には世界 7 カ国から 425 ものニュースレターやマガジンがエントリしました」。

Xcell Journal は、第一印象や図版の美しさ、文章の読みやすさ、創造性、メッセージの明快さ、特長の多様性、対象読者の明確さ、内容の適切さ、情報の探しやすさなど、複数のカテゴリで審査されました。その結果、Xcell は 100 点満点中 92 点を獲得し、“Superb - among the very best judged (優秀 - 最高レベルの審査結果)” という評価を得ました。

「Xcell Journal が今年の LACP Inspire Awards を受賞できたことを大変誇りに思っています」と、ザイリンクスのワールドワイド マーケティング担当バイス プレジデント、Sandee Vij は語りました。「Xcell Journal はザイリンクスの総合的なマーケティング戦略において重要な役割を果たしています。私たちは、Xcell Journal が今後も読者の方々に最大限の価値を提供できるよう、社内スタッフおよびパートナー各社と協力しながら、読者のニーズに即した有益な情報をお届けしていく所存です」。

Xcell の製作チームは、デジタルやオンライン、印刷媒体において業界標準となる革新的なカスタム出版を確立しています。Xcell Journal が世界中のプログラマブル ロジック ユーザーのための出版物として受賞できたのは、ひとえにザイリンクスのスタッフ、パートナー各社、そしてザイリンクス ユーザーが、長年にわたり多くの時間と労力をかけて寄稿してきた結果です。この場を借りて感謝の意を表したいと思います。

Forrest Couch

発行人

# Xcell journal

## VIEWPOINT

成長を続けるザイリンクス PLD ..... 2

## COVER STORY

量産アプリケーション向けのプログラマブル ロジック ..... 3

## FEATURES

### Power Optimization

FPGA アーキテクチャにおける消費電力 ..... 4

### Non-Volatility

ここまでできたインクジェット プリンタ ..... 10

### Security

Spartan-3A と Spartan-3AN が実現する

低コスト セキュリティ ソリューション ..... 14

### Memory Interfaces

Spartan-3A FPGA を使用した低価格 DDR2 のインプリメント ..... 18

## DIGITAL SIGNAL PROCESSING

Virtex-5 SXT を活用する高パフォーマンス

デジタル信号処理 DSP ソリューション ..... 22

公開! FPGA のデジタル信号処理 DSP パフォーマンス ..... 26

FPGA を用いたビデオ監視システムの映像処理 ..... 28

技術の最適な組み合わせによる画像処理システムの開発 ..... 31

## GENERAL

3Gbps eSATA/SATA ベース RAID 5 ソリューションの構築 ..... 34

FPGA プラットフォームでリアルタイムなビームフォーミングを実現 ..... 37

驚異の DSP パフォーマンスを提供する Spartan-DSP シリーズ ..... 42

## INFORMATION

ザイリンクス トレーニング スケジュール ..... 8, 16

ザイリンクス販売代理店 オリジナル トレーニング ..... 24

ザイリンクス ウェブ セミナー ..... 46

ザイリンクス イベント カレンダー ..... 47

## 広告索引

株式会社コンピューテックス ..... 9

シンプリシティ株式会社 ..... 13

株式会社ミッシュインターナショナル ..... 17

アルデック・ジャパン株式会社 ..... 21

有限会社ヒューマンデータ ..... 45

リニアテクノロジー株式会社 ..... 48 - 表 3

Xcell Journal 日本語版のご送付先住所等の変更は:

<http://japan.xilinx.com/xcell/henko/>

Xcell Journal 日本語版の新規定期購読のお申込みは:

<http://japan.xilinx.com/xcell/toroku/>

## TABLE OF CONTENTS, 60号

| COVER STORY                                                                        |                                                                                                                                                     |

|------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p>量産<br/>アプリケーション<br/>向けの<br/>プログラマブル<br/>ロジック<br/>量産市場におけるデザイン セキュリティ<br/>差別化、柔軟性ニーズに応える<br/>Spartan FPGA と<br/>CoolRunner-II</p> <p><b>3</b></p> |

| POWER OPTIMIZATION                                                                  |                                                                                     |

|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

|  | <p>FPGA<br/>アーキテクチャ<br/>における消費電力<br/>低消費電力 FPGA デザインの<br/>現在と未来</p> <p><b>4</b></p> |

| NON-VOLATILITY                                                                       |                                                                                                                  |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

|  | <p>ここまでできた<br/>インクジェット<br/>プリンタ<br/>Spartan-3AN FPGA が可能にする<br/>ユビキタス対応の画期的な<br/>マーキングとプリント</p> <p><b>10</b></p> |

| SECURITY                                                                             |                                                                                                                                                                      |

|--------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | <p>Spartan-3A と<br/>Spartan-3AN が実現<br/>する低コスト セキュリティ<br/>ソリューション<br/>リバース エンジニアリング、<br/>オーバービルディング、クローニング<br/>からデザインを守る Spartan-3<br/>ファミリの新機能</p> <p><b>14</b></p> |

## Xilinx PLDs: On the Go and On the Road

# 成長を続けるザイリンクス PLD

2006 年度は量産分野での広範な採用により記録的成長を達成

Wim Roelandts

CEO and

Chairman of the Board

Xilinx, Inc.

2006 年、ザイリンクスは民生機器と自動車関連の市場において 40% もの成長率を記録し、驚異的な成功を収めました。これら競争の激しい市場で成功できたのは、ザイリンクスの Spartan™ FPGA、CoolRunner™ CPLD、Xilinx® Automotive (XA) の各製品ラインが、ユーザーの量産アプリケーションに広く採用された結果です。

私たちは、PLD 売上の 80% 近くを通信業界に依存していた 1990 年代後半、市場の多角化に着手しました。最初に取り組んだのは民生機器市場で、1998 年に Spartan ジェネレーション FPGA を、1999 年に CoolRunner CPLD を投入しました。当時、量産アプリケーションに FPGA を採用するのはごく稀でした。この市場では一般に、ASSP や ASIC といった標準的な固定ファンクションの半導体デバイスが採用されていました。コスト意識が高い民生機器市場では、ASSP や ASIC と比較して FPGA や CPLD はユニットコストが高すぎると考えられていました。

しかし、ザイリンクスはそうは考えませんでした。私たちはムーアの法則に従い、半導体の回路構造を微細化することにより、ユニットコストを劇的に削減しました。また、世界的な競争激化により新製品を市場に投入するまでの期間が短くなつたことで、民生機器メーカーにとって Time-to-Market (市場投入までの期間) のコンセプトがいっそう重要になりました。この結果、製品開発者はビジネス上の理由から、製品発表後の短期間にで

きるだけ多くの利益と市場シェアを獲得することに主眼を置くようになりました。この Time-to-Market の面でも柔軟性を持つザイリンクスの FPGA と CPLD は、開発に多大の時間を要する ASIC と ASSP と比較して、はるかに有利でした。

プロセス技術の進化により PLD のコストが下がり続けるなか、ザイリンクスは民生用量産アプリケーション とりわけデジタルディスプレイとコンシューマ向けハンドセットの分野でいっそう競争力を高めています。2006 年最後の四半期には、大手取引先のハンドセットメーカー 1 社に 1 カ月だけで 100 万ユニット以上のデバイスを出荷しています。

2004 年には自動車関連市場へも参入し、多角化の幅を広げました。自動車関連業界の厳しい要求を満たすことを目的に開発した業界初の PLD ライン、Xilinx Automotive (XA) ファミリを投入しました。以来、ザイリンクスは自動車関連市場に次々に新製品を送り込んでいます。2006 年にデビューしたある高級車には、インフォテイメントと運転支援機能を実装したザイリンクスの 18 個のデバイスが搭載されました。

今日、ザイリンクスの量産向けデバイスは売上全体の 35% を占めており、年成長率は 38% にもなります。

### 2007 年以降

ザイリンクスが先駆けとなって、半導体業界はパーティカル市場重視に転換し、ユーザーとの関係をシステムアーキテクチャレベルで考えるようになりました。ザイリンクスでは、ユーザーがコスト管理、Time-to-Market、リーダーシップという目標を達成するための革新的かつ柔軟性に優れた魅力的なソリューションを提供することで、ユーザーの複雑な設

計課題の解決に寄与しています。

業界アナリストらは、PLD 業界は民生用電子機器と自動車関連の両市場でさらに成長すると予測しています。民生および自動車関連向けの電子機器業界で新たな需要が発生していることから、現在のアプリケーションだけでなく将来の未知のアプリケーションにも対応できる柔軟なアーキテクチャが求められています。米国の調査会社 iSuppli によると、民生用電子機器業界における PLD と ASIC の市場規模は、2010 年までに 53 億ドルを超えると予測されています。

民生用機器市場における PLD デザインの普及をさらに促すには、コストを追求するだけでなく、アプリケーション特有のソリューションを求めるユーザーのニーズにも応えていく必要があります。民生機器に対する要求が急速に変化するなか、私たちはいっそう完全なソリューションを提供する必要があります。ザイリンクスはこれまで、ユーザー固有のニーズに合った高付加価値のソリューションを提供するため、強力な機能を持つハードおよびソフト IP コアと市場に即した開発プラットフォームに加え、ドメインごとに最適化したプラットフォームをリリースしてきました。

ザイリンクスの PLD は、新興市場において、新しいタイプの多種多様なアプリケーションに適したデザインとして採用されています。すでに、デジタルディスプレイ、携帯電話、PDA、自動車の後席エンターテイメント、衛星ナビゲーションシステムなど、さまざまな民生用電子機器と自動車関連アプリケーションに採用されています。2007 年には、民生機器と自動車関連市場で獲得した量産アプリケーション向けのデザインが生産体制に入ることから、2006 年と同様、この 2 つの市場セグメントはザイリンクスにさらなる成長をもたらすでしょう。

# Programmable Logic in High-Volume Applications

# 量産アプリケーション向けの プログラマブル ロジック

量産市場におけるデザイン セキュリティ、差別化、柔軟性ニーズに応える Spartan FPGA と CoolRunner-II

Kevin Kitagawa

Director, Worldwide Marketing - High-Volume Products

Xilinx, Inc.

kevin.kitagawa@xilinx.com

民生機器や自動車関連などの産業分野の OEM メーカーは、システム コストの低減や、より緊密なシステム統合、Time-to-Market の短縮はもちろんのこと、革新的で独創的な製品の開発を望んでおり、プログラマブル ロジックはこうした量産アプリケーションに対して重要な役割を果たしています。OEM メーカーは、顧客の多種多様にわたる要望に応え、コストとパフォーマンス、製品の特長をバランスさせた OEM 製品を消費者へ提供しています。従来、これらの市場では ASIC と ASSP が使われていましたが、ASIC は初期コストとリスクが高く、また ASSP は柔軟性に欠けるため、Time-to-Market と費用対効果の条件を同時に満たす製品を投入することは困難でした。

ザイリンクスは、Xilinx® Spartan™ シリーズの FPGA や CoolRunner™-II CPLD といったドメイン最適化のプラットフォームを提供し、OEM メーカーの多様な要望に応えてきました。これらの製品ファミリは、量産市場における多彩な顧客ニーズに合わせて作られています。たとえば、CoolRunner-II はバッテリで駆動する消費電力重視のポータブルアプリケーション向けに、不揮発性の Spartan-3AN プラットフォームはシステムの統合やデザイン セキュリティ重視のアプリケーション向けにそれぞれ最適化されています。

す。プログラマブル ロジック デバイスの柔軟性と迅速な Time-to-Market という利点により、OEM メーカーはリスクを最小限に抑え、製品のタイムリな市場投入を可能にします。

## ■ デザイン セキュリティ

企業は全体的な製品コストの削減を迫られ、量産品は労働コストを抑えて製造コストを低減させる方向へ向かっています。OEM 製品には製造コストを低く抑えられるメリットがある半面、委託先のメーカーがデザインを模倣したり発注量以上のユニットを生産したりする新たな問題が発生しています。このような不正に製造されたデバイスが市場に出回ると、OEM メーカーは収益機会を逃すだけでなく、修理や交換のために欠陥品が返却されると追加のコストが発生することになります。

このような状況下では、デザインのセキュリティは不可欠です。ザイリンクスの製品には、量産アプリケーションに最適な多彩なセキュリティ メソッドが組み込まれています。

## ■ 製品の差別化と柔軟性

OEM 製品は、パフォーマンスの改善や柔軟性の向上、さまざまな問題を解決するため進化してきた標準規格に常に適応し続けています。しかしながら、規格の承認プロセスに関わるステークホルダーの増加に伴い、その認可に長い時間がかかることがあります。

OEM メーカーは、製品の仕様を考える際、Time-to-Market と機能セットを秤にかけ、どの規格を優先すべきか難しい判断を迫られます。

デバイスのフィールド アップグレードには、OEM メーカーがデバイスを市場に投入した後でもそれを柔軟にアップデートできるという利点があります。これにより、製品の寿命が大幅に延びるうえ、多額の投資が不要になります。OEM メーカーにとって、新規格の登場で自社製品が市場で陳腐化する心配なく製品を発表できるわけです。

Spartan FPGA と CoolRunner-II CPLD を採用することで、OEM メーカーは規格の変化に素早く適応できます。新たな市場ニーズに応じて、プロトコルやバス、インターフェイスの数など、あらゆる決定を迅速に変更できるのです。

## ■ 結論

移り変わりの激しい量産アプリケーションの分野では、設計エンジニアはこれまでにない難題に直面しています。そのため OEM メーカーは、豊富な機能を備え電力効率に優れているだけでなく、費用対効果と Time-to-Market の面でも優れた製品を提供しなくてはなりません。ドメインを最適化した Spartan シリーズの FPGA と Cool Runner-II CPLD の包括的な製品ポートフォリオから、目的のデザインに最適なプラットフォームを選択することが可能です。

# The Power of FPGA Architectures

# FPGA アーキテクチャ における消費電力

## 低消費電力 FPGA デザインの現在と未来

Tim Tuan

Staff Research Engineer

Xilinx, Inc.

tim.tuan@xilinx.com

Steve Trimberger

Distinguished Engineer

Xilinx, Inc.

steve.trimberger@xilinx.com

FPGA の消費電力が低減すると、信頼性の向上や冷却コストの削減、電源の簡易化、ポータブル システムにおけるバッテリの長寿命化など、数多くの利点が得られます。さらに、パフォーマンスを犠牲にすることなくデザインの消費電力を低減するには、電力効率に優れた FPGA アーキテクチャと、アーキテクチャの特長を活かした設計手法が必要です。

本稿では、FPGA の消費電力や、現在利用できる低消費電力の機能、消費電力に影響を与えるユーザーのさまざまな選択肢を概説すると共に、電力効率に優れた未来の FPGA に向けて近年どういった研究が行われているかをご紹介します。

### 消費電力の種類

FPGA の消費電力には、ダイナミック消費電力とスタティック消費電力の 2 種類があります。ダイナミック消費電力は、信号がキ

ヤパシタンス ノードを充電すると散逸します。これらキャパシタンス ノードは、ロジック ブロック、インターフェクト ファブリックの配線（ワイヤ）、外部パッケージ ピン、もしくはチップの出力によって駆動されるボードレベル トレースに存在します。FPGA の総ダイナミック消費電力は、すべてのキャパシタンス ノードを充電することで発生する消費電力の合計です。

一方、スタティック消費電力は、回路の活動とは関係なく、トランジスタのリーク電流もしくはバイアス電流として散逸します。総スタティック消費電力は、FPGA 内の各トランジスタのリーク電力とすべてのバイアス電流の合計です。ダイナミック消費電力は駆動されるキャパシタンスの量に依存するため、トランジスタのサイズが小さくなればダイナミック消費電力は改善されます。ところが、トランジスタが小型になるほどリーク電流は増えるため、スタティック消費電力は

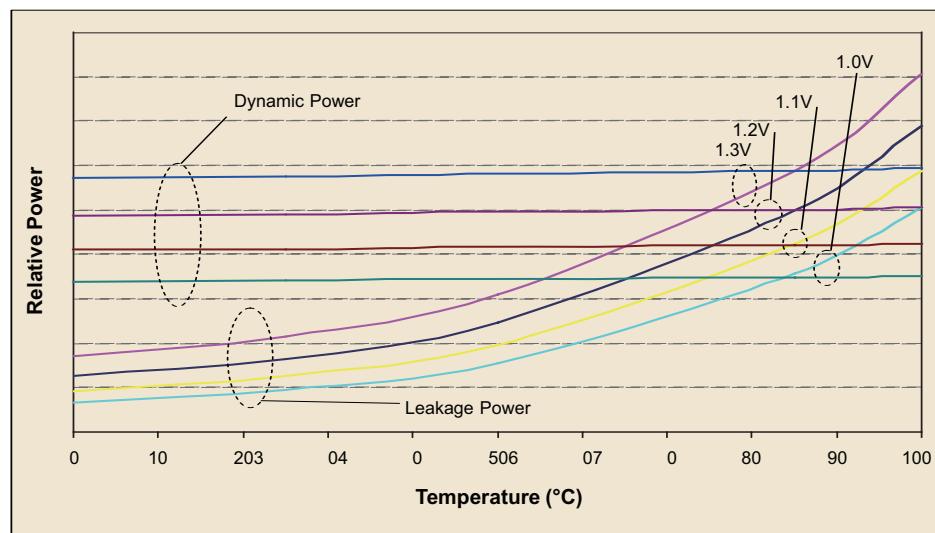

かえって増加します。この結果、集積回路の総消費電力に占める割合はスタティック消費電力のほうが高くなりつつあります。消費電力は、図 1 に示すように、電源電圧と温度によって左右されます。FPGA の電源電圧を減らすと、ダイナミック消費電力は二次関数的に減少し、リーク電力は指数的に減少します。また、温度が高くなるほどリーク電力は指数的に増加します。たとえば、85 °C から 100 °C に上昇した場合、リーク電力は 25% 増加します。

### 消費電力の内訳

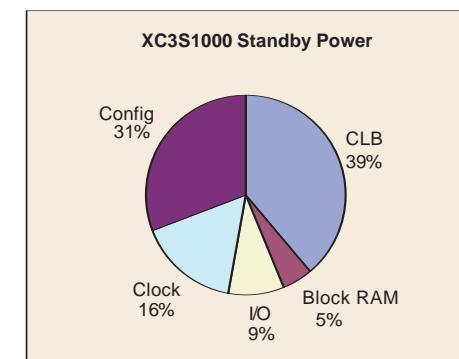

電力が主にどこで消費されるかを理解するため、FPGA の総消費電力の内訳を見ていきましょう。FPGA の電力はデザイン、つまり部品ファミリやクロック周波数、トグルレート、リソース使用効率に依存します。ここでは、例として Xilinx® Spartan™-3

XC3S1000 FPGA を使い、クロック周波数 100MHz、トグル レート 12.5%、リソース使用効率に数多くの実デザインをベンチマークして決定した典型的な数値を使って説明します。

図 2 は、XC3S1000 FPGA のアクティブ電力とスタンバイ電力それぞれの内訳です。アクティブ電力とは、高温時におけるアクティブ デザインの電力（ダイナミック消費電力とスタティック消費電力）です。スタンバイ電力とは、名目温度におけるスタンティック消費電力からなるアイドル デザインの電力です。当然、アクティブ電力とスタンバイ電力の両方で最大のコンポーネントは CLB ですが、他のブロックも大量の電力を消費します。I/O とクロック回路だけで総アクティブ電力の 3 分の 1 を占め、より高出力の I/O 規格を使う場合はさらに高くなります。

総スタンバイ電力の半分近くはコンフィギュレーション回路とクロック回路によって消費され、その主な原因はバイアス電流です。したがって、チップの総消費電力を削減するには、電力を消費する主な部品すべてに対応するため複数の対策を講じる必要があります。

## 低消費電力に向けたデザイン

FPGA のデザインには、消費電力に配慮した設計手法が多数使われています。FPGA 内のトランジスタの 3 分の 1 はコンフィギュレーション メモリ セルで占められることがあるため、ザイリンクスは Virtex™ ファミリに低リーケークの “中厚酸化膜” トランジスタを採用することでメモリ セル内のリーケークを減らしています。また、スタティック消費電力を低減する目的から、チャネル長が長く、しきい値が高いトランジスタを用いています。ダイナミック消費電力には、低キャパシタンス回路とカスタム ブロックで対応しています。DSP ブロック内の乗算器は、FPGA ファブリックで作られた乗算器の 20% 未満の消費電力で済みます。

FPGA に組み込まれている部品以外に、FPGA の消費電力に影響を及ぼすデザイン上の選択肢はたくさんあります。次に、いくつかの選択肢を見ていきましょう。

## 消費電力の見積もり

低消費電力のデザインを実現するうえで重要なステップの 1 つが、消費電力の見積もりです。FPGA の消費電力を知るための最も正確な方法はハードウェアによる測定ですが、あらかじめ見積もることで高消費電力モジュールを判別できるうえ、デザイン サイクルの初期に消費電力バジェットを確認できて便利です。

Xilinx Power Estimator (XPE) や Xilinx Power Analyzer (XPA) など、消費電力を見積もるためのツールがいくつかあります。XPE では、シンプルなユーザーインターフェイスを通して消費電力を簡単に見積もることができます。これはロジック

セルの数や、ブロック RAM の数、平均的なスイッチング アクティビティなどの高水準な統計に基づく見積もりです。XPA はスイッチング アクティビティのシミュレーションと、配置・配線後に生成される正確なユーティリゼーション統計に基づいて消費電力を詳細に見積もります。どちらのツールを使うかは、利用できる設計情報と見積もりに求められる精度によって選択します。

図 1 に示すとおり、外的な要因の中にも、消費電力に指紋的な影響を及ぼすものがあります。環境がごく少し変化するだけで消費電力の見積もりが大きく変わることがあるのです。消費電力見積もりツールを使って完全に正確な見積もりを得るのは困難ですが、高消費電力のブロックを突き止めて

図 1 消費電力と電圧／温度の相関関係

図 2 Spartan-3 XC3S1000 FPGA の典型的な消費電力の内訳

おくことで、消費電力を最適化するためのよい参考になります。

## 電圧と温度の制御

図 1 のとおり、電圧と温度が低くなるほどリーク電流は大幅に低減します。電源電圧が 5% 低くなるだけで消費電力が 10% 低減するのです。電源電圧は電源の構成を変えるだけで簡単に調整できます。現在の FPGA では電圧を幅広く調整することはできません。通常、電圧の推奨範囲は +/-5% です。ジャンクション温度はヒートシンクやエアフローなどの冷却対策を講じることで低減できます。温度を 20 °C 下げればリーク電力を 25% 以上低減することもあります。温度を抑えればチップの信頼性は飛躍的に向上します。過去の調査では、20 °C 下がるとチップの寿命が 10 倍以上延びるケースもありました。

## サスPEND モードとハイバーネートモード

Spartan-3A FPGA には 2 種類の低消費電力アイドル状態があります。サスPEND モードでは、リーク電力を低減すると共にバイアス電流を除去するため、VCCAUX 電源の回路をディスイネーブルにし、スタティック消費電力を 40% 以上減らします。チップコンフィギュレーションと回路の状態(ステート)はそのまま保持されます。サスPEND モードの終了は AWAKE ピンをアサートすることで再動作します。このプロセスの所要時間は 1ms 未満です。

Spartan-3A デバイスのハイバーネートモードでは、消費電力をゼロにするため、すべての電源レギュレータをオフにできます。再始動するには、その部品に電源を入れなおしてリコンフィギュレーションが必要があり、これには數十ミリ秒かかります。電源がオフの間、すべての I/O はハイインピーダンス状態です。ハイバーネートモード中に I/O をアクティブに駆動する必要がある場合、それに対応する I/O バンクが電源オンの状態でなくてはならないため、少量のスタンバイ電力を消費することになります。

## I/O 規格の選択肢

消費電力は I/O 規格によって大きく異なります。スピードやロジックユーティリゼーションを犠牲にする代わりに、低消費電力の I/O 規格を選択することで消費電力を大幅に低減できます。たとえば、LVDS は入力ペアあたり 3mA、出力ペアあたり 9mA と、多くの電力を消費します。したがって、消費電力の観点から、LVDS はシステムの仕様上どうしても必要な場合や、最高のパフォーマンスを求める場合にのみ使用すべきです。

LVDS より低消費電力で高パフォーマンスの選択肢として、HSTL や SSTL を使用することもできますが、これらも入力あたり 3mA を消費します。ザイリンクスでは可能なかぎり LVCMS の入力を使うことを推奨しています。最後に、DCI 規格は大量の電力を消費します。RLDRAM などのメモリデバイスに接続する場合は、電力を節約するためメモリに ODT、FPGA に LVDCI を使うとよいでしょう。

## エンベデッド ブロック

プログラマブルファブリックの代わりにエンベデッド ブロックを使うことで、消費電力を大幅に抑えることができます。ザイリンクスの FPGA には、PowerPC™ ハードコアブロッセッサ、DSP スライス、ChipSync™ テクノロジ、エンベデッド Ethernet MAC、FIFO、SRL16 といった多数のエンベデッド ブロックがあります。エンベデッド ブロックはカスタム デザインであるため、プログラマブル ロジックより小型でスイッチングキャパシタンスが少なくてすみます。また、エンベデッド ブロックは相当するプログラマブル ロジックの構成と比べて、消費電力が 5 分の 1 から 12 分の 1 です。デザインが小型化され、より小型の部品に実装できるようになれば、エンベデッド ブロックを使うことでスタティック消費電力の低減につながります。非常に単純なファンクションの場合、大型のエンベデッド ブロックを使ったのではインプリメンテーションの効率をそれ以上改善できないことが考えられます。こ

の問題は、XPE を使用して両方のインプリメンテーションを確認することで容易に避けられます。

## クロック ジェネレータ

クロック生成時の電力を抑えることで消費電力を節約できます。周波数や位相の異なるクロックを生成するために、デジタルクロック マネージャが広く使われています。とはいえ、DCM は VCCAUX から相当量の電力を消費するため、できるだけ使用を控えたほうが賢明です。通常、1 個の DCM でも、CLK2X、CLKDV、CLKFX など複数の出力を使うことで複数のクロックを生成できます。同じファンクションに複数の DCM を使うより、このほうが消費電力の低減につながります。

## ブロック RAM の構築

1 個の大容量 RAM を構築するため複数のブロック RAM を組み合わせることができます。これは、やり方によって消費電力が大きく異なります。タイミング ドリブンな方法とは、すべての RAM に並列アクセスすることです。たとえば、2k × 36 RAM は、4 個の 2k × 9 RAM で構築されます。この大容量 RAM のアクセス時間は 1 個のブロック RAM と同じですが、アクセスあたりの消費電力は 4 個のブロック RAM に匹敵します。

消費電力を低減するには、この 2k × 36b RAM を 4 個の 512 × 36b RAM で構築するとよいでしょう。各アクセスは、アクセスする 4 個のブロック RAM の 1 つを選択するためプリデコードされます。プリデコードによりアクセス時間は増えますが、大容量 RAM のアクセスあたりの消費電力は 1 個のブロック RAM の消費電力とほぼ同じにまで抑えることができます。

## 低消費電力に向けた研究

近年、ザイリンクスは低消費電力の FPGA デザインを実現するためさまざまな手法を研究してきました。研究成果はまだ市販の

FPGA に実装されていませんが、未来の FPGA でどのような手法が取り込まれるかを紹介しましょう。

### 電圧スケーリング

前述のとおり、電源電圧を減らすことは消費電力を低減するための最も効果的な方法の 1 つであり、それに伴うパフォーマンスの劣化は、最高のパフォーマンスを必要としない多くのデザインにとって許容範囲内です。しかし、現在の FPGA は狭い電圧範囲で動作し、電圧の影響を受けやすい一部の回路では限界があります。

ザイリンクスは、さらに低電圧で動作するよう CLB 回路を設計しなおし、パフォーマンスの限界と消費電力の低減の広範囲なトレードオフを可能にしました。たとえば、90nm プロセスでは、200mV 低減されればピーク パフォーマンスを 25% 犠牲にする代わりに消費電力を 40% 低減でき、400mV 低減されればピーク パフォーマンスを 55% 落とす代わりに消費電力を 70% も削減できるのです。

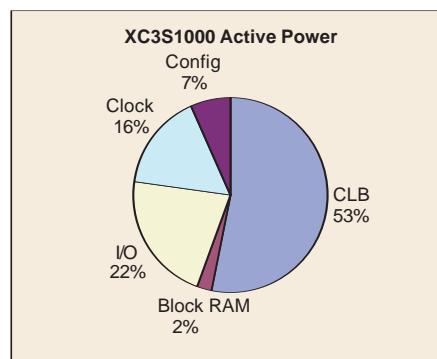

### 粒度の細かい電力スイッチング

プログラマブル ロジックのデザインに特有の問題として、いかなるデザインであっても、実装されたすべてのリソースが使われるわけではないことがあります。ところが、実際にはそれらリソースに常に電力が供給されており、リーク電力として総消費電力を増やす原因になっています。ブロックレベルの電力スイッチングを使えば、個々の未使用ブロックへの電力を遮断できます。各ブロックは電力スイッチを通して電源に結合されています。ブロックは、スイッチが閉じているときに機能し、スイッチが開いていると電源から切り離され、リーク電力は 50 分の 1~100 分の 1 に低減します。電力スイッチの粒度は、個々の CLB またはブロック RAM と同程度です。ザイリンクスのデザインでは、これら電力スイッチをコンフィギュレーション ビットストリームによってプログラミングできる他、ユーザーが直接、あるいはアクセス ポートを介して制御できます。実際

図 3 消費電力を低減するためのさまざまな対策を講じたコンセプト アーキテクチャ

のデザインをベンチマークしたところ、粒度の細かい電力スイッチングはリーク電力を 30% 低減することがわかりました。

### ディープスリープ モード

携帯端末で重要な条件の 1 つが、デバイスを使ってないときに電力をほとんど、あるいはまったく消費しないことです。Spartan-3A FPGA では、ハイバーネート モードに入ることでこれを実現できます。ただし、そのためには外部の制御装置が必要なうえ、起動が遅く、FPGA の状態を復元できなくなります。ザイリンクスのデザインでは、コンフィギュレーションと回路の状態格納エレメントに電力を供給したまま、すべての内蔵ブロックへの電源を遮断するために、前述した粒度の細かい電力スイッチをダイナミックに制御します。この結果、状態はディープスリープ モードとなり、リーク電力が名目値の 1~2% に低減するうえ、FPGA の状態も保たれます。また、このモードから数ミリ秒で起動することができます。

### 異種混合ファブリック

回路の最大クロック周波数は、タイミングクリティカル パスの遅延によって決まりま

す。クリティカル パス以外は、遅くしてもチップの全体的パフォーマンスに影響を及ぼしません。大規模システムの場合、プロセッサ内のデータ パスなど、スピード クリティカルなブロックが数種あり、それ以外のブロックはキャッシュなどのクリティカルでないブロックです。

今日の FPGA は、電力とスピードの点でどれも同じです。すべての CLB は電力、スピードとも同じ特性を持っています。クリティカルでないブロックを低消費電力のブロックにインプリメントすることで、低消費電力でもそのぶん遅いブロックを混合した異種アーキテクチャにすることで、電力を節約できます。これは、タイミング クリティカルなブロックを犠牲にしているわけではないため、全体的なチップ パフォーマンスにはまったく影響がありません。

異種混合アーキテクチャを構築するための 1 つの方法は、高電圧レール (VDDH) と低電圧レール (VDDL の 2 種類のコア電源レールを分散することです。FPGA の各部品はエンベデッド電源スイッチを使っていずれかを選択し、高速、または低消費電力のどちらかの特性を持つことになります。電圧の選択は、デザインの詳細なタイミングを得られた時点で完了となるため、VDDL から動作するのは非クリティカル ブロックだけとな

るはずです。

異種混合アーキテクチャを構築するためのもう1つの方法は、FPGAを高速および低消費電力用として作られた異なるリージョンに分割することです。リージョンはそれぞれ異なる電源電圧、異なるしきい値でインプリメントでき、またデザイン上の多数のトレードオフを通してインプリメントできます。パフォーマンスの劣化を避けるため、デザインツールは、デザインのタイミングクリティカルな部品を高速リージョンに、非クリティカルな部品を低消費電力のリージョンにマッピングする必要があります。

### 低スイング シグナリング

FPGAの容量が増えるほど、オンチップのプログラマブルインターネットにおける消費電力は増大します。この通信電力を低減するための効果的な方法は、配線上の電

圧スイングが電源電圧よりはるかに低い、低スイングシグナリングを使うことです。低スイングシグナリングは、今日、バスやオフチップリンクなど、高キャパシタンスの配線で通信する場合によく使われます。低スイングのドライバとレシーバはCMOSバッファより複雑であるため、多くのシリコンエリアを費やします。しかし、オンチップインターネットが総消費電力に占める割合が増えると、たとえデザインが複雑化しても低スイングシグナリングにするメリットのほうが大きいのです。もちろん、FPGAのユーザーが内部信号の異なる電圧に気づくことはありません。

図3に、これまで述べてきた概念を反映したFPGAアーキテクチャを示します。プログラマブルファブリックは高速リージョンと低消費電力リージョンの異種混合です。オンチップの電源モードコントローラは、ディープスリープ、サスPEND、ハイバーネート

の各低消費電力モードを管理します。ファブリック内では、専用の電源スイッチを使って各ロジックタイルの電源をオフにできます。配線ファブリックを通る通信は、インターネットの消費電力を低減するため低スイングのドライバとレシーバを経由します。

### 結論

昨今のFPGAデザインに使われているさまざまな消費電力最適化以外にも、ユーザーが消費電力を大幅に減らすために行えることはたくさんあります。将来のFPGAでは、消費電力を抑えて新たなFPGAアプリケーションを可能にする、さらに革新的なアーキテクチャソリューションが登場するでしょう。

本稿で解説したソリューションに加え、ザイリンクスはソフトウェアを使用したさまざまな電力最適化の研究開発を進めています。

## ザイリンクストレーニングスケジュール [9~10月]

11~12月のスケジュールは16ページをご覧ください。

ザイリンクスでは、大規模、高速FPGAを対象にしたFPGA設計のための各種トレーニングを各地で開催しております。是非ご利用ください。

| コース名                          | 日 程 |               | 主 催          | 開 催 地 |

|-------------------------------|-----|---------------|--------------|-------|

| ISE デザイン                      | 9月  | 5日(水)         | ザイリンクス       | 東京会場  |

|                               | 10月 | 4日(木)         |              |       |

| FPGA 設計導入                     | 9月  | 6日(木)         | ザイリンクス       | 東京会場  |

|                               | 10月 | 5日(金)         |              |       |

| FPGA 設計実践                     | 9月  | 13日(木)~14日(金) | 菱洋エレクトロ      | 大阪会場  |

|                               | 10月 | 11日(木)~12日(金) |              |       |

|                               |     | 30日(火)~31日(水) |              |       |

| アドバンスド FPGA 設計                | 9月  | 13日(木)~14日(金) | 新光商事         | 東京会場  |

|                               | 10月 | 15日(月)~16日(火) |              |       |

| Virtex-4 デザイン                 | 9月  | 25日(火)~26日(水) | ザイリンクス       | 東京会場  |

|                               | 10月 | 23日(火)~24日(水) |              |       |

| Virtex-5 デザイン                 | 9月  | 27日(木)        | ザイリンクス       | 東京会場  |

|                               | 10月 | 30日(火)        |              |       |

| エンベデッドシステム開発                  | 9月  | 25日(火)~26日(水) | PALTEK       | 東京会場  |

|                               | 10月 | 11日(木)~12日(金) |              |       |

|                               |     | 23日(火)~24日(水) |              |       |

| アドバンスド エンベデッドシステム開発           | 9月  | 27日(木)~28日(金) | 東京エレクトロンデバイス | 東京会場  |

| System Generatorを使用したDSP デザイン | 9月  | 6日(木)~7日(金)   | PALTEK       | 東京会場  |

|                               | 10月 | 17日(木)~18日(木) |              |       |

| MGT シリアル I/O デザイン             | 9月  | 20日(木)~21日(金) | 東京エレクトロンデバイス | 東京会場  |

|                               | 10月 | 25日(水)~26日(金) |              |       |

\*すべてのトレーニングは、ザイリンクス認定インストラクターによるオフィシャルトレーニングです。

\*日程および会場は、都合により変更となる場合もございます。最新情報はザイリンクストレーニングWebサイトをご覧ください。

詳細とご登録はこちらから ►► <http://japan.xilinx.com/support/education-home.htm>

# Inkjet Power Unleashed ここまでできた インクジェット プリンタ

Spartan-3AN FPGA が可能にする

ユビキタス対応の画期的なマーキングとプリント

Alex Breton

CEO and Founder

PrintDreams AB

[alex.breton@printdreams.com](mailto:alex.breton@printdreams.com)

製品の製造やパッケージというプロセスは手間のかかる作業であり、綿密な計画と複数の作業工程を必要とします。通常、製品へのマーキングは、製品が製造ラインの横に据え付けられたプリントステーションを通るときに行われます。

また、製造後のマーキングは主にラベル貼りという形で行われ、その場合はロール状またはシート状のラベルをあらかじめ作っておく必要があります。製品やパッケージにはそのプリント済みのラベルを貼ります。

PrintDreams 社の RMPT (Random Movement Printing Technology) は、マーキングをより柔軟に、容易に、そして楽

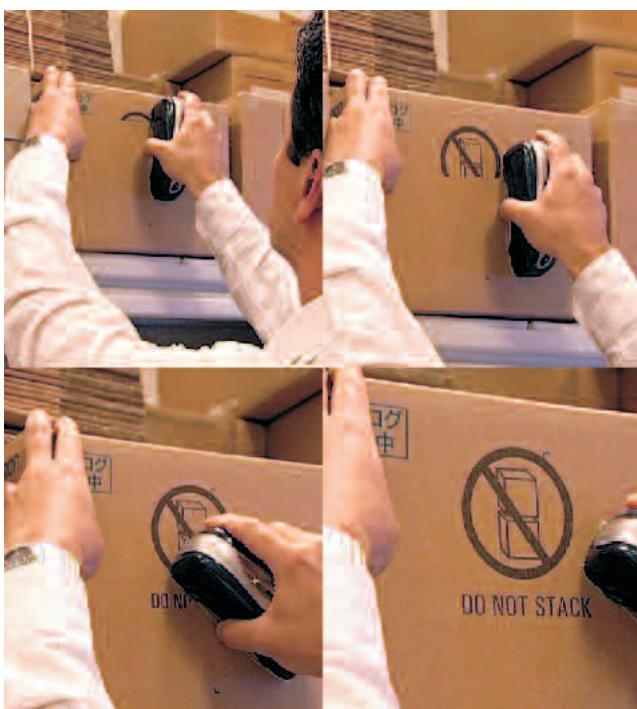

しくするテクノロジです。このプリント テクノロジは Xilinx® の Spartan™-3 FPGA を採用しており、触れるだけで、まるでマジックのようにどこにでもプリントが可能です。マーキングしたいエリアをデバイスでなぞるだけで、あとはこのテクノロジがすべてを行います。図 1 は、RMPT テクノロジでマーキングした保存箱です。

秘密は、先進のセンサ テクノロジと、何をいつどこにプリントするかを決める制御アルゴリズムにあります。すべてのインクジェット ノズルを、列単位で制御できるのです。また、上下・左右・曲線の移動が必要な場合は、すべてのノズルをそれぞれ独立して制御することも可能です。Spartan-3AN FPGA プラットフォームを使うことにより、PrintDreams 社は新しいパラメータを迅速にコンフィギュレーションできます。コンテンツのサイズが限られている場合、FPGA はその内蔵ブロック RAM から直接プリントするコンテンツにアクセスします。

RMPT プリンタは、バッテリで動作する携帯端末です。スタティック消費電力を 99% 低減したユニークなデュアルモードの電源管理と卓越したパフォーマンスは、ユーザーからも高く評価されています。

## 無限のサイズとフォーマット

RMPT テクノロジには、基本的にプリント サイズやフォーマットの制限がありません。ザイリンクスの FPGA はリコンフィギブルな特性に優れているため、新しいフォーマットへすばやく移行できます。FPGA を別々のコントローラとして動作させ、新たなエンティティを追加することでより大きなプリント面にも対応できます。

これと関連して、Spartan-3AN プラットフォームには、もう 1 つ便利な機能としてビルトインのマルチブート機能がありま

す。この機能を用いることで、同一のハードウェア デザイン上でさまざまなプリントヘッド ノズルとプリントヘッド ブロックのジオメトリに対応した異なるコンフィギュレーションを用いて動作させることができます。これにより、コストと新たなデザインを開発する手間が省けます。

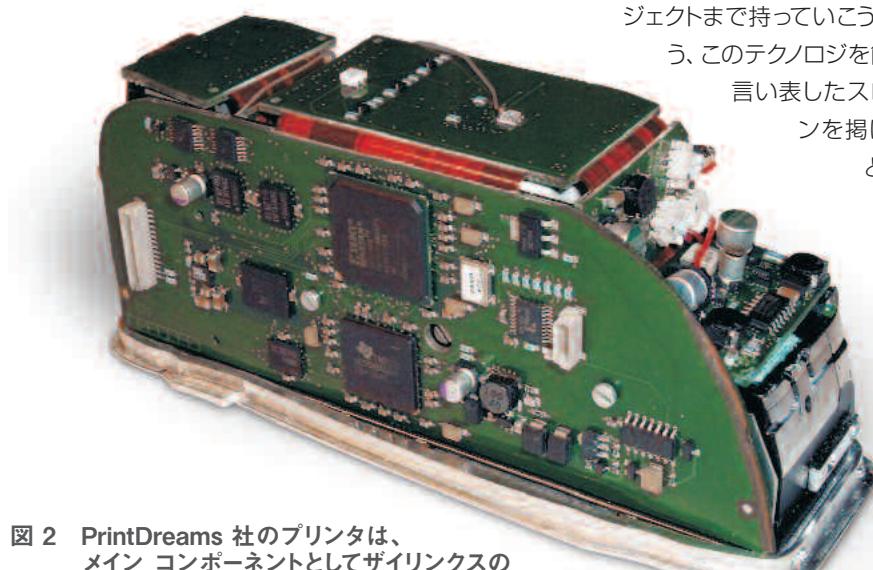

図 1 PrintDreams 社の RMPT テクノロジをストレージ ボックスに利用

図 2 PrintDreams 社のプリンタは、メイン コンポーネントとしてザイリンクスの Spartan-3 XC3S400AN FPGA を採用した小型の PCB のみを搭載

RMPT を発明したとき、当社は「プリンタ装置の幅はプリントするメディアの幅より広い」という、プリンタ業界における暗黙のルールを打ち破りました。一夜にして、物理的限界はプリントヘッドのカートリッジ サイズ、バッテリ、電子基盤のレベルまで下がったのです。従来のテクノロジでは大きな筐体に常に十分なスペースがありました。当社の新しい手法では PCB (プリント サーキット ボード) のフトプリントのサイズがさらなる小型化のボトルネックになり始めています。Spartan-3AN プラットフォームのオンチップ フラッシュは、我々にとってたいへん有意義で、これにより、フトプリントのサイズと外部コンポーネントのさらなる削減を実現しました。

ユーザーがこの装置を目にして最初に驚くのはそのサイズです。また、レターサイズの用紙をこれほどの小型装置にどのように挿入するのか疑問に思うようです。今や、用紙をプリンタに挿入するのではなく、プリンタを用紙 (あるいはプリントするメディア) まで持っていく時代になったのです。早速これを採用したあるユーザーは、「Take the printer to the project」(プリンタをプロジェクトまで持っていく)といふ、このテクノロジを簡潔に言い表したスローガンを掲げたほどです。

ユーザーがこの装置を目にして最初に驚くのはサイズです。次に、レターサイズの用紙をこれほど小型の装置にどうやって挿入するのか疑問に思うようです。今や用紙をプリンタに挿入するのではなく、プリンタを用紙（あるいはプリントするメディア）まで持つていける時代になったのです。

### 廉価で環境に優しいテクノロジ

PrintDreams 社のテクノロジは、現行のソリューションと比べても非常に競争力があります。それは、Spartan-3 FPGA の価格が廉価であること、また RMPT は基本的に複雑なメカニカル セットアップが必要ないソリッド ステートであるためです。

デスクトップであれポータブルであれ、プリンタを分解すると、いかに多くの機械部品で構成されているかがわかります。プリンタによっては 200 以上の部品で構成されていることもあるほどです。このため、プリンタを設計、製造するプロセスは非常に複雑で、膨大な手間とコストがかかっています。すべての部品に特殊な工作作業が必要なうえ、長い組み立てラインでそれぞれ独自のステップが必要になるためです。業界では、プリンタの製造に毎年数百トンもの鉄とプラスチックを消費しています。

PrintDreams 社の場合、必要なのは 1 個の小さな PCB とプリントヘッドのみです。プリンタの重さは携帯電話と同程度で、リサイクルが非常に簡単です。ラベルを用意する必要はなく、対象とするメディアにマークやコードを付けたりプリントするのに最適です。RMPT が唯一適るのは、一度に 5 ~ 10 ページ以上を印刷するような比較的大量のプリント ジョブです。また、極めて高品質な印刷にも適しません。PrintDreams 社はあくまでも小型、廉価、柔軟性という特長を追求していくつもりです。

### 過剰な柔軟性？

RMPT はプリントする材質を選びません。対応するインクさえあれば、どのような材質にもプリントできます。一般的な材質と

してはダンボールや木材、繊維、プラスチックですが、需要に応じて金属やガラスにプリントするソリューションも提供が可能です。

RMPT をいち早く導入した業界としてクラフト（手芸／工芸）業界があり、Xyron Design Runner という製品に採用されました。スクラップ ブッカー（趣味の工芸として手作りのフォト アルバムを制作する人たち）が使う材料の量と種類には驚くばかりです。コレクションから非常に目の粗い生地にいたるまで、その多彩さには驚きました。

今後は玩具にも採用される予定ですが、RMPT の卓越した柔軟性が逆に不安の元にもなっています。子どもが床や壁に メンタル落書きモードをプリントしたり、自分や他人の体にプリントしたりする心配があります。実際、RMPT を使えば肌にも簡単にプリントできてしまうのです。

しかしながら、この柔軟性は他の分野では歓迎されています。一般的なインクジェットのプリントヘッドだけでなく、レーザーヘッドなど他の装置も制御できるため、金属をはじめとする硬い材質により高度な恒久的マーキングを簡単に施すことができます。ザイリンクスの FPGA の柔軟性は、PrintDreams 社にとってもはや必要不可欠です。

### テクノロジの限界に挑戦

先進の RMPT を技術開発するうえで、最も重要な問題はリアルタイム性でした。電気通信やネットワークなど、多くの業界ではリアルタイムを定義する遅延をミリ秒単位で測定しています。しかし、PrintDreams 社はリアルタイムをマイクロ秒レベルで測定しているのです。

当社のシステムは、それぞれのプリントヘッド ノズルからプリントするかどうかを、毎秒

250 万回の速さで決定する必要があります。典型的な 600dpi のインクジェット プリントヘッドの場合、これは 300 ノズル以上に相当し、ハードウェアとソフトウェア両方のコンポーネントに膨大な負荷がかかります。

開発までの道のりは、まさにボトルネック 解消のプロセスでした。以前は 300 回以上の計算を直列実行するため DSP を使用していましたが、現在は新しいタイプのプリントヘッドをリコンフィギュレーションする機能を残しながら、高いキャパシティと高度な並列化で動作するようシステムを拡張しました。もし ASIC を採用していたら、おそらく 1 種類のプリントヘッド アーキテクチャに縛られていたはずです。

このような業界初のテクノロジを開発した PrintDreams 社にとって、知的財産権 (IP) の保護が大きな関心事であることは言うまでもありません。当社のプリンタにザイリンクスのコンピューティング テクノロジを選択したのは、クローニングやリバース エンジニアリングから保護する Spartan-3AN プラットフォームのセキュリティ機能がそうした不安を取り払ってくれたことも採用の一因です。

### 結論

PrintDreams 社がザイリンクスの Spartan-3AN プラットフォームを選んだ理由は、手ごろな価格で優れた柔軟性やパフォーマンス、セキュリティ機能を提供しているためです。また、電源管理がさらに改善され、いっそう小型化されたことから、このプラットフォーム以外に候補は考えられませんでした。PrintDreams 社と RMPT テクノロジの詳細は、[www.printdreams.com](http://www.printdreams.com) をご覧ください。

## Low-Cost Security Solutions with Spartan-3A and Spartan-3AN Platforms

# Spartan-3AとSpartan-3AN が実現する低成本 セキュリティ ソリューション

リバース エンジニアリングや

オーバービルディング、クローニングから

デザインを守る Spartan-3 ファミリの新機能

Maureen Smerdon

Strategic Marketing Manager

Xilinx, Inc.

maureen.smerdon@xilinx.com

飛行機への搭乗から玄関ドアのロック、次世代の回路設計にいたるまで、セキュリティは今や重要な問題となりました。設計者が最も恐れるのは、デザインが盗まれて偽造品が市場に溢れることです。国際模倣対策連合 (International AntiCounterfeiting Coalition) によると、2003 年における米国全体の偽造品による被害額は 2,870 億ドルで、世界中で年間に売られる偽造品の総額、4,560 億ドルの 63% を占めるそうです。

本稿では、低成本 FPGA デザインを保護するため、ザイリンクスがどのようなセキュリティ対策を講じているかを解説します。

### セキュリティ上の脅威トップ 3

電子機器のデザインで最も一般的な違法行為は、リバース エンジニアリングです。リバース エンジニアリングとは、デザインを盗んだ人物がオープン市場でより安く販売することを目的に、製品を違法に作り直すことです。リバース エンジニアリングにより、研究開発にまったく資金をかけずに、安いコストで、しかもはるかに短期間で製品化できてしまうのです。

今日、企業の製造委託が進んだことで、オーバービルディング (過剰生産) やクローニング (模造) と呼ばれる新たな違法行為が問題化しています。オーバービルディングとは、委託を受けたメーカーが OEM メーカーの発注量以上の数量を製造することです。その発注量以上の製品は、OEM メーカーの承認を得ずに市場に出回ることになります。

クローニングは、デザインや IP、製品のコピーを作り、同じ、もしくは別のラベルを付け、市場に出すことです。この場合も研究開発費はかかりません。オーバービルディングやクローニングによって作られる製品は、きわめて短時間で市場へ送り出され、流通します。

こうした違法行為により、どれだけの無形資産が失われるか分かりません。リバース エンジニアリング、オーバービルディング、クローニングのいずれも、OEM メーカーにとっては莫大な収益ロスです。そればかりか、返品という形で品質に付随するコストもかかります。これはブランド イメージに悪影響を及ぼすだけでなく、不具合を突き止めて消費者の問題を解決するための RMA (返品不良解析) やテクニカル サポートが増加し、OEM メーカーの最終損益に影響を及ぼす可能性さえあります。また、その製品が正規品か偽造品かを最後まで判断でき

ないこ

ともあるで

しょう。このよ

うな損失は永久的で、

回復不可能です。

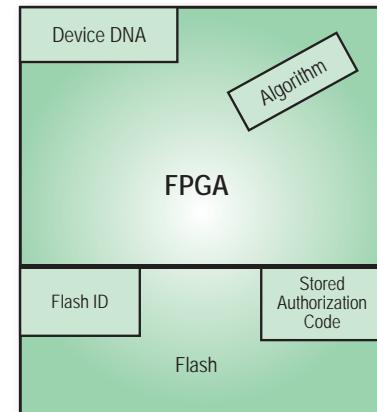

### DeviceDNA を用いたセキュリティ

従来、FPGA はリバース エンジニアリングとクローニングに対する防衛策として、ビットストリームの暗号化を用いてきました。一昔前まではそれで十分対応できましたが、今日のオーバービルディングを防ぐことはできません。

では、設計者はこれら 3 つの違法行為からどのようにデザインを保護すればいいのでしょうか？ ザイリンクスは、デザインをクローニングやオーバービルディング、リバース エンジニアリングから保護するため、DeviceDNA を実装した Spartan™-3A と Spartan-3AN デバイス ファミリを発表しました。

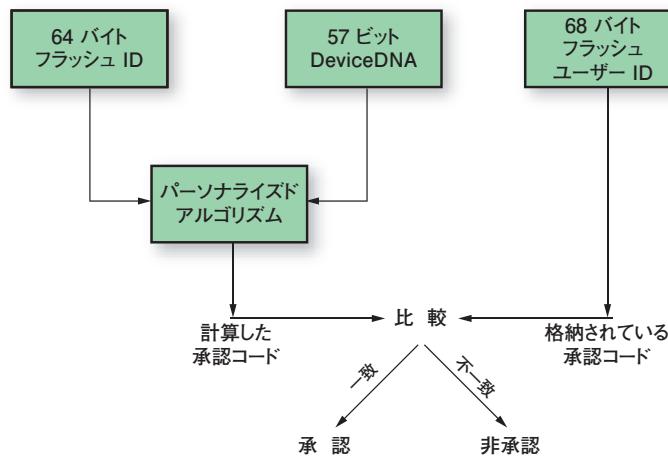

デザイン レベルのセキュリティである DeviceDNA は、デザインと IP、エンベデッド コードを保護します。DeviceDNA は、各デバイスに固有の 57 ビットの ID です。この 57 ビット ID は FPGA の特定工

リアに内蔵されており、ザイリンクスのファクトリで設定され、出荷されます。ID は変更することができません。Spartan-3A および Spartan-3AN FPGA は、各デバイスの出荷時に固有の ID が組み込まれます。

この ID は、設計者がパーソナライズしたアルゴリズムと組み合わせて FPGA に格納されます。アルゴリズムは、基本的に DeviceDNA を用いてどのように結果を作成するかを定義する算式です。結果は外部メモリやフラッシュメモリなど、任意の場所に格納します。アルゴリズムは設計者しか知らないため、セキュリティの鍵を握るのはこのアルゴリズムです。アルゴリズムは FPGA に格納されますが、第三者にはビットストリームの一部にしか見えません。

## Spartan-3A のセキュリティ

Spartan-3A デバイスの場合、デバイスのコンフィギュレーション後、アルゴリズムは DeviceDNA を使用した結果をフラッシュメモリに格納されている結果と照合します。両方の結果が一致するとそのデザインは承認されます。一致しない場合は、機能を制限した形でデザインをセットアップできます。どの程度制限するかは任意に決定できます。

この認証プロセスを日常生活に例えてみましょう。軽食を買うためファストフードのレストランに立ち寄ると考えてください。手持ちの現金がないため、ATM カード (DeviceDNA) を使うことにします。このカードはあなただけが使えるカードです。注文し、磁気カードを読み取り機に通します。

すると、機械から PIN 番号 (パーソナライズしたアルゴリズム) を入力するよう求められます。システムはあなたが入力した PIN 番号を銀行に格納されている番号と照合します。両方の番号が一致すれば軽食を購入できますが、一致しないと空腹のまま店を出るしかありません。

しかし、もし誰かがあなたの ATM カードを持っていて、PIN 番号を知っていたらどうでしょう。PIN の承認アルゴリズム番号を覚えれば、クローンを作成するのは簡単です。承認アルゴリズムをデザインそのものに組み込んであるのは、そのような理由からです。アルゴリズムはプログラマブルロジック内の最も機密性の高いエリアに格納されており、コンフィギュレーションオプションは数百万通りに上ります。

## Spartan-3AN のセキュリティ

ザイリンクスの新しい不揮発性 FPGA、Spartan-3AN プラットフォームの場合、承認プロセスは Spartan-3A とほぼ同じですが、さらにいくつかの面でセキュリティを強化しています。1 番目は、ビットストリームが FPGA 内部に隠されていることです。これにより、ビットストリームを覗くのがいっそう難しくなります。

2 番目は、DeviceDNA と、フラッシュメモリに記録されているファクトリフラッシュ ID の 2 つの固有のシリアル番号です。2 つの固有の ID を組み合わせることにより 70 バイト以上のシリアルナンバーができる、膨大な数のアルゴリズムが可能にな

ることから、認証アルゴリズムを破るにはさらに多くの時間が必要です。このように、デザインが FPGA とフラッシュ ID の両方に関連付けられるようになるわけです。

先ほどの例で言えば、2 つの固有の ID を持つということは、軽食を買うために 2 枚の別々のカードが必要ということです。

3 番目の改善点は、格納されている承認コードです。Spartan-3AN プラットフォームでは、承認コードをオンチップのフラッシュユーザー フィールドという、1 回のみプログラミング可能な専用の 64 バイト レジスタに格納できます。これにより、自己完結型の完全なセキュリティシステムが実現されます。外部のインターフェイスやストレージが不要なことから、全体的なセキュリティが高まり、リバース エンジニアリングがいっそう難しくなります。

認証アルゴリズムはユーザーが定義するため、デザイン バジェットを考慮しながら適切なセキュリティ レベルをインプリメントできます。認証アルゴリズムはこのセキュリティシステムにおける重要な鍵でもあります。セキュリティが破られないよう、認証プロセスのどこかを秘密にする必要があります。アルゴリズムが未知であるため、このアルゴリズムがデザイン レベルのセキュリティを確保する鍵となるのです。アルゴリズムは FPGA のファブリックにインプリメントされることから、FPGA 内の数百万に及ぶコンフィギュレーションビットのごく一部のビットになります。これらビットの関係や、アルゴリズムが理解できない限り、膨大な数字にしか見えません。図 1 は、Spartan-3AN

図 1 Spartan-3AN FPGA で可能なセキュリティ セットアップ

図 2 セキュリティを施した Spartan-3AN デバイス

デバイスで可能な 1 つの流れを示したもの

図 2 に示す Spartan-3AN のデザインレベル セキュリティは、完全に自己完結型のセキュリティ ソリューションです。フラッシュに、FPGA コンフィギュレーション ビットストリームと、以前に生成された承認コードが両方格納されています。このコードは、信頼性／セキュリティの保証されたメーカーもしくは登録プロセスにより、一回限りプログラムが可能なフラッシュ ユーザー フィールドに格納されます。

電源投入時、FPGA は通常どおりにコンフィギュレーションされます。コンフィギュレーションが終わると、FPGA アプリケーションには、その Spartan-3AN FPGA で動作することを承認されたデザインを有効化するための回路が用意されます。認証アルゴリズムにより DeviceDNA とファクトリ フラッシュ ID が読み込まれ、アクティブな承認コードを生成して、フラッシュ ユーザー フィールドに格納されている以前生成した承認

コードと比較します。両方のコードが同じならデバイスは認証され、異なる場合は不正デバイスとして承認されません。

- Permanent self-destruction – フラッシュの内容をすべて消去し、フラッシュを永久にすべてゼロにします。

## アクセス拒否

DeviceDNA によるデザイン レベル アプローチのもう 1 つの長所は、失敗した認証の処理方法にあります。認証はデザインに完全に統合できます。したがって、承認されなかったデザインに、次のような複数の対策を取ることができます。

- No functionality – 機能を完全にストップします。

- Limited functionality – 一次回路または主要回路がディスエーブル、もしくはバイパスされます。

- Time bomb – 限られた期間のみすべての機能を利用できます。

- Active defense – システムはアクティビティを監視し、攻撃から防御します。

これらのデザイン レベルのセキュリティは、Spartan-3A と Spartan-3AN プラットフォーム内で実現可能な基本レベルのセキュリティです。

## 結論

Spartan-3A および Spartan-3AN プラットフォームのセキュリティ対策は、リバース エンジニアリングやオーバーハーク、クローニングから保護するための数多くの方法を提供します。低コスト FPGA デザインのセキュリティの詳細は、Spartan ジェネレーションのコンフィギュレーション ユーザー ガイド「Spartan-3AN In-System Flash User Guide (英語版)」(<http://japan.xilinx.com/bvdocs/userguides/ug333.pdf>) をご覧ください。

# ザイリンクス トレーニング スケジュール [11~12月]

9 ~ 10 月のスケジュールは 8 ページをご覧ください。

| コース名                            | 日 程  |                    | 主 催          | 開 催 地 |

|---------------------------------|------|--------------------|--------------|-------|

| ISE デザイン                        | 11 月 | 1 日 (木)            | ザイリンクス       | 東京会場  |

|                                 | 12 月 | 4 日 (火)            |              |       |

| FPGA 設計導入                       | 11 月 | 2 日 (金)            | ザイリンクス       | 東京会場  |

|                                 | 12 月 | 5 日 (水)            |              |       |

| FPGA 設計実践                       | 11 月 | 6 日 (火)~ 7 日 (水)   | アヴィネット ジャパン  | 東京会場  |

|                                 |      | 27 日 (火)~ 28 日 (水) |              |       |

| アドバンスド FPGA 設計                  | 12 月 | 11 日 (火)~ 12 日 (水) | 菱洋エレクトロ      | 東京会場  |

|                                 | 11 月 | 5 日 (月)~ 6 日 (火)   |              |       |

|                                 | 12 月 | 6 日 (木)~ 7 日 (金)   |              |       |

| Virtex-4 デザイン                   | 11 月 | 15 日 (木)~ 16 日 (金) | 菱洋エレクトロ      | 大阪会場  |

|                                 | 12 月 | 20 日 (木)~ 21 日 (金) |              |       |

| Virtex-5 デザイン                   | 11 月 | 22 日 (木)           | ザイリンクス       | 東京会場  |

|                                 | 11 月 | 13 日 (火)~ 14 日 (水) |              |       |

| エンベデッド システム開発                   | 12 月 | 13 日 (木)~ 14 日 (金) | PALTEK       | 東京会場  |

|                                 | 11 月 | 27 日 (火)~ 28 日 (水) |              |       |

| アドバンスド エンベデッド システム開発            | 11 月 | 15 日 (木)~ 16 日 (金) | 東京エレクトロンデバイス | 東京会場  |

|                                 | 12 月 | 18 日 (火)~ 19 日 (水) |              |       |

|                                 | 11 月 | 29 日 (木)~ 30 日 (金) |              |       |

| System Generator を使用した DSP デザイン | 12 月 | 11 日 (火)~ 12 日 (水) | PALTEK       | 東京会場  |

|                                 | 11 月 | 18 日 (火)~ 19 日 (水) |              |       |

| MGT シリアル I/O デザイン               | 11 月 | 29 日 (木)~ 30 日 (金) | 東京エレクトロンデバイス | 東京会場  |

|                                 | 12 月 | 11 日 (火)~ 12 日 (水) |              |       |

\*すべてのトレーニングは、ザイリンクス認定インストラクターによるオフィシャル トレーニングです。

\*日程および会場は、都合により変更となる場合もございます。最新情報はザイリンクス トレーニング Web サイトをご覧ください。

詳細とご登録はこちらから ►► <http://japan.xilinx.com/support/education-home.htm>

# Implementing Low-Cost DDR2 Interfaces with Spartan-3A FPGAs

# Spartan-3A FPGA を 使用した低価格 DDR2 の インプリメント

ザイリンクスが提供する短期の製品化を支援する

メモリ インターフェイス ソリューション

Adrian Cosoroaba

Marketing Manager

Xilinx, Inc.

adrian.cosoroaba@xilinx.com

一般にアプリケーションは、最高のバンド幅を第一の目的とする高性能型と、システムコストを重視する低コスト型の 2 種類に分類できます。ハイエンド アプリケーションについては、ザイリンクスは最高のバンド幅ニーズに応える Virtex™-5 FPGA を提供しています。

しかし、すべてのシステムがメモリのパフォーマンスを限界まで追求するわけではありません。ほとんどの低コスト システムには、ピンあたりのデータ レートが 400Mbps 未満の DDR SDRAM や DDR2 SDRAM で十分です。こうしたアプリケーションについては、ザイリンクスは Spartan™-3 や Spartan-3E、Spartan-3A、Spartan-3AN FPGA からなる Spartan-3 ジェネレーションを提供しています。

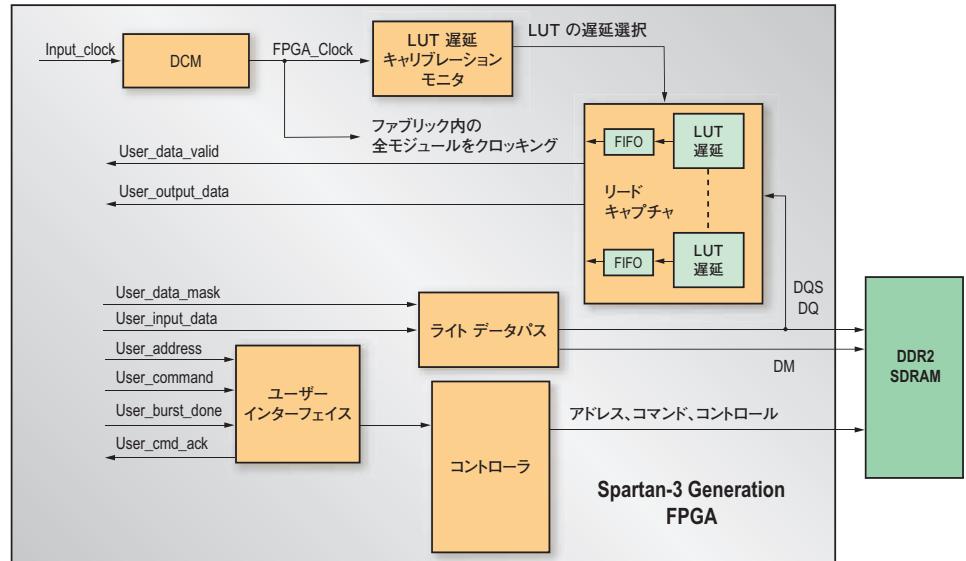

本稿では、Spartan-3 ジェネレーション FPGA でインプリメントした DDR2 SDRAM メモリ インターフェイスのアーキテクチャと、ザイリンクスのツールやハードウェア検証済みのリファレンス デザインがお客様独自のメモリ インターフェイスを構築するうえでいかに役立つかを解説します。

## メモリ コントローラと DDR2 インターフェイス

FPGA ベースのデザインでは、コントローラとメモリ インターフェイスは 3 つの基本的なビルディング ブロックで構成されます。リード/ライト データ インターフェイス、メモリ コントローラ ステート マシン、そしてメモリ インターフェイスのデザインを FPGA

デザインの他のエリアに橋渡しするユーザーインターフェイスの3つです（図1）。

Spartan-3 ジェネレーション FPGA のユーザーインターフェイスは、ハンドシェーリング型のインターフェイスです。コマンド（read または write）に、書き込むアドレスとデータを付けて送信すると、ユーザーインターフェイス ロジックは "user\_cmd\_ack" 信号で応答し、次のコマンドを入力できるようになります。

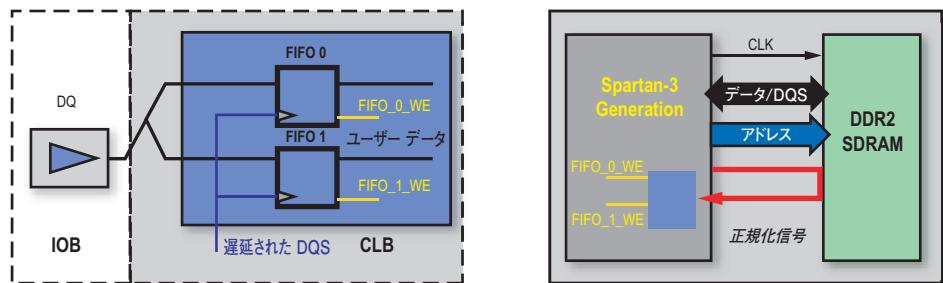

ファブリックにインプリメントされているファンクション ブロックは、デジタルクロック マネージャ（DCM）の出力によってクロッキングされ、LUT（レックアップ テープル）遅延キャリブレーション モニタを駆動します。このキャリブレーション回路は、リードデータ（DQ）の場合に、リードデータストローブ（DQS）を遅延させるために必要な LUT ベースのエレメント数を選択します。そうすることで、FPGA 内でキャプチャできるよう正しくアラインすることができます。

リード トランザクション中、DDR2 SDRAM デバイスは DQ とエッジアラインされている FPGA に、DQS とその関連データを送信します。データは非フリー ランニングの DQS ストローブのエッジごとに変化するため、DQ をキャプチャするのは困難な作業です。

DQ キャプチャは、コンフィギュアブル ロジック ブロック（CLB）内の LUT を用いてインプリメントされます。DQ キャプチャのインプリメンテーションは、LUT をベースとするタップ遅延メカニズムを使います。DQS クロッキング信号は十分なタイミング マージンを提供するために遅延されます。DQ のキャプチャは、デュアルポート LUT ベースの RAM にインプリメントされます（図2）。LUT RAM は一対の FIFO として構成され、各データ ビットが立ち上がりエッジ（FIFO\_0）と立ち下がりエッジ（FIFO\_1）の各 FIFO に入力されます。深さ 16 エントリのこれら FIFO は非同期であり、独立したリード ポートとライト ポートを持ちます。

DQS クロック ドメインからメモリ コントローラ クロック ドメインへの DQ 転送

図1 Spartan-3 ジェネレーション FPGA への DDR2 SDRAM インターフェイスのインプリメンテーション

図2 Spartan-3 ジェネレーション FPGA に対する DQ キャプチャ FIFO インプリメンテーション

は、これら非同期の FIFO を通して行われます。データはメモリ コントローラ クロック ドメイン内の FIFO\_0 と FIFO\_1 の両方から同時に読み出すことができます。FIFO リード ポインタは FPGA の内部クロック ドメインで生成されます。ライト イネーブル信号（FIFO\_0 WE と FIFO\_1 WE）の生成には、DQS と外部ルックバックもしくは正規化信号が使われます。

外部の正規化信号は出力として入出力ブロック（IOB）を駆動し、その後入力バッファを通して入力され使用されます。これにより、FPGA とメモリ デバイス間の IOB やデバイス、トレース遅延が補正されます。

ライト データ インターフェイスは、ライト データのコマンドとタイミングを生成、制御します。ライト データ インターフェイスは、DDR および DDR2 SDRAM のタイ

ミング要件に従って、コマンドおよびデータ ビットに正しくアラインされた DQS ストローブを伝送するため、IOB フリップフロップと DCM の 90, 180, 270°出力を使用します。

デザインには、コントローラ ステート マシンの総合的なロジック生成やユーザーインターフェイスといった他の面もあります。ザイリンクスは、設計者が完全なソリューションをより簡単に作成できるよう、メモリ インターフェイス ジェネレータ（MIG）ツールを開発しました。

## コントローラのデザインと MIG ソフトウェア ツールとの統合

デザインを作成するには、メモリ コントローラ ステート マシンを含むあらゆるビル

ディング ブロックを統合することが不可欠です。コントローラ ステート マシンは、メモリ アーキテクチャとシステム パラメータによって異なります。ステート マシンのコードも複雑になります。次のような多くの変数に左右されます。

- ・アーキテクチャ (DDR、DDR2)

- ・バンク数 (メモリ デバイスの外部もしくは内部)

- ・データ バス幅

- ・メモリ デバイスの幅と深さ

- ・バンクとロー (行) のアクセス アルゴリズム

最後に、データ/ストローブ比 (DQ/DQS) がデザインをいっそう複雑化させることができます。コントローラ ステート マシンは、メモリ デバイスのタイミング要件を考慮してコマンドを正しい順序で発行しなくてはなりません。

デザインは、MIG ソフトウェア ツールを用いて生成できます。このツールは、リファレンス デザインと IP からなる ISE<sub>I</sub> ソフトウェア、CORE Generator<sup>TM</sup> スイートの一部として、ザイリンクスから無償で入手できます。MIG のデザイン フローは従来の FPGA デザイン フローに非常によく似ています。このソフトウェアを使用することで、設計者は物理レイヤ インターフェイスやメモリ コントローラ用に RTL コードをゼロから生成する必要がありません。

システムとメモリのパラメータを設定するには、MIG のグラフィカル ユーザー インターフェイス (GUI) を使います。たとえば、FPGA デバイス、パッケージ、スピード グレードを選択した後にメモリ アーキテクチャを選択することが可能で、実際のメモリ デバイスや DIMM (デュアル インライン

メモリ モジュール) を選ぶことも可能です。この GUI では、バス幅とクロック 周波数を選択できます。他に、CAS (カラム アクセス ストローブ) レイテンシ、バス長、ピン割り当てを制御するオプションがあります。

MIG ツールは、1 分もしないうちに RTL ファイルと UCF ファイル (それぞれ HDL コード ファイルと制約ファイル) を生成します。これらのファイルは、ハードウェア検証済みのリファレンス デザインのライブラリを使って生成され、設計者の入力に基づいて変更が加えられます。出力ファイルは、ユーザー インターフェイス、物理レイヤ、コントローラ ステート マシンなど、それぞれのビルディング ブロックに適用されるモジュールごとにカテゴリ化されます。

RTL コードにはさらに自由に変更を加えることができます。「ブラックボックス」のインプリメンテーションを提供する他のソリューションとは異なり、コードが暗号化されないため、デザインを変更してからさらに柔軟にカスタマイズすることができます。コードの変更後、追加のシミュレーションを実行してデザイン全体の機能性を検証できます。

また、MIG ツールは、メモリ チェック機能を備えた合成可能なテスト ベンチを生成します。テスト ベンチは、ザイリンクスのリファレンス デザインの機能をシミュレーションしたりハードウェアを検証したりするために使われるデザイン サンプルです。テスト ベンチは、メモリ コントローラに一連のライトおよびリードバックを発行します。これは独自のカスタム テスト ベンチを生成するためのテンプレートとして使うことも可能です。

デザインの最終段階では、MIG ファイルを ISE プロジェクトにインポートし、残りの FPGA デザイン ファイルとマージした後、合成と配置配線を行い、さらに必要に応じて追加のタイミング シミュレーションを

実行してからハードウェア検証を実施します。MIG ソフトウェア ツールは、最終的なビット ファイルを最適な形で生成できるよう、合成、マッピング、配置配線の適切なオプションを用いてバッチ ファイルを生成します。

## ハードウェアの検証と開発ボード

リファレンス デザインのハードウェア検証は、堅牢で信頼性の高いソリューションにするための重要な最終ステップです。

ザイリンクスでは、Spartan-3A FPGA に対する DDR2 SDRAM メモリ インターフェイスのインプリメンテーションをハードウェアで完全検証してみました。我々は、DDR2 SDRAM のデザインは低コストの Spartan-3A スタータ キット ボードを使ってインプリメントしました。デザインとしては、オンボードの 16 ビット幅 DDR2 SDRAM メモリ デバイスと XC3S700A-FG484 FPGA を使用しています。リファレンス デザインは、Spartan-3A デバイスの利用可能なリソースのうち、IOB の 13%、ロジック スライスの 9%、BUFG MUX の 16%、そして 8 つの DCM のうち 1 つのみを使用しています。このようにインプリメントすることで、他のファンクションに十分なリソースを確保することができます。

ザイリンクスは、さまざまな Spartan-3 ジェネレーション FPGA 用のメモリ インターフェイス デザインを検証しました。表 1 に、Spartan-3 ジェネレーション FPGA の開発ボードごとに、ハードウェア検証したメモリ インターフェイスをまとめてあります。

## 結論

低コストの Spartan-3 ジェネレーション FPGA や、メモリ インターフェイス ジェネレータ (MIG) ツール、ザイリンクスの開発ボードを使用することで、メモリ インターフェイスやコントローラのデザインを迅速化できます。

メモリ インターフェイス ソリューションの詳細は、<http://japan.xilinx.com/memory> をご覧ください。

表 1 メモリ インターフェイス用の低コスト開発ボード

| ザイリンクス FPGA         | Spartan-3 FPGAs | Spartan-3 FPGAs | Spartan-3 FPGAs |

|---------------------|-----------------|-----------------|-----------------|

| 開発ボード               | SL361           | Starter Kit 3E  | Starter Kit 3A  |

| サポートされるメモリ インターフェイス | DDR             | DDR             | DDR2            |

# Leveraging the Virtex-5 SXT High-Performance DSP Solution

# Virtex-5 SXT を活用する 高パフォーマンス デジタル 信号処理 DSP ソリューション

信号処理バンド幅を最大化し、電力消費を最小化する Virtex-5 SXT

Brent Przybus

Sr. Product Marketing Manager,

Advanced Products Division

Xilinx, Inc.

brent.przybus@xilinx.com

FPGA は、20 年以上にわたり、最も柔軟で適応性に優れた高速なデザイン環境を提供してきました。DSP の設計者は、当初から再設計可能な多数のゲートをデジタル信号処理に利用できることに気付いていました。FPGA ファブリックに組み込まれている乗算器や加算器、アキュムレータを組み合わせれば、巨大な並列性（パラレリズム）を活かして効率的な DSP フィルタ アルゴリズムをインプリメントできます。

FPGA の周波数問題は並列性により相殺され、さらに性能が高まることにより、DSP の代替ソリューションに匹敵するようになりました。その後、乗算器と加算器のインプリメンテーションをより効率的に行うことができるようになり、1998 年、ザイリンクスは Virtex™-II FPGA ファミリに統合された初のエンベデッド乗算器を発表しました。大ヒットを記録したこの Xilinx® Virtex-II と Virtex-II Pro ファミリは、FPGA ベースの DSP を新たな次元へと高め、毎秒 10 億 MAC（積和演算）という壁を打ち破りました。

デジタル通信や軍事、防衛、ビデオおよび画像処理市場の需要に支えられ、ザイリンク

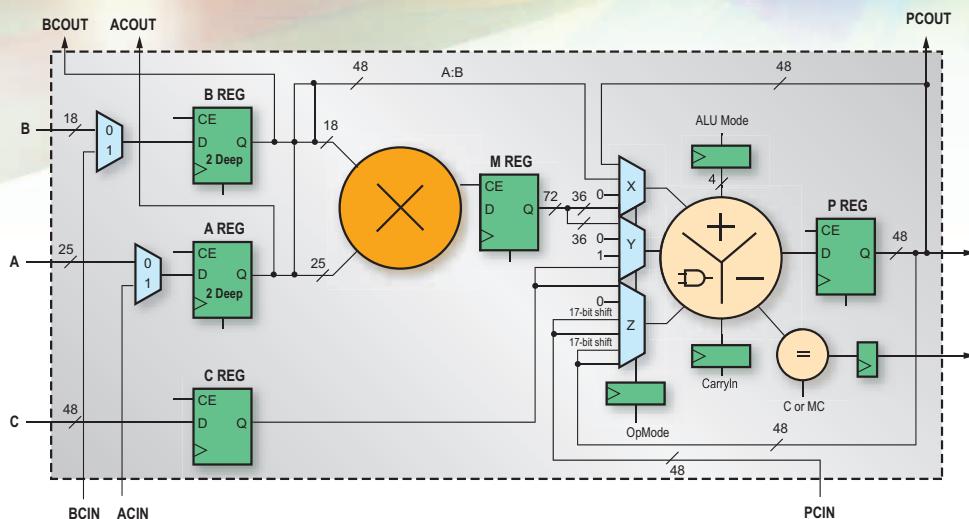

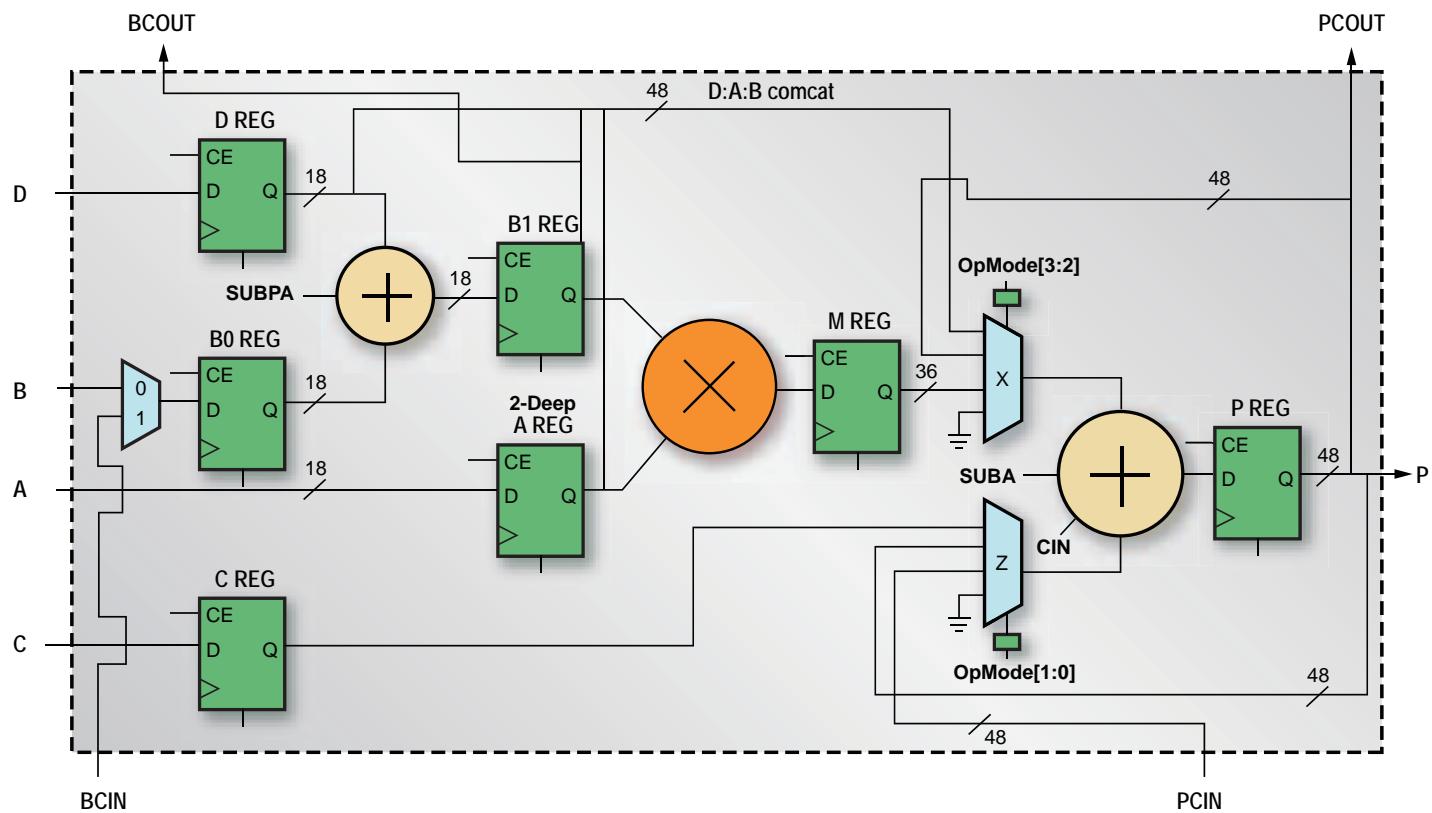

図 1 Virtex-5 FPGA における DSP48E スライスの回路図

スはそれぞれの業界特有の課題に応えると共に、巨大な並列実装のスタイルをいっそう強化すべく、さらに改良を加えてきました。しかし、パフォーマンスの向上や乗算器および加算器の増加に伴い、消費電力の管理はますます難しくなったのです。

そこで、FPGA ファブリックのリソースを使わずに簡単にカスケード化できる、超低消費電力の高性能かつ包括的なデジタル信号処理エレメントとして DSP48 スライスをデザインすることで、この課題に対応しました。このエレメントは Virtex-5 デバイスでさらに機能強化され、さらにその後の DSP48E スライスでは、より高い精度、

SIMD（単一命令／複数データ）演算、統合型パターン検出回路、ロジック ユニットをサポートしています。

また、ザイリンクスは高速なオンチップ データと係数ストレージに対する需要に応えるため、独特な比率の DSP48E スライスと多数のブロック RAM および分散 RAM からなるデジタル信号処理プラットフォームを構築しました。最後に、チップとの間でデータをより高速にやり取りできるように、3.125Gbps で動作する統合型の高速シリアル チャネルを採用しました。これらエレメントを組み合わせて生まれたのが Virtex-5 SXT プラットフォームです。

## Virtex-5 SXT エンジン - DSP48E スライス

FPGA 内のデジタル信号処理の進化を理解するには、DSP48E スライス（図 1）とそのデザインの 3 つの特徴を理解しておく必要があります。

### ・ 統合型乗算器と第 2 ステージ

統合型の第 2 ステージ加算器／減算器／アキュムレータを用いて乗算器の演算を拡張します。これにより、1 個の DSP48E スライス内に DSP 演算の最も一般的な組み合わせをインプリメントできます。

### ・ シストリック インプリメンテーション

DSP48E スライスは、ビルディング ブロックのようにお互いにインタフェースし合う自己完結型のエレメントで、それぞれ FPGA ファブリックから独立した専用の配線とバッファリングを持ち、パフォーマンスの改善と消費電力の低減を同時に実現します。

### ・ カスタム デザイン

ザイリンクスは早い段階から、高度な性能と極めて低い消費電力を達成するには、最新のプロセス ジオメトリに即した完全なカスタム デザインが必要だと考えていました。ザイリンクスの設計チームは Arithmetica 社と共に、乗算器と加算器の回路に対して MathIP ライブライを統合し、さらなる効率化を図りました。

このようなデザインにより、DSP48E スライスのインプリメンテーションは、前例のないパフォーマンスと優れた電力効率を達成しています。Virtex-5 デバイスの DSP48E スライスは、高速、中速、低速のスピード グレードでそれぞれ 550MHz、500MHz、450MHz のスピードで動作します。このパフォーマンスは、1 個の DSP48E スライスを単独で使用する場合でも、毎秒 3,520 億回の積和演算を達成するため専用のカスケード ロジックを使って最も大型の Virtex-5 SXT デバイスに 640 個の DSP48E スライスをすべて組み合わせる場合でも、ど

ちらでも可能です。しかも、この驚異的パフォーマンスはロジックや FPGA の配線リソースをいっさい使用せずに DSP48E スライスだけを用いて達成したものです。

専用のカスケード ロジックを使うということは、各 DSP48E スライス、そのスライスの動作スピード、および入力のトグル レートに基づいて消費電力を計算できるということです。個々の DSP48E スライスの代表的な実測消費電力は 1.38mW/100MHz です。したがって、Virtex-5 SX 95T 内の 640 個の DSP48E スライスがすべて 550MHz で動作しており、代表的トグル レートが 38% であれば、総ダイナミック消費電力は 4.92W というように簡単に計算できます。

## 低消費電力、高性能を実現する 設計手法

デジタル信号処理のために Virtex-5 SXT アーキテクチャをフルに活用するには、次のシンプルなガイドラインに従うことをお勧めします。

- ・ **DSP48E スライスを最大限使用する**

フィルタ アルゴリズムをインプリメントする 25 X 18 ビットの各 DSP48E スライスは、500 スライス以上のプログラマブル ロジックに相当し、消費電力は相当するロジック インプリメンテーションの 10 分の 1 となり、また、単独、連結を問わず 550MHz のスピードで動作します。

### ・ DSP48E スライスのすべての機能を利用する

各 DSP48E スライスは、スタンドアロンの 25 X 18 乗算器、25 X 18 ビット 乗算器と加算器／減算器／アキュムレータ

タ、もしくは 48 X 48 ビットの加算器または減算器としてコンフィギュレーションできます。また、各 DSP48E スライスは SIMD 演算と正負対称丸め、もしくは偶数丸めをサポートします。

### ・ 固定小数点または浮動小数点演算をインプリメントする

DSP48E スライスは固定小数点の FIR、FFT、あるいは複雑なフィルタ演算に理想的なだけでなく、25 X 18 の入力サイズとカスケード配線により、2 個の DSP48E スライスを用いて効率的な 24 X 24 の符号なし浮動小数点演算を可能にします。

## デジタル信号アプリケーションに DSP48E スライスを利用する

Virtex-5 SXT プラットフォームに DSP48E スライスやブロック RAM、ロジック、マルチギガビット トランシーバを組み合わせることで、DSP フィルタ アプリケーションに対する費用対効果に優れた高性能、低消費電力のソリューションを実現できます。一例として、Virtex-4 SX と Virtex-5 SXT デバイスの両プラットフォームにインプリメントしたワイヤレス ラジオ カード アプリケーションについて、それらの消費電力を比較してみましょう。

WiMAX デジタル フロント エンド (DFE) は、デジタル アップ コンバージョン (DUC)／デジタル ダウン コンバージョン (DDC)、クレスト ファクタ低減 (CFR)、およびオートマチック ゲイン コントロール (AGC) を統合したものです。このデザインに必要なフィルタリングは、Virtex-4 SX25 FPGA または Virtex-5 SX35T FPGA で利用可能な DSP48E スライスにまさにぴったりです。このデザインは 276MHz で

表 1 実際のアプリケーションで測定した消費電力

| デザイン      | Virtex-4 消費電力 (W) | Virtex-5 消費電力 (W) | 低減率  |

|-----------|-------------------|-------------------|------|

| DUC + CFR | 0.858             | 0.552             | 35.6 |

| DDC + AGC | 0.740             | 0.478             | 35.4 |

| Total DFE | 1.598             | 1.030             | 35.5 |

動作し、Virtex-4 SX25 FPGA の場合は DSP48 リソースの 73% (128 のうち 95)、また Virtex-5 SX35T FPGA の場合は DSP48 リソースの 48% (196 のうち 95) を消費します。

WiMAX DFE ソリューションをインプレミントするために使われるパフォーマンスやリソースは、それだけでも驚かされますが、電力効率はさらに驚異的です。このデザインでは主に DSP48 または DSP48E スラ

イスを使いますが、ブロック RAM とロジックも使用します。表 1 に、これらのソリューションと実測消費電力、および Virtex-4 デバイスから Virtex-5 デバイスに移行することで消費電力がどれだけ低減するかを示します。

## 結論

デジタル信号処理の要求が増し、スケーラブルな高性能 DSP を提供することがます

ます難しくなる中、毎秒数百 GMAC 以上のレベルで消費電力を管理するのはいっそ困難になります。ザイリンクスの Virtex-5 SXT FPGA プラットフォームは、巨大な並列性を利用して消費電力を最小限に抑えながら超高性能を達成する、ユニークなシングルチップ ソリューションを提供します。ザイリンクスの DSP ソリューションの詳細は、<http://japan.xilinx.com/dsp> をご覧ください。

# ザイリンクス販売代理店オリジナルトレーニング

## 東京エレクトロン デバイス <http://ppg.teldevice.co.jp/>

| コース名                                       |

|--------------------------------------------|

| FPGA 設計導入コース (ISEコース)                      |

| ベーシック CPLD 半日コース (ISE WebPack コース)         |

| 初めてでも使える! Spartan-3 (Virtex-II) 設計コース      |

| 初めて作る!! Virtex-4 による高性能 FIR フィルタ設計実践 コース   |

| 動かす! わかる! Virtex-5 + DDR2 SDRAM 高速設計手法コース  |

| 初級ザイリンクス プロセッサ・ワークショップ (ハードウェア編)           |

| 初級 System Generator for DSP コース (初級DSPコース) |

| 動かす!! 高速シリアル IO 体験セミナー                     |

| ベーシック Verilog-HDL 記述コース                    |

| ベーシック VHDL 記述コース                           |

| SUZAKU-S を使用した MicroBlaze 開発フローコース         |

| 初めての Synplify/Synplify-Pro セミナー            |

| 開催日                  | 開催地                |

|----------------------|--------------------|

| * 開催日程はWebにてご確認ください。 | * 場所はWebにてご確認ください。 |

## 菱洋エレクトロ <http://www.ryoyo.co.jp/xilinx/seminar/list.cgi>

| コース名                    |

|-------------------------|

| ISE デザイン入力コース           |

| FPGA 設計導入コース            |

| FPGA 設計実践コース            |

| HDL 入門/VHDL 入門コース       |

| HDL 入門/VerilogHDL 入門コース |

| 開催日                                    | 開催地 |

|----------------------------------------|-----|

| 9月27日(木)、10月18日(木)、11月29日(木)、12月20日(木) | 東京  |

| 10月4日(木)                               | 大阪  |

| 11月8日(木)                               | 福岡  |

| 9月28日(金)、10月19日(金)、11月30日(金)、12月21日(金) | 東京  |

| 10月5日(金)                               | 大阪  |

| 11月9日(金)                               | 福岡  |

| 12月6日(木)~7日(金)                         | 大阪  |

| 10月17日(水)、12月19日(水)                    | 東京  |

| 10月3日(水)、12月5日(水)                      | 大阪  |

| 9月26日(水)、11月28日(水)                     | 東京  |

| 9月12日(水)、11月14日(水)、12月12日(水)           | 大阪  |

| 11月7日(水)                               | 福岡  |

## PALTEK <http://www.paltek.co.jp/seminar/index.htm>

| コース名                                  |

|---------------------------------------|

| 初級者のための ISE ハンズオントレーニング               |

| 初級者のための EDK ハンズオントレーニング               |

| 初級者のための DSP ハンズオントレーニング               |

| ISE デザイン入力コース                         |

| FPGA 設計導入コース                          |

| オープンソース ITRON on FPGA ハンズオントレーニング     |

| ANSI C から FPGA を実現 Impulse C 設計トレーニング |

| SUZAKU-S を使用した MicroBlaze 開発トレーニング    |

| VHDL 初級 ハンズオン トレーニング                  |

| Verilog-HDL 初級トレーニング                  |

| 開催日                                    | 開催地 |

|----------------------------------------|-----|

| 9月20日(木)、10月18日(木)、11月29日(木)、12月20日(木) | 新横浜 |

| 9月14日(金)、10月12日(金)、11月2日(金)、12月7日(金)   | 大阪  |

| 9月21日(金)、10月19日(金)、11月22日(木)、12月21日(金) | 新横浜 |

| 9月12日(水)、10月11日(木)、10月31日(水)、12月6日(木)  | 大阪  |

| 11月21日(水)                              | 新横浜 |

| 9月6日(木)、10月4日(木)、11月7日(水)、12月13日(木)    | 新横浜 |

| 9月7日(金)、10月5日(金)、11月8日(木)、12月14日(金)    | 新横浜 |

| 9月27日(木)                               | 新横浜 |

| 9月26日(水)                               | 新横浜 |

| 9月28日(金)                               | 新横浜 |

| 9月11日(火)                               | 大阪  |

| 9月5日(水)、11月28日(水)                      | 新横浜 |

| 9月13日(木)、11月1日(木)                      | 大阪  |

| 10月17日(水)、12月19日(水)                    | 新横浜 |

# DSP Performance of FPGAs Revealed

# 公開! FPGA の デジタル信号処理 DSP パフォーマンス

FPGA の DSP パフォーマンスを計測した OFDM ベンチマークの

最新レポート

Jeff Bier

President

BDTI - Berkeley Design Technology, Inc.

bdti@bdti.com

無線基地局などの高性能 DSP アプリケーションに使用する処理エンジンとして、FPGA を候補にするケースが増えています。これらのアプリケーションでは、FPGA と DSP のどちらかを選ぶか、あるいは両方を併用することになります。

選択肢の増加に伴い、システム設計者はさまざまなハイエンド FPGA とハイエンド DSP プロセッサの信号処理性能を正確に把握し、比較する必要があります。残念ながら、一般的に使われている性能値は信頼性に欠け、混乱を招くばかりか、実際とは逆の結果を示す場合さえあります。

たとえば、DSP アプリケーションは積和 (MAC) 演算に大きく依存するため、DSP プロセッサや FPGA ベンダは、デジタル信号処理の性能を比較するための単純なメトリックとしてピーク時の MAC/秒を使うことがあります。しかし、MAC のスループットでは FPGA と DSP のいずれの性能も正しく予測できません。その理由をいくつか見てきましょう。

## 単純なメトリックでは不十分

FPGA に対する MAC の性能値は、ハー

ドウェイア接続された DSP 要素は最高クロック レートで動作するという前提で算出されることが多いようです。実際には、一般的な FPGA デザインはそれより遅いスピードで動作します。また、ハードウェイア接続された要素を使うのは、FPGA に MAC をインプリメントする方法の 1 つにすぎず、プログラマブル ロジックのリソースと分散演算を用いて追加の MAC スループットを達成できます。この方法は、ハードウェイア接続された要素だけを使うより高い MAC スループットを達成できます。

もう 1 つ考えるべきポイントは、一般的な DSP アプリケーションは MAC 以外にもたくさんの演算に依存することです。たとえば、Viterbi デコーダは通信アプリケーションに使われる重要な DSP アルゴリズムですが、これは MAC をまったく使用しません。

信号処理性能を評価するためのもう 1 つの方法は、FIR フィルタなどのよくある DSP ファンクションを使うことです。しかし、この方法には問題点もあります。1 つの問題は、ベンダによってこれらファンクションの実装方法が異なることです。データ幅、アルゴリズム、あるいはレイテンシなどの実装パラメータがそれぞれ異なるわけです。このため、ベンダが提示する結果をそれぞれ単純に比較することはできません。

そのうえ、FPGA のフル アプリケーション内でファンクションをインプリメントするのと、そのファンクションを単独でインプ

リメントするのとではかなりやり方が異なるため、小さなカーネル ファンクションは FPGA のベンチマークングに有効ではありません。ただし、プロセッサの場合はこれら小さなベンチマークで DSP アプリケーションの全体性能を十分正確に予測できます。最後に、プロセッサや FPGA のベンダがインプリメントしたベンチマークは第三者によって検証されないことから、エンジニアがそれぞれのデバイスを確信をもって比較するのが難しいという点も問題です。

## ギャップを埋めるのは 第三者のベンチマーク

BDTI 社は信号処理ベンチマークで最も信頼されている会社です。当社のベンチマークは、数十の半導体ベンダと数千のチップユーザーが、信号処理エンジンを評価、比較、選択するために採用しています。BDTI 社は 15 年近くにわたりプロセッサの信号処理性能をベンチマークし、現在では FPGA、マルチコア チップ、その他のテクノロジもカバーするまでになりました。

BDTI 社は数年前、DSP アプリケーションをターゲットとする FPGA とプロセッサのパフォーマンスを、第三者的な立場から同じ基準で正確に比較できるようにする必要があると考えました。これを実現するため、BDTI 社は直交周波数多重分割変調方式 (OFDM: Orthogonal Frequency Div

BDTI 社の新しいレポート「FPGAs for DSP, Second Edition」は、FPGA の信号処理に関する客観的なベンチマーク結果をお届けする信頼できる情報ソースです。

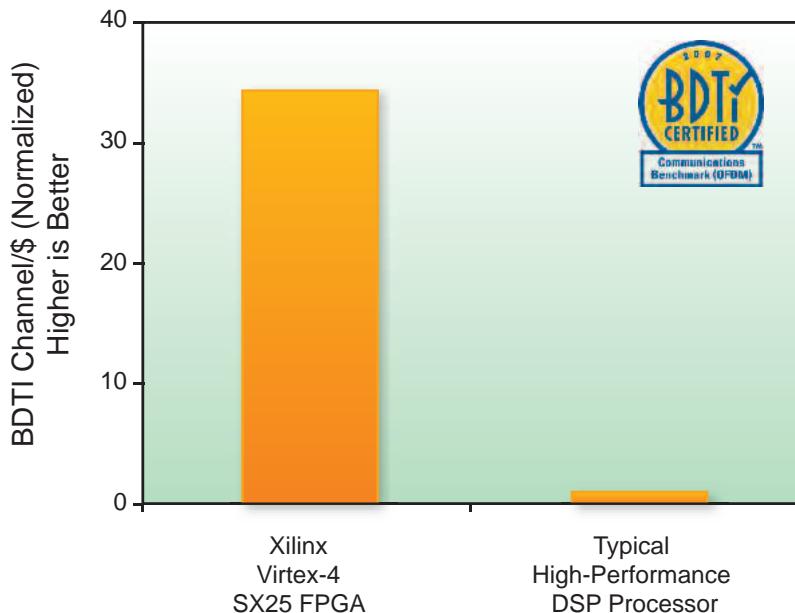

図 1 BDTI Communications Benchmark (OFDM)

BDTI 社認定のコスト パフォーマンス最適化結果

ision Multiplexing) レシーバに基づき、BDTI Communications Benchmark (OFDM) という新たなアプリケーション指向のベンチマークを開発しました。このベンチマークは、DSL、ケーブル モデム、ワイヤレス システムなどのアプリケーション向け通信機器で増えつつある、「ベースバンド」信号処理の負荷を把握するためのものです。このベンチマークは FPGA、DSP プロセッサ、マルチコア チップ、その他多数の信号処理エンジンでのインプリメンテーションに適しており、同じ基準で比較したベンチマークの結果を提供します。

BDTI 社は最近、数種類の新しい高性能 FPGA と DSP プロセッサを評価するため、BDTI Communications Benchmark (OFDM) を使用しました。解析結果の詳細は BDTI 社のレポート「FPGAs for DSP: Second Edition」として公開されており、DSP システム設計者の間で大きな注目を集めました。レポートにはベンチマーク結果が 2 セット掲載されており、1 つはチッ

プ当たり最大数のチャネルをサポートするよう最適化した大容量の結果、もう 1 つはチャネル当たりのコストを最低限に抑えるよう最適化した低成本の結果です。図 1 は、Xilinx® Virtex™-4 SX25 FPGA と代表的な高性能 DSP プロセッサに対する正規化した低成本の結果を示しています。

図 1 に示す BDTI 社のベンチマーク結果を見れば、高性能 DSP アプリケーションに FPGA を使うことがいかにコスト面で有利か一目瞭然です。このベンチマークでは、Virtex-4 SX25 デバイスは代表的な高性能 DSP プロセッサと比較して費用対効果が 10 倍以上優れています。FPGA は、アプリケーションによっては DSP よりチップレベルのコスト パフォーマンスに優れているかもしれないが、どれだけ優れているのか確信をもてずにいたシステム設計者にとって、これはきわめて貴重な情報です。同レポートでは、各ベンダの FPGA に対するコスト パフォーマンスの結果も比較しています。

もちろん、新しいシステム デザインに

FPGA を使うか否かや、使う場合どの FPGA を使うべきかなどを、ベンチマークの結果だけで判断するわけにはいきません。設計者は、処理エンジンの選択が開発の流れやインプリメンテーション、システム デザインにどう影響するかも理解する必要があります。このような理由から、BDTI 社のレポートは FPGA と DSP のどちらを使うか、あるいは両方を使うべきかを判断するための質的要因を掘り下げると共に、いかにして信頼性の高い情報を基に選択するかについて、ガイドラインを提供しています。さらに、同レポートは FPGA のエネルギー効率や FPGA に対する新たなハイレベルな合成ツールの有効性など、ハイエンドな DSP アプリケーションで FPGA が長期にわたって成功するための重要なポイントにもスポットを当てています。

## 結論

BDTI 社はこれら分野でのさらなる解析を進めていくと共に、新しい FPGA とプロセッサの信号処理能力を評価し続けています。信号処理エンジンの競争が激しさを増す中、BDTI 社は設計者が自信をもって選択できるようデータと解析結果を提供し続けます。

BDTI 社の新しいレポート「FPGAs for DSP, Second Edition」は、FPGA の信号処理に関する客観的なベンチマーク結果を提供する信頼できる情報ソースです。

「FPGAs for DSP, Second Edition」の詳細は、<http://www.BDTI.com/fpgas> 2006

をご覧ください（同サイトよりオンラインでレポートをオーダーすることも可能です）。また、BDTI 社の詳細は <http://www.BDTI.com> をご覧ください。

# Video Processing Using FPGAs in Video Surveillance Systems

# FPGA を用いたビデオ監視システムの映像処理

## ザイリンクス Video IP Block Set を使った DVR のインプリメント

Hong-Swee Lim

Senior Manager, DSP Product and Solutions Marketing

Xilinx Asia Pacific Pte. Ltd.

hong-swee.lim@xilinx.com

David Zhang

DSP Specialist

Xilinx Asia Pacific Pte. Ltd.

david.zhang@xilinx.com

ビデオ監視システムは、駅や空港、銀行、カジノ、ショッピング モール、そして一般家庭において、セキュリティのための重要なツールとして利用されています。セキュリティリスクの増大に伴い、状況を視覚的に監視、記録する必要性は、多岐の用途にわたるようになりました。このため新しいアーキテクチャでは、ビデオ監視システムの多種多様な要件を満たす費用対効果の高いソリューションを実現する優れたスケーラビリティが必要不可欠となっています。

Time-to-Market のプレッシャーに加え、新たな CODEC 規格や幅広い要件（高度なオブジェクト検出、モーション検出、オブジェクト追跡、オブジェクト追跡の各種機能）への対応など、新たなビデオ監視アーキテクチャをめぐる課題は数多くあります。こうした課題に応えるため、広範なパフォーマンスに対応できる拡張可能な実現手段が求められているのです。

ザイリンクスの FPGA は、ローエンドからハイエンド、スタンダードアロンから PC アドオン カードにいたるまで、ビデオ監視システムに理想的なソリューションです。

### ビデオ監視システムと DVR システム

ビデオ監視システムのデジタルビデオレコーダ (DVR) に、先進のデジタルビデオ圧縮技術が急速に採用されつつあります。ほとんどの DVR メーカーが MPEG4 から H.264 高品位 (HD) CODEC に移行するなか、解像度と圧縮率の改善がますます求められています。ASSP (特定用途向け汎用 IC) は量産アプリケーションには適していますが、柔軟性に欠け、開発費が高く、開発期間も長くなりがちです。たいていのデジタルメディアプロセッサは H.264 HD デコーディングをどうにか実行できる程度にすぎません。(H.264 HD エンコーディングにいたってはデコーディングよりも複雑です。) H.264 HD に求められるパフォーマンスを達成するための最善の方法は、

FPGA と外部の DSP もしくはデジタルメディアプロセッサを併用することです。

低コストのザイリンクス FPGA を使えば、さらに一步進んで、モーション検出やビデオスケーリング、カラー スペース変換、ハードディスクインターフェイス、DDR2 メモリインターフェイスを実現できる

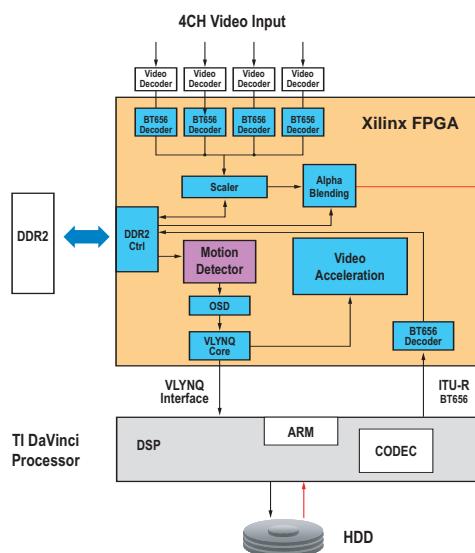

だけでなく、DSP プロセッサにビデオアクセラレーションを提供することで 2 つの 27MHz ITU-R BT656 データストリームを 1 つの 54MHz データストリームに時間多重化が可能です。2 つの ITU-R BT656 データストリームを 1 つの ITU-R BT656 データストリームに多重化することで、1 チャンネルのビデオポートを使って 2 チャンネルのビデオデータ全体を独立して転送できるのです。これは、1 個の ITU-R BT656 ビデオ入力ポートしか持たないデジタルメディアプロセッサとインターフェイスするのにとても便利です。図 1 は、このようなアーキテクチャのブロックダイアグラムを示したものです。

1 個の ITU-R BT656 ビデオ入力ポートしか持たない Texas Instruments 社の DaVinci プロセッサを使う DVR デザインの

図 1 FPGA とデジタルメディアプロセッサを使用するビデオ監視システム

場合、DaVinci プロセッサに送る前に 2 つ以上の ITU-R BT656 データストリームを 1 つの VLYNQ データストリームに時間多重化すればさらに効率的にインプリメンテーションが可能です。このインプリメンテーションでは、より少ない I/O ピンでビデオストリームを転送できることから、より小さなパッケージ デバイスを使用でき、結果としてシステム コストを削減することができます。図 2 に、このデザインのブロック ダイアグラムを示します。

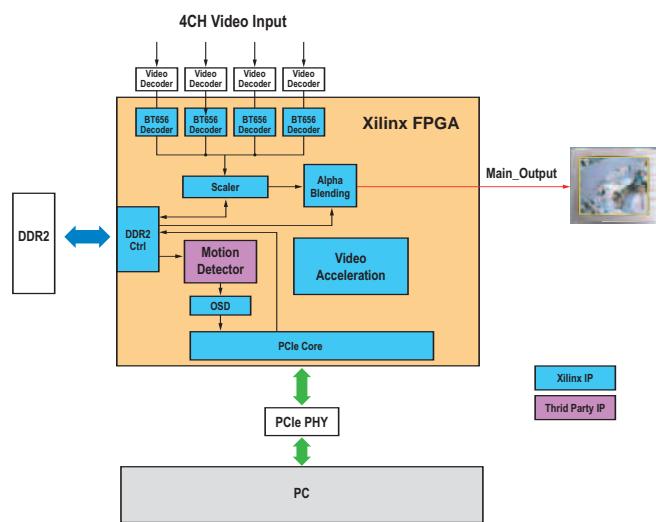

## PC アドオン カードの DVR システム

PCI バスは、過去 10 年間にわたり PC に採用されてきました。しかしながら、今日の PC アドオン カード DVR システムは、PCI バスでは対応できないほど高いバンド幅を必要とします。ブランкиングを除去すると、非圧縮ビデオのデータは約 165Mbps です。したがって、PCI の総バンド幅が 1Gbps の場合、1 本の PCI バスで併用できる非圧縮ビデオのキャプチャもしくは再生デバイスは最高 6 台までに限られます。バス上のバンド幅を減らすためアドオン カードに MPEG4 CODEC チップセットを使う方法もありますが、コストが高くなるうえ、既存の MPEG4 チップセットに縛られることになります。

PCI Express 技術はスルーパットを大幅に

高めます。PCI Express はレーンに分かれており、各レーンはそれぞれ双方の差動ペアからなり、方向ペア当たりのデータ スルーパットは 2Gbps です。マザーボード上の各 PCI Express スロットは、他のスロットと共有されない専用レーンを持ちます。各スロットは 16 レーン (x16)、8 レーン (x8)、4 レーン (x4)、もしくは 1 レーン (x1) でコンフィギュレーションできます。つまり、PCI Express では、それぞれのカードは 2Gbps (x1 レーン) から 32Gbps (x16 レーン) までのデータを提供できます。PCI Express のデータ スルーパットだと、PCI カードあたり 6 チャネルの非圧縮ビデオという制約から解放されます。

図 1 と同じデザインを使い、デジタル メディア プロセッサを PC に置き換えて、PCI Express バスを通して PC にビデオストリームをスプールすることで、PC アドオン カード DVR システムを素早く簡単にインプリメントできます。ビデオ アナログ/デジタル コンバータは、4 つの独立した ITU-R BT656 ストリームを生成し、それらストリームを低コスト Spartan™-3 デバイスへ送り、プリプロセッシングを行います。ビデオデータは FPGA でブランクと同期を取り除かれ、PCI Express 用に適切にパケット化されてからザイリンクスの PCI Express コアへ送信されます。その後、ソフトウェア上で、入力ビデオを表示、処理、あるいはディスクに

保存します。図 3 に、PC アドオン カード ビデオ監視システムのデザインを示します。

## ザイリンクスのビデオおよび画像処理アルゴリズム

ザイリンクスの FPGA は、ポリフェーズ ビデオ スケーラから 2 次元 FIR フィルタ、オンスクリーン ディスプレイ、オーバーレイ、アルファ ブレンディングなどのシンプル エフェクト、フォーマットおよびカラー スペース変換にいたるまで、リアルタイムのデジタル ビデオ、画像処理、フィルタリングに理想的なプラットフォームです。表 1 は、Video IP Block Set の一般的なアプリケーション ノートです。

ザイリンクス FPGA は抜群の DSP 処理能力を誇り、1080p という非常に高い解像度をサポートできるため、大型 DSP アレイの数を減らすことが可能となります。ザイリンクスの FPGA はリプログラマブル ハードウェアであるため、斬新かつ高性能な ハードウェア ベースのビデオ/画像処理アルゴリズムを簡単に実験できることから、最終製品における差別化へと直接つながります。

## すぐに使える IP

ザイリンクスは、ビデオ監視システムにおけるビデオ/画像処理アルゴリズムを迅速にデ

図 2 FPGA と DaVinci プロセッサを使用するビデオ監視システム

図 3 PC アドオン カード ビデオ監視システム

ザイン、シミュレート、インプリメント、検証で きるよう、Video IP Block Set を提供して います。Video IP Block Set には、DVR を デザインするための基本的なプリミティブと 高度なアルゴリズムが用意されています。

さらに、ザイリンクスはパートナーと共に、 高速なインプリメンテーションを必要とする 設計者用の既製品コアから、より低いビット レートでより高いクオリティを実現することで 製品を差別化したい設計者用のビルディング ブロック リファレンス デザインとハ ドウェア プラットフォームにいたるまで、幅 広い圧縮コーディング、デコーディング、コー デック ソリューションを提供しています。

特定のコーデック ブロックにおける極めて 集中的な処理にザイリンクスの FPGA を 使用することで、マルチチャネルの HD コーディングをサポートし、貴重なシステム プロセッサ サイクルを節約し、DSP プロセッサ アレイを削減もしくは除去することで コストを大幅に低減します。また、インター フェイスから追加のビデオ処理にいたるま で、システムにより多くの機能や特長を容易 に統合でき、加えて、FPGA はスケーラブル なソリューションを提供するため、同じシ ステムで異なるプロファイルや追加のチャネル、あるいは新しいコーデック スキームを サポートできるのです。

さらにザイリンクスの FPGA は、システム ロジックを併合して新しいペリフェラルを インプリメントすることで DVR システムの コストをいっそう削減できます。また、ザイ リンクスはパートナーと共に、先進のビデオ インターフェイス、PCI Express、Texas Instruments 社の VLYNQ と EMIF インターフェイス、ハードディスク インターフェイス、ITU-R BT656 インターフェイスなど、ビデオ監視システムを短期間で開発するためのさまざまなシステム インターフェイスも 提供しています。

## ザイリンクスのツールで デザインを簡単に

ザイリンクスの System Generator for DSP により、Video IP Block Set を用いて Simulink で高性能 DVR システムを構築、デ

表 1 Video IP Block Set アプリケーション ノート

| 機能                              | アプリケーションノート |

|---------------------------------|-------------|

| Polyphase Video Scaler          | XAPP929     |

| Color Space Converter RGB2YCrCb | XAPP930     |

| Color Space Converter YCrCb2RGB | XAPP931     |

| Chroma Resampler                | XAPP932     |

| 2D FIR                          | XAPP933     |

| 2D Rank Order Filter            | XAPP953     |

バッグできます。ビデオ処理アルゴリズムを 開発、インプリメントするために System Generator for DSP を使うことで、完全 に検証され容易に実行可能なデザインを 実現できます。

ザイリンクスは、新たにさまざまなプリテ スト済みの Video IP Block Set を開発しま した。これを使用することにより、System Generator for DSP 内でブロックをド ラッグ & ドロップするだけでビデオ/画像処理 システムを簡単に構築できます。これは、HDL を使って基本的なビルディング ブロ ックをコーディングするより、大幅な時間の 節約となります。

開発ボードから PC への膨大なビデオ データ ストリームに対応するため、System Generator for DSP は、イーサネット インターフェイスを通して行うもう 1 つの革新的な高速ハードウェア協調シミュレーション 手法を導入しています。このインターフェイ スは低レイテンシでの高スループットを可能 にし、System Generator for DSP 環境で ビデオ/画像処理システムを構築する際にき わめて効果的であることが実証済みです。

MATLAB 言語をベースとするザイリンクス のもう 1 つのデザイン ツール、AccelDSP 合成ツールは、ザイリンクスの FPGA 向けに DSP ブロックをデザインする ための高水準な MATLAB 言語ベースのツー ルです。このツールは浮動小数点から固定小 数点への変換を自動化し、合成可能な VHDL または Verilog を生成し、検証のためのテ 斯ト ベンチを作成します。MATLAB アルゴリズムから固定小数点の C++ モデルや System Generator ブロックを生成する ことも可能です。AccelDSP は、最先端の

FPGA、設計ツール、IP コア、パートナーシッ プ、そしてデザインおよび教育サービスを組み 合わせたザイリンクス XtremeDSP™ ソリ ューションの重要なコンポーネントです。

## 結論

ビデオ監視システムでは、ビデオ信号は複 数のカメラにより生成されます。FPGA は ビデオ デコーダから ITU-R BT656 フォーマットでデジタル ビデオを受信し、処理済みのビデオを表示するためにモニターに 出力すると共に圧縮やハードディスクへの格 納のためにデジタル メディア プロセッサや DSP に出力します。

ザイリンクスの FPGA を使うことにより、 標準に準拠するシステムを競合他社の製品から 差別化しつつ、アプリケーションに応じた最 適なバランスで達成できます。また、ザイリンクス の Video IP Block Set により、ローエンドとハイエンド両方の市場に向けて柔軟性と 拡張性の非常に高い DVR システムを簡 単に構築できます。PCI Express コアを Video IP Block Set と統合することで、低コ ストな PC アドオン カード ビデオ監視シス テムの開発も可能となります。また、ザイリンクス FPGA に用意されている VLYNQ コアに より、ザイリンクスの FPGA を通して、複数 のカメラから Texas Instrument 社の DaVinci プロセッサに多数のビデオ ストリー ムとの接続を簡単に行なうことができるのです。

ザイリンクスの System Generator for DSP に AccelChip を統合したことにより、アルゴリズム開発者が好む MATLAB ベースのアルゴリズム合成は、システム設計者やハードウェア設計者の間で使われている グラフィカルなデザイン フローと連携します。 これは複雑な DSP アルゴリズムからなる System Generator IP ブロックを作成する ために、MATLAB 言語とそれに付属する 豊富なツール ボックスを使います。これらの ツールを組み合わせて使用することで、設計 チームはインプリメントするハードウェアをモ デル化するための最も効率的な方法を使い ながら、FPGA デザイン プロセスにアルゴリズムの開発を完全に取り込んでより高品質な デザインをより迅速に作成できるのです。

# Develop Imaging Systems with the Right Mix of Technology 技術の最適な組み合わせによる 画像処理システムの開発

画像処理用開発システム SMT339 による DSP と FPGA の連携

Justin Wheatley

Systems Manager

Sundance Multiprocessor Technology Limited

[justin.wheatley@sundance.com](mailto:justin.wheatley@sundance.com)

画像処理アプリケーションでは、1 つのアプリケーションで多数のプロセスを同時に実行することが求められます。そこで多くの場合、複数の DSP を用いて処理能力を高め、大きなサイズの FPGA に数多くのファンクションを盛り込んでデザインされます。しかし、これは、手間やコスト、効率を考えると、かならずしも最善のアプローチとは言えません。オブジェクト認識などの高水準な画像処理アルゴリズムは、最近の高速な画像処理 DSP に最適ですが、FFT やエッジエンハンスメント（輪郭補正）、あるいは MPEG-4 エンコーディングなどは、並列処理利用する大型かつ高速の FPGA で処理するのが適します。

最良の解決策はこの 2 つのテクノロジを併用することですが（Xcell Journal 58 号英語版の記事「The Benefits of FPGA Coprocessing」を参照）、DSP と FPGA のデザインはまったくの別物であり、設計手法からスキル、ツール、そして担当する人々までまったく異なります。こうした違いは、共同でデザインするうえで円滑な進行の妨げとなります。このため、両方のテクノロジを併用するという考えは、いずれか一方のみを専門とするエンジニアにとっては受け入れがたいでしょうし、どちらにも精通しない人にとっては特に不可解でしょう。また、1 つのテクノロジだけを利用する場合とは異なる

り、ハードウェアの統合にも膨大な手間がかかります。

本稿で解説する Sundance 社の SMT339 は、小型で柔軟、拡張性に優れたユニットに卓越した画像処理アプリケーションを実現できるように設計された、画像処理ソリューションのためのパワフルな開発システムです。SMT339 の代表的な機能としては、ビデオ画像の中で動いている人物をハイライト表示する追跡システムなどの画像処理機能があります。

## 設計者の期待に応えるパフォーマンス

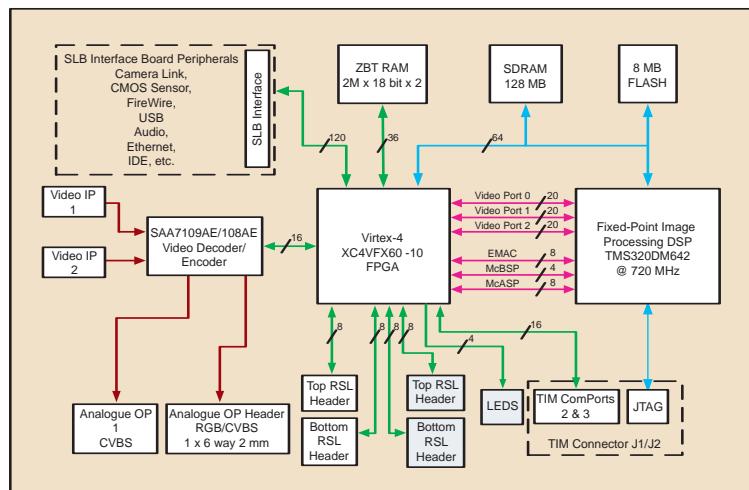

図 1 は SMT339 のハードウェアです。

図 1 画像処理モジュールのハードウェア ダイアグラム (SMT339)

図 2 人物追跡システムのデータフロー ダイアグラム

TIM (Texas Instruments Module) フォーム ファクタに準拠する SMT339 は、PCI、PCI-X、VME、Compact-PCI といったキャリアにマウントされるか、単体でマウントされます。キャリアは、モジュールの格納場所であると共に電源でもあり、通常、ホスト コンピュータへのインターフェイスになります。

システムにはビデオ デコーダを通してさまざまなアナログ ビデオ フォーマットを接続できます。また、所定の I/O ドータボードに各種デジタル ビデオ ソースを接続することも可能です。入力ソースは、ザイリンクスの FPGA である 60,000 ロジック セルの Virtex™-4 FX60 デバイスに配線されています。データは DSP に渡される前に

プリプロセスできます。

FPGA は、FPGA で実行されるさまざまなプリプロセッシングとポストプロセッシング ファンクションのフレーム ストアに理想的な 2 個の独立した 8MB ZBTRAM バンクを持ちます。

DSP は、Texas Instruments 社の TMS320DM642 ビデオ デジタル信号プロセッサです。この DSP は、C64x DSP レンジと完全にソフトウェア互換である Texas Instruments 社の Code Composer Studio を用いてプログラミングできます。クロック周波数 720MHz で 5.76GMAC/秒を達成でき、3 つの双方向ビデオ ポートにより FPGA にリンクされる他、コントロールとその他のデータ用に追加のポートもあります。図に示されている配線はどれも FPGA にすでにインプリメントされているため、アプリケーションに応じて必要なファンクションを自由にインプリメントするだけで使用できます。また、DSP は 128MB の高速 SDRAM を備えています。この 64 ビット幅のメモリには、DSP とプログラム/データ スペース用のイメージ バッファがあります。

FPGA からビデオ エンコーダへは出力が可能で、未処理、一部処理、もしくは完全処理のライブ イメージをモニターに直接表示することができ、アルゴリズムの開発時に大変便利です。デジタル出力は、Sundance LVDS バス (SLB) インターフェイスに接続されている所定の I/O ドータボード、もしくは高速シリアル リンクから得られ、他のモジュールとの相互接続は 4 本の Sundance ロケット シリアル リンク (RSL) の形でザイリンクスの 16 本の RocketIO™ チャネルによって提供されていることから、システムは極めて高い拡張性を持ちます。

## 比類ない優れた機能

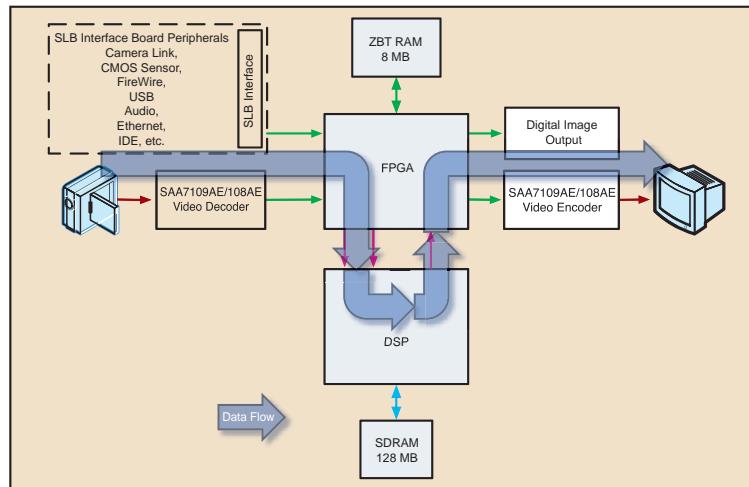

図 2 は、人物追跡の画像処理システム用にコンフィギュレーションした場合に、画像データがハードウェア リソースをどのように流れれるかを示したものです

ビデオはビデオ デコーダによりキャプチ

やされ、FPGA に送り込まれます。デコードは、PAL/NTSC CVBS または別の YC からのさまざまな入力フォーマットに対応します。また、データボードのデジタルインターフェイス モジュールを通してデジタルビデオを入力することも可能です。

FPGA はイメージ バッファとして、ZBTRAM バンクの 1 つを使って着信ビデオ ストリームをプリプロセスします。スローモーションのリファレンス イメージは、各ピクセルをフレーム当たり 1 ビットずつ現在のイメージの値に繰り返すことで維持されます。差分画像は現在のイメージとリファレンス イメージと比較することで計算されます。

大型でパワフルな FPGA を搭載するこのシステムの利点として、空間フィルタ、エッジ エンハンスメント フィルタ、ヒストグラム ファンクションといった各種プリプロセッサを簡単に試し、システムのライブ出力で結果をすぐに見ることができます。

計算された差分画像は、現在の画像と一緒に DSP に送信されて解析されます。DSP は差分画像に検出アルゴリズムを実行し、シルエットを抽出して画像の動いている部分で人物の特徴的な形状を探します。ここから、表示領域に検出された人物について次のようなさまざまな属性を計算します。

- ・その人物を取り囲む対象領域の四隅の座標

- ・中心点（その領域の四隅の中央ポイントとして計算）

- ・求心点（シルエットの領域の中央を基点とする）

- ・輪郭全体の座標（シーンのバイナリ オーバレイ画像として返されることがある）

次に、FPGA はこの情報をポストプロセスし、それをソース画像と再び組み合わせます。たとえば、人物の周囲に輪郭を重ね、色を変更したり、他の操作を実行したりできます。

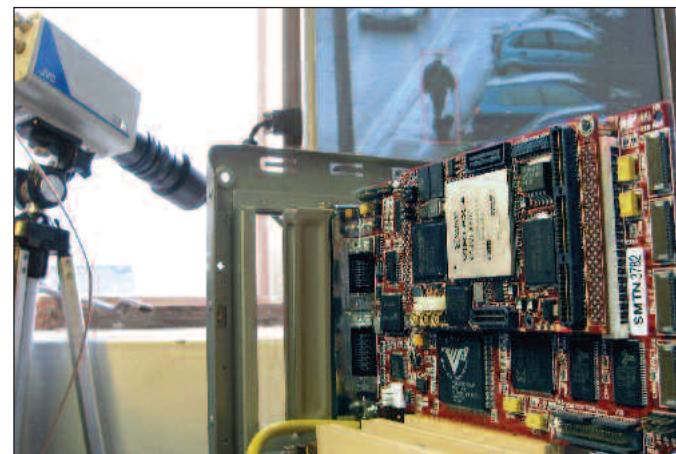

計算結果は図 3 に示すようにライブビデオ出力で見ることができます。データボードや他のインターフェイスを通してデジタルビデオ システムに転送したり、これらシステムにログ、あるいは表示したりできます。

## ソフトウェアのサポートの役割

DSP エンジニアのなかには、原理として素晴らしいことは納得できても、実際に連携させるにはどのようなコツがいるのか、疑問に思う方もいるでしょう。幸いなことに SMT339 は、Sundance 社の多くのモジュールと同様、包括的な開発ツール環境にサポートされており、このような問題を解消します。

混合プロセッサ システムに対するアプリケーション開発全体を単純化するには、多くの VHDL コアと DSP ライブリ モジュール以外に、コヒーレントなソフトウェア モデルが必要です。3L Limited 社の Diamond は、マルチプロセッサ システムをチャネル経由で通信する多数の独立したタスクとして記述することができます。これらのタスクが DSP と FPGA のどちらで実行されるにせよ、相互接続とプログラミングは Diamond により管理されるため、設計者はアプリケーションに専念できます。

Diamond は、エンジニアのタスクを Sundance 社の標準的なファームウェアに自動的に追加することで、Sundance DSP TIM 上で FPGA を使用します。これらのタスクは VHDL もしくはザイリンクスの System Generator for DSP などのツールで作成されるか、標準的なネットリスト ファイルを利用して、システムにプロプライエタリなコアを取り込んで標準コアおよびユーザー開発コアと混在させることができます。Diamond は、タスクが他のタスクとやり取りできるように自動的にロジックを追加し、その後ザイリンクスの標準的なツールを用いて FPGA ビットストリームを作成します。

このテクニックではハードウェアに独立性を確保できるため、コードをいっさい変更せずに基礎となるハードウェアに大

規模な変更を加えることができます。膨大なリコンパイル作業に手間をかけることなく、必要に応じて、DSP や FPGA を追加することでハードウェアを拡張できるのです。別の DSP にタスクのポジションを変えることは、1 つのテキスト ファイルをほんの少し変えるだけで済みます。したがって、より多くの処理能力が必要になった際その都度追加すればよいため、現在進めている開発に支障をきたすことはありません。アクセラレーションのためにタスクを DSP から FPGA に移す必要がある場合でも、周囲のファンクションが影響を受けることはありません。

## 結論

FPGA と DSP それぞれの長所を組み合わせるという難しい技術は、デリケートな統合が既に済んでいるスケーラブルなシステムを利用することで単純化できます。包括的なソフトウェア環境によってサポートされていることから、そのような複雑なハードウェアでもニーズに応じて適応させることができ、全体的な処理能力を目的のアプリケーションに合わせて微調整できるのです。ソリューションの開発後はモジュール型のアプローチを使い既製のモジュールから実稼動システムを効率的に構築できます。

FPGA および DSP システムの構築についての詳細は、<http://www.sundance.com> をご覧ください。

図 3 単純なシステムに採用した Sundance SMT339

# Building a 3-Gbps eSATA/SATA Hardware RAID 5 Solution 3Gbps eSATA/SATA ベース RAID 5 ソリューションの構築

革新的 RAID ストレージを提供する

ザイリンクス FPGA

Paul Chu

Director of Product Marketing

Accusys, Inc.

[paulchu@accusys.com.tw](mailto:paulchu@accusys.com.tw)

Jason Lin

Hardware Design Manager

Accusys, Inc.

[jasonl@accusys.com.tw](mailto:jasonl@accusys.com.tw)

Cliff Tsai

Senior Field Application Engineer

Xilinx Taiwan Pte. Ltd.

[cliff.tsai@xilinx.com](mailto:cliff.tsai@xilinx.com)

RAID（独立ディスクの冗長アレイ）技術は、データの保護やシステムの可用性の向上、システム性能の改善を目的に、ハードディスク搭載のシステムに広く採用されてきました。Accusys 社は、低価格で高性能な ATA ハードウェア RAID 5 ソリューションなど、多彩な RAID 製品を送り出してきました。

Accusys 社は、3Gbps SATA2 規格をサポートする次世代の eSATA RAID 製品を開発するにあたり、ザイリンクスの Virtex™-4 FX FPGA を用いて eSATA ホストインターフェイス コントローラと RAID エンジンをインプリメントしました。本稿では、3Gbps eSATA RAID ソリューションの利点と Virtex-4 FX FPGA の役割について説明します。

## RAID の基本

RAID のアルゴリズムにはさまざまな種類があり、それに応じて性能、信頼性、容量が異なります。RAID 0 は、複数のディスク ドライブにデータを同時に分散することで I/O 性能を改善すると共に、單一ディスク ドライブより大容量です。しかし、RAID 内のディスク ドライブがどれか 1 つでも故障すると、データが失われてしまいます。データを保護するには、元のデータを再生する必要が生じた場合に備えて、そのデータに関連する追加情報を格納する必要があります。

RAID 1 はデータを 2 つのディスク ドライブに同時に格納するため、一方のディスク ドライブが故障してもデータは保たれます。ただし、この場合は 2 倍の記憶容量が必要になるため、非常に高価です。RAID 5 は、他にディスク ドライブがいくつあろうと、データを保護するには 1 つのディスク ドライブの容量で済むため、最も費用対効果に優れたソリューションです。また、データが RAID 0 のように複数のディスク ドライブに分散されるた

め、パフォーマンス面でも優れています。このため、現在利用されているストレージシステムのほとんどは RAID 5 を採用しています。

## ハードウェア RAID の利点

RAID 処理は、ホスト コンピュータで動作しているソフトウェア（ソフトウェア RAID）、もしくは専用の RAID プロセッサ（ハードウェア RAID）によって実行されます。とはいっても、ほとんどの基幹システムやヘビーデューティなアプリケーションには、ホスト コンピュータで膨大なリソースを費やすソフトウェア RAID より、最適化されたハードウェアで高いパフォーマンスを発揮できるハードウェア RAID が適しています。また、ハードウェア RAID のほうがディスク ドライブのデータを短時間で再生でき、そのぶん RAID を高速に正常な状態に回復できるため、信頼性にも優れています。このような理由から、現在主流の RAID 製品はすべてハードウェア RAID をベースにインプリメントされています。

## 高速、低価格の eSATA

RAID ソリューションの特徴の 1 つとして、ホスト コンピュータが RAID ストレージにアクセスするためのホスト インターフェイスがあります。一般に使われているホスト インターフェイスは、ファイバ チャネルのような RAID カードと SCSI ファミリの接続用、もしくは RAID システム向けシリアル接続 SCSI 用の PCI-X と PCI Express です。これら 2 種類のインターフェイスは高性能ではあるものの、インストール手順が複雑なため、IT に詳しくないユーザーでは RAID ソリューションを使用するのは困難です。一方、eSATA インターフェイスは外部記憶装置を簡単に接続できることから、デスクトップコンピュータで人気を得ています。

eSATA は 3Gbps の高速シリアル接続を実現しており、マルチタスク アプリケーションやマルチストリーム画像処理を最適化するためのネイティブ コマンド キューイング (NCQ) をサポートします。さらに、eSATA デバイスにアクセスするために追加のドライバやアドオン カードをインストールする必要

がないため、コストが安く使い勝手も向上します。このため、ホスト インターフェイスとして eSATA を使う RAID 記憶装置は、パフォーマンスと使い勝手の点から優れたソリューションと言えます。

## 従来の技術

現在市販されているほとんどの eSATA RAID 製品は、ハードウェア RAID 5 をサポートしていないため、アプリケーションの分野が大きく限られています。これら製品にインプリメントされている RAID は SATA ポート マルチプライヤから派生したもので、パケットを送信し、RAID 0 や RAID 1 といった基本的な RAID レベルのみをサポートします。RAID 0 は画像編集などの高性能アプリケーションには有用ですが、ユーザーが定期的にバックアップする必要があるうえ、セクタ不良やドライブのクラッシュによる突然のデータ消失という心配もあります。RAID 1 ではデータは保護されますが、膨大な容量が無駄になるうえ、パフォーマンス上の利点もありません。

現在出回っている他の eSATA RAID ソリューションと異なり、オンチップの「Accusys ACS-76000 RAID」システムはハードウェア RAID 5 を提供します。しかし、そのパフォーマンスは 1.5Gbps SATA1 スピードにより制限されています。高品位なメディア コンテンツや他のアプリケーションが一般化すれば、より高性能なソリューションが必要になるでしょう。

## インプリメンテーションの概要

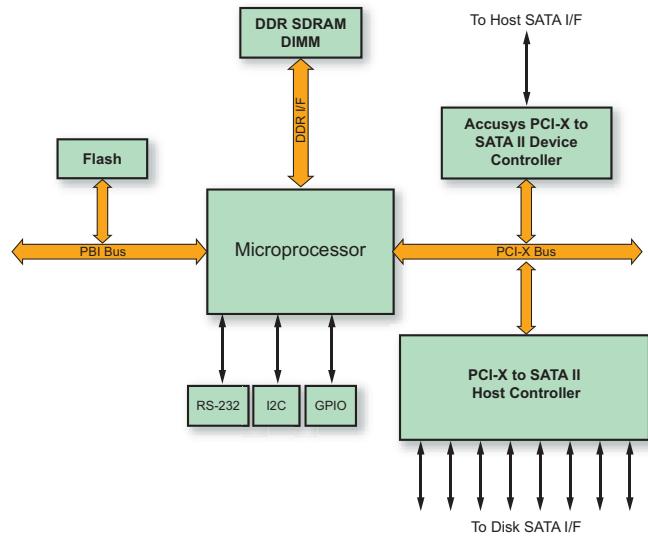

高性能化に向けて最初に必要なのは、ストレージのインターフェイスを SATA1 から SATA2 にアップグレードし、3Gbps をサポートすると共に NCQ をサポートできるようにすることです。第 2 の要件は、プロセッサ

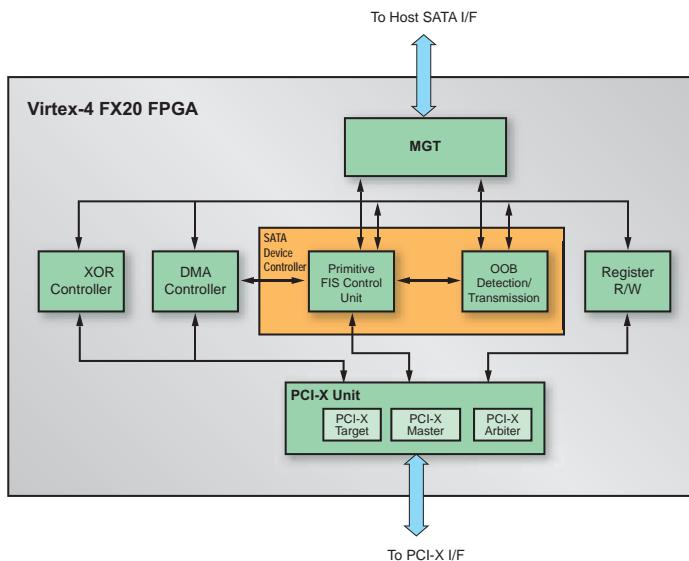

図 1 SATA2-SATA2 RAID コントローラのブロック ダイヤグラム

に接続するための高性能な標準バスを用意することです。Accusys 社は、高性能なエンベデッド システムに一般に使われているという理由から PCI-X を選択しました。最後に、ハードウェア RAID 5 の処理をサポートするには、パリティを計算してデータを再生するため排他的論理和 (XOR) エンジンが必要です。図 1 に、SATA2-SATA2 RAID コントローラ ボードのブロック ダイヤグラムを示します。

Accusys 社は、3Gbps SATA ホスト インターフェイスをインプリメントするためのマルチギガビット シリアル I/O を備えていること、MGT ハード コアのデジタル パラレル バス インターフェイスに接続するための SATA デバイス モード コントローラ ロジックをサポートしているという理由から、ザイリンクスの Virtex-4 FX FPGA を選択しました。また、FPGA に 64 ビット / 133MHz の PCI-X コントローラと XOR コントローラをインプリメントしました。PCI-X ベースの外部プロセッサは SATA ホストからのコマンドを解析し、ステータスを返すことができます。また、XOR コントローラは、PCI-X バスでソース メモリ データを直接読み込んで RAID 5 エンコーディングのために XOR データを計算できます。これらタスクは、すべてプロセッサが介入することなく行われます。FPGA のブロック ダイヤグラムについては図 2 をご覧ください。

## 3Gbps eSATA のインプリメンテーション

SATA コントローラには、トランスポート層、リンク層、物理層 (PHY) という 3 種類の層が定義されています。

### 1. トランスポート層

SATA のコマンド実行とデータ転送は、ATA レジスタやディスク データを含むフレーム情報構造 (FIS) をやり取りすることで行われます。トランスポート層は PCI-X バスから伝送する FIS を形成し、受信した FIS を分解して PCI-X バスに送信します。つまり、トランスポート層はリンク層と上位のアプリケーション層の中間に位置するインターフェイスであり、Accusys 社のデザインでは PCI-X バスです。

### 2. リンク層

リンク層はパケット フレーミング、8b/10b のエンコーディングとデコーディング、CRC コードの生成とチェックを行う層です。リンク層はまた、フロー制御を扱い、バースト転送を処理するため必要に応じてデータをバッファリングしプリティップをやり取りします。Virtex-4 FX デバイスのマルチギガビット トランシーバ

(MGT) には、8b/10b のエンコーダとデコーダ、および CDC-32 生成回路が組み込まれており、SATA のリンク層を構築するうえで非常に便利です。

### 3. 物理層

Virtex-4 FX FPGA の 6.5Gbps RocketIO™ トランシーバは、ホスト PHY からの受信データのデシリアル化と、リンク層からの発信 10b エンコード データのシリアル化を行う、SATA 物理層の基本的なビルディング ブロックを提供します。また、物理層は SATA ホストとデバイス間の接続を開始するための アウトオブバンド (OOB) 信号をサポートします。外部の 3Gbps SATA2 をサポートするには、SATA 物理層のインプリメンテーションに Gen2m 電気仕様が必要です。

割を果たします。これにより、大容量のデータ転送が大幅に高速化されます。

## XOR コントローラのインプリメンテーション

画像の編集や記録などのアプリケーションでは、低い I/O レイテンシーと高スループットという厳しい条件を満たすため、XOR を効率的に計算することが不可欠です。XOR コントローラは 256 のデータ ソースと 128 のチェーン コマンドを持ち、それぞれ 64KB のパリティ データを計算できます。FPGA に XOR コントローラをインプリメントすることで、プロセッサとメモリ バンド幅は、エントリあたり 64KB で、128 のチェーン コマンドを用いて 256 のソースに日常的に延々と XOR 計算を実行することから解放されるのです。

## 結論

3Gbps eSATA ハードウェア RAID は、高性能、低価格、使いやすさという利点を併せ持っています。eSATA ポートを搭載するコンピュータとエンベデッド システムが増えつつある今、eSATA RAID 製品は高性能、高信頼性を求めるユーザーにとって重要な外付け RAID ソリューションです。Accusys 社は、デジタル クロック マネージャや、デュアルポート ブロック RAM に代表される使いやすいビルディング ブロックなど、Virtex-4 FX FPGA の先進機能を活用することで、3Gbps eSATA RAID システムに対する主要コンポーネントを素早く効率的に開発できました。

ザイリンクスの Virtex-4 FX FPGA をベースとする製品の開発に成功したことで、Accusys 社は画像編集やワークグループ共有型ストレージなどのハイエンド アプリケーションから、DVR のバックアップや家庭用ストレージといったエントリ レベルのアプリケーションにいたるまで、幅広い eSATA RAID 製品を提供しています。RAID とストレージ技術の詳細は、Accusys 社の Web サイト、<http://www.accusys.com.tw> をご覧ください。

図 2 3Gbps eSATA RAID エンジンのブロック ダイヤグラム

# Implementing a Real-Time Beamformer on an FPGA Platform

# FPGA プラットフォームで リアルタイムな ビームフォーミングを実現

ザイリンクス System Generator for DSP

を使った QRD ベースの

ビームフォーミングの設計

Chris Dick

Xilinx Chief DSP Architect

Xilinx, Inc.

[chris.dick@xilinx.com](mailto:chris.dick@xilinx.com)

Fred Harris

Professor

San Diego State University

[fred.harris@sdsu.edu](mailto:fred.harris@sdsu.edu)

Miroslav Pajic

Engineer

Signum Concepts

[miroslav.pajic@signumconcepts.com](mailto:miroslav.pajic@signumconcepts.com)

Dragan Vuletic

Engineer

Signum Concepts

[dragan.vuletic@signumconcepts.com](mailto:dragan.vuletic@signumconcepts.com)

ほとんどの通信システムは、複数の処理要素を併せ持っています。たとえば、アプリケーションプログラム、マン／マシンインターフェイスの管理、上位ネットワーキングプロトコル スタックの処理は、汎用プロセッサにインプリメントするのがベストです。

しかし一般には、厳密なリアルタイム性が求められ、かつアルゴリズムが複雑なデータ処理については、FPGA などのハードウェアリソースが適しています。両者をつなぐインターフェイスは状況により異なります。FPGA は、プリプロセッサ、コプロセッサ、ポストプロセッサのどれか 1 つ、あるいは任意の組み合わせを選択できます。重要なのは、これら異種システムをスムーズに連携させることです。

本稿では、ソフトウェアを通して容易にコントロールできる、柔軟で最適化されたアダプティブ（適応型）ビームフォーミング エンジンの開発について説明します。DSP 集約型のタスクを FPGA で走らせ、またコマンドとコントロールを外部プロセッサで走行させます。ビームフォーミング エンジンは、斬新な構造を持つコンパクトな QR 分解（QRD ベースの回路）です。エンジンとホスト プロセッサ間のインターフェイスは、ザイリンクスの System Generator for DSP デザイン フローにおいて共有メモリを抽象化することでインプリメントされています。

## MVDR ビームフォーミング

アダプティブ ビームフォーミングは、アダ

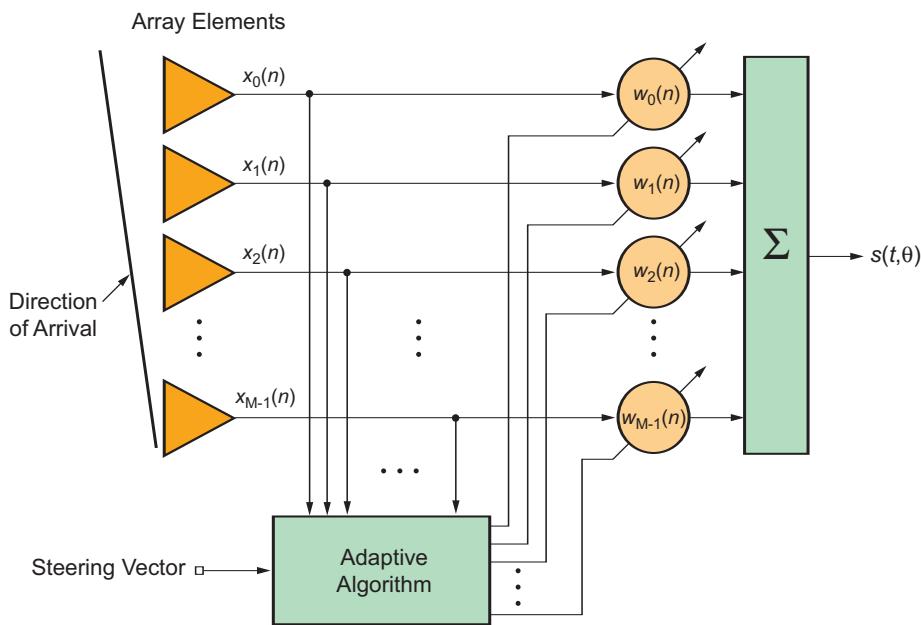

図 1 アダプティブ ビームフォーミングの構造

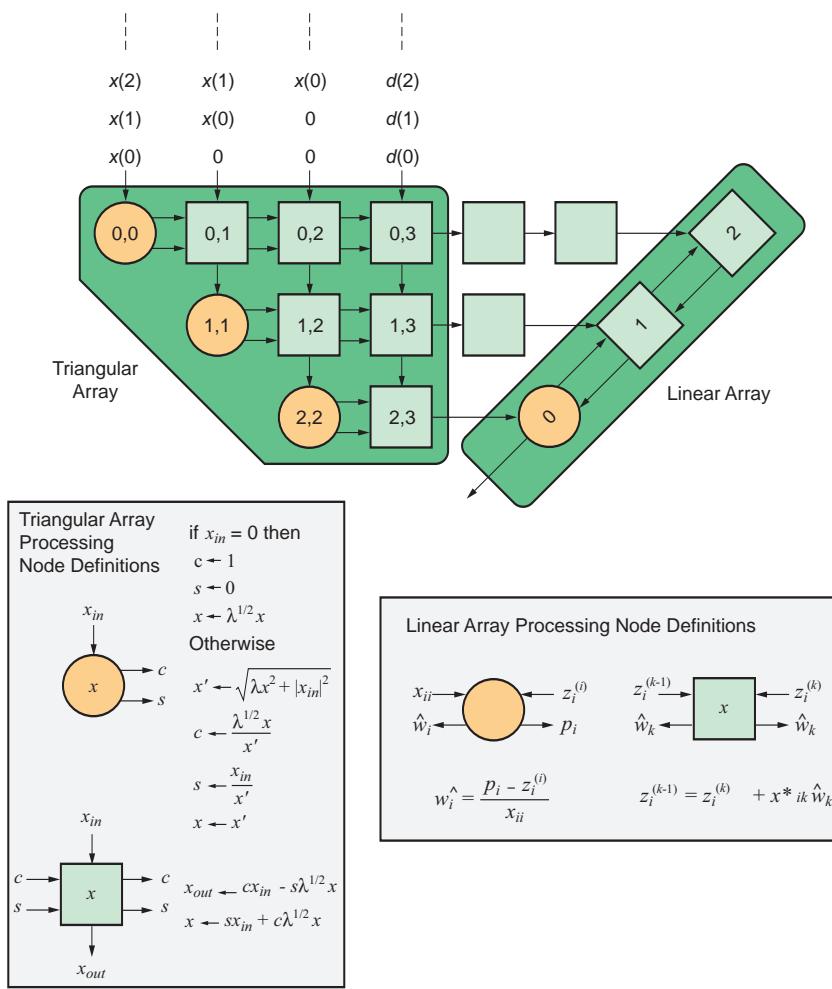

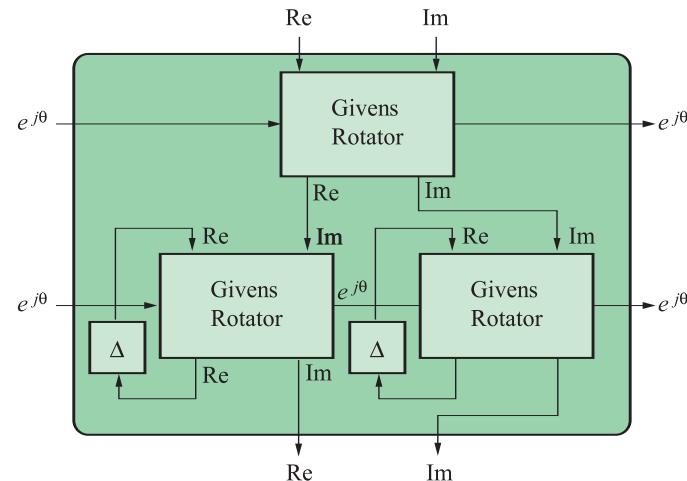

図 2  $3 \times 3$  アレイに対する QRD 行列転置のシストリック アレイ インプリメンテーション

アダプティブ フィルタを空間信号処理に応用したものです。等間隔のアレイ要素から収集した時系列の加重和を求めて、選択した到達方向からのシグナル コンポーネントを形成し、それ以外の到達方向からのシグナル コンポーネントを抑止します（図 1）。不要なシグナル コンポーネントの到達方向が未知、もしくは時間に伴って変化する場合、それらの方向に Null を向けるためフィルタ加重をアダプティブに調節する必要があります。この適応プロセスは、ステアリング ベクトルは信号方向にユニティ ゲインを持つという制約に従って実行されます。こうしたビームフォーミングの安定状態加重は、アレイ要素から MVDR (Minimum Variance Distortionless Response) を形成します。

数値の堅牢性と計算の複雑さという理由から、相関行列を直接転置しないで必要な加重ベクトルを計算するための一般的な方法は、QR分解に基づきます。ここで採用したのはこの手法です。手順の詳細は、「Adaptive Filter Theory」(Simon Haykin 著) をご覧ください。

#### QRD 行列転置プロセス

QRD プロセスは、複素入力データを実データに変換するユニタリ回転と、入力データ セットの選択要素を個別に無効化する角度／要素コンバインという 2 つの演算子のシーケンスにより形成されます。図 2 のシグナル フローは、QRD プロセスを最もコンパクトに表現したダイアグラムです。この図は、QRD 最小二乗法プロセッサでシストリック アレイを実現したものです。

アレイには、境界セル、内部セル、出力セルの 3 種類の処理セルがあります。境界セルは複素入力サンプルに「ベクトル化」演算を実行し、架空部分を無効化して内部セルによって使われる回転角を形成します。内部セルは入力値を境界セルから渡された角度だけギブンス (Givens) 回転することで、変換後のデータ行列の非上三角項目を無効化します。線形アレイ内の出力セルは、ビームフォーミングの加重を生成する後退代入を実行するため、上三角アレイの要素を処理します。

## QRD の FPGA インプリメンテーション

このインプリメンテーションの目標は、コンパクトな QRD FPGA インプリメンテーションを生成することです。このデザインは 1 個の境界セル、内部セル、後退代入セルからなります。この処理リソース セットには図 2 のストリック アレイがたたみ込まれています。2 つの角度を計算するために境界セルが必要です。最初の角度は次のようになります。

$$\Phi = \arctan(\Im(x_m)/\Re(x_m))$$

これは、境界セルの入力ポートに送られた複素入力サンプルを実値データに変換します。この境界セルに関連する同じ列内のすべての要素に架空コンポーネント  $x_m$  を強制的に 0 にする変換を適用する必要があり、この演算は内部セルにより実行されるタスクの 1 つです。

ここで 2 つの隣接する列の先頭にあるデータが実値になったため、次の式で 2 番目の角度を求めます。

$$\Theta = \arctan(x_m e^{j\phi}/x)$$

この角度は入力データ セットの項を順番に無効化するために使用され、最終的に右上三角行列  $R$  を生成します。境界セルに採用されている算式は、図 2 の等式をそのままインプリメントすることでハードウェア内に実現できます。これには、平方根と除算を実行するためハードウェアのサポートを必要とします。これらの回路は一般に FPGA ハードウェアにインプリメントされますが、私たちは必要な角度を計算するうえで、直接的なインプリメンテーションよりリソース コストを安く抑えられる代替方法を探しました。

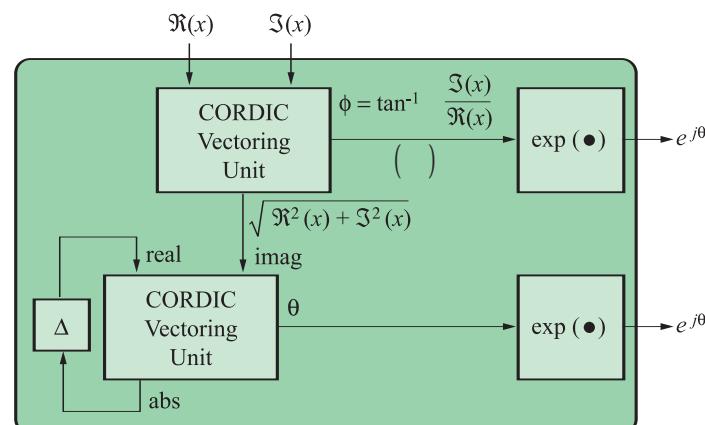

角度を計算するための比較的シンプルな方法として、座標回転デジタル コンピュータ (CORDIC) アルゴリズムのベクタリングモードが有名です。CORDIC アルゴリズムは、多彩な数学関数を計算できる反復的なプロセッサーです。CORDIC アルゴリズムに必要な要素演算は、加算、減算、ビット シフト、テーブル ルックアップです。これらの関数

はすべてザイリンクスの Virtex™ シリーズなどの FPGA アーキテクチャにより効率的にサポートされるため、アルゴリズムのベクタリングモードは QRD プロセッサの境界セルの基礎として良い候補となります。図 3 に示すとおり、境界セルには 2 つの CORDIC エンジンが使われています。1 つは  $\Phi$  を計算するため、もう 1 つは  $\Theta$  を計算するためのエンジンです。

CORDIC アルゴリズムは反復的性質を持ち、反復のたびに角度の推計を約 1 ビット精度ずつ改善していきます。N 回反復する CORDIC プロセスを採用したプロセスでは、N クロック サイクルごとに新しい出力が生成され、また N クロック サイクルごとに新しいオペランド セットが用意されます。境

界セルのスループットを高めるため、ここでは CORDIC に完全にパラレル、もしくはアンロールされたアーキテクチャを採用しています (図では示されていません)。回路の初期始動時のレイテンシが吸収された後、セルの開始および完了レートはクロック サイクルあたり 1 つの新しい入力/出力です。

列  $m$  の内部セル (図 4) に入る各データ要素  $x_m$  は、 $m^{\text{th}}$  列に対して境界セルによって計算された角度  $\Phi$  回転する必要があります。

$$\begin{aligned} \Re(v) &= \cos(\phi) & -\sin(\theta) & \Re(x_m) \\ \Im(v) &= \cos(\phi) & \sin(\theta) & \Im(x_m) \end{aligned}$$

QRD プロセッサにおける回転タスクに

図 3 2 ベクトル モード CORDIC 処理エンジンをベースとする境界セルのアーキテクチャ

図 4 3 つの MAC ベース ギブンス回転エンジンを採用したストリック アレイの内部セル アーキテクチャ

一般に使われてきたオプションとして、CORDIC アルゴリズムの回転モードがあります。また、他の手法として積和 (MAC) 関数ユニットを使って回転を明示的にインプリメンテーションする方法もありますが、今回のインプリメンテーションではこのアプローチを採用しています。このデザインに対するターゲット FPGA テクノロジは Virtex-4 FPGA です。このデバイスには、DSP48 スライスというエンベデッド MAC ユニットの膨大なアレイがあります。

DSP48 スライスは、特定のクロック サイクル中にタイルによって計算される算術演算を変更できる、クロック サイクルごとでアップデート可能な多数の opcode をサポートします。先ほどの等式に示した 4 つの乗算は一対の DSP48 スライスにたたみ込まれ、各 DSP48 スライスは 2 つの出力項

$\Re(v)$  と  $\Im(v)$  のうち 1 つを計算します。2 つの出力項を計算するには 2 つのクロック サイクルが必要です。各 DSP には各クロック ピリオド用に固有の opcode が与えられています。 $\Re(v)$  項を計算する場合を考えてみましょう。最初のクロック ピリオド中、 $\cos(\Phi)$   $\Re(x_m)$  の積が計算され、DSP48 の積を意味する p レジスタに格納されます。

2 番目のクロック サイクル中には  $\sin(\Phi)$   $\Im(x_m)$  が求められ、最終的な出力項を生成するため p レジスタの値から減算されます。 $\Im(v)$  を計算する際にもこれと似た一連の計算が行われます。内部セルに対して CORDIC ベースのアプローチでなく DSP 48 エンベデッド ブロックを使うことで、計算のこの段階のレイテンシを低減すると共に、インプリメンテーションに必要な FPGA ロジック ファブリック (ルックアップ

テーブル [LUT] とレジスタ) の量を最小限に抑えられます。表 1 に、QRD インプリメンテーションにおける主な関数ユニットに対するエリアの内訳と、デザインの総エリアを示します。

内部セルにより必要とされる  $\cos(\Phi)$ 、 $\sin(\Phi)$ 、 $\cos(\Theta)$ 、 $\sin(\Theta)$  の各項は、境界セル内のベクタリング ユニットによって計算される角度  $\Phi$  と  $\Theta$  をそれぞれの正弦および余弦にマッピングする、単純な LUT を用いて計算されます。LUT そのものを單一ブロック RAM で実現しつつ、角度から振幅へのマッピング精度を高めるため、LUT の出力サンプルに線形内挿が適用されます。

QRD プロセッサに対する入力アレイの行と列のサイズは、FPGA コントロール プレーンの一部であるコントロール レジスタに新たなサイズを書き込むことでランタイムに動的に調節できます。

表 2 に、入力データ セットの複数のコンフィギュレーションに対するタイミング情報を示します。

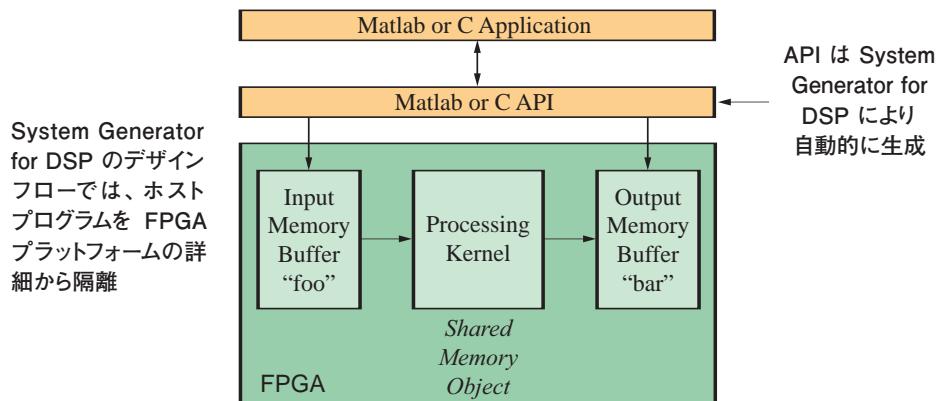

## デザイン フロー

私たちの QRD インプリメンテーションは、DSP モデルをベースとするデザインフローにザイリンクスの System Generator for DSP を使用しています。System Generator for DSP は、FPGA 信号処理のインプリメンテーションを開発するための自然な開発環境を提供することに加え、FPGA エレメントだけでなくプロセッサから成る異種アプリケーションの開発をサポートする豊富な機能を備えています。プロセッサは、エンベデッド PowerPC™ 405 ハード IP ブロック、MicroBlaze™ ソフトプロセッサ コア、あるいは FPGA の外部プロセッサでもいずれも可能です。

このプロジェクト用に開発したビームフォーミングでは、ホスト PC と FPGA プラットフォーム間をパーティションで区切りました。このインプリメンテーションでは、PC で走っているホスト アプリケーションは単なるビームフォーミング検証プロセス (テスト ベンチ) の 1 つの要素ではなく、手元のタスクに応じて任意かつ複雑になること

表 1 たたみ込まれた QRD と後退代入アレイに対する FPGA リソースの利用

| 関数ユニット | IUT   | FF    | DSP48 スライス | ブロック RAM | スライス  |

|--------|-------|-------|------------|----------|-------|

| 境界セル   | 2,145 | 2,057 | 3          | 1        | 1,266 |

| 内部セル   | 216   | 329   | 6          | 0        | 176   |

| 後退代入   | 2,862 | 3,286 | 4          | 1        | 1,932 |

| QRD 合計 | 5,411 | 5,916 | 13         | 6        | 3,530 |

表 2 M X N 行列に対するFPGA QRD インプリメンテーションの三角化と後退代入フェーズの実行時間

| M  | N  | 三角化のサイクル | 後退代入のサイクル | 合計サイクル | 250MHz クロックでの実行時間 |

|----|----|----------|-----------|--------|-------------------|

| 3  | 3  | 792      | 147       | 939    | 3.76              |

| 8  | 3  | 2,112    | 147       | 2,259  | 9.04              |

| 5  | 5  | 2,540    | 255       | 2,795  | 11.18             |

| 9  | 5  | 4,572    | 255       | 4,827  | 19.31             |

| 7  | 7  | 5,656    | 371       | 6,027  | 24.11             |

| 10 | 7  | 8,080    | 371       | 8,451  | 33.80             |

| 9  | 9  | 10,476   | 495       | 10,971 | 43.88             |

| 11 | 9  | 12,804   | 495       | 13,299 | 53.20             |

| 10 | 10 | 13,630   | 560       | 14,190 | 56.76             |

があります。

このビームフォーミング ホスト アプリケーションは、ビームフォーミング ネットワークに対するセンサー アレイをシミュレートする MATLAB スクリプト (m-code) です。このスクリプトはダイナミック ターゲットをシミュレートし、移動するターゲットに対して遠方場放射パターンのサンプルを生成します。MATLAB に各センサーにおける電気場のサンプルが生成され、FPGA QRD プロセッサに転送されます。ビームフォーミング加重ベクトルの新たな推計が算出され、追加処理のために MATLAB 環境に返されます。

この場合、追加処理にはアップデートされた複素数値の加重ベクトルに対する指向性放射パターンをプロットすることが含まれます。ホスト アプリケーションが MATLAB 環境に関連している必要はなく、たとえば C 言語で書かれたプログラムであってもかまいません。

ビームフォーミング アプリケーションの興味深い要素として、この場合は PC 上で動作しているホスト アプリケーションと、FPGA プラットフォームで実行している QRD プロセス間のインターフェイス管理があります。System Generator for DSP は、プロセッサ/FPGA インターフェイスの事実上あらゆる詳細を抽象化する一連の共有メモリ ライブライオブジェクト (ROM, RAM, FIFO) を提供し、ホストソフトウェアと FPGA ハードウェアをそれぞれ別々に構築することができます (図 5)。

ビームフォーミングの新規アップデートは次の 3 ステップで行われます。

1. MATLAB ホスト アプリケーションにより生成される各アンテナ素子からの新規入力サンプルが、本来の場所である FPGA 上の QRD エンジンに転送されます。

2. QRD プロセスがトリガされます。

3. FPGA からホストに新しい加重ベクトルが返されます。

共有メモリ ライブライモジュールとそれに関連するアプリケーション プログラマイインターフェイスは、FPGA とホスト PC 間の

図 5 System Generator for DSP の共有メモリ ライブライ要素によるハードウェアとソフトウェアの抽象化 - ホスト アプリケーションは、シンプルな名前/空間参照を使い、FPGA ストレージ要素とのトランザクションを実行 (この場合は "foo" および "bar" という名前のメモリへ)