# Xcell journal

SOLUTIONS FOR A PROGRAMMABLE WORLD

## エンベデッド プロセッサ ソリューション 特集号

### COVER

民生用電子機器と車載用電子

機器の革新を考える

Virtex-5 FXT デバイスで

エンベデッド処理に革新を

もたらす

### INSIDE

高速ブロードキャスト ビデオ

コネクティビティ

ソリューション

マルチプロセッサ SoC の

デザイン

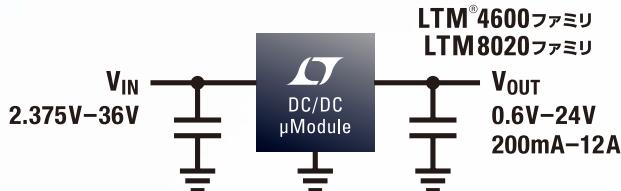

### 36V高電圧ファミリ

#### LTM8020

$I_{OUT}$  200mA

$V_{IN}$  4~36V

$V_{OUT}$  1.25~5V

短絡保護機能

6.25×6.25×2.32mm

#### LTM8021

$I_{OUT}$  500mA

$V_{IN}$  3.6~36V

$V_{OUT}$  0.8~5V

短絡保護機能

6.25×11.25×2.8mm

#### LTM8022

$I_{OUT}$  1A

$V_{IN}$  3.6~36V

$V_{OUT}$  0.8~10V

短絡保護機能

9×11.25×2.8mm

#### LTM8023

$I_{OUT}$  2A

$V_{IN}$  3.6~36V

$V_{OUT}$  0.8~10V

短絡保護機能

9×11.25×2.8mm

### 低電圧ファミリ

#### LTM4604

$I_{OUT}$  4A

$V_{IN}$  2.375~5.5V

$V_{OUT}$  0.8~5V

トランク機能

9×15×2.3mm

#### LTM4608

$I_{OUT}$  8A

$V_{IN}$  2.375~5.5V

$V_{OUT}$  0.6~5V

PLL機能

トランク機能

マージン機能

9×15×2.8mm

### 昇降圧型ファミリ

#### LTM4605

$I_{OUT}$  5A (12A 降圧モード時)

$V_{IN}$  4.5~20V

$V_{OUT}$  0.8~16V

PLL機能

パワーグッド出力

15×15×2.8mm

#### LTM4607

$I_{OUT}$  5A (10A 降圧モード時)

$V_{IN}$  4.5~36V

$V_{OUT}$  0.8~24V

PLL機能

パワーグッド出力

15×15×2.8mm

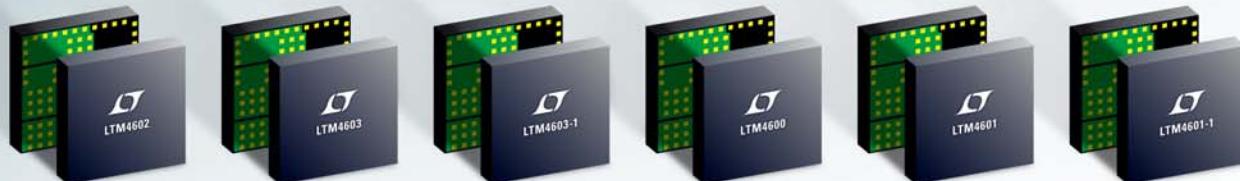

#### LTM4602

$I_{OUT}$  6A

$V_{IN}$  4.5~28V

$V_{OUT}$  0.6~5V

ピーク電流:8A

15×15×2.8mm

#### LTM4603

$I_{OUT}$  6A

$V_{IN}$  4.5~28V

$V_{OUT}$  0.6~5V

PLL機能

トランク機能

マージン機能

リモートセンス機能

15×15×2.8mm

#### LTM4603-1

$I_{OUT}$  6A

$V_{IN}$  4.5~20V

$V_{OUT}$  0.6~5V

PLL機能

トランク機能

マージン機能

15×15×2.8mm

#### LTM4600

$I_{OUT}$  10A

$V_{IN}$  4.5~28V

$V_{OUT}$  0.6~5V

ピーク電流:14A

15×15×2.8mm

#### LTM4601

$I_{OUT}$  12A

$V_{IN}$  4.5~28V

$V_{OUT}$  0.6~5V

PLL機能

トランク機能

マージン機能

リモートセンス機能

15×15×2.8mm

#### LTM4601-1

$I_{OUT}$  12A

$V_{IN}$  4.5~20V

$V_{OUT}$  0.6~5V

PLL機能

トランク機能

マージン機能

15×15×2.8mm

回路の実装面積 50% 削減

電源の設計時間 大幅短縮

しかも高信頼性 ICと同等

# 実現したのは、μModule™

インスタント 200mA～12A 電源 [マイクロ・モジュール]

高性能アナログICメーカーならではのノウハウと共に、DC/DCコントローラも、MOSFETも、インダクタさえも、小型パッケージに収容した簡単・すぐに使えるインスタント電源「μModule」。発売以来、電源回路の実装面積と設計工数を大幅に削減するメリットが評価され、採用実績が急増しています。そして、「さらに高電圧の入力にも対応したモジュールを」という要求に応えて、今度は3.6V～36Vワイドレンジ入力のLTM8020ファミリもリリース。

ラインナップも、ますます充実しています。

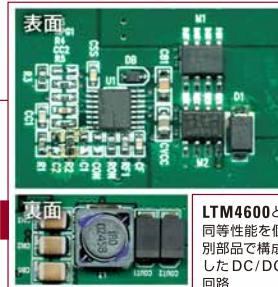

## 特長① 実装面積半減

- 個別部品で構成した同等性能のDC/DC回路に比べ、実装面積を約50%削減 [LTM4600]

- RoHS準拠の100%表面実装、軽量LGAパッケージ

0.25g [LTM8020]

1.7g [LTM4600]

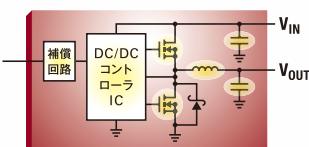

## 特長② 簡単、すぐに使える、しかも高性能

- 設計不要

- 外付けは入出力コンデンサと抵抗1個

- インダクタ、パワーMOSFET、DC/DCコントローラ、補償回路を内蔵

- パワーMOSFETも自社開発するなど、各内蔵部品は最適化され、卓越した高性能を実現

## 特長③ ヒートシンク不要

- わずか15°C/Wの優れた熱特性

- 複数のμModuleを並列接続し、最大48A出力

μModuleの

技術資料へアクセス!

[www.linear-news.jp/LTM](http://www.linear-news.jp/LTM)

評価ボード

お問い合わせは、

下記販売代理店まで

リニアテクノロジー国内ニュースサイト

[www.linear-news.jp](http://www.linear-news.jp)

LN、LT、LTC、LTMは、リニアテクノロジー社の登録商標です。μModule、LINEAR EXPRESSは、リニアテクノロジー社の商標です。他の商標はそれぞれが所有するものです。

オンラインストア リニアエクスプレス

**LINEAR EXPRESS™**

☎ 0120-7291-22

東京エレクトロンデバイス株式会社

本社 TEL 045-474-5114

大阪 06-6399-1511 名古屋 052-562-0825

東京 03-3251-0083 北関東 048-600-3880

水戸 029-227-6552 立川 042-548-0255

横浜 045-474-7023 松本 0263-36-8112

福岡 092-474-4121 仙台 022-212-2746

株式会社 トーメン エレクトロニクス

本社 TEL 03-5462-9615

大阪 06-6447-9644 名古屋 052-582-1591

福岡 092-713-7779 宇都宮 028-625-8331

松本 0263-34-6131 北関東 048-521-9011

仙台 022-221-8061 浜松 053-452-8147

立川 042-548-9871

東京電子販売株式会社

本社 TEL 03-5350-6711

株式会社 三共社

本社 TEL 03-5298-6201

伊藤電機株式会社

本社 TEL 052-935-1746

株式会社 信和電業社

本社 TEL 06-6943-5131

|                   |                                                                                                  |

|-------------------|--------------------------------------------------------------------------------------------------|

| 発行人               | Forrest Couch<br>forrest.couch@xilinx.com                                                        |

| 編集                | Charmaine Cooper Hussain                                                                         |

| アートディレクター         | Scott Blair                                                                                      |

| デザイン/制作           | Teie, Gelwicks & Associates                                                                      |

| テクニカル<br>コーディネーター | Kevin Kitagawa<br>Kevin Tanaka<br>Tamara Snowden<br>Silvia Gianelli<br>Larry Caputo<br>Jay Gould |

| 日本語版統括            | 澤田 修<br>osamu.sawada@xilinx.com                                                                  |

| 制作進行              | 竹腰 美優紀<br>miyuki.takegoshi@xilinx.com                                                            |

| 制作・広告・印刷          | 有限会社エイ・シー・シー                                                                                     |

Xcell Journal 日本語版 63・64 合併号

2008 年 8 月 12 日発行

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400ザイリンクス株式会社

〒141-0032

東京都品川区大崎 1-2-2

アートヴィレッジ大崎セントラルタワー 4F

© 2008 Xilinx, Inc. All Right Reserved.

XILINX や、Xcell のロゴ、その他本書に記載の商標は、米国およびその他各国の Xilinx 社の登録商標です。PowerPC は、米国またはその他の国における IBM 社の商標です。ほかすべての名前は、各社の登録商標または商標です。

本書は、米国 Xilinx, Inc. が発行する英文季刊誌を、ザイリンクス株式会社が日本語に翻訳して発行したものです。

米国 Xilinx, Inc. および Xilinx, Inc. 株式会社は、本書に記載されたデータの使用に起因する第三者の特許権、他の権利、損害における一切の責任を負いません。

本書の一部または全部の無断転載、複写は、著作権法に基づき固く禁じます。

Printed in Japan

# 統合システム プラットフォーム： エンベデッド アプリケーションにおける FPGA 革新の第二の波

FPGA は、デザインをテストするプロトタイプとしての役割を長い間歩んできました。現在では、その役割のみならず、日々我々の生活を改善する多くの革新的製品に採用され、欠くことのできないデバイスとなっています。FPGA は市場からのさまざまな厳しい要求に応え、何よりもその柔軟性において高い評価を受けてきました。デバイス本来が持つプログラマビリティ性は、製品開発者にとって保険証書のようなものであり、迅速かつ効率的に市場のニーズを取り込み、展開の早い市場において常に製品を最新の状態に維持できます。

Xcell Journal に掲載している多くの記事が示すように、FPGA はもはや単一機能のデバイスではありません。このプログラマブル デバイスは、システム オン チップ (SoC) とエンベデッド システム デザインなどの高集積デバイス分野で理想的なプラットフォームとして注目を集めています。

ザイリンクスは、2008 年 4 月に究極のシステム統合プラットフォームとして Virtex™-5 FXT FPGA を発表しました。Virtex-5 FXT デバイスは 65nm FPGA である Virtex-5 ファミリの第 4 世代のプラットフォームとして、非常に高性能なエンベデッド処理やデジタル信号処理、コネクティビティの各機能をその高い柔軟性と組み合わせてワンチップに集積したことにより、トータル システムコストや消費電力の削減、そしてボードの実装面積の低減を実現します。

## 本号について

Xcell Journal 日本語版 63・64 合併号では、Virtex-5 FXT プラットフォームがエンベデッド開発者に与える重要性を、カバー記事の 1 つとして紹介しています。同記事では、エンベデッド PowerPC® 440 プロセッサ ブロックや高速 RocketIO™ シリアル トランシーバ、および XtremeDSP™ 処理機能を備えた業界初の FPGA を解説します。このデバイスは最適化されたシステム統合プラットフォームを提供し、広範なアプリケーションにおける音声やビデオ、データ送信、そしてバンド幅要件を満たしています。適用可能なアプリケーションとしては、有線／無線通信、オーディオ／ビデオのブロードキャスト機器、航空宇宙、産業生産システムなど、多くが挙げられます。本号では、宇宙空間から地上における科学的革新やオートモーティブ革新までの幅広い各種 FPGA ベースのエンベデッド システム アプリケーションの「舞台裏」を紹介します。

また、いかにザイリンクスのエンベデッド処理ソリューションに改善が施され、直感的なハードウェアおよびソフトウェア ツールによって使い勝手が大幅に簡易化されているかを解説します。ザイリンクスのエンベデッド ソリューションの利点を最大限に引き出す上で重要な役割を果たすサードパーティのエンベデッド技術およびサービス プロバイダが提供する最新ソリューションも紹介します。

加えて、昨今著しい革新を見せ「コンピュータ トランスポーテーション」化しているオートモーティブ市場に向けてザイリンクスが提供するソリューション、XA (Xilinx Automotive) 製品ファミリが、先端エレクトロニクス モジュールやシステムにいかに最適なソリューションを提供するかを紹介します。

さらにザイリンクスは、低コストの量産アプリケーション市場において急速な変化を続けるコンシューマ製品用に応えるソリューションとして、アプリケーション セグメントに最適化した PLD 製品を提供します。コンシューマ製品のなかでもハンドセット向けに提供しているソリューションを紹介します。

Forrest Couch

発行人

澤田 修

日本語版統括

## VIEWPOINTS

ザイリンクス新社長兼 CEO 就任 ..... 4

## FEATURES

### Cover

民生用電子機器と車載用電子機器の革新を考える ..... 6

Virtex-5 FXT デバイスでエンベデッド処理に革新をもたらす ..... 8

### Portable Handsets

CPLD でプロセッサの消費電力を低減する ..... 14

CPLD で複数の SD デバイスをサポート ..... 19

### Audio/Video

高速ブロードキャスト ビデオ コネクティビティ ソリューション ..... 22

### Embedded Applications

宇宙船画像処理の高性能化を実現する FPGA コプロセッサの開発 ..... 26

### System Development

マルチプロセッサ SoC のデザイン ..... 32

ザイリンクス XtremeDSP ビデオ スタータ キット により

FPGA 上でのビデオ開発を加速 ..... 35

### Platforms, Processors, & Tools

MicroBlaze v7 が MMU (メモリ管理ユニット) を装備 ..... 40

FPGA エンベデッド プロセッサによるデバッグ システム ..... 46

### INFORMATION

ザイリンクス トレーニング スケジュール ..... 38

ザイリンクス ウェブ セミナー ..... 51

ザイリンクス イベント カレンダー ..... 52

### 広告索引

リニアテクノロジー株式会社 ..... 表2-1

有限会社ヒューマンデータ ..... 5

アルデック・ジャパン株式会社 ..... 31

株式会社ミッシュインターナショナル ..... 39

株式会社コンピューテックス ..... 50

日本イヴ株式会社 ..... 表3

## TABLE OF CONTENTS, 63・64 合併号

### COVER STORY

### 民生用電子機器と車載用電子機器の革新を考える

ザイリンクスは民生用電子機器や車載用電子機器向けに、温度や品質、信頼性に対する各要件を満たしたシリコン、開発ツール、IPコア、ミドルウェア、およびデザインサービスなどをトータルに提供

6

### COVER STORY

### Virtex-5 FXT デバイスでエンベデッド処理に革新をもたらす

内蔵 PowerPC 440 プロセッサ ブロックを利用して性能とスループットを最大化

8

### AUDIO/VIDEO

### 高速ブロードキャスト ビデオ コネクティビティ ソリューション

ザイリンクス Spartan-3E と Spartan-3A FPGA、NS 社の Smart SERDES、およびザイリンクス プロトコルスタックにより、SD や HD、3G-SDI 向けマルチレート ブロードキャストの課題に費用対効果が高く柔軟性の高いアプローチを提供

22

### SYSTEM DEVELOPMENT

### マルチプロセッサ SoC のデザイン

ザイリンクスのEDKツールとIPコアで、複数プロセッサのSoCをデザインすることにより、アプリケーションの縮小が可能

32

## Xilinx Welcomes New President & CEO

# ザイリンクス新社長兼 CEO 就任

Wim Roelandts、業界のベテラン Moshe Gavrielov にトーチを託す

2008 年 1 月 7 日、ザイリンクスは新社長兼 CEO に Moshe Gavrielov を任命しました。彼はこの業界で最も尊敬されている CEO の一人である Wim Roelandts の重責を引き継ぐこと

になります。Roelandts は取締役会長にとどまり、Gavrielov は Xilinx® の 24 年の歴史で第 3 代目の CEO となります。本号の View from the Top では、Moshe がザイリンクスに対する彼の構想と、今後この会社をどのように牽引していくかを語ります。

世界で最も尊敬されている半導体企業の一社の牽引を引き受けることは、非常に名誉あることで胸の高まりを覚えます。ザイリンクスの非常にエキサイティングな時期に経営に参加できたと感じています。我々は、ザイリンクス技術の利点をさまざまな企業や幅広いアプリケーションに広める大いなる機会を手にしています。

FPGA は広範囲の設計者にますます大きな影響をおぼしつつあります。設計者にとって将来の変化に備える最良の方法がオプションで武装することだということは、よく知られた事実です。FPGA は常に、そのハードウェアのプログラマビリティ性により、さまざまなオプションを提供してきました。ザイリンクスは、Time-to-Market の短縮を提供する究極のソリューション プロバイダです。それは、シリコンと柔軟性に限ったことではありません。これは IP コアに関しても同様です。今日のザイリンクスは、私がかつて直面したケースによく似たある移行過程にあります。それは、単な

るゲートのサプライヤからゲートに取り込む IP コアのサプライヤおよびサポートへ変わることです。しかし、フィールドで IP コア全体をサポートするのは、簡単なことはありません。

ザイリンクスがユーザーにより良いサービスを提供して売上を伸ばし、市場シェアを拡大するには、3 つの機会があると考えています。まず、弊社の基礎を成すシリコン機能の拡張ペースを維持することです。次に、拡大する広範なアプリケーションに対して IP コア製品の拡充を続けて行くことです。そして最後に、開発ツールに投資を続け、既存および新しいユーザーのますます拡大する特別なコミュニティのニーズに応えることです。

ザイリンクスは、完璧なソリューションサプライヤになるためのステージに既に立っています。あとは、そこへたどり着くための方法を模索すればよいのです。世界中のユーザーから学び、彼らの問題点を我々の問題として認識した上で、親切そして適切な対応をとることが重要です。そして、彼らの問題点が解消できるソリューションを提供していく必要があります。

### DSP とエンベデッドについて

私がザイリンクスに入社したとき、ザイリンクスはすでに DSP やエンベデッド市場に目を向けていました。三年前、ザイリンクスは新しい事業部門の創設を発表しました。それは、以前 ASIC や ASSP がほぼ

支配していた数十億ドルに上る AVB (オーディオ、ビデオ、ブロードキャスト) や、産業機器、航空宇宙／防衛、医療、自動車、民生電子機器に代表されるパーティカル マーケット向けに、ザイリンクス FPGA を参入させ拡大するのが目的でした。

FPGA は、高性能 DSP およびエンベデッド アプリケーション向けに、市場価値の非常に高い提案や大きな技術的優位性を提供しています。ザイリンクスにとって、DSP およびエンベデッド プロセッサはまったく新しい市場機会でした。設計者が重要なファンクションを 1 個の FPGA に統合すると、トータル システム コストや消費電力の低減を実現し、さらにコンポーネント数を減らすことで基板スペースを削減することも可能になります。これは簡単なことではありません。ソリューション全体を提供するプロバイダになるべきだという意見に話を戻しますが、すべての設計者、特に DSP やエンベデッド分野の設計者は、単に ASIC や ASSP から FPGA へ移行しただけに止まるのではなく、定評を得るまでのレベルを望んでいるのです。

ザイリンクスは、IP コアやソフトウェアツール、デザイン手法を含むすべての必要なツールを提供していかなければなりません。それによって、設計者は FPGA の高性能と柔軟性の高い機能を享受できるのです。可能な限りの高機能をごく簡単な手法で提供しなければなりません。私は、その目的を達成することを個人的にも非常に楽しみにしています。•

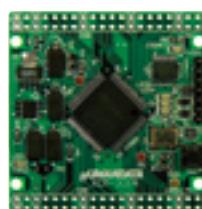

# FPGA/CPLD 評価ボード

全100種類以上をラインナップ

: RoHS指令対応品

<原寸大>

Virtex-5 LXT

FBGA665 ブレッドボード

**XCM-107シリーズ**

XC5VLX30T-1FFG665Cまたは

XC5VLX50T-1FFG665Cを搭載。

ハーフ

カードサイズ

RoHS指令

対応品

開発中

ハーフカードサイズ、セミカードサイズの

小型モジュールも充実。

ボードサンプル進呈中

(数量限定)

- FPGAの動作に必要な最低限の機能を搭載。単一電源ですぐに活用できます

- XCMシリーズはそれぞれ外形やコネクタ位置が同一で置き換えが可能です

- 回路図、マニュアルは購入前でも自由に参照できます

- 豊富な納入実績で安心してお使いいただけます

- 基本的に即納体制で最短翌日からご活用いただけます

- スピードグレード変更などのカスタマイズもご相談ください

Spartan-3 ブレッドボード

**XCM-301**

XC3S200-4VQ100Cを搭載。

セミ

カードサイズ

¥14,000 (税込14,700)

Spartan-3E

SP3E 208pin ブレッドボード

**XCM-302**

XC3S250E-4PQG208Cまたは

XC3S500E-4PQG208C搭載。

セミ

カードサイズ

¥29,000 (税込30,450) ~

Spartan-3AN

SP3AN 144pin ブレッドボード

**XCM-303**

XC3S50AN-4TQG144Cを搭載。

セミ

カードサイズ

¥19,000 (税込19,950)

Spartan-3 ブレッドボード

**XCM-101**

XC3S200-4PQ208Cまたは

XC3S400-4PQ208Cを搭載。

ハーフ

カードサイズ

¥21,000 (税込22,050) ~

Spartan-3 ブレッドボード

**XCM-102**

XC3S1000-4FG456Cまたは

XC3S1500-4FG456Cまたは

XC3S2000-4FG456Cを搭載。

ハーフ

カードサイズ

¥51,000 (税込53,550) ~

Virtex-II Pro ブレッドボード

**XCM-104**

PowerPCハードプロセッサ内蔵

FPGA XC2VP7-5FG456C搭載。

ハーフ

カードサイズ

¥59,500 (税込62,475)

Virtex-4 FBGA668 ブレッドボード

**XCM-105**

XC4VLXの668pinBGA

チップ搭載。

ハーフ

カードサイズ

¥91,000 (税込95,550) ~

Spartan-3 ブレッドボード

**XCM-001**

XC3S200-4PQ208Cまたは

XC3S400-4PQ208Cを搭載。

¥19,000 (税込19,950) ~

XC9500CPLD ブレッドボード

**XCM-002**

XC95144-15PQ160Cまたは

XC95200-15PQ160Cを搭載。

¥14,000 (税込14,700) ~

Virtex-II Pro ブレッドボード

**XCM-003**

Virtex-II Proを搭載した

ブレッドボード。

¥65,000 (税込68,250)

Spartan-II ブレッドボード

**XCM-004**

Spartan-II (208pin)を

搭載したブレッドボード。

¥23,000 (税込24,150) ~

Spartan-3 ブレッドボード

**XCM-005**

XC3S1000-4FG456Cまたは

XC3S1500-4FG456Cまたは

XC3S2000-4FG456Cを搭載。

¥64,000 (税込67,200) ~

CoolRunner

XPLA3 ブレッドボード

**XCM-007**

XCR3128XL-10TQ144Cまたは

XCR3256XL-12TQ144Cを搭載。

¥12,600 (税込13,230) ~

Spartan-3 ブレッドボード

**XCM-008**

XC3S50-4TQ144Cまたは

XC3S200-4TQ144Cまたは

XC3S400-4TQ144Cを搭載。

¥14,000 (税込14,700) ~

CoolRunner-II

XC2C256 ブレッドボード

**XCM-012**

XC2C256-7PQG208Cを

搭載したブレッドボード。

¥15,000 (税込15,750)

Spartan-3E FBGA676

ブレッドボード

**XCM-010**

XC3S1600E-4FGG320C

を搭載したブレッドボード。

¥59,000 (税込61,950)

Virtex-5 FBGA676

ブレッドボード

**XCM-011シリーズ**

XC5VLX50-1FFG676Cまたは

XC5VLX30-1FFG676Cを搭載。

¥120,000 (税込126,000) ~

XILINX対応FPGAトレーナ

**EDX-001**

USBケーブルのみで動作、コンフィ

グレーション可能な

学習用ボード。

大好評

¥14,800 (税込15,540)

XILINX対応FPGAトレーナ

**EDX-002**

USBケーブルのみで動作、コンフィ

グレーション可能な

学習用ボード。

¥14,800 (税込15,540)

XILINX対応FPGAトレーナ

**EDX-004**

USBインターフェースをもつPC

に接続し、コンフィグレーションでき

る学習用ボード。

¥14,800 (税込15,540)

XILINX対応FPGAトレーナ

**EDX-005**

USBインターフェースをもつPCに

接続し、コンフィグレーションでき

る教育用ボード。

¥39,900 (税込41,895)

そのほか各種評価ボードの情報は、<http://hdl.co.jp>へ

## 教育用ボード

FPGAトレーナ

**EDX-001**

USBケーブルでコンフィグレ

ーション可能な学習専用ボード。

プラスチックケース、ACアダプタ対

応。

¥48,000 (税込50,400)

XILINX対応FPGAトレーナ

**EDX-002**

USBケーブルのみで動作、コンフィ

グレーション可能な

学習用ボード。

¥14,800 (税込15,540)

XILINX対応FPGAトレーナ

**EDX-004**

USBインターフェースをもつPC

に接続し、コンフィグレーションでき

る学習用ボード。

¥14,800 (税込15,540)

XILINX対応FPGAトレーナ

**EDX-005**

USBインターフェースをもつPCに

接続し、コンフィグレーションでき

る教育用ボード。

¥39,900

(税込41,895)

# At the Heart of Consumer and Automotive Innovation

## 民生用電子機器と車載用電子機器の革新を考える

ザイリンクスは民生用電子機器や車載用電子機器向けに、温度や品質、信頼性に対する各要件を満たしたシリコン、開発ツール、IPコア、ミドルウェア、およびデザインサービスなどをトータルに提供

Kevin M. Kitagawa

Director, Worldwide Marketing, High-Volume Products

Xilinx, Inc.

[kevin.kitagawa@xilinx.com](mailto:kevin.kitagawa@xilinx.com)

世の中がますますデジタルに移行するにつれ、利用者はいつでもどんなところでも、オーディオやビデオ、データなどのコンテンツを楽しみたいと思っています。より良い品質でしかも廉価な有線・無線のインフラが利用可能となった今日、このインフラを利用して消費者がより楽しめるコンテンツを配信することが可能になり、機器メーカーはその楽しみを高める革新的な機能を提案できるよう、常に新しい挑戦に取り組んでいます。

たとえば、デジタル音楽プレイヤーやHDTV デジタル ディスプレイ、車載用電子機器、携帯電話、ブロードバンド インターネット アクセスなどは、家や自動車の中、あるいは車で移動中にもコンテンツにアクセスして楽しむことができます。多くの場合、どんな革新的機能が市場に受け入れられるかを予測して製品決定を行うのは、非常にリスクが高いため、機器メーカーは直接利用者のフィードバックを早い時期から製品開発に取り込み、成功を確実なものにしようとします。これには迅速な製品開発が必要で、その結果、革新的な製品をいち早く

市場に投入できるようになります。

ASIC 開発は、各プロセス ジオメトリが縮小するにつれ初期コストが指数関数的に上昇されることから、多くのアプリケーションでこの方法は魅力のないものになってきています。また、ASSP では、ユーザーのニーズを全て満たすことは通常できないので、シリコン メーカーは最も多くのユーザーが要求する機能をあらかじめインプリメントする必要があります。

今後この革新の中心となって行くのは Xilinx® の FPGA および CPLD です。これらは、高い柔軟性に加え、低コストソリューションが提供可能なことから、デジタルディスプレイやセットトップ ボックス、車載後部座席エンターテインメント システム、スマートフォン、ビデオ機器など、量産製品の特定アプリケーションの要件を満たします。

### 民生電子機器でのザイリンクス

民生用電子機器メーカーは、自社製品を競合他社製品と差別化する必要があります。

競争の厳しい市場で一步先を歩み続けるには、最新技術と革新的機能をできるだけ早く消費者に提供することが必要不可欠です。製品のライフ サイクルの後半で、メーカーは製品コストを下げることに注力し、より安価でより多くの機能を利用者に提供する努力を続けます。

たとえば、HDTV デジタル ディスプレイのメーカーは、完全な TV 画像を提供できるようある欠陥に対処した画質の改善に取り組みながら、新しいフラットパネル技術やインターフェイス標準への対応に直面する

ことがあります。異なるモデルで使用されているパネルは、仕様が異なったり、あるいはまったく別のサプライヤのパネルであったりすることが多いのです。

FPGA のプログラマビリティを利用し、Spartan® FPGA にインプリメントされた

高画質化アルゴリズムを使用すれば、これらの変化に対応するのは容易です。また、同じハードウェア デザインを製品の全ファミリに利用することも可能です。Spartan FPGA は、ほとんどの差動 I/O インターフェイスをサポートしているので、新しいパネル インターフェイスに直接インターフェイスするのが容易です。Spartan FPGA はこれらの利点により、多くの民生電子機器で採用されています。

### 車載電子機器でのザイリンクス

OEM 自動車メーカーは、より多くの電子機器を自社自動車に搭載していくことで、他社製品との差別化を図る傾向にあります。一言で電子機器システムというと幅広いのですが、これには、ドライバの情報システムや後部座席のエンターテインメント Sys

テムから、夜景システム、レーンはみ出し警報システムなど新しいドライバ支援技術までが含まれます。

ザイリンクス オートモーティブ (XA) ファミリは、車載用電子機器市場に FPGA と CPLD のスケーラビリティと柔軟性を提供します。これにより主要自動車メーカーは革新的な機能を考案できるようになります。また、プラットフォーム開発機能が、細分化されたアプリケーションの分野にも利用可能となり、コストの低減化が図れます。

LCD/TFT ディスプレイやマルチブルネットワーキング プロトコル、ビデオ、グラフィックスの使用が増えるにつれ、ザイリンクス XA ソリューションは開発から生産までのサイクルを加速し、また柔軟性の高いカスタマイズを可能にします。自動車メーカーは、ザイリンクス XA プログラマブル ロジックを使用することで、次の電子機器の再設計を待つことなく、FPGA 内の構成を変えるだけで、新しい機能の追加や、既存機能の改良、あるいはインターフェイスの変更が可能です。また、FPGA を使用することにより、デザイナは、アプリケーション アーキテクチャ全体を見直して、ニーズに基づいたシステムの構築を、半導体ハードウェアで現在何が利用可能なのかを考えることなく行うことができます。

### 結論

ザイリンクスの量産向け製品である Spartan FPGA や CoolRunner™-II CPLD、XA 製品ファミリは、開発に伴うリスクを最小化できるプログラマブル ロジックの柔軟性を備えているため、メーカーはさらに革新的な製品をいち早く市場に投入できるようになります。

ザイリンクスは、最先端技術の採用とサプライヤからのコスト削減により、低価格化を実現し、量産への採用が増大しています。ザイリンクスの FPGA および CPLD は、より低い価格設定から始まっており、民生用電子機器や車載用電子機器などの量産アプリケーションでも、量産時に ASIC や ASSP への移行が不要で、しかもユーザーの要望に沿ったカスタマイズが可能です。

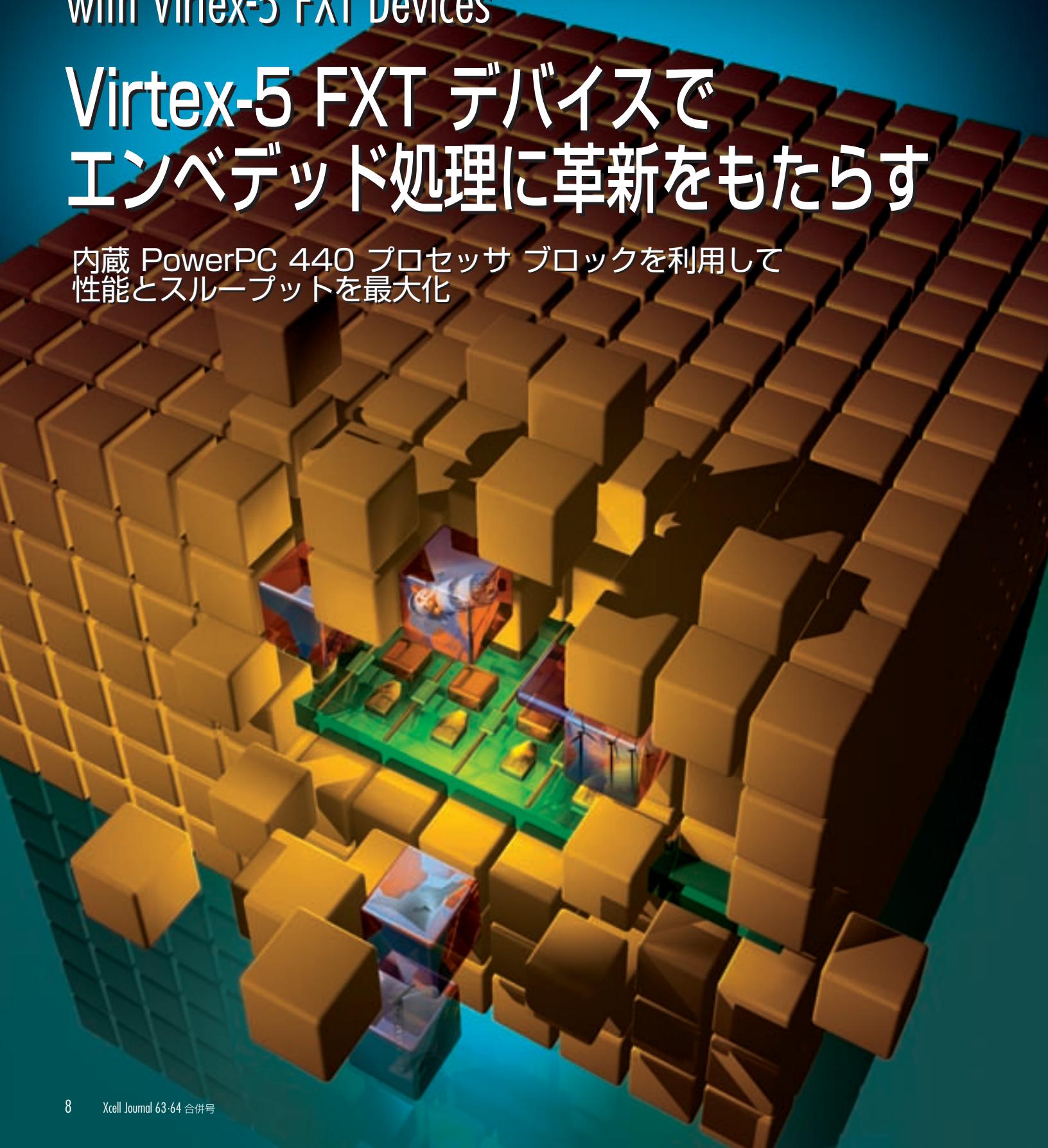

## Embedded Processing Innovations with Virtex-5 FXT Devices

# Virtex-5 FXT デバイスで エンベデット処理に革新をもたらす

内蔵 PowerPC 440 プロセッサ ブロックを利用して

性能とスループットを最大化

Craig Abramson

Product Marketing Manager

Xilinx, Inc.

craig.abramson@xilinx.com

Dan Isaacs

Director of Embedded Processor Marketing

Xilinx, Inc.

dan.isaacs@xilinx.com

Ahmad Ansari

Principal Engineer

Xilinx, Inc.

ahmad.ansari@xilinx.com

ザイリンクス Virtex®-5 FXT FPGA を採用することにより、エンベデッド システム デザインにおける市場優位性を持つ可能性がでてきました。これまで、エンベデッド システムを短期間に開発しその有効性を確認する必要性は、エンベデッド システム デザイン以外の分野では必ずしも明確ではありませんでした。

ソフトウェアとハードウェアを組み合わせて、これをシステム レベルでできるだけ短期間に実証することは、業界の常識となっています。より緊密に連携された柔軟性の高いスケーラブルなソリューションを提供することにより、ハードウェアとソフトウェアの SoC デザインの多くの課題に対処可能となります。

FPGA は、デザイナがエンベデッド デザインを開発し、プロトタイプ作成後にテストするまでの作業時間を大幅に短縮します。PowerPC® プロセッサを内蔵した第 3 世代の Virtex-5 FXT FPGA プラットフォームは、新たにエンベデッド ブロックを追加しており、より厳しいデザイン要件にも対応可能で、デザインの迅速かつ容易な完成に寄与します。

本稿では、PowerPC 440 プロセッサ ブロックとシステム インターコネクトがもたらすエンベデッド 处理における革新について詳しく説明します。Virtex-5 FXT FPGA プロセッサ ブロックは、インテグレーションによる簡略化にフォーカスしています。

これによって、開発とテストが簡易化されます。Virtex-5 FXT デバイス PowerPC

440 プロセッサは、ソフトウェア開発者がシステムを迅速に立ち上げ、ハードウェアにおける実際の開発を早期にスタートできるようにすることを最大限に支援するソリューションです。

## インテグレーションによる簡略化

鍵はインテグレーションにあります。ザイリンクスは、少ない FPGA ロジックの使用量で高性能処理システムを構築し、かつ多種多様なトポロジーを実現しています。FPGA ベースのインプリメンテーションには元々柔軟性という利点がありますが、さらに、ハード化や、特に外部メモリへのアクセスの最速化を実現する統合されたインターフェクチャによる新しい利点も享受できます。

その結果より広範な高性能処理アーキテクチャをより短期間で開発できるエンベデッド ブロックが作成できます。

PowerPC プロセッサには一般的に 3 つのインターフェイスがあります。それは、命令の読み出し、データの読み出し、データの書き込みです。PowerPC 405 内蔵の Virtex の旧世代デバイスのアーキテクチャでは、これらのプロセッサ バスは FPGA ファブリックに接続されていました。この回路のタイミング クロージャ要件は、デザインによりバスに加えられる負荷の数と種類により変化します。

PowerPC 440 内蔵の Virtex-5 FXT FPGA では、これらのバスはハード化されて新しい構造に直接接続されています。この構造は、統合された  $5 \times 2$  クロスバースイッチで、一般的にはクロスバーと呼ばれています。このハード化されたインターフェクチャは、Virtex-5 FXT デバイスのエンベデッド プロセッサ ブロックにおいてアーキテクチャが強化されている他の部分と接続された際に、FPGA のロジック リソースを使わずに固定されたタイミングで、かなりの高性能を実現します。この結果、システムの全体コストが低減され、より緊密に統合化されたプロセッサ システムが常に開発できます。

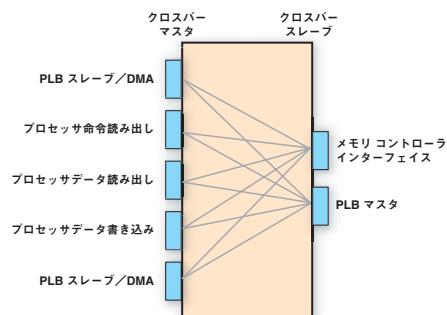

プロセッサ バスは、 $5 \times 2$  クロスバー上の 5 つの「クロスバー マスタ」ポートのうち

図1 - クロスバー

3 つのみを使用します (図 1 参照)。クロスバーには 2 つのマスタ ポートが残っていますが、それは、実際のアプリケーションでは、メモリやペリフェラルへのアクセスはプロセッサ以外も必要になることが多いのです。これらの「クロスバー マスタ」ポートは、プロセッサ ローカル バス (PLB) スレーブ インターフェイスと 2 チャネルのスキャター/ギャザー ダイレクト メモリ アクセス (DMA) で構成されています。

クロスバーの「スレーブ」側は 2 つのポートで構成されています。1 つのポートは専用のメモリ コントローラ インターフェイスで、ソフト メモリ コントローラに対して高スループットの一般的なインターフェイスを提供します。

## より高性能なプロセッサ

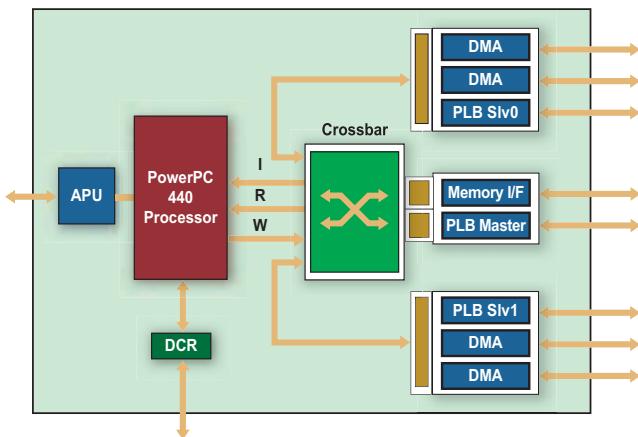

エンベデッド プロセッサ ブロックにこれらの機能をすべて追加したとしても、それを利用する強力なプロセッサがなければ、さほど効果は期待できません。Virtex-5 FXT FPGA は、FPGA に PowerPC 440 クラスのプロセッサを内蔵した最初のデバイスです。

PowerPC 440 は、PowerPC 405 (Virtex ファミリの旧世代デバイスに内蔵) に比較すると、いくつかの分野で大幅な性能改善が行われています。

まず、PowerPC 440 を最速スピードグレードの FPGA 内で使用すると、550 MHz でクロッキングができます。PowerPC 405 の最高スピードは 450MHz ですが、これはほぼ 20% の性能改善に相当します。加えて、I (命令) と D

図2 - PowerPC 440 エンベデッド プロセッサ ブロック

(データ) のキャッシュ サイズが 2 倍になっており、命令のパイプラインが 5 ステージから 7 ステージに増え、さらに実行ユニットは順不同の 2 つの命令をパラレルに実行できます。

その結果、今日のエンベデッド プロセッサが抱える多くの課題に対応できる十分な性能のプロセッサが作成できます。

表 1 は、PowerPC 405 から PowerPC 440 への移行に伴う利点を示します。

図 2 は、PowerPC 440 のエンベデッド ブロックを示します。

## 高スループット スイッチ マトリックス

5 × 2 クロスバーは、ただ大きいだけではありません。5 つのクロスバー マスターから 2 つのクロスバー スレーブへの非プロトキシング パイプライン アクセスが可能です(図 1 参照)。クロスバー上の異なるエージェント間で、平行転送が同時にできます。

図に示すように、クロスバーに向かうバスを「クロスバー マスター」と呼び、クロスバーから出てくるバスを「クロスバー スレーブ」と呼びます。これらのインターフェイスは高度にパイプライン化されているため、多数の処理を同時に進行させることができます。

実際には、最大で 4 つの同時処理が可能です。各クロスバー スレーブ(メモリ コントローラと PLB マスター)に 2 つずつ処理できます。さらに、各クロスバー マスター(3 つのプロセッサ PLB インターフェイスと 2

トストリームを介してプログラムするか、あるいは FPGA の外部ロジックでデバイスコントローラ レジスタ (DCR) バスと呼ばれるクロスバーのサイドバンド バスを使ってプログラムします。

## 統合 PLB インターフェイス

前述のとおり、クロスバーに接続されている多くのバスは、プロセッサ ローカル バスで、PLB とも呼ばれます。

PLB は、IBM 社によって定義された標準 CoreConnect バスの一つです。PLB の早期バージョン(バージョン 3.4)は、Virtex-II Pro と Virtex-4 FX FPGA 内蔵 PowerPC 405 の標準バスの 1 つとして使われていましたが、新しい PowerPC 440 エンベデッド プロセッサ ブロックでも使用されています。

PowerPC 440 エンベデッド プロセッサ ブロックでは、PLB はプロセッサの内部 キャッシュをクロスポートの入力側に接続します。接続するバスは次のとおりです。

- ICURD : 命令キャッシュ ユニット読み出し

- DCURD : データ キャッシュ ユニット読み出し

つの PLB スレーブ インターフェイス) は、同一のスレーブに対して、4 つの読み出し処理と 4 つの書き込み処理をパイプライン化できます。

クロスバーのこの他重要な機能として、メモリ マッピングが高度にプログラマブルできます。全体のシステムが、4GB のメモリ空間を利用できると仮定します。メモリ コントローラ インターフェイスと PLB マスターの両方は、いずれのクロスバー マスターのメモリ空間にも異なるメモリ ウィンドウをマッピングできます。これらのメモリ空間は、実行時のプロセッサで FPGA のビッ

表1 - PowerPC 内蔵 Virtex のプロセッサ機能比較

|                | PPC405<br>(Virtex-4 FX FPGA)             | PPC440<br>(Virtex-5 FXT FPGA)                          | PowerPC 440<br>の利点                |

|----------------|------------------------------------------|--------------------------------------------------------|-----------------------------------|

| アーキ<br>テクチャ    | 32 ビット命令、<br>32 ビット アドレス、<br>64 ビット データ  | 32 ビット命令、<br>36 ビット アドレス、<br>128 ビット データ、<br>Book E 準拠 | より多い物理メモリ<br>にアクセス、<br>より高速なデータ移動 |

| パイプライン         | シングル命令/サイクル、<br>5 ステージ パイプライン、<br>順序通り実行 | 2 命令/サイクル<br>7 ステージ パイプライン、<br>順不同で実行                  | より効率的な<br>命令実行                    |

| キャッシュ -<br>I/D | 16K/16K、2-way セット<br>アソシエーティブ<br>非ロッキング  | 32K/32K、64-way<br>セットアソシエーティブ、<br>ロッキング                | メモリ アクセスの<br>待ち時間が短い              |

| MMU            | ページ サイズ: 1KB~16MB                        | ページ サイズ: 1KB~256MB                                     | ページ交換が少なくて済む                      |

| DMIPS 評価       | 700 DMIPS 以上                             | 1000 DMIPS 以上                                          | より良いベンチマーク<br>による高性能化             |

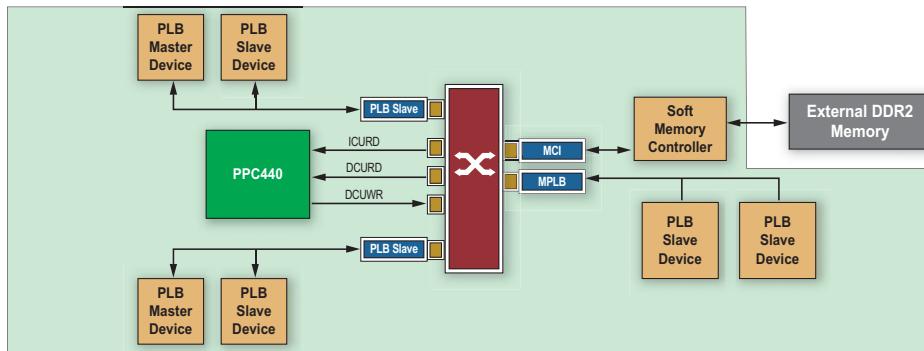

図3 - PLB マスタとスレーブ

- DCUWR : データ キャッシュ ユニット書き込み

Virtex-5 FXT デバイスで使用されている PLB はバージョン 4.6 (PLB46) です。PLB46 のバス アーキテクチャは、従来なかった高性能な新しい機能を備えています。事実、PLB34 は 64 ビットで、PLB46 は 128 ビットであるためこれは明白です。バスに接続された IP コアのビット数がそれより少ない場合でも心配することはありません。バスは、32 ビット処理と 64 ビット処理を適応させるのに必要なバス サイズの分割をダイナミックに実行します。

ただし、PLB46 バージョンは IBM 社が定義した PLB46 を、ザイリンクスがインプリメントする際、FPGA リソースをできるだけ利用できるように最適化されているということに注意する必要があります。

PLB46 は、実際には PLB のすべてのバージョンで、マスタとスレーブの概念を持っています。これをクロスバー マスタおよびクロスバー スレーブと混同しないよう注意が必要です(図 1 を参照)。前述のとおり、クロスバーには 2 つの PLB スレーブ ポート インターフェイスがありますが、これはクロスバー マスタです。これらのスレーブ ポートは FPGA ファブリックに接続されます。

プロセッサ システムでは、多くの場合、プロセッサが外部メモリやオンチップ ペリフェラルにアクセスする以外に別のものを許可する必要が生じます。PLB スレーブ インターフェイスは、それらを許可する役割を担います。FPGA ロジックで構築されて、PLB スレーブ ポートに接続されている

PLB マスタ(図 3 参照)は、クロスバーを介して MCI か MPLB のいずれかにアクセスできます。

同様に、PLB マスタ(クロスバー スレーブの一つ)の機能には、PLB を I/O デバイスとソフト ペリフェラルに接続する機能が必要になります。PLB マスタはクロスバー スレーブですから、クロスバー マスタ ポートに接続されるものすべてにアクセスできることになります。

各 PLB スレーブ バスに接続された PLB マスタは、4 つを超えて存在できないことに注意してください。4 つ以上のマスタを必要とするシステムは稀ですが、その場合は、エンベデッド開発キット (EDK) により提供されている PLB/PLB ブリッジ IP コアを常に使用できます。([http://japan.xilinx.com/support/documentation/ipembed/process\\_coreconnect\\_plbbusstruct.htm](http://japan.xilinx.com/support/documentation/ipembed/process_coreconnect_plbbusstruct.htm) を参照してください)。

図 3 は簡略化したシステム ダイアグラムで、PLB ペリフェラルをクロスバー マスタ ポートとクロスバー スレーブ ポートへ接続する方法を示します。1 つの PLB 上に複数のマスタがある場合には、バスに対する IP コアでアービトレイションを取り扱う必要があることに注意してください。個別のアービターは必要ありません。

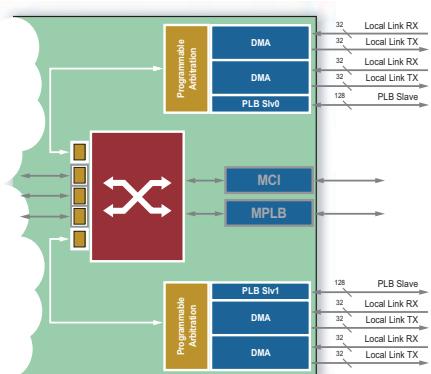

## 最適化 DMA エンジン

その他に 4 つのクロスバー マスタがあります。それは 4 つの DMA チャネルです。各 DMA チャネルは、32 ビット送信インターフェイスと 32 ビット受信インターフェイスを個別に持っています。図 4 に示す

ように、それは PLB スレーブ インターフェイスとクロスバー アービトレイションを共有します。

DMA ポートはすべて同時に動作できます。各 DMA ポートは専用の FIFO を持っているため、一つの DMA がデータを蓄積している間に、他の DMA がクロスバーを介してデータを送り込むことができます。各 DMA チャネルは、プロセッサ クロックとは非同期で動作します。

DMA チャネルへのインターフェイスは、LocalLink と呼ばれるインターフェイスを介して行われます。ザイリンクスは、多くの IP コアブロックに LocalLink を使用しています。LocalLink は、ポイントツー ポイントのインターフェイスで、外部デバイスにパケットを送信したり、外部デバイスからパケットを受信したりします。

LocalLink インターフェイスを使用している最も注目すべきプロセッサ IP コアは、ハード エンベデッド トライモード Ethernet メディア アクセス コントローラ (TEMAC) ブロックです。TEMAC はラップを持っていているため、PowerPC 440 DMA と直接通信できます。

クロスバーを通るすべてのデータ パスは 128 ビットで、DMA チャネルから来る LocalLink インターフェイスと DMA チャネルへ向かう LocalLink インターフェイスはすべて 32 ビットです。すなわち、DMA コントローラとクロスバーの間には、データを再調整する内蔵ロジックが存在します。

PowerPC 440 エンベデッド ブロック

図4 - PLB スレーブ バスと DMA チャネルはクロスバー アービトレイションを共有

はスループットと性能を最大化するため、スキャター／ギャザー DMA を採用しています。ザイリンクスはこの機能の使用をできる限り容易化するため、各種 IP コアと IP コアが提供するエンベデッド ブロックに対してラッパを提供しています。

PowerPC 440 を特定して向かう第 1 のターゲットは、エンベデッド TEMAC ブロック用ソフト ラッパです。このラッパを、PowerPC 440 エンベデッド ブロック内の DMA エンジンの機能と組み合わせて使用すると、PowerPC 440 DMA チャネルに直接接続された高性能 TEMAC で処理システムを容易に構築できます。図 5 は、DMA と PLB の両ペリフェラルがクロスバー マスターとクロスバースレーブの各ポートに接続される方法を示します。

DMA チャネルはデスクリプタで制御され、メモリの小さなブロックは DMA 動作を開始する前に PowerPC 440 プロセッサによってセットアップされます。デスクリプタは、転送するデータの量とシステムメモリ内でのそのデータの配置先を制御します。

必要に応じて、複数のデスクリプタと一緒につなぎ合わせることが可能です。これによって、DMA チャネルを制御するコマンド シーケンスを効率的に生成できます。DMA コントローラの詳細は、「Embedded Processor Block in Virtex-5 FPGA (英語

版)」([http://japan.xilinx.com/support/documentation/user\\_guides/ug200pd\\_f](http://japan.xilinx.com/support/documentation/user_guides/ug200pd_f))をご覧ください。

## 高性能専用メモリ インターフェイス

新しいプロセッサ ブロックの紹介の最後に、専用のメモリ コントローラ インターフェイスを示します。このインターフェイスは、外部メモリに対して専用リンクを提供することを目的としていますが、ある特定メーカーのメモリ接続のみに限定されてしまいません。

現時点では、このメモリ コントローラ インターフェイスは、スタンドアローンの DDR2 コントローラと MPMC4 コントローラをサポートしていますが、それらはすべて Xilinx Platform Studio および EDK 10.1 を介して利用できます。このインターフェイスには高い柔軟性があるため、今後もほぼすべてのメーカーで製造されたメモリに接続できます。

このメモリ コントローラ インターフェイスは合理化されており、アドレス／データ／制御信号で構成されています。128 ビット、64 ビット、32 ビット、16 ビットのメモリでもサポートできるようにプログラムが可能です。ビット幅とバーストの再編成を行うため、DMA が 1 つのサイズの

パケットをバースト転送している際、メモリ コントローラはメモリへのバンド幅が最大になるようにパケットデータをバッファリングして再編成します。バースト サイズは 1、2、4、あるいは 8 のいずれかににプログラム可能で、メモリ コントローラ インターフェイスは、アドレスを自動的に調整して各種のバースト幅に対応します。

ソフト メモリ コントローラのハンドシェーク用信号の多くは、メモリ コントローラに代わってこのインターフェイスで生成されます。これらの信号は前もって提供され、ソフト メモリ コントローラがスロットル信号を生成してメモリ インターフェイスに戻せるようにします。メモリ コントローラ インターフェイスは、ソフト メモリ コントローラに代わって、前もってバンクと欠損行を検出するようにプログラムが可能で、検出した内容をソフト メモリ コントローラに送信してバンクや欠損行を予想できるようにします。これらの機能をすべて一つにまとめると、メモリのスループットを最大化するソリューションが得られます。

## システムのチューニング

ある状況下では、PLB や DMA インターフェイスが正確で正しいソリューションではない場合もあるでしょう。たとえば、実行に多くのサイクルが必要で、システムのバンド幅に影響を与えるソフトウェア アルゴリズムが存在したと仮定します。そのアルゴリズムはハードウェアでインプリメントする必要があり、そのハードウェアを接続するインターフェイスが、補助的処理ユニット、すなわち APU インターフェイスです。

PowerPC 440 には、プロセッサの実行ユニットに緊密に接続された第 2 世代の APU インターフェイスがあります。このインターフェイスは 16 個のユーザ定義命令 (UDI) で制御されます。APU インターフェイスのデータ パスは 128 ビットです。

APU インターフェイスは、浮動小数点ユニット (FPU) に接続する目的でに使用するのが一般的でしょう。FPU は IEEE754 に準拠しており、PowerPC 440 に対するシングル精度と倍精度の両方をサポートして

図5 - PLB と DMA の両ペリフェラルを搭載したシステム例

図6 - ザイリンクス ML507 評価ボードと ML510 開発ボード

います。

FPU は FPGA のソフトロジックファブリックにインプリメントできます。ソフトロジックへのインプリメンテーションは、最大でハードエンベデッドプロセッサの半分の周波数で動作します。

APU インターフェイスの他の使用方法として、ハードウェアアルゴリズムの加速用とブロック RAM への高バンド幅リンクの代替が考えられます。

## エンベデッド ブロックのコンフィギュレーション

PowerPC 440 ブロックを FPGA に集積する際、プロセッサ ブロックは複数の方法でコンフィギュレーションができます。ほぼすべてのインターフェイスはプログラマブルです。

たとえば、Xilinx Platform Studio 開発環境で処理システムを構築し、そのためのビットストリームを生成するには、処理システムの仕様のすべてがそのビットストリーム内に置かれます。このように、FPGA がスタートアップすると、プロセッサが起動して実行を開始します。

ここで、処理システムが起動して実行している間に DMA チャネルの一つを変更したい場合を仮定します。それは、DCR インターフェイスを介して行うことができます。DMA 動作のすべての側面を制御する DCR

レジスタが存在するのです。

実際に、エンベデッド ブロックの他のサブシステムすべてへの DCR アクセスが存在します。サブシステムとしては、PLB やクロスバー、メモリ コントローラ インターフェイス、APU コントローラが挙げられます。詳細は図 2 を参照してください。

## すべてと一緒にまとめる

この革新技術は、ザイリンクスがアーキテクチャ上の強化策のすべてを利用できる包括的なインフラを提供することで実現しています。PowerPC 440 ブロック内蔵の Virtex-5 FXT FPGA は、ザイリンクスの 8 年にもおよぶエンベデッド処理の経験に基づいてハードプロセッサを搭載した第 3 世代 FPGA へ引き継がれています。

ザイリンクスは、エンベデッド開発キット (EDK) にアップデートを加え改善を繰り返し、賞も受賞しています。EDK には、Platform Studio とハードウェアデザイン用の包括的な IP コアライブラリが含まれています。また、Platform Studio SDK は、エンベデッドソフトウェアエンジニアの多くに使いやすいソフトウェア開発環境を提供します。

ザイリンクスは、Virtex-5 FXT デバイスファミリの発表により、Wind River Systems 社や VxWorks 社、Green Hills Integrity 社を代表とする業界最先端のオペ

レーティング システムをサポートするプロバイダとのサードパーティ アライアンス関係をさらに強化していきます。

Linux のサポートは、LinuxWorks 社や Monta Vista 社、Wind River Systems 社によって行われます。また、ザイリンクスはオープンソース Linux の重要性を認めており、それらへの対応も進める考えです。

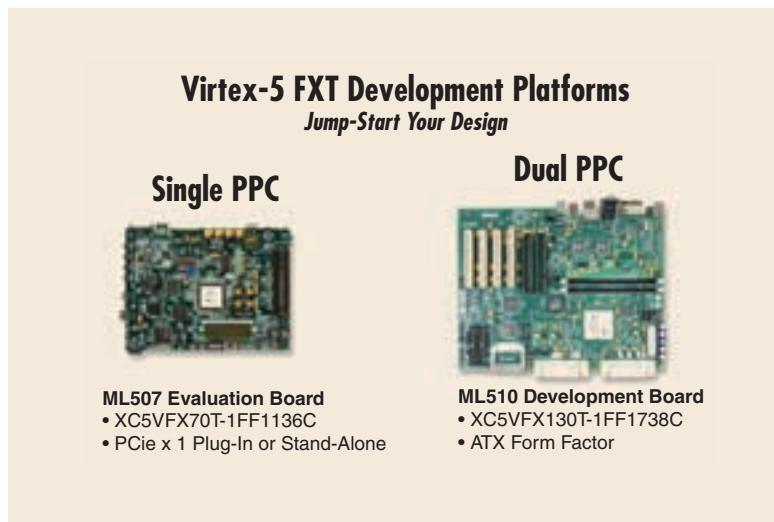

ザイリンクスとパートナー企業は、多種多様のボードも共同開発しています。Virtex-5 FXT デバイス向けにも複数のボードが開発されています。図 6 に示すように、XC5VFX70T を搭載した ML507、XC5VFX130T を搭載した ML510 です。ML507 評価プラットフォームは、ハードウェアとソフトウェア両方の迅速な開発を実現します。複数のプロセッサやマザーボード タイプのプラットフォームが必要な場合は、デュアル プロセッサ XC5VFX130T を搭載した ML510 が理想的です。

## 結論

データのスループットを最適化した高性能処理ソリューションは、全世界のエンベデッド設計者が待ち望んでいるものです。これには、最新のワイヤレスベースステーションの中心でクリティカルなアルゴリズムを実行したり、ビデオスイッチを介して高バンド幅データをスイッチングしたり、コプロセッサアクセラレーションを使うガイダンスシステムのための先進信号処理を実行したり、あるいは複雑な制御とシステム管理タスクを扱ったりする場合などが挙げられます。

Virtex-5 FXT エンベデッドプロセッサ ブロックは、複数ポートの非ブロッキング統合プロセッサ インターコネクトや、高性能統合 DMA と共に、エンベデッドデザインの重要なエレメントに集中できるソリューションを提供します。

これらのエンベデッド機能は数多くの使い方が考えられます。Virtex-5 FXT FPGA エンベデッド処理ソリューションは、高性能で高スループットな SoC デザインに高度に統合されたプラットフォームを提供します。 ●

# Decrease Processor Power Consumption Using a CPLD

## CPLD でプロセッサの消費電力を低減する

CPLD によりシステム マイクロプロセッサへの演算荷重を低減させ、プロセッサをより長くパワー セーブ モードにすることにより、大幅な消費電力の削減を実現

Mark Ng

Applications Engineer

Xilinx, Inc.

mark.ng@xilinx.com

今日の携帯電子機器の設計にあたり最も重要なファクタの一つは、システム全体の消費電力を低減することです。機器ユーザーの期待にこたえるには、携帯デバイスの長いバッテリ寿命と高性能化が必要です。10mW 程度の消費電力でも、携帯システム デザイナとメーカーにとって大きな意味を持ちます。

今日のデザイナはシステム全体の消費電力を大幅に低減できるよう、次に示すデザイン手法を使用しています。

- ・動作電圧を下げる

- ・システムと CPU のクロック周波数を最適化する

- ・パワー アップ シーケンス時に、多くの電流を消費するスパイクを除去する

- ・システムのバッテリ動作を効率よく管理する

- ・システム デバイスの動作モードを効率よく管理する

- ・バスの動作を極力減らす

- ・バスの容量負荷を減らす

- ・スイッチング ノイズを減らす

これらは、アプリケーションにおける消費電力の低減を実現するためのデザイン手法のほんの一部です。

ここに示される最も重要な消費電力設計は、システム内デバイスの動作モードを管理する機能です。今日、多くのメーカーは、デバイスをノーマル動作から一時停止させるパワー セーブ モード機能のデバイスを提供しています。これらのデバイスには、ある特定の時間デバイスがアクティブでないときは、パワー ダウンするか非動作状態に移行するオプションがあります。この機能は、今日のマイクロプロセッサやマイクロコントローラの多くで使用されています。これにより、基板上の電力を多く消費するデバイス、たとえばプロセッサの動作モードを管理することにより、システム全体の消費電力を大幅に低減することができます。

消費電力を低減するには、デバイスの動

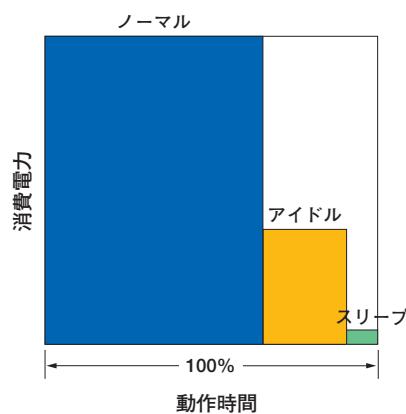

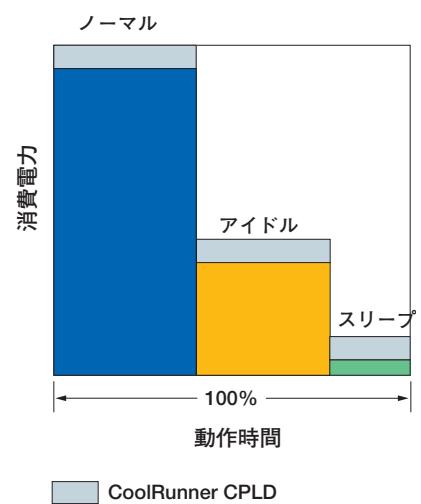

図1 - Web Pad の消費電力

作モードを正しく管理することだけでなく、デバイスが動作できるモードをうまく利用してシステムをデザインする必要があります。マイクロプロセッサの演算負荷を低減すれば、プロセッサはより長い時間低消費電力状態に保持されます。システム電力を低減する一つの方法として、CPLD のような低消費電力プログラマブル ロジック デバイスを使い、これらの演算負荷を開放することが挙げられます。本稿では、この可能性について解説し、あわせてプロセッサが低消費電力状態に長く保持される動作の種類について述べます。

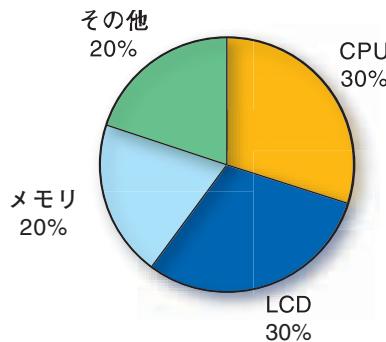

### マイクロプロセッサの動作モード

ある携帯アプリケーションでは、システム消費電力全体の 30% を CPU が占めます。図 1 は、Web Pad アプリケーション上の各システム コンポーネントの典型的な消費電力を示します。

ノーマル動作時のマイクロプロセッサの消費電力は  $720\mu\text{W} \sim 1\text{W}$  です。マイクロプロセッサの動作モードはパートごとに

異なり、メーカーによっても違います。ノーマル、実行、スリープ、一時停止、スタンバイ、停止、アイドルなどが挙げられます。動作モードによって消費電力は異なり、モード間の差異は  $230\text{mW}$  にもなります。ある低消費電力マイクロプロセッサのノーマル動作時の消費電力が  $250\text{mW}$  と少ないものもあります。

### 例

ここに掲げるマイクロプロセッサ リファレンスは、動作モードにより消費電力がどのように異なるかを例証しています。消費電力を決定する標準的な方法は存在せず、本稿に掲載したデータはメーカーが提供しているものに基づいています。参考にとどめてください。(詳しくは本稿後述の『参考』をご覧ください。)

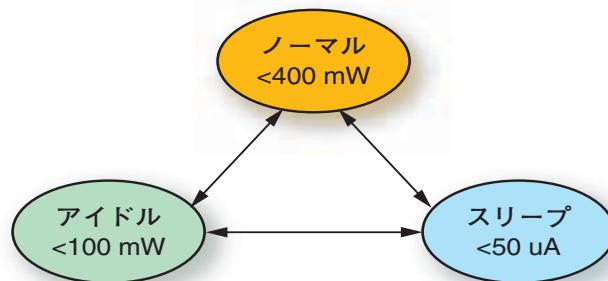

マイクロプロセッサの動作モードでの消費電力の違いを、例で示します。図 2 は、インテル社製 StrongARM SA-1110 マイクロプロセッサの動作モードを示しています。図 2 に示した消費電力の数値は、公称外部電源電圧  $3.3\text{V}$ 、内部電源電圧  $1.8\text{V}$  の条件下で  $206\text{MHz}$  動作時の数値です。

StrongARM プロセッサの動作モードには、ノーマル、アイドル、スリープがあります。ノーマル動作では、CPU はフル稼動状態で、デバイスにはフルに電力が供給され、アクティブ クロックを受信している状態です。アイドル モードでは、CPU と他のコンポーネントに電力は供給されていますが、CPU へのすべてのクロックは停止され、ペリフェラル デバイスへのクロックだけがアクティブになっています。スリ

図2 - インテル社製 StrongARM SA-1110 の消費電力

ープ モードでは、CPU と他のペリフェラル コンポーネントへの電力はすべてデバイス内で遮断されています。スリープ モードでは、リアルタイム クロックや割り込みコントローラ、パワー マネージャ、汎用 I/O を除くすべてのファンクションは無効にされています。

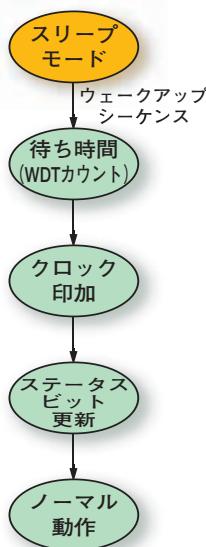

## 動作モードの制御

パワー セーブ モードのあるマイクロプロセッサは、オンボードの電源管理コントローラを備えています。動作モードを利用すれば、オペレーティング システムやソフトウェア アプリケーションが CPU を一時停止させることができます。マイクロプロセッサは、一連の命令を実行した後にパワー セーブ状態に入ります。パワー ダウン モードに入っても、マイクロプロセッサのコンポーネントの一部にはシステムの割り込みに応答できます。

たとえば、StrongARM SA-1110 プロセッサのアイドル モードではかなりの電力が低減されますが、LCD やメモリ、I/O コントローラのようなモジュールには電力が供給された状態になっています。CPU に対するクロックが停止されても、ペリフェラル モジュールはまだアクティブになっています。アイドル モードでもかなりの

電力を消費し、100mW のオーダーです。プロセッサをスリープ モードにすると、割り込みとウェークアップ信号要求に応答するモジュールだけに電源が供給されてアクティブになります。スリープ モードで消費される電力はアイドル モードのときよりも少なく、消費電流は  $100 \mu A[m1]$  以下となります。

プロセッサがパワー ダウン モードからノーマル動作に戻ると、イベントが 1 つ発生します。次に挙げるイベントがプロセッサをウェークアップしますが、それはプロセッサのメーカや型番、および現在の動作モードによって異なります。

- ・ハードウェア リセット

- ・システム割り込み

- ・汎用 I/O 割り込み

- ・リアルタイム クロック割り込み

- ・OS タイマ割り込み

- ・ペリフェラル割り込み

- ・外部ウェークアップ信号

ウェークアップ イベントがイネーブルされたことを認識したら、マイクロプロセッサはパワー ダウン状態からウェークアップするための一連のステップを開始します。図 3 は、プロセッサがパワー ダウン モードからウェークアップするときの一般的なフローを示します。

マイクロプロセッサが許可されている割り込みを受け取ると、プロセッサはその割り込み要求に応答します。プロセッサが割り込みに応答しているときは、実行モード、すなわちノーマル モードで動作します。プロセッサに対する割り込み数を減らすと、プロセッサがパワー セーブ状態にかかる時間が増えます。マイクロプロセッサに実行すべき命令がなければ、パワー セーブ モードが永遠に保持されるというわけです。システムの割り込みに応答しこれを扱える外部デバイスを挿入すると、プロセッサに要求されている演算を減らすことができます。マイクロプロセッサをできるだけ長くパワー ダウン モードに保持できれば、大幅な消費電力の削減が実現できます。

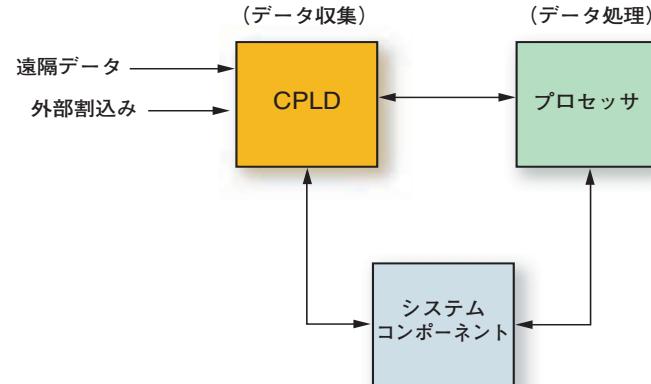

低消費電力のプログラマブル ロジック デバイスを利用してマイクロプロセッサを補完すれば、システム電力を低減でき、バッテリの長寿命化が可能です。業界最新の CPLD 製品は、高性能と低消費電力の両方を同時に提供しています。典型的な低消費電力 CPLD のスタンバイ電流は  $100 \mu A$  以下です。図 4 は、受信したシステム割り込みにインターフェイスするリプログラマブル CPLD の使い方を示します。外部のデータ収集デバイスを利用してマイクロプロセッサに求められる割り込み要求を開放できれば、システム全体の電力は低減されます。

図3 - ウェークアップ シーケンス

## CPLD デザイン

マイクロプロセッサが特定の時間アイドル状態にあると、動作モードに入ります。

図4 - システム ブロック ダイアグラム

## システム割り込み

プロセッサの最終アプリケーションが何

かによりますが、さまざまな外部デバイスがプロセッサに割り込みを送信します。割り込みには、データ収集要求とデータ処理要求の両方が含まれます。マイクロプロセッサに対するデータ処理割り込みを分離すれば、データ収集割り込みは外部 CPLD でサービスできることになります。CPLD を利用してデータ収集割り込みを取り扱えば、マイクロプロセッサに対する割り込み要求を開放することになり電力を低減できます。

データ収集割り込みが CPLD に対してであるかどうかの判断は、最終アプリケーションに依存します。しかし、ペリフェラルデバイスや受信データへの応答を要求する受信データは、データ収集割り込み要求に分類されます。データ収集割り込みには次のものがあります。

- ・メモリアクセス割り込み

- ・I<sup>2</sup>C や UART、SPI、ISA などの通信インターフェイス

- ・汎用 I/O 割り込み

- ・LCD インターフェイス割り込み

図5 - CPLD フロー ダイアグラム

これは、CPLD で処理できる割り込みのリストのすべてではありませんが、システム デザインのスタート ポイントを提供します。

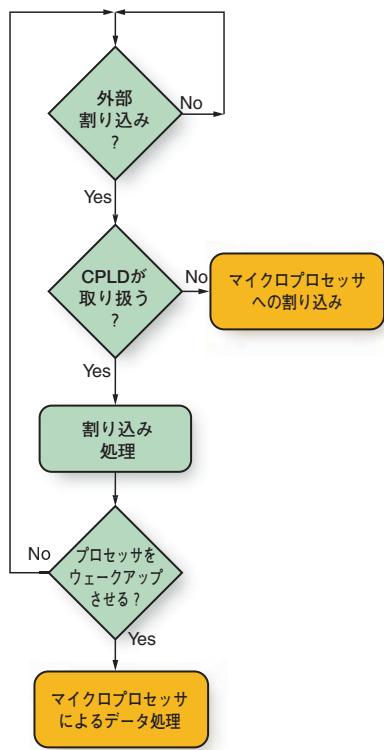

## 動作フロー

図5は、CPLD デザインの主な動作フローを示します。CPLD が有効な外部割り込みを認識すると、割り込みを処理する必要性があるかどうかを判断することになります。CPLD が割り込みを処理すると、プロセッサに対する割り込みをアサートすることができ、何らかのデータ処理要求が必要であることを伝えます。CPLD がこの割り込みを処理できない場合は、この割り込みはプロセッサに渡されます。CPLD はプロセッサの動作状態もモニタしています。

## CPLDの機能

低消費電力 CPLD のデザインは、割り込みインターフェイスと割り込み要求を取り扱うコントローラや、割り込みを処理する機能、プロセッサ インターフェイスで構成されます。次に、下記に挙げる CPLD の主なファンクションを個々に解説します。

- ・システム デバイス用の割り込みインターフェイス

- ・割り込みコントローラ

- ・割り込み処理用ペリフェラル デバイスとのインターフェイス

- ・マイクロプロセッサ割り込みインターフェイス

- ・マイクロプロセッサ動作モードインターフェイス

### 割り込みインターフェイス

CPLD の割り込みインターフェイスは、以前はマイクロプロセッサにより認識されていたすべての外部デバイスの割り込み要求を受け取ります。割り込みインターフェイスは、CPLD がその割り込み要求を処理することが可能かどうかを判断します。CPLD は、データの受信とストレージ機能を要求するデータ収集割り込みを取り扱います。CPLD がこの割り込みを処理できな

いときは、この割り込みをマイクロプロセッサに渡します。

CPLD の割り込みインターフェイスは、すべての割り込みソースに対するマスキング機能と割り込みソースを判断する機能を提供しています。プログラマブル ロジックはトリガー モードを変更する柔軟性を提供し、このトリガー モードの変更には、ハイ レベルまたはロー レベルの変更、立ち下がりエッジまたは立ち上がりエッジの変更が含まれます。CPLD の割り込み制御レジスタは、マイクロプロセッサ内部のレジスタに類似しています。

### 割り込みコントローラ

CPLD の割り込みコントローラは、システム マイクロプロセッサ内の機能をエミュレートします。割り込みコントローラは、どのデバイスからデータ収集割り込みが受信されたのかを判断し、その割り込みの処理を開始します。CPLD は、CPLD が処理しなければマイクロプロセッサに送信されてしまうようなデータ収集の割り込み要求のみを処理します。

割り込みコントローラは要求の処理に必要な操作を開始します。この例として、CPLD が遠隔デバイスからデータを受信するアプリケーションが挙げられます。デバイスはこれから送るデータをメモリに書き込むように要求します。CPLD の割り込みコントローラは、有効な割り込みを認識し、メモリ インターフェイスを起動してデータを読み取ります。

### ペリフェラル デバイスインターフェイス

CPLD は割り込み要求を処理するシステム デバイスへのインターフェイスを提供しています。必要とされるデバイスインターフェイスは、最終アプリケーションによって決定されます。外部デバイスが CPLD に割り込みをかけて、メモリ コンポーネントにデータを読み書きする場合、CPLD デザインにはその特定メモリへのインターフェイスが必要になります。必要とされるインターフェイスの種類は、メモリ インターフェイスから LCD インターフェイスまでに

及び、またその範囲は PCI、UART、SPI、および ISA などの通信インターフェイスまでを含みます。

### マイクロプロセッサ割り込みインターフェイス

CPLD は、プロセッサのサービスを要求する外部デバイスと同様に、マイクロプロセッサに割り込みを掛ける機能を持っています。データ収集動作が完了すると、CPLD はマイクロプロセッサに割り込みをかける必要があります。デザイナは、CPLD からの割り込み要求にプライオリティ レベルを設定することが可能です。また、CPLD からの割り込みを受信した際にプロセッサをパワー ダウン状態からウェークアップさせ

せるかどうかを選択することも可能です。

### マイクロプロセッサ動作モードインターフェイス

システム マイクロプロセッサによって、CPLD がプロセッサの動作状態を認識できる場合があります。あるマイクロプロセッサは、現在の動作モードを示す外部ピンを提供しているものもあります。また、CPLD とマイクロプロセッサのデザインによっては、CPLD がプロセッサの現在の動作状態を認識し、プロセッサに対して待機割り込みの実行を希望する内容の割り込みをアサートするかどうかを判断することができます。たとえば、CPLD がプライオリティの低い割り込みを受信しても、プロセッサを低消費電力状態からウェークアップさせる必要がないと判断した場合、CPLD はペンドイング割り込みを表示するレジスタを生成することができます。その後、プロセッサがウェークアップした際、割り込みペンドイング レジスタはマイクロプロセッサによって読み出されて処理されることになります。

CPLD を使用した典型的なバッテリ駆動デバイスで実現できる低消費電力（図 7）に対して、スタンドアロン マイクロプロセッサのデザインによる消費電力（図 6）を示します。CPLD に必要な電力は、マイクロプロセッサを長時間低消費電力モードに保持した際に得られる電力低減と比較すると、ごく僅かなものです。典型的な低消費電力 CPLD のスタンバイ電流は 100  $\mu$ A です。動作時の消費電力はアプリケーションとクロック周波数に依存します。16 ビットカウンタがいっぱいに配置された 64 マクロセルの CPLD を 50MHz のクロックで動作させると、ICC は約 10mA となります。実際に実現できる消費電力の量は、マイクロプロセッサの種類と CPLD のデザインを含むシステム全体のデザインに依存します。

CPLD を使うと電力が低減されるだけでなく、割り込み応答時間も短縮されます。ペリフェラル デバイスは、マイクロプロセッサがパワー セーブ状態からウェークアップするための時間を持つ必要はありません。この他電力を低減できる例を次に示します。

- ・プロセッサへの割り込み数を減らす

- ・長時間にわたりプロセッサのウェークアップ サイクル数を減らす

- ・スループットに影響を与えない範囲でクロック周波数を下げる

- ・データ処理動作ではプロセッサを低い周波数で動作させる

- ・データ収集動作では CPLD を高い周波数で動作させる

### 利 点

図 6 と 7 は、最先端の低消費電力

図6 - スタンドアローン プロセッサの消費電力

図7 - プロセッサとCoolRunner-II CPLD の消費電力

### 参考文献

インテル社『Intel StrongARM SA-1110 Microprocessor Developer's Manual』(2000 年 6 月)

モトローラ セミコンダクタ社 アプリケーション ノート『DragonBall Power Management』(1998 年)

ナショナル セミコンダクタ社『Geode GX1 Processor Series Low Power Integrated x86 Solution』(2000 年 10 月)

Turley Jim 著『Microprocessors for Consumer Electronics, PDAs, and Communications』

『Microprocessor Report』(1999 年 9 月)

『EDN Access, 27th Annual Microprocessor/Controller Report』(2000 年 9 月)

### 結 論

消費電力が問題となるアプリケーションをデザインする際は、電力管理用ソフトウェアの使用に加え、ハードウェアのデザイン手法も利用する必要があります。マイクロプロセッサを長時間低消費電力動作状態に保持できるよう低消費電力 CPLD でデザインすれば、システム消費電力の大幅な削減につながります。今日の市場で入手可能な最新 CPLD では、最終アプリケーションに対して、低消費電力と高速処理の柔軟な組み合わせが選択できます。

# Supporting Multiple SD Devices with CPLDs

## CPLD で複数の SD デバイスをサポート

CPLD を使用して SD マルチプレクサを生成

Mark Ng

Staff Applications Engineer, CPLD Applications

Engineering Xilinx, Inc.

[mark.ng@xilinx.com](mailto:mark.ng@xilinx.com)

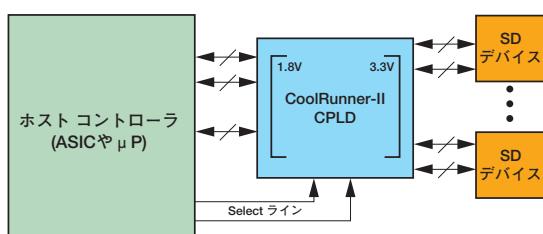

単一システムに複数の Secure Digital (SD) デバイスを追加したいという要望がますます高まってきています。しかし、Intel 社製 PXA270 や、TI 社製 OMAP、あるいは Qualcomm 社製 MSM プロセッサなどほとんどのデバイス／プロセッサは、1 個の SD インターフェイスしか提供していません。CPLD として知られている Complex Programmable Logic Device を使用すると、ホスト デバイスが SD デバイスをいくつでもサポートできるようになります。本稿では、スケーラブルで双方向

自動検出機能付きマルチプレクサ ベース デザインの詳細を説明します。

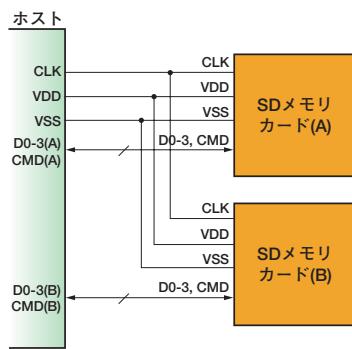

図 1 は、本来 1 個の SD インターフェイスしか持たないホスト デバイスに対して、複数の SD ポートを組み入れることができる CPLD 使用モデルを示します。CPLD は、ホスト コントローラと SD デバイスの間に配置されます。CPLD は双方向性のマルチプレクシングの機能を果たし、ホストが選択した任意の SD デバイスと通信を行えるようになります。もっと重要なこととして、このデザインには方向を制御するピンがありません。これは CPLD がデータの流れの方向を自動的に検出することを意味しています。

このインプリメンテーションは柔軟性に富みスケーラブルなため、SD ポート数を希望に応じて増減することもできます。また、定義された SD カードのモードや SPI、1 ビット、あるいは 4 ビットの各データ モードのいずれかをサポートします。

この種のアプリケーションに CPLD を使用する主な目的は、ホスト コントローラに SD ポートを追加することですが、二次的な利点として、ホストと SD カード間での電圧レベルの変換とロジックの分離が行えます。図 1 は、ホストが 1.8V で SD デバイスが 3.3V の場合を示します。業界の最新 CPLD では、スタンバイ電流は無視できるほど少なく、また動作時も超低消費電力を保ちます。従って、システムの電力にそれほどの影響を与えることはありません。

### SDA 仕様に準拠

SDA (Secure Digital Association) の仕様では、1 本の SD バスがサポートできるのは SD デバイス 1 個です。クロック ピンは共有できますが、DAT[3:0] と CMD ラインはすべての SD デバイスにユニーク

図1 - CoolRunner-II CPLD を使用して追加の SD ポートを提供

図2 - SD システム バスのトポロジ

なものでなければなりません。詳しくは図 2 をご覧ください。

図 2 のリファレンス デザインは SDA 仕様に完全に準拠しています。次のセクションで、シングル バスのコントローラで複数の SD デバイスをサポートしている場合、どのようにして前述の要件を満たすかを説明します。

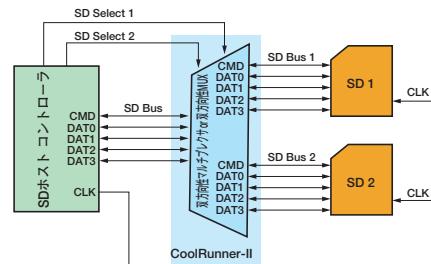

## CPLD デザイン

2 つの SD デバイスが同じ SD ホストインターフェイスを共有するこのデザインの、典型的な使用例を示すブロック ダイアグラムを図 3 に示します。概念的には、このデザインは双方向性マルチプレクサの形態を有し、そのようなものとして使用されます。ホストデバイスは Select 信号で CPLD を制御しますが、そこでどの SD と通信するかを伝達します。SD デバイスが選択されると、CPLD 内のロジックは自動的にデータの方向を検出し、それに従って(ホストから SD カードへ、あるいは SD カードからホストへのいずれか)データが流れるようにします。このデザインでは、方向制御ピンは必要がないため使い易くなっています。

ホストは各 SD デバイスに個別にアクセスできるため、マルチプレクサが適切に切り替えることにより他の SD の状態に影響を与えることはありません。CPLD は、ホストや SD がデータを駆動していないときは、システムをデフォルトの弱いプルアップしたハイ インピーダンス状態にします。この回路の主な目的はホストに追加の SD 機能を提供することですが、この回路は電圧レベル変換やロジックの分離にも使うこ

図3 - ブロック レベル ダイアグラム： 双方向性マルチプレクサ

とができます。

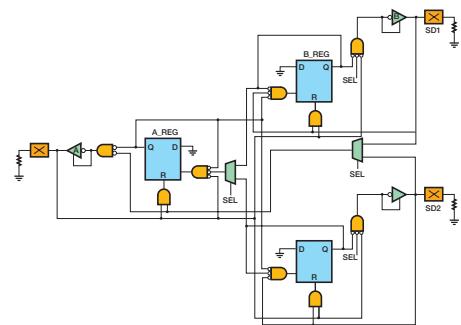

## インプリメンテーションの詳細

図 4 は、1:2 双方向性マルチプレクサ デザインの実際のロジック回路を示しますが、これは VHDL を用いて記述することができます。初期条件、すなわちアイドル状態では、ホストおよび SD カードは弱いプルアップのハイ インピーダンスである必要があります。したがって、図 4 の回路は CPLD の出力バッファが 3 ステートになるようデザインされており、それによって外部プルアップ抵抗が有効に動作します。レジスタ A (A\_REG) およびレジスタ B (B\_REG) は共に、パワーアップ時にロジック '0' に初期化されるようにデザインされています。

SD カードは CPLD への Select 入力を介して選択されます。Select がロジック '0' のときは SD1 が選択され、Select がロジック '1' のときは SD2 が選択されます。この回路の説明を簡易化するため、ホストを SD1 のみ選択して通信を行うものと仮定します。

このデザインの自動方向制御機能は次のようにしてインプリメントされます。処理は、ホストと SD1 デバイスの両方が Low のときに開始されます。たとえば、ホストが SD1 デバイスにデータを送信する場合、ホストは A 側を Low に駆動することから始めます。Low に駆動すると、回路のロジックが Low に変化するエッジを検出して B 出力バッファをイネーブルすることで応答しますが、A 出力バッファはディスエーブルのままに保ちます。厳密には、A が Low に駆動されたときに、立ち上がりエッジが A\_REG のクロック入力に送信されます。ク

ロッキングの後、A\_REG の Q 出力はロジック '1' になるため、B\_REG はクロックを受け取ることができなくなります。A\_REG がクロッキングされてトリガされると同時に、A が Low になったときにゲート B1 はロジック '1' を出力します。これが B 出力バッファをイネーブルし、最終的に、A に続いて B も Low に駆動されます。

逆に、それが Low から High に駆動されると、ゲート B1 は Low を出力して B 出力バッファを 3 ステートにします。これにより、B は外部プルアップ抵抗によって High に強制されます。A 側と B 側の両方が High になると、A\_REG と B\_REG は '0' にリセットされます。このプロセスが無限に繰り返されます。SD1 がデータを駆動してホストに送ろうと試みると、逆のことが起こります。また、ホストが SD2 デバイスとの通信を望む場合は、回路への Select 入力がロジック '1' に設定され、イベントのシーケンスは上記と類似のものとなります。

## デザインの検証

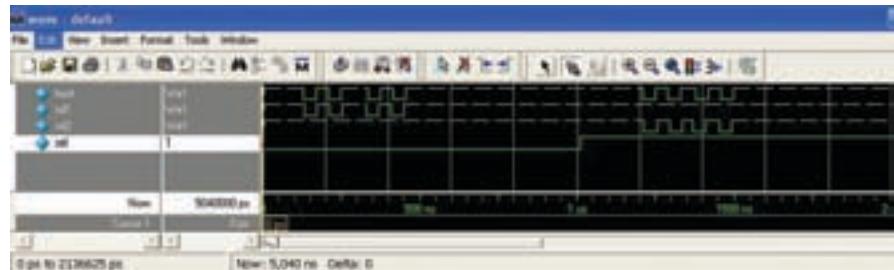

### シミュレーションの結果

この回路の機能シミュレーションとタイミングシミュレーションを、ModelSim を使って実行しました。テスト用のスティミュラスはリファレンス デザインに含まれています。図 5 にシミュレーションの結果の一部を示します。

図 5 では、Select 入力は Low に保持されています。白の破線は Week 1 状態、す

図4 - 2 つの DS デバイス用の SD マルチプレクサ回路

なわちブルアップ状態を意味しています。最初の処理で、ホストはデータを駆動して SD1 へ送ろうと試み、SD1 もそれに従います。その後に、SD1 デバイスがデータを駆動してホストへ送ろうと試み、ホストはそれに従います。Select 入力を Low に駆動すると類似のイベントが起こります。ホストはデータを駆動して SD2 デバイスへ送り、それから SD2 デバイスがデータを駆動してホストへ送ります。

### ハードウェアの結果

ザイリンクスは SD マルチプレクサのデモ ボードを作成し、このボードを使ってこの双方向性マルチプレクシング デザインを検証しました。図 6 にそのデモ ボードを示します。この ボード の 中 心 に CoolRunner™-II XC2C32A CPLD が実装されています。2 個の SD カードソケットがボードの上部エッジに沿って配置されています。ボードの最も下の部分は、SD カードの物理的寸法を模倣するようにデザインされています。図 7 は、デモボードを USB SD カードリーダに差し込んだ様子を示します。期待通り、XC2C32A によって PC は第 1 と第 2 の SD カードと完璧に通信することができました。

### デバイスの利用率

表 1 は、各種のインプリメンテーションに対するデバイスの利用率を示します。SDA 仕様のところで述べたように、SD カード用に 3 つの信号モードが定義されています。それは、SPI モード、1 ビット SD データ転送モード、および 4 ビット SD データ転送モードです。このデザインは、どのモードにも容易に適合することができます。このデザインでは、SD 拡張ポートをいくつでも対応できますが、デフォルトの VHDL コードでは 2 ポートに設定しています。

### 電圧と電流の考察

SDA 仕様には、SD カードに対する厳密な電圧と電流の要件が含まれています。プログラマブル ロジック デバイスは、超低消

図5 - シミュレーションの結果

費電力で I/O バンキングのような機能を備えているため、このアプリケーションには理想的といえます。I/O は、1.5V や 1.8V、2.5V、3.3V にコンフィギュレーションできるため、どの SD デバイスにもインターフェイスできます。CPLD にも I/O バンクが備わっているため、プロセッサと SD カードの間で電圧変換機能を果たすことができます。

最新の CPLD はそもそもが非常に低消費電力で、スタンバイ動作の消費電流では 15  $\mu$ A と小さくなっています。そのため、低消費電力 CPLD をシステムに追加しても、消費電流への影響は最小限に抑えられます。

### VHDL ダウンロード

これらのデザインは、VHDL ファイルをザイリンクスの Web サイトより入手してコンパイルおよびシミュレーションすることができます。詳細は [http://japan.xilinx.com/products/silicon\\_solutions/cplds/resources/coolvhdlq.htm](http://japan.xilinx.com/products/silicon_solutions/cplds/resources/coolvhdlq.htm) をご覧ください。

### 結 論

SD デバイスの人気が高まるにつれ、ホストコントローラでの 1 個以上の SD デバ

図6 - ザイリンクス SD マルチプレクサ デモ ボード

図7 - USB SD カード リーダに差し込んだザイリンクス デモ ボード

イスのサポートの必要性も増えることになるでしょう。この記事では、目前の問題に対する検証済みのソリューションを提供しています。このソリューションにより、1 個のシステム内に 2 個あるいはそれ以上の SD デバイスをインプリメントする柔軟性が提供されます。 ● ● ●

表1 - 各種のインプリメーションに対するデバイスの利用率

| SD 拡張ポートの数 | デバイス    | マクロセルの利用率<br>(SPI あるいは 1 ビットデータモード) | マクロセルの利用率<br>(4 ビットデータ転送モード) |

|------------|---------|-------------------------------------|------------------------------|

| 1          | XC2C32A | 13 マクロセル数                           | 19 マクロセル数                    |

| 2          | XC2C32A | 21 マクロセル数                           | 30 マクロセル数                    |

| 3          | XC2C64A | 27 マクロセル数                           | 39 マクロセル数                    |

# A High-Speed Broadcast Video Connectivity Solution

## 高速ブロードキャスト ビデオコネクティビティソリューション

ザイリンクス Spartan-3E と Spartan-3A FPGA、NS 社の Smart SERDES、およびザイリンクス プロトコル スタックにより、SD や HD、3G-SDI 向けマルチレート ブロードキャストの課題に費用対効果が高く柔軟性の高いアプローチを提供

Bob Feng

Spartan Applications Engineer

Xilinx, Inc.

bob.feng@xilinx.com

Mark Sauerwald

SDI Applications Engineer

National Semiconductor

mark.sauerwald@nsc.com

今日の高速ビデオ アプリケーションの設計者は、デジタル IP コアとアナログ物理インターフェイスの両方をデザインする際にかなりの困難に直面しています。デジタルおよびアナログ コンポーネントにはそれぞれ異なる要件が求められる場合があり、1 個の ASSP チップで両方をサポートするには、ソリューションの品質と費用対効果の点で妥協せざるを得ない場合があります。複数の標準規格に合わせるために、無駄な領域が少なく高い柔軟性を維持した、正確な IP コアと物理インター

フェイスのソリューションを探すのは非常に困難です。

ザイリンクスと National Semiconductor 社（以下 NS 社）が共同で開発した新しいチップ セットは、デジタル世界とアナログ世界のベストを組み合わせて、高度に統合化されたソリューションを提供しています。プロトコル スタックも含んでいるこのソリューションは、Spartan®-3E および Spartan-3A FPGA で実現されています。アナログの部分は、NS 社の SDI 製品ファミリで実現されており、信号品質に優れまたジッタも非常に少なくなっています。業務用のオーディオ／ビデオ／ブロードキャスト (AVB) システムの開発者は、これらソリューションを使用することで、フロントエンドのインターフェイス コネクティビティの設計に手をとられることなく、彼らが専門とするビデオコンテンツ処理の機能性や IP コアの開発に専念することができます。

### SDI ビデオ標準

シリアル デジタル インターフェイスの SDI [SMPTE-259M] はブロードキャスト業界の標準で、圧縮されていない標準品 (SD) ビデオ信号を 1 本の同軸ケーブルで送信するのに、今日広く使われています。SDI は、定義上、データ レート 270Mbps をサポートし、480i のスクリーン フォーマットを 60Hz でカバーします (480i60)。

高品位 (HD) SDI の HD-SDI [SMPTE-

表1 - FPGA デザインの周波数領域

|        | ソフトSERDES | ピクセル処理    |

|--------|-----------|-----------|

| SD-SDI | 27 MHz    | 27 MHz    |

| HD-SDI | 148.5 MHz | 74.25 MHz |

| 3G-SDI | 297 MHz   | 148.5 MHz |

292M]、は最大ビット レート 1.485 Gbps を誇り、720p60 や 1080i60 の高品位フォーマットをサポートしています。

3 ギガビット SDI の 3G-SDI [SMPTE-424M] は、さらにシリアル デジタルのスループットを 2.97Gbps まで広げ、これは最も高いスクリーン解像度、1080p60 に対応しています。

## NS 社の SDI

NS 社は、SDI アプリケーションと関連ビデオ クロック (タイミング) 用に物理層送信をサポートする製品ポートフォリオを提供しています。NS 社の Smart SERDES は、SDI シリアライザとデシリアライザの新しいファミリで、スピードグレード オプションとしては、270Mbps の SD SMPTE 259M、1.485Gbps の

HD SMPTE 292M、および 2.97Gbps の新しい 3Gbps 標準 (3G-SDI) SMPTE 424M をサポートしています (表 2)。

NS 社の LMH0340 と LMH0341 は業界最先端のアナログ性能として以下を提供しています。

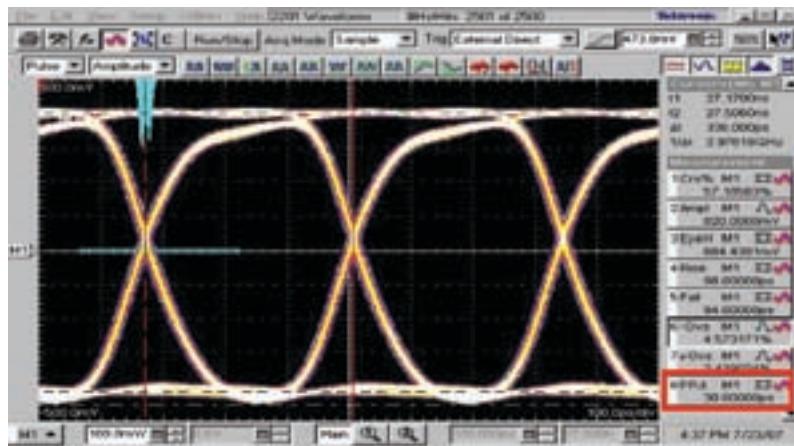

- ・ HD と 3Gbps レートでティピカル値 50ps の超低出力ジッタ (図 1)

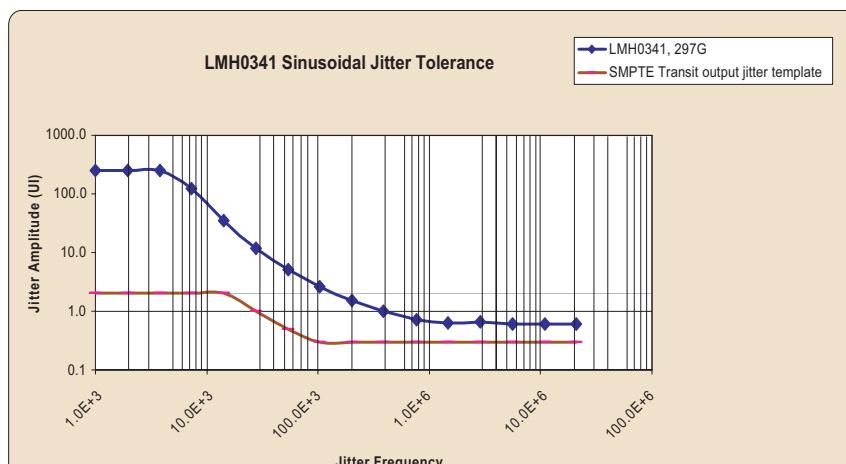

- ・ 最小 0.6 UI の優れた入力ジッタ トレランス (図 2)

- ・ シリアル クロック リファレンスとデータリカバリに統合された高精度 PLL

- ・ LMH0340 トランスマッタ内の統合されたケーブル ドライバ

- ・ 統合されたシリアル リクロックド ループスルーとドライバ

- ・ 低消費電力

- ・ TX : 420mW

- ・ RX : 590mW

- ・ 外部 VCO やクロック クリーニングが不要

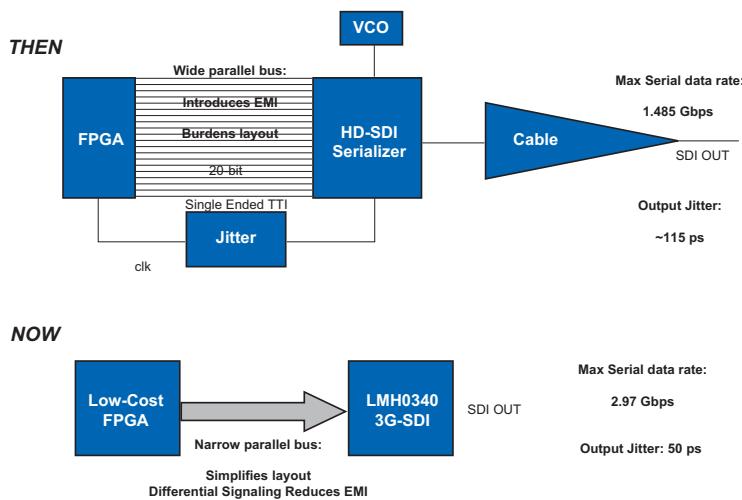

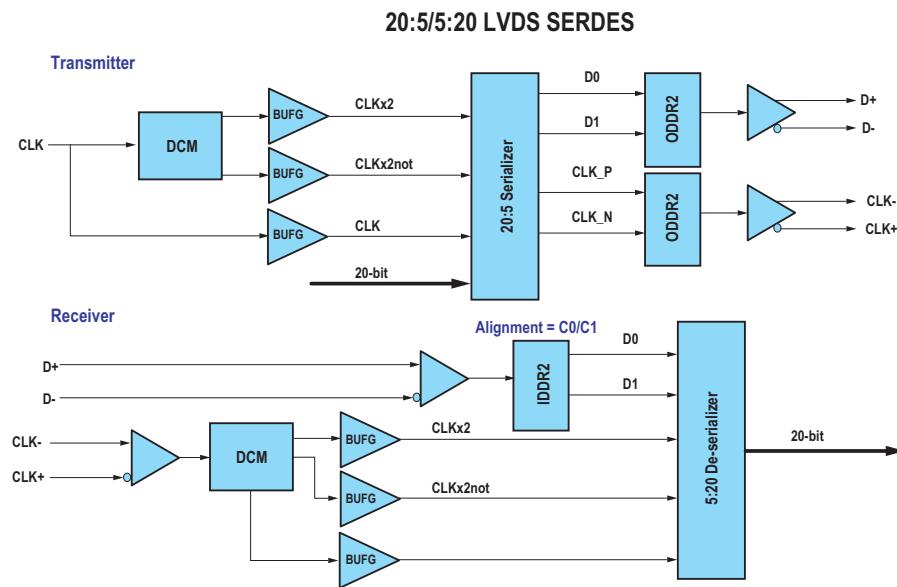

NS 社の Smart SERDES ファミリは、最先端のアナログ性能に加え、PHY (シリアルライザあるいはデシリアルライザ) とホスト FPGA 間の従来のパラレル バスを、20 ビット シングルエンド インターフェイスから 5 チャネル低電圧差動信号 (LVDS) インターフェイスに減らしています。この革新的な狭い差動バスは EMI を低減しており、また、インターフェイス上のトレースの本数を削減し、ホスト FPGA での使用ピンを減らすことでボード レイアウトを簡素化しています。さらに、NS 社のディスクリートのシリアルライザとデシリアルライザは、外部 VCO やジッタ低減用 PLL を必要としません (図 3)。

NS 社およびザイリンクス Spartan が統合ソリューションにより、業務用のビデオ アプリケーション用の SD や HD、3Gbps データ レートをサポートするハイエンド AVB 市場において、低コストでの FPGA の導入を可能にしています。

## ビデオ アプリケーションで使用される Spartan の機能

Spartan-3E と Spartan-3A FPGA フ

図1 - LMH0340 による 3Gbps 出力の整合ジッタ : 30ps

図2 - LMH0341 の最小入力ジッタ トレランス : 0.6UI

図3 - SDI 部品点数の削減

図4 - Spartan-3E FPGA 内の基本的なソフト SERDES の構成概念

アミリは、高性能、高集積度（ロジックとI/O）、高い柔軟性、およびスケーラビリティなどを提供しており、ビデオ アプリケーションで求められるさまざまな要求に応えます。Spartan FPGA が提供するユニークで費用対効果の高い機能は次のとおりです。

- ・システムゲート数 50,000～1,600,000

- ・動作スピード 666Mbps 以上で、チッ

プ ツー チップ間の直接通信用レシバ側の内部ターミネーションを持つLVDS 差動 I/O

- ・動作スピード 300MHz 以上で、実質 バンド幅を 600Mbps 以上に増大するダブル データ レート (DDR) I/O レジスター

- ・動作スピード 200MHz 以上で、FIFO とデータのバッファリングに使用可能な 18Kb デュアルポート ブロック RAM

- ・高速デジタル信号処理用の動作スピードが 200MHz 以上の専用 18 X 18 の乗算器

- ・デジタル クロック マネージャ (DCM)

- ・クロックのスキュー除去

- ・周波数合成

- ・高分解能のフェーズ シフト機能

- ・広い周波数レンジ (5MHz～300MHz 以上)

- ・フルにプログラミングが可能なため開発やフィールドでデザインの変更が容易、またシングル ソリューションで複数の標準をサポート

- ・ソフトウェアと IP コアを使い、ビデオ アプリケーションの重要な機能を迅速にインプリメント

- ・デザイン例やリファレンス ボードを使って迅速なスタートが可能

FPGA を使用すれば、業界標準に準拠した製品開発ができ、また競合他社との差別化を図ることができます。このような差別化は、ASSP ソリューションでは実現が困難で、ASIC では非常に高額になります。プログラマブル ソリューションの柔軟性により製品の Time-to-Market が短縮され、また、フィールドでのアップデートが可能になるため、製品を市場に長くとどめることができます。送信スキームや MPEG プロファイル、ディスプレイ フォーマット、カラー訂正などのデザインには、標準（およびバージョン）が無数に存在するため、柔軟性が必要となります。

## インターフェクト ソフト SERDES とプロトコル スタック

NS 社の Smart SERDES やイコライザ、ケーブル ドライバは SDI 物理インターフェイスを管理していますが、FPGA はプロトコル スタックですべてのデジタル ファンクションをサポートするという必要不可欠の役割を担っています。それに次のようなものが含まれます。

- ・20:5:5:20 LVDS ソフト シリアル化ゼーションとデシリアル化ゼーション (SERDES)

- ・SMPTE スクランブリング／デスクラ

## ンプリング

- ・ビデオのフレーマー／デフレーマー

- ・CRC とライン番号挿入

- ・ラストライゼーション

- ・ANC 挿入

- ・ビデオ標準の検出とフライホイール

FPGA のデザインは、表 1 に示すよう 「ソフトSERDES」と「ピクセル処理」で、実質的には 2 つの周波数領域に分けられます。ソフト SERDES で使用されるクロック周波数は DDR 手法を利用してい るため、一般的にシリアライゼーション ビット レートの半分ですみます。一方、ピクセル処理のクロック周波数は、関連するビデオ送信フォーマットによって決定さ れます。すなわち、720p60 に対しては 74.24MHz、1080p60 に対しては 148.5MHz です。

タイミング クロージャの課題は、主にソフト SERDES 側に生じます。それは、差動チャネル全体で 594Mbps を実現し ようとした場合 297MHz の動作が必要 になるためです。ザイリンクスの Spartan アプリケーション チームは、2007 年 5 月から β バージョンでこのソ フト SERDES リファレンス デザインを 提供してきました。以来ザイリンクスおよび NS 社は、広範なテストを実施してき ました。3 つのデータ レートはすべて、ザイリンクスが開発した BERT テスト ス イートに合格しました。図 4 は基本的な SERDES の構成概念を示します。

ザイリンクスには、Virtex® ファミリ FPGA で SDI インターフェイスをサポー トしてきた長い歴史があります。ザイリンクスのアプリケーション ガイド「放送業 界用オーディオ／ビデオ接続ソリューショ

ン (XAPP514)」は、ビデオ コネクティ ビティ IP コアとリファレンス デザインに 関するもので、プロトコル スタックに 関する詳細を、SDI や HD-SDI、DVB-ASI、 SDTV/HDTV テスト パターン生成から、 エンベデッド オーディオにいたるまで、 説明しています。ザイリンクスおよび NS 社は、これらの価値あるリファレンス デザインを Spartan-3E と Spartan-3A FPGA に移植しようと積極的に作業を 進めています。

## ■ ターゲットアプリケーション

ザイリンクスの低コストソリューショ ン、Spartan-3 ジェネレーション FPGA は、広範囲の民生および業務用のビデオ アプリケーションに採用されてきました。 代表的なものとして、Spartan-3E FPGA を使用した JVC 社の業務用ブロードキャ 斯ト HDV カメラ／レコーダがあります。 デジタル ロジック用の Spartan FPGA とアナログ インターフェイス用の NS 社 の Smart SERDES の組み合わせは、業 務用のビデオやブロードキャスト、デジタ ル シネマなどのハイエンド アプリケーシ ョンに新しい可能性の道を開きます。適用 可能な製品としては、高品位ビデオ カメ ラやデジタル ビデオ レコーダ、ビデオ エ ディタ、ディスプレイ モニタなどが挙げ られます。

## ■ 結 論

ザイリンクス Spartan-3E と Spartan-3A FPGA の機能は、NS 社の 実証済み SD/HD/3G-SDI Smart SERDES および XAPP514 リファレンス IP コアと組み合わせることで、ブロードキャスト ビデオ アプリケーションのデータ スループットへ高まる要求に対して 費用対効果の高いソリューションを提供 します。ハードウェア ソリューションはす べて現在利用可能です。また、ザイリンクス の販売代理店である アヴネット 社では 2008 年の第二四半期に SDI 評価キット を提供する予定です。

表2 - National Semiconductor 社の Smart SERDES ファミリ

| 製品番号    | 詳細              | 最大 データレート | サポートされている データレート        | サポートされている SMPTE標準    |

|---------|-----------------|-----------|-------------------------|----------------------|

| LMH0340 | シリアライザとドライバ     | 3G        | 2.97G<br>1.485G<br>270M | 424M<br>292M<br>259M |

| LMH0341 | リクロッキング デシリアライザ | 3G        | 2.97G<br>1.485G<br>270M | 424M<br>292M<br>259M |

| LMH0040 | シリアライザとドライバ     | HD        | 1.485G<br>270M          | 292M<br>259M         |

| LMH0041 | リクロッキング デシリアライザ | HD        | 1.485G<br>270M          | 292M<br>259M         |

| LMH0050 | シリアライザ          | HD        | 1.485G<br>270M          | 292M<br>259M         |

| LMH0051 | デシリアライザ         | HD        | 1.485G<br>270M          | 292M<br>259M         |

| LMH0070 | シリアライザとドライバ     | SD        | 270M                    | 259M                 |

| LMH0071 | リクロッキング デシリアライザ | SD        | 270M                    | 259M                 |

# Developing FPGA Coprocessors for Performance-Accelerated Spacecraft Image Processing

## 宇宙船画像処理の高性能化を実現する FPGA コプロセッサの開発

C-to-FPGA デザイン手法で宇宙ベースの画像処理アプリケーションの開発を加速

Paula J. Pingree

Senior Engineer

Jet Propulsion Laboratory, California Institute of Technology

[paula.j.pingree@jpl.nasa.gov](mailto:paula.j.pingree@jpl.nasa.gov)

Lucas J. Scharenbroich

Staff Engineer

Jet Propulsion Laboratory, California Institute of Technology

[luca.j.scharenbroich@jpl.nasa.gov](mailto:luca.j.scharenbroich@jpl.nasa.gov)

Thomas A. Werne

Associate Engineer

Jet Propulsion Laboratory, California Institute of Technology

[thomas.a.werne@jpl.nasa.gov](mailto:thomas.a.werne@jpl.nasa.gov)

David Pellerin

CTO

Impulse Accelerated Technologies

[david.pellerin@impulsec.com](mailto:david.pellerin@impulsec.com)

画像データをオンボードで高速かつ正確に分類することは、現代衛星画像処理においてクリティカルな課題です。地球科学やその他アプリケーションにおいては、空間をベースにしたスマートな観測機器は、インテリジェントな機械学習アルゴリズムと自立計器を利用して、洪水や火山噴火、海面の氷崩落などの自然現象を検出して特定します。

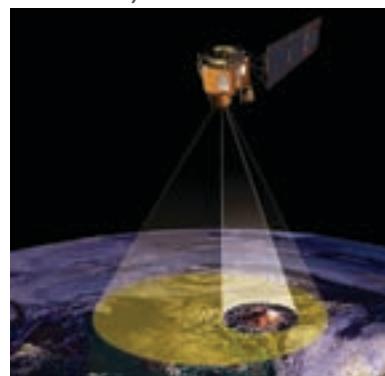

米航空宇宙局 (NASA) のジェット推進研究所 (JPL) は、サポート ベクタ マシン (SVM) 分類アルゴリズムを開発しました。このアルゴリズムは宇宙船から優先度の高い画像データを特定して地上にダウンリンクするために使用されます。また、船内のデータ解析にも使われ、ダイナミックな出来事への迅速な対応を可能にします (図1)。これらのオンボード分類器は、地上にダウンロードするデータ量の削減を支援し、計測器の科学的価値を大幅に増やします。

SVM 分類アルゴリズムは今日既に使用されており、RAD6000 や Mongoose V プロセッサのような計算用プラットフォームを使用しています。これらの従来型プロセッサの計算能力には限界があり、またアクティブなストレージ機能が極端に制限されているため、もはや最先端のものとはいえないません。そのため、オンボード分類は、全計測データのサブセットにのみ実行できる最も簡単なファンクションだけに限定されてきました。たとえば、EO (Earth Observing : 地球観測) -1 衛星に搭載されている Hyperion 計測器の場合、242 バンドのうち 11 にのみ適用されています。

FPGA コプロセッサは、これらのアルゴリズムにとって理想的です。FPGA は、現在使用されている従来型処理プラットフォームと比較した場合、オンボード分類の性能と精度において大幅な改善を実現します。

FPGA の SVM アルゴリズムに対する効果を評価するため、Hyperion 計測器用に開発された従来型 SWIL (snow-water-ice-land : 雪-水-氷-陸) 分類器を、ザイリンクス Virtex®-4 FX60 FPGA にインプリメントしました。また、アプリケーションをより迅速に開発できるよう、Impulse Accelerated Technologies 社の Impulse C-to-FPGA コンパイラ ツールを利用しました。このツールは、高度にパラレルなハードウェア アルゴリズムとアプリケーションの迅速な開発をサポートします。

本稿では、Hyperion リニア SVM を Virtex-4 FX60 FPGA にインプリメントした手法に加え、より高いデータバンドとより精緻な SVM カーネルを使用して行った実験について説明します。これらの実験により、FPGA エンベデッド アルゴリズムを

使用することで、より効率的、かつ、高性能のオンボード分類器を実現できることが示されました。

## FPGA でオンボード計算

空間をベースとした先進の科学的エンジニアリング アプリケーションにとって、オンボード計算処理はかなりのボトルネックになっています。現在利用できる宇宙船向けのプロセッサは、消費電力が高く高価で、追加のインターフェイス ボードが必要になったり、計算能力に制限があったりします。

ザイリンクス Virtex-4 FX デバイスのような最近のハイブリッド FPGA は、リコンフィギュラブルなハードウェア リソースを利用できるという特性を活かしつつ、さまざまなソフトウェア アプリケーションのエンベデッド プロセッサでの実行を、すべて

シングル チップで提供しています。この緊密に結合されたシングル チップのハードウェア／ソフトウェア システムは、汎用シングルボード コンピュータ (SBC) と比較して、より低い電力とより低いコストでの実現が可能です。FPGA プラットフォームは、放射線対策をした SBC よりも飛躍的に性能が優れており、スマート観測機器にまったく新しいアーキテクチャを導入できます。

FPGA による加速化の可能性を評価する目的で特定のスマート観測機器の概念を検証するため、ザイリンクスの ML410 評価用プラットフォームを使用しました。ザイリンクス ML410 評価ボードは、2 個のエンベデッド PowerPC® 405 プロセッサと豊富な FPGA ロジックを搭載した Virtex-4 FX60 FPGA を装備しています。

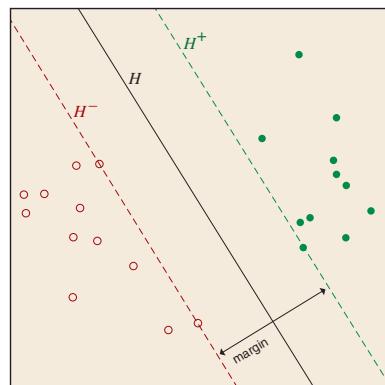

この検証には、SVM 分類アルゴリズムを使用しました。この種のアルゴリズムは、一般的な機械学習や分類タスク、オンボード遠隔検知などの広範なアプリケーションの礎を築いてきました。SVM は、2 つのラベル付けされたクラス間の分離超平面を、それぞれのクラスのもっとも近いデータとの距離が最大になるように計算する最大マージンの分類器です。(図2)。SVM 分類器はこのような最大マージン超平面を選択することで、他のリニア分類手法よりも新しいデータをより一般化できます。

SVM をトレーニングする目的は、トレーニング データ  $x_i$  とテスト ベクタ  $-t$  との重み付けされたドット積の総和の符号が新しいデータ ベクタのクラスを正確に予測できる加重を突き止めることです。

SVM はまた、カーネル トリックとして知られている、純粋にリニアな分類器からノンリニアな分類器に拡張する手法に対応しています。この手法は、トレーニングとテストのアルゴリズムをドット積で公式化し、その後、引数をあるノンリニアなファンクションに通した新しいドット積を表すカーネル ファンクションで置き換えます。このカーネル ファンクションは、オリジナルの低次元空間からの項を使用して、高次元 (あるいは無限次元も可能) のドット積をノンリニアな空間で計算することができます。

SVM はオンボードの自立アプリケーションに非常に適しています。それは、アル

図1 - NASA はスマート観測機器を使用して地表画像データを分類し、ダウンロードするデータ量を低減 (NASA 提供画像)

図2 - SVM を使用して分離超平面を計算: 円形のデータ ポイントはマージン上に横たわるサポート ベクタ

ゴリズムのトレーニング ステージでの計算量とテスト ステージでの計算量の非対象性という SVM の特性によります。新しいデータ ポイントを分類するのに必要な計算量は、トレーニングをする際の計算量よりも数桁少なくなりますが、これは、SVM をトレーニングするプロセスが 二次の最適化問題を解く必要があるためです。

SVM のトレーニングには  $O(n^3)$  オペレーションが必要で、ここでの  $n$  はトレーニング例の数を示します。これとは対照的に、トレーニングされた SVM で新しいベクタをテストするには、 $O(n)$  オペレーションだけが必要です。SVM 最適化問題のある特定の構造を利用した高速トレーニング アルゴリズムは存在しますが、それでもトレーニングは計算上の主なボトルネックになっています。

SVM をトレーニングした後は、多くの加重、 $w_i$  はゼロになります。これは、これらの項を分類公式内で無視してよいことを意味します。ゼロでない加重を持つ入力ベクタはサポート ベクタと呼ばれます。利用可能な CPU リソースの量に厳しい制限があるため、サポート ベクタの数を減らすことが、宇宙船のオンボードで SVM 分類器を展開させる成功の鍵となります。

これまで展開してきた分類器は、このような縮小セット手法を使用してきましたが、それでも利用できる分類特性のサブセットしか操作できないという制限があります。このようなボトルネックを取り除くことが、オンボード自立ツールとしての SVM の可能性を完全に実現することになるのです。

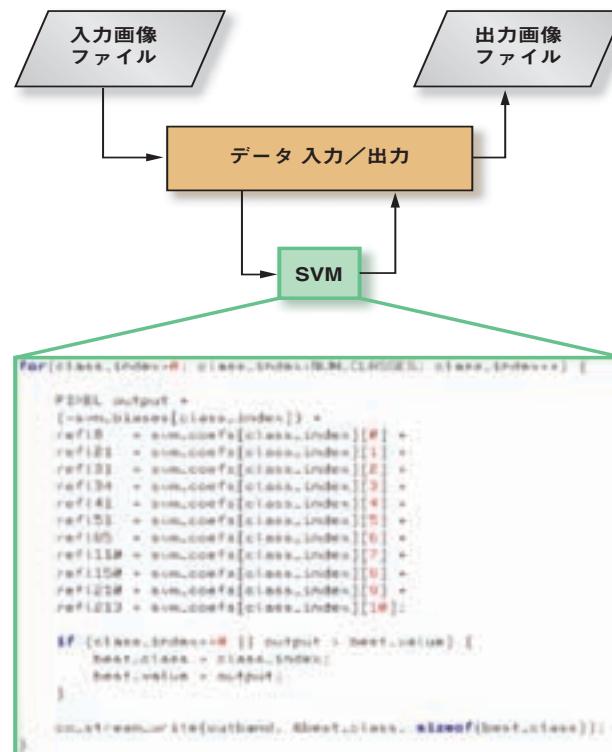

## 問題点の分割

エンベデッド プロセッサを搭載した FPGA を使用して高性能を達成しようとした場合、ソフトウェアとハードウェア間でアルゴリズムの効率的な分割が重要となります。FPGA ベースの SVM を開発するにあたり、以前はソフトウェアだけで行われていたアルゴリズムを FPGA ハードウェア ファブリックにインプリメントして、FPGA の高速パラレル処理能力を利用しました。画像ファイル入力と分類ファイル出

図3 - SVM アルゴリズム用のソフトウェア／ハードウェアの分割

ロセッサと SystemACE™ インターフェイス コントローラおよび UART ペリフェラル間のデフォルト インターフェイスとしての役割を担っています。

Impulse ツールは、このような分割されたソフトウェア／ハードウェア アプリケーションをサポートするために、プロセス ツー プロセス通信手法をインプリメントできる C と互換性のあるファンクションのライブラリを含んでいます。これらの手法には、ストリーミングやメモリ共有、メッセージの伝達などが含まれます。このアプリケーションでは、Impulse C のストリーミングプログラミング モデルが明白な選択肢となりました。

Impulse C のストリーミング アプリケーションでは、ハードウェアとソフトウェアの各プロセス間の通信は主に、直接ハードウェアでインプリメントされたバッファ データ ストリームを介して行われます。このデータのバッファリングにより、比較的抽象化レベルの高いパラレル アプリケーションを書くことが可能になります。この際、バッファリングをしない場合に通常必要とされるサイクルごとの同期は不要です。

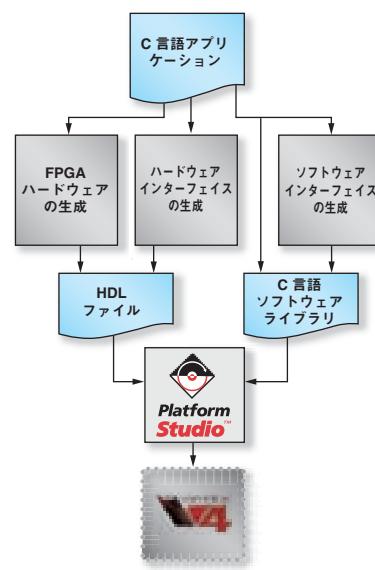

図 4 は、ザイリンクス Virtex-4 FX60 FPGA をターゲットとして使用する際の、C からハードウェアにコンパイルするためのデザイン フローを示しています。

アプリケーションのソフトウェア側では（この場合 PowerPC 405 プロセッサは、ハードウェア レベルのテストに使用されます）、Impulse C ファンクションを使用して、データ ストリームをオープン／クローズし、ストリーム上のデータの読み書きを行い、必要に応じてステータス メッセージを送ったり結果をポーリングしたりします。Virtex-4 FX の場合、ストリームの読み書きは、PLB あるいは補助的ペリフェラルユニット (APU) インターフェイスのいずれかを利用的操作として指定できます。

## パラレル FPGA ハードウェアの生成

このアプリケーションのハードウェア部分を生成するのに、Impulse C コンパイラを使用して、ザイリンクス EDK ツールで

使用できる合成可能な HDL ファイルを生成しました。Impulse コンパイラは、HDL ファイルの生成に加えて、EDK ツールが必要とする PLB や APU バスインターフェイスを含むファイルも生成します。Impulse C コンパイラは、C ステートメントのスケジューリングやループのパイプライン化など、各種の下位レベルの最適化を行い、アプリケーション開発者に大幅な時間の節約をもたらします。

Impulse C コンパイラはこれらの最適化を実行し、VHDL や Verilog 形式でハードウェアを生成します。このハードウェアは、ザイリンクス ISE® ソフトウェアや Platform Studio などの FPGA ツールを使って合成できます。プロセッサ側では、コンパイラがエンベデッド PowerPC プロセッサで使用できるランタイム ライブラリを生成します。

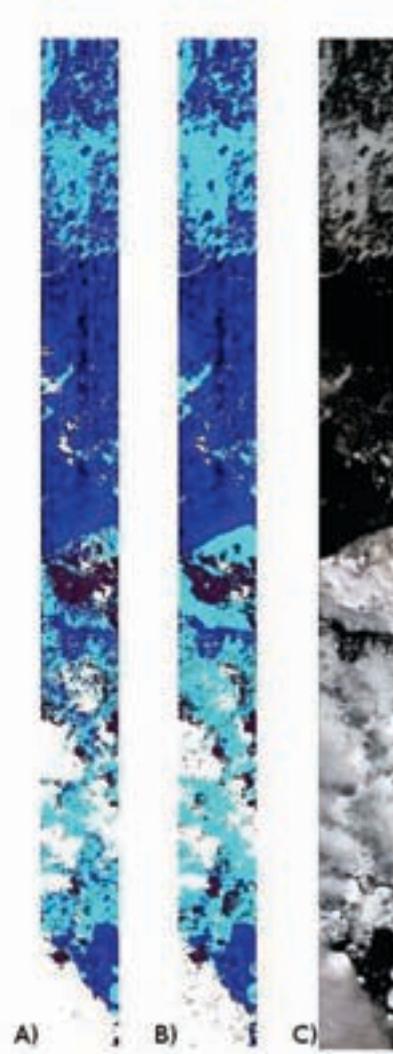

## アルゴリズムの立証

ソフトウェア／ハードウェアを組み合わせたアプリケーションの出力は、画像中の各ピクセルの結果として得られたクラスを示す整数のコラムで構成されたファイルです。実験の結果を立証しその結果を見るために、MATLAB を使用して整数値のコラムを再フォーマットし、オリジナルのピクセル類似次元の画像にしました。各クラスには任意の色が割り当てられ、各クラスに属するピクセルの数を平面に表しました。そうすることで、各クラスに所属するピクセルのパーセンテージを容易に計算でき、また、分類されたピクセルの結果ファイルはカラー画像で視覚化されます。

この立証には、このプロジェクトの 2 つの目標を満たす必要がありました。最初に、ソフトウェアのみの従来型バージョンの SVM から得られたピクセル分類結果と、ハードウェアを生成してインプリメントされた SVM から得られたピクセル分類結果の両方を立証する必要がありました。これは、ハードウェアである FPGA で行われた整数と浮動小数点の計算結果が、現在使用されているソフトウェアで計算されたものと、一定の許容範囲内で同じ結果であったことを立証するために必要でした。

この検証で得られたピクセル分類のパーセンテージ結果を、現在飛行中の EO-1 衛星で使われている SVM によって報告されたものと比較することから立証プロセスを開始しました。分類パーセンテージは、特に雪と水のクラスで、良く一致しました。

この作業では、画像の視覚化も重要でした。この視覚化の結果得られたものは、EO-1 からの結果とすばらしく良く一致しました（図 5）。

画像の定性的な比較に加えて、従来アルゴリズムの結果と我々の分類との間で、ピクセルごとの比較を実行しました。ピクセルごとに分類を比較した結果、我々が得たピクセル分類の結果の 76.8% が Autonomous Sciencecraft Experiment (ASE) からのものと一致しました。残りの不一致の部分は、SVM のトレーニング データ セットの違いによって引き起こされたものと推測されましたが、念のためハードウェア インプリメンテーションをピクセルバイピクセルベースで検証することにしました。

アルゴリズムを完全に立証するのに、同じ入力データを使用した際の、ソフトウェア インプリメンテーションの出力と、Impulse C コンパイラでハードウェアにイ

図4 - C コードから FPGA エンベデッド アプリケーションへのデザイン フロー

## 図5 - 結果の比較

- a) 従来型 11 バンド SVM インプリメンテーション

- b) FPGA 加速化インプリメンテーション

- c) オリジナルのハイパースペクトル画像

[カラー コード、青 = 水、青緑 = 氷、濃い紫 = 雪、薄紫 = 分類不可]

ンプリメントした場合の出力とを比較しました。この 2 つのインプリメンテーションは、ピクセル バイ ピクセル ベースで等価な分類を生成しました。我々の結果が従来型 ASE の結果と良く一致したことと、ソフトウェア プラットフォームからの独立した結果を考慮して、我々のインプリメンテーションは正当なものであったといえるでしょう。これらすべての立証は、C 言語と MATLAB プログラミング手法の組み合わ

せで行われ、ハードウェア デザイン手法やハードウェア記述言語の必要はありませんでした。

## アルゴリズムの拡張

Hyperion のためにデザインされた従来型 SVM のインプリメンテーションに成功した後、C 言語アルゴリズムに 2 つの拡張を行いました。それは、同じリニア カーネル SVM でバンド数を大幅に増加させたことと、ノンリニア カーネルの新しい SVM を生成したことです。拡張されたリニア カーネル SVM に対して、画像で利用できる 242 のバンドの中から任意に 30 バンドを選択しました。ノンリニア カーネル SVM に対しては、従来型 SVM と同じ 11 バンドを使用しましたが、カーネルは変更されたものを使いました。オリジナルの従来型 SVM に対するトレーニング データがなかったため、それと比較できる新しい SVM を生成できませんでした。そこで、新しいトレーニング データを使用して 2 つの新しい SVM を生成することにしました。また、従来型 SVM と比較するために、新しい 11 バンドのリニア カーネル SVM も生成しました。

C からハードウェアへ変換するコンパイラを使用することで、これらの代替インプリメンテーションをすばやく実験し、精度と性能を比較することができました。これらの SVM のハードウェア インプリメンテーションはアルゴリズムのソフトウェア シミュレーションと非常によく一致する結果を生成し、システム全体の性能の大幅な向上が実証されました。

ザイリンクスの合成ツールを使用して、これら SVM の各 FPGA ファブリックの利用パーセンテージを確認することもできました。

## 結 論

エンベデッド プロセッサを搭載した FPGA は、従来のプロセッサでは不可能であった性能と効率性において実証レベルに達しています。SVM アルゴリズムのハードウェアによる加速化は、将来の科学的ミッションにおいて、オンボード データ処理が大幅に改善されることを約束してくれます。

Virtex-4 FX60 デバイスなどのエンベデッド FPGA を使用すれば、ますます進んだ SVM を「成長の余地を残しながら」オンボードのリソースだけでインプリメントすることができます。我々の得た結果は、Virtex-4 FX-60 FPGA で利用できる DSP ブロックとスライスの 1/3 を使うだけで、最も高度な SVM 拡張、すなわち多項式カーネルでさえ実現が可能であることを実証しています。

ソフトウェアからハードウェアへの変換用デザイン ツールは、これらの SVM アルゴリズムをすばやくプロトタイピングして開発する上で重要な役割を果しました。Impulse C ツールにより、アプリケーションの複雑性を容易に管理でき、また代替インプリメンテーションの実験も行うことができました。テストとアルゴリズムの立証には、ザイリンクス ML410 ボードを使用したことによって、優れた費用対効果の高い開発ターゲットが得られました。 ●

表1 - FPGA ベース SVM アルゴリズムのデバイスの利用率

| FPGA リソース       | V4FX60 での総数 | リニア (11 バンド) | リニア (30 バンド) | (2,1) 多項式  |

|-----------------|-------------|--------------|--------------|------------|

| スライス数           | 25,280      | 1,151 (4%)   | 2,253 (8%)   | 2,082 (8%) |

| スライス フリップ フロップ数 | 50,560      | 1,290 (2%)   | 1,337 (2%)   | 2,519 (4%) |

| 4 入力 LUT 数      | 50,560      | 1,838 (3%)   | 3,110 (6%)   | 3,287 (6%) |

| FIFO16/RAMB16 数 | 232         | 2 (1%)       | 2 (1%)       | 5 (2%)     |

| DSP48 数         | 128         | 4 (3%)       | 4 (3%)       | 12 (9%)    |

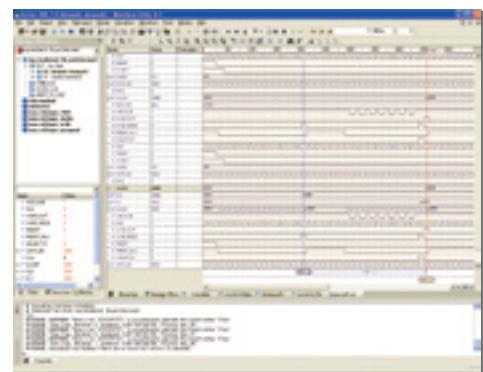

# FPGA Designs Made Easy

## Active-HDL

Active-HDLは、高速シミュレーションエンジン、グラフィカルデザインエントリ、ドキュメント作成支援機能を搭載し、大規模かつ複雑化するFPGAの設計生産性を大幅に向上します。

### 特 長

#### ■ 高速シミュレーションエンジン

- Windowsベース業界最高水準のパフォーマンス

- VHDL/Verilog/SystemVerilog/SystemC/EDIF混在

- 豊富なHDLデバッグ機能

#### ■ グラフィカル・デザイン・エントリ

- ブロックダイアグラム、ステートマシンエディタ

- HDLからブロック図、ステート図生成

- 波形ファイルからのテストベンチ生成

#### ■ コードカバレッジ

#### ■ MATLAB/Simulink協調検証

#### ■ SWIFTインターフェース

#### ■ EDK、SOPC Builder、CoreConsoleサポート

#### ■ マルチFPGAベンダサポート

詳細情報はこちらから

<http://www.aldec.co.jp/products/active-hdl/>

アルデック・ジャパン株式会社

東京都新宿区新宿1-8-4 JESCO新宿御苑ビル7F

TEL: 03-5312-1791 FAX: 03-5312-1795 Email: [info@aldec.co.jp](mailto:info@aldec.co.jp)

<http://www.aldec.co.jp>

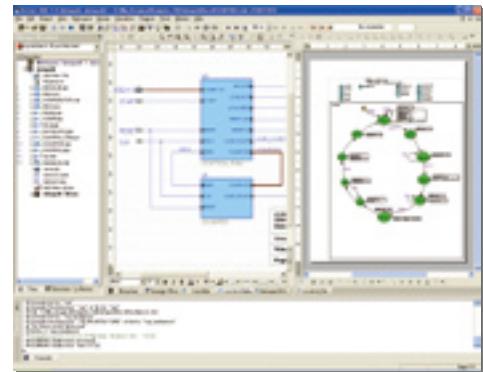

# Designing Multiprocessor SoCs

# マルチプロセッサ SoC の デザイン

ザイリンクスの EDK ツールと IP コアを使用して複数プロセッサを搭載した SoC をデザインすることによりアプリケーションに拡張性を持たせる

Vasanth Asokan

Staff Software Engineer

Xilinx, Inc.

[vasanth.asokan@xilinx.com](mailto:vasanth.asokan@xilinx.com)

エンベデッド処理への要求が急速に高まるにつれ、システム設計者は、複雑性とシングル プロセッサ システムの限界という 2 つの課題に直面していますが、この問題の解決策として、マルチプロセッサ デザインに注目が集まっています。

新世代 FPGA は、ロジックの高集積度と高性能ハードウェア ブロックに加えて、チップ マルチ処理 (CMP) ソリューションを可能にします。このソリューションをいち早く調査してデザインを生成する手法を開発することが求められます。

ザイリンクス エンベデッド開発キット (EDK) ツールと IP コアは、価格と性能目標を満たす、独自かつ精巧にカスタマイズされたマルチ処理ソリューションを FPGA で設計する柔軟性を提供します。本稿では、PowerPC® および MicroBlaze™ をベースにしたザイリンクスが提供するマルチ処理ソリューションを紹介します。

## シナリオ

マルチプロセッサでシステムをデザイン

するポイントは、高性能と機能の分割を行うことです。一般的に、マルチ処理が有効となる共通のシナリオがいくつか考えられ

ます。

- ・複数の独立した機能：複数の独立した処理タスクで構成されているデザインの場

合、各々に処理タスク専用の独立した処理モジュールを生成し、各処理モジュールに独自のプロセッサとペリフェラルのセットを割り当てます。

- ・制御とデータの荷重軽減：リアルタイムタスク（計算指向あるいはデータ指向）と非リアルタイムタスクの異なるセットが存在して、シングルプロセッサベースのソリューションでは応答不能状態を引き起こす場合、リアルタイムタスクをタイミングよく処理する専用のスレーブプロセッサを割り当てます。これにより、マスタープロセッサは他の通常タスクを処理し、ホストシステムへのインターフェイスの役割を担います。同時にマスタープロセッサは、スレーブプロセッサをモニタして制御します。スレーブプロセッサは特定の機能やインターフェイスを搭載している場合もあります。このシナリオの例としては、ネットワークの荷重軽減やメディア処理、セキュリティアルゴリズムなどが挙げられます。

- ・インターフェイス処理：複数のインターフェイスのブリッジやスイッチとして動作するシステムで、各インターフェイスでのデータ処理用にスレーブプロセッサを専用に使用し、1個または複数のマスタープロセッサにはもっと高度なブリッジやスイッチングタスクを制御させます。

- ・ストリーム処理：ストリーム指向の計算を扱うには、複数のプロセッサがパイプラインのようにデータストリームに作用するようアレンジします。マルチプロセッサパイプラインの各々同等のステージでは、計算の1部を処理して次のプロセッサに受け渡します。これはシステムのスループットを向上させる効果的な方法です。

- ・信頼性と冗長性：処理システムを複数回複製することで、信頼性と冗長性を向上します。

- ・対称処理：従来の対称処理（SMP）は効果的なソリューションで、プロセッサを追加することで明確に処理の種類を分割できないアプリケーションの性能を向上します。SMPが可能なOSレイヤは、パラレルタスクを管理し、それらのタスク

を自動的にスケジューリングして複数のプロセッサにデータを渡します。SMP 使用モデルは、SMP をインプリメントする際に必要となるキャッシュ コヒーレンスを持っていないため、ザイリンクス のプロセッサには適しません。

SMP シナリオを除くその他すべてのシナリオは、EDK ツールを使用してザイリンクスの FPGA 上に実現できます。ザイリンクス処理ソリューションのユニークな機能はその柔軟性であり、各処理用のサブシステムがアプリケーションの要求を満足できるカスタマイズが可能です。たとえば、すべてのプロセッサがキャッシュ メモリや浮動小数点ユニットを必要としているわけではありません。特定のプロセッサに特定の機能を割り振ることで、すべてのデザイン目標を満たし、状況に合ったソリューションが生成できます。

## 簡単でスケーラブルなシステム アーキテクチャ

お分かりのように、マルチプロセッサ システムには、数多くのモデルが使用可能で

す。また、システム アーキテクチャにも、

非常に多くの可能性があります。使用ケー

スをクリーンでスケーラブルなトポロジーに限定しても、アーキテクチャには非常に難しい面があるので、多くのニーズに合った基本的なアーキテクチャを定義するのが良いでしょう。

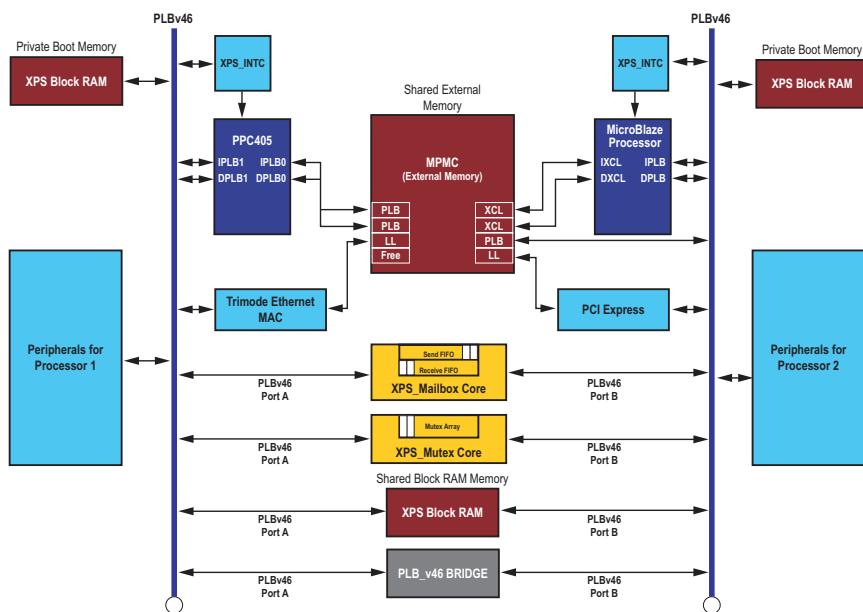

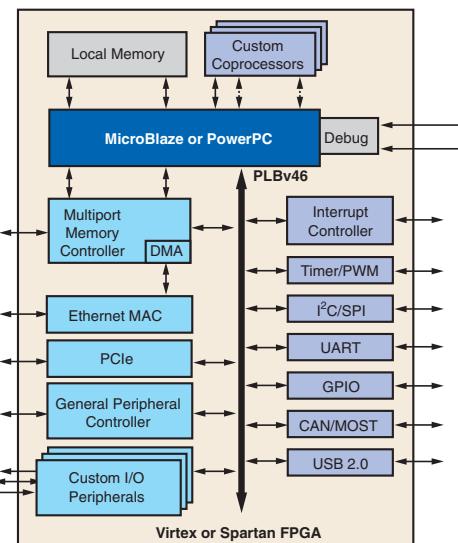

図1は、デュアルコアアーキテクチャを示します。このアーキテクチャは簡単でスケーラブルなマルチプロセッサシステムを定義し、この定義から始めてデザインの制約と課題を満たす派生的トポロジーが生成できます。次にこのアーキテクチャの鍵となる概念を示します。

- ・このアーキテクチャは、完全に独立した 2 つのシングル処理システムを単純に拡張しており、通信用コンポーネントにより 2 つのシステムが一緒にリンクされ形成されています。

- ・共有できるコンポーネントは、事実上すべてマルチ (あるいはデュアル) ポートです。これらのコンポーネントはマルチポートの性質があるため、各プロセッサのシステム バスは、静的負荷と動的負荷の両方の観点で、他から独立させることができます。各々の処理用サブシステムを分離することにより、他のプロセッサやペリフェラルが、別のプロセッサで処理が行われっていてもシステム バスから締め出されないようにできます。すべてのマ

図 1 - デュアル プロセッサ アーキテクチャ

- ルチポート ペリフェラルは、各種ポートへのアクセスを内部で調停します。

- 鍵となる共有ペリフェラルは、マルチポートメモリ コントローラ (MPMC) です。MPMC は、異なるポートのインターフェイスを介して外部メモリへのアクセスを提供します。複数のプロセッサは、独立したポートを介して MPMC に接続されます。このトポロジーでは、PowerPC および MicroBlaze の両プロセッサは、最小の待ち時間と高バンド幅を維持しながら、外部メモリに同時にアクセスできます。現在 MPMC は最大で 8 ポート提供しているので、3 個から 4 個のプロセッサを 1 個のシングル外部メモリに接続できます。

- このアーキテクチャは、プロセッサ間で内部ブロック RAM メモリを共有できることも示しています。オンチップ ブロック RAM を共有すると、キロバイト単位のデータをプロセッサ間で非常に高速にて受け渡しが可能となります。ブロック RAM へのアクセスは決定論的 (次のステップが常に 1 つに決まる) にもできます。アプリケーションによっては、これが重要な要件となっています。

- 共有メモリとは別に、2 個のコア XPS Mailbox と XPS Mutex があります。これらは簡単な形式のプロセッサ間の通信を提供します。XPS Mailbox コアは、2 個のプロセッサの間に、同期と非同期を問わず待ち時間の少ない FIFO スタイルのメッセージを受け渡しするインターフェイスを提供します。これを使用して、メッセージを直接受け渡しするか、共有メモリに格納されているメッセージへポインタを受け渡します。XPS Mutex コアは、2 個のプロセッサ上のソフトウェア間で、共有リソース (オンチップやオフチップでも可) へのアクセスを調停するのに使用できます。この 2 個のコアと一緒に使用すると、各プロセッサ上に協調ソフトウェア プログラムを構築できます。

- あるシステムでは、マルチポートではないペリフェラル (UART、SPI や I<sup>2</sup>C など) を共有したい場合があります。その場合、ペリフェラルに接続していないバスからペリフェラルに接続しているバスへ、

システムバス ブリッジを提供する必要があります。図 1 は、2 個のプロセッサ間で UART を共有するバス ブリッジの使用方法を示しています。

図 1 では、各プロセッサのある特定の特性を例証するために、PowerPC 405 プロセッサを一番目に、MicroBlaze プロセッサを二番目で示していますが、ほんのわずかな調整で、どのプロセッサでも対等に置き換えることができます。このようにして、このアーキテクチャはプロセッサ間でシームレスに移行できます。

図 1 は、推奨できるマルチ処理用アーキテクチャの全体像を示していますが、制約によってはこのアーキテクチャを変更する必要が生じる場合もあります。たとえば、ロジック エリアとリソースの利用が主要な問題となるシステムでは、すべてのプロセッサを同一のシステムバスに接続することができます。これにより、決定論的ではなくなり、実行時にバスへの負荷も増えますが、新しいシステム バスの除去に加え、IP コア上にマルチポートを作成不要なことからエリアの節約もできます。

他の派生的アーキテクチャも可能です。たとえば、高性能プロセッサを分離した別のシステム バスに接続し、複数の低性能プロセッサを共有システム バスに接続することもできます。処理用サブシステムをマルチレベルのブリッジを介してお互いに接続することで、階層的トポロジーを生成することも可能です。EDK が提供している各種ツールと IP コアを使用すれば、この基本トポロジーに変更を加え、所望するニーズに正確にマッチしたデザインが作成できます。

## 他の考察

マルチ処理アーキテクチャに関しては、その他の考察が必要である場合も考えられます。たとえば、2 個のプロセッサ間で競合しないように、メモリ マップを定義する必要が生じる場合があります。EDK の自動アドレス生成ツールでは、このタスクを、ただボタンを押すだけのように簡単に実現します。

ネットワークのクロッキングやリセット

についても考慮が必要でしょう。すべてのプロセッサに同じレートのクロックを与えることも可能ですし、各々のプロセッサに異なるクロック レートを与えることもできます。また、各種の異なるレベルでのリセットを定義できます。たとえば、プロセッサだけのリセット、プロセッサ サブシステムのリセット、システムのリセットなどです。プロセッサは個々に独立したデバッガ ポートに接続し、プロセッサごとに分けてデバッグする必要があるでしょう。

ハードウェアだけでなく、複数のソフトウェア システムが協調して動作するようなデザインを設計する場合もあるかもしれません。これには共有メモリの使用、メッセージの受け渡し、バリアやランデブといった共通の同期用概念が含まれ、これらをうまく取り入れることで、システムは予測可能で同期の取れた動作をさせることができます。多くの市販ソフトウェアが利用できますが、それらを使用すれば、高レベルの通信パラダイムが得られます。

## 結論

このように、ザイリンクスのプロセッサを使用することでマルチ プロセッサ システムを効率よく、また容易に実現します。マルチプロセッサ システムの可能性についての詳細は、ホワイトペーパー (英語版) [http://japan.xilinx.com/support/documentation/white\\_papers/wp262.pdf](http://japan.xilinx.com/support/documentation/white_papers/wp262.pdf) をご覧ください。

また、リファレンス デザインを解説しているザイリンクスのアプリケーション ノート「Dual Processor Reference Design Suite (英語版)」(XAPP996) [http://japan.xilinx.com/support/documentation/application\\_notes/xapp996.pdf](http://japan.xilinx.com/support/documentation/application_notes/xapp996.pdf) もご覧ください。

今後も EDK 開発ツールは、自動化されたマルチプロセッサ デザイン生成や協調デベッギングに対するサポートなど、新しい機能を将来提供していく予定です。また、PowerPC 440 プロセッサ搭載のザイリンクス Virtex<sup>®</sup>-5 FXT プラットフォームは、超高性能マルチプロセッサ システムに対し限りない可能性を切り開いていきます。

# Accelerating Video Development on FPGAs Using the Xilinx XtremeDSP Video Starter Kit

## ザイリンクス XtremeDSP ビデオ スタータ キット により FPGA 上でのビデオ開発を加速

VHDL や Verilog の知識を必要としない、プロセッサに最適で高画質結果を生成するビデオ開発手法の試み

Tom Hill

Sr. Marketing Manager, DSP

Xilinx, Inc.

[tom.hill@xilinx.com](mailto:tom.hill@xilinx.com)

ビデオ開発市場の、基本ビデオ処理からより複雑にインテグレーションされた処理ソリューションへの移行は、次世代ビデオ圧縮標準と共に、単独の DSP では処理できないビデオ パフォーマンスのシステムを要求しています。Xilinx® Spartan®-3A DSP などの FPGA は、費用対効果が重視される軍事産業や自動車、医療、民生機器、産業機器、セキュリティなどの各アプリケーションに対して、30 ドル以下で

20GMAC 以上の DSP 性能を提供することにより、このギャップを埋めています。FPGA はビデオに対して、完全なエンドツー エンドのソリューションを提供するため、独自のロジックやエンベデッド処理機能、OS サポート、ドライバを提供しています。

ビデオ アプリケーションで FPGA の採用が妨げられている理由は、FPGA の性能利点について設計者の理解が不足しているためではなく、デザイン フローの経験を欠いているためです。これは特に、C 言語でのプログラミングに慣れている従来の DSP プログラム開発者にいえることです。

デバイスの柔軟性を利用して、特定アプリケーション用に最適化したハードウェアアーキテクチャをコンフィギュレーションすることにより、FPGA の性能の向上を達成できます。この柔軟性により、開発工程に自由度が増し、複雑なデザイン開発も可能になります。

XtremeDSP™ ビデオ スタータ キット (VSK) は、使い易いデザイン環境を提供します。このキットは、アプリケーション例、および、ザイリンクスの標準ツールフローのフル サポートを提供しており、デザイン工程の加速化を支援すると共に、最終製品における他社製品との差別化を可能にします。

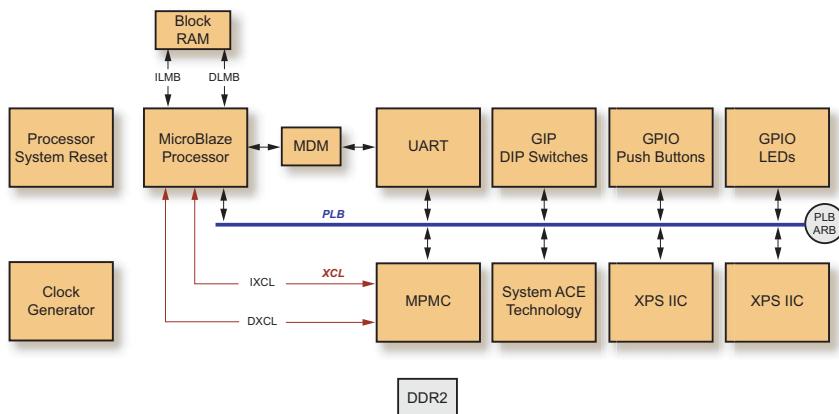

図 1 - 基本プラットフォームのブロック図

### XtremeDSP VSK - Spartan-3A DSP 版

XtremeDSP ビデオ スタータ キット - Spartan-3A DSP 版は、Spartan-3A DSP 3400A 開発プラットフォームや FMC ビデオ ドーターカード、VGA カメラで構成されているビデオ開発プラットフォームです。

Spartan-3A DSP 3400A 開発プラットフォーム (個別で購入可能) は Spartan-3A DSP XC3SD3400A デバイスを中心に構築されています。このデバイスは、126 個のエンベデッド DSP ブロックを提供しており、これらはコプロセッシングと高性能ビデオ処理システムをインプリメントするのに使われます。

FMC ビデオ ドーターカードは、次に挙げる追加のインターフェイスを含むことにより、Spartan-3A DSP 3400A 開発プラットフォームのビデオ I/O 機能を拡張しています。

- ・DVI-I 入力、デジタルとアナログ双方

- ・コンポジット入力と出力

- ・S- ビデオ入力と出力

- ・2 つのカメラ入力

### ビデオ開発ツール

RTL の知識や、ザイリンクスのエンベデッド開発キット (EDK) および System Generator for DSP の経験がなくても、VSK でビデオ アプリケーションを生成す

### 基本プラットフォームを使ったビデオ アプリケーションの開発

基本プラットフォームと呼ばれるエンベデッド システムは、VSK を使ってビデオ アプリケーションを開発できるフレームワークを提供します。この基本プラットフォームは、ザイリンクス Platform Studio のベース システム ビルダ (BSB) で生成されたエンベデッド システムで、MicroBlaze エンベデッド プロセッサを含んでいます。

このフレームワークを使用すると、新しいデザインを一から設計することも可能で、また、プロセッサ ベースのシステムで開発された既存アプリケーションから移行して設計することも容易にできます。外部プロセッサ用に生成した C コードは、最小の労力で MicroBlaze プロセッサ用に再コンパイルすることができます。一度移植すると、高性能ビデオ チェーンは、ソフトウェアから FPGA ファブリックに移動できます。

この移動を容易に行うために、VSK には Platform Studio を使うことで基本システムに簡単に追加可能なカスタム ペリフェラルの IP コア ライブラリが含まれています。このライブラリを使用して、ビデ

ることが可能です。EDK は、エンベデッド プログラマブル システムをデザインするための包括的なソリューションで、Platform Studio ツール スイートやエンベデッド IP コア、MicroBlaze™ エンベデッド プロセッサを含んでいます。

System Generator for DSP は、ザイリンクス用に最適化された 100 個以上の DSP ビルディング ブロックからなる Simulink ブロックセットを提供することにより、MathWorks 社の Simulink/MATLAB モデリング環境を使った FPGA のデザイン設計を可能にします。

表 1 - VSK リファレンス デザインの概要

| リファレンス デザイン   | 機能の詳細                                                                                                                                                                                                               |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DVI パス スルー    | <ul style="list-style-type: none"> <li>・入力ポートからビデオ ストリームを捕捉</li> <li>・ビデオ ストリームにリアルタイム画像処理を実行</li> <li>・処理ビデオの表示</li> </ul>                                                                                         |

| DVI フレーム バッファ | <ul style="list-style-type: none"> <li>・DVI ソースからビデオ ストリームを捕捉</li> <li>・ビデオ ストリームを外部メモリにバッファリング</li> <li>・バッファリングされたビデオの表示</li> <li>・メモリバンド幅の利用データをレポート</li> </ul>                                                  |

| カメラ フレーム バッファ | <ul style="list-style-type: none"> <li>・カメラからビデオ ストリームを捕捉</li> <li>・ビデオ ストリームに画像処理を実行</li> <li>・ビデオ ストリームを外部メモリにバッファリング</li> <li>・処理されたビデオを異なるレートで表示</li> <li>・マイクロプロセッサを使った、ビデオ パイプラインの各種側面のコンフィギュレーション</li> </ul> |

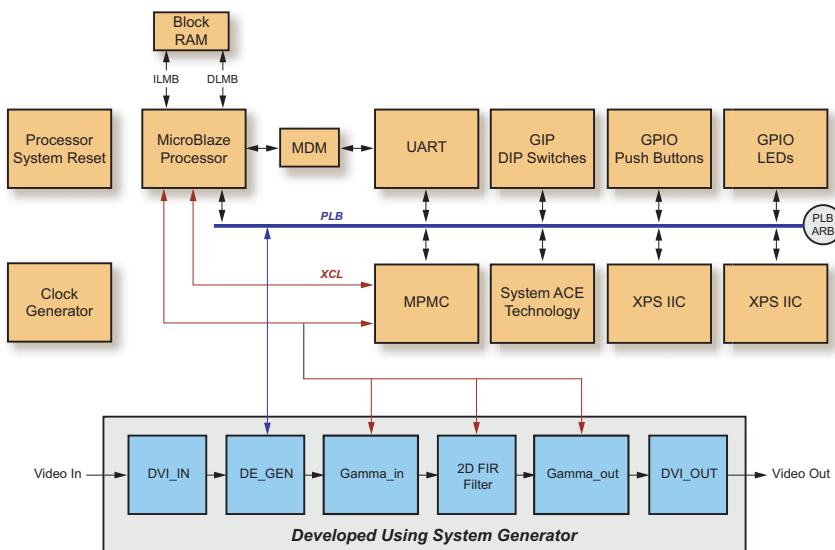

図 2 - ビデオ パイプライン搭載の基本システム

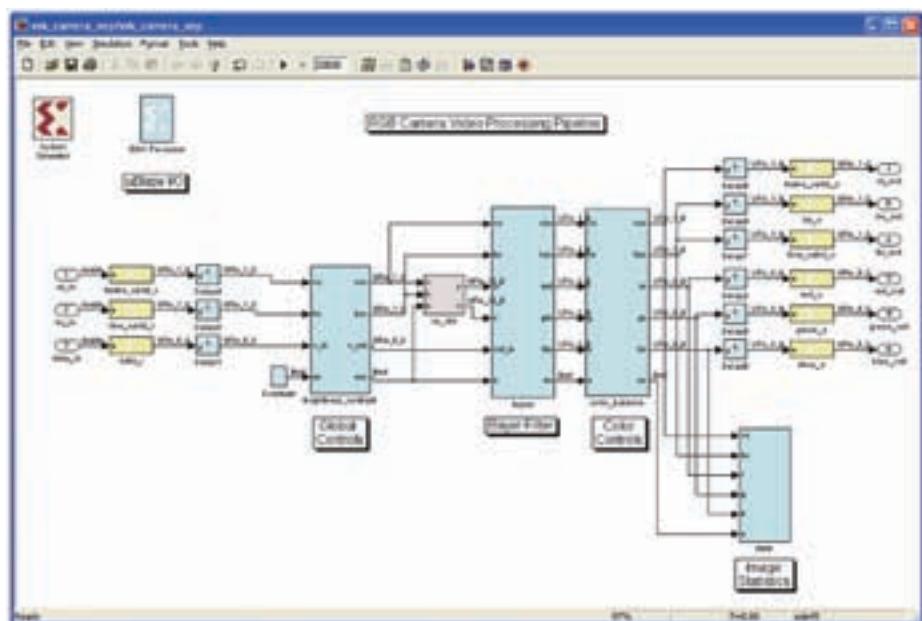

図 3 - カメラビデオ処理パイプラインのためのSystem Generator for DSP ダイアグラム

オ インタフェイスへの接続やデータ フレームの管理、そしてメモリや基本的なビデオ処理へのアクセスが行えます。同梱されているカスタム ペリフェラルは次のとおりです。

- ・DVI 入力

- ・DVI 出力

- ・カメラ

- ・ビデオ フレーム バッファ コントローラ

(VFBC)

・ビデオ処理パイプライン

ザイリンクス VFBC はリアルタイム オペレーションを実現する際に 2 次元データのハードウェア制御が必要となるビデオアプリケーションに理想的です。この典型例としては、ビデオ監視やビデオ会議、ビデオ ブロードキャストなどに使われています。

る、動き検出やビデオ スケーリング、オンラインスクリーン ディスプレイ、ビデオ捕捉などが挙げられます。

## VSK リファレンス デザインで開発をすばやく開始

VSX は、ザイリンクス FPGA 上で動作するビデオ アプリケーションの開発を即開始できるよう、3 つのリファレンス デザインを提供しています。各リファレンス デザインは基本プラットフォーム上に構築され、VSX IP コアのライブラリからのカスタム ペリフェラルを使用します。表 1 は、各リファレンス デザインとそのビデオ処理機能およびコネクティビティ機能を示します。これらのリファレンス デザインは、開発をスムーズに進めるための開始点となることを目的としています。図 2 は、DVI パス スルーリファレンス デザインが基本システム内でインターフェイスする様子を示します。

## モデル ベース デザインを使ってビデオ アプリケーションを設計

FPGA 上のビデオ アプリケーションの開発を加速するには、プロセッサ上のソフトウェアで実行している性能に大きな影響を与えるオペレーションをハードウェアへ移動する必要があります。VSX は多様なハードウェア設計をサポートします。VSX は、VHDL/Verilog を使う強力なハードウェア デザイン バックグラウンドを利用するフローヤ、ハードウェアのデザイン経験が皆無に近いエンジニア用に C 言語、MATLAB、および Simulink を含むより抽象的なモデリング環境を利用したフローを提供しています。

MathWorks 社の Simulink はモデルベースのデザイン環境で、これを使ってビデオ システムのアルゴリズム モデルを開発できます。MathWorks 社は、Simulink 用にビデオや画像用のブロックセットをオプションで提供しています。これはビデオ用ビルディング ブロックの豊富なセットを提供し、ストリーミング ビデオの処理やモデル内の各ステップでの結

果の視覚化を容易にしています。

まず、浮動小数点データ タイプおよび高画質な動画や画像用の各ブロックを使ってビデオ処理アルゴリズム自身を抽象的にモデル化し、複雑性やシステム コスト、性能に関連したトレードオフを考慮してこのアルゴリズムを修正します。

System Generator for DSP は、ザイリンクスのデバイスに最適化された豊富な DSP ビルディング ブロックを提供することで、Simulink を使ってのザイリンクス FPGA のデザインを可能にしました。System Generator for DSP で設計された DSP デザインは、Platform Studio 用にカスタム ペリフェラルに変換され、プロセッサ ローカル バスあるいは Fast Simplex Link バスを使って基本システムに接続されます。

図 3 に System Generator を使い生成したカメラ ビデオ処理パイプラインの

例を示します。これは、VSK と共に出荷されるカメラ フレーム バッファのリファレンス デザインに含まれています。

System Generator for DSP は、Spartan-3A DSP 3400A 開発プラットフォームの HiL (Hardware-in-the-loop) システム協調シミュレーションをサポートしています。このプラットフォームを使って、Simulink のシミュレーション性能を最大で 1,000 倍加速することができます。これにより、ビデオ アルゴリズムの開発と、MathWorks 社のデータ収集ツールボックスを介して Simulink に読み込まれるリアルタイム ビデオ ストリームのデバッグを可能にします。

## 結論

XtremeDSP ビデオ スタータ キット Spartan-3A DSP 版は、1,600 ドル以

下で完全なビデオ開発ソリューションを提供し、開発コストを低く抑えます。このキットに含まれる DSP やエンベデッド デザイン ツールにより、RTL デザインの経験がなくても、FPGA でのビデオ システムの迅速な開発が可能となります。

Virtex-5 SXT デバイスや Virtex-4 SX デバイス、Spartan-3A DSP のような DSP 用に最適化された FPGA プラットフォームは、高性能ビデオや画像処理アプリケーションに求められるコストと性能要求の両方を満たす最適なソリューションを提供します。このアプリケーションには、セキュリティやブロードキャスト、産業機器、民生機器、医療、自動車に向けたアプリケーションがあり、これにより製品開発を早め、製品が早期に陳腐化するのを防いでいます。

詳細は、[http://japan.xilinx.com/s3adsp\\_vsk](http://japan.xilinx.com/s3adsp_vsk) をご覧ください。

## ザイリンクス トレーニング スケジュール

[8~9月]

10 月以降のトレーニング スケジュールは Web サイトでご確認ください。

ザイリンクスでは、大規模、高速 FPGA を対象にした FPGA 設計のための各種トレーニングを各地で開催しております。是非ご利用ください。

| コース名                                    | 日 程 |                   | 主 催     | 開 催 地 |

|-----------------------------------------|-----|-------------------|---------|-------|

| ISE デザイン入力                              | 9月  | 2日 (火)            | ザイリンクス  | 東京会場  |

| FPGA 設計導入                               | 9月  | 3日 (水)            | ザイリンクス  | 東京会場  |

| FPGA 設計実践                               | 8月  | 6日 (水)~ 7日 (木)    | ザイリンクス  | 東京会場  |

|                                         |     | 20日 (水)~21日 (木)   | ザイリンクス  | 東京会場  |

|                                         | 9月  | 10日 (水)~11日 (木)   | ザイリンクス  | 東京会場  |

|                                         |     | 25日 (木)~26日 (金)   | ザイリンクス  | 東京会場  |

| アドバンスド FPGA 設計                          | 8月  | 28日 (木)~29日 (金)   | ザイリンクス  | 東京会場  |

|                                         | 9月  | 4日 (木)~ 5日 (金)    | 菱洋エレクトロ | 大阪会場  |

|                                         |     | 30日 (火)~10月1日 (水) | ザイリンクス  | 東京会場  |

| Virtex-5 LX および LXT デザイン                | 9月  | 5日 (金)            | ザイリンクス  | 東京会場  |

| エンベデッド システム開発                           | 8月  | 7日 (木)~ 8日 (金)    | ザイリンクス  | 東京会場  |

|                                         | 9月  | 11日 (木)~12日 (金)   | ザイリンクス  | 東京会場  |

|                                         |     | 18日 (木)~19日 (金)   | ザイリンクス  | 東京会場  |

| アドバンスド エンベデッド システム開発                    | 8月  | 21日 (木)~22日 (金)   | ザイリンクス  | 東京会場  |

|                                         | 9月  | 25日 (木)~26日 (金)   | ザイリンクス  | 東京会場  |

| System Generator for DSP を使用した DSP デザイン | 8月  | 19日 (火)~20日 (水)   | ザイリンクス  | 東京会場  |

|                                         | 9月  | 16日 (火)~17日 (水)   | ザイリンクス  | 東京会場  |

| MGTシリアル I/O デザイン                        | 8月  | 5日 (火)~ 6日 (水)    | ザイリンクス  | 東京会場  |

|                                         | 9月  | 2日 (火)~ 3日 (水)    | ザイリンクス  | 東京会場  |

| PCI Express システム <b>NEW</b>             | 9月  | 9日 (火)~10日 (水)    | ザイリンクス  | 東京会場  |

\*すべてのトレーニングは、ザイリンクス認定インストラクターによるオフィシャルトレーニングです。

\*日程および会場は、都合により変更となる場合もございます。最新情報はザイリンクス トレーニング Web サイトをご覧ください。

詳細とご登録はこちらから ►► <http://japan.xilinx.com/support/education-home.htm>

## ザイリンクス販売代理店オリジナル トレーニング

販売代理店各社のオリジナル トレーニングの内容およびスケジュールは、各社の Web サイトをご覧ください。

|               |                                                                                                                     |

|---------------|---------------------------------------------------------------------------------------------------------------------|

| 東京エレクトロン デバイス | <a href="http://ppg.teldevice.co.jp/">http://ppg.teldevice.co.jp/</a>                                               |

| アブネット ジャパン    | <a href="http://www.avnet.co.jp/services/Training/index.asp">http://www.avnet.co.jp/services/Training/index.asp</a> |

| 新光商事          | <a href="https://xilinx.shinko-sj.co.jp/training/index.html">https://xilinx.shinko-sj.co.jp/training/index.html</a> |

| 菱洋エレクトロ       | <a href="http://www.ryoyo.co.jp/xilinx/">http://www.ryoyo.co.jp/xilinx/</a>                                         |

| PALTEK        | <a href="http://www.paltek.co.jp/seminar/index.htm">http://www.paltek.co.jp/seminar/index.htm</a>                   |

レーダ

無線

# 高速信号処理に最適!!

4ch 200MHz 16bit AD 塔載

Virtex-5 FPGA ボード

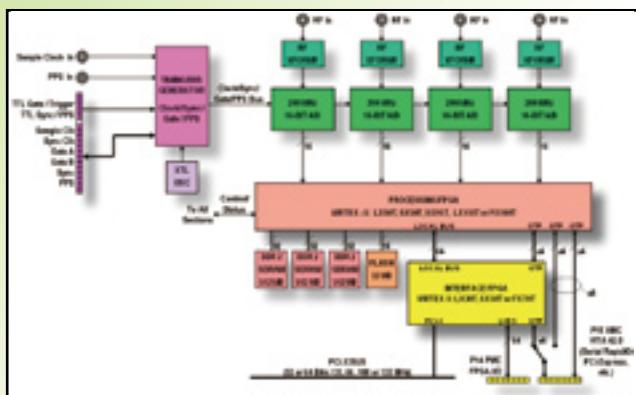

Model 7x50は通信システムのHF帯やIF帯の信号処理に適した4chの高速AD塔載FPGAボードです。その特徴はハイパフォーマンスなシステムの要求に応えるため、4ch 200MHz 16bit AD を搭載し、更にデータ処理用と I/O 制御用に 2 個 Virtex-5 FPGA を搭載しています。ボードは、PCI ExpressをはじめPCI、CompactPCI、PMC/XMCの各種と、複数枚のボードにClockを供給するための Clock Synthesizer ボードもございます。

Model 7150 ブロック図

## 【特徴】

- 4ch 200MHz 16bit AD

- 1.5GB まで DDR2 SDRAM 塔載可能

- Xilinx Virtex-5 FPGA を 2 個塔載

- 200MHz で 2.56 秒のデータキャプチャが可能

- 複数枚のボード間同期を可能とするLVDS clock / sync バス

- カスタムIOのためFPGAと 32PairのLVDS接続

- VITA42.0 対応 XMC インターフェースを用意

- PCI Express をはじめ、PCI/CompactPCI/PMC ボードを用意

- FPGA 開発のための Design Kit を用意

- VxWork / Linux / Windows をサポート

■■■■ ソフトウェア開発者に朗報 !!! ■■■■

MATLAB/Simulink を使ったアルゴリズムの開発

・検証や VHDL コードの自動生成等に運動した

専用アダプテーションキットにも対応予定

■■ DDC の IP コアインストール製品も用意 !!! ■■

256 チャネル DDC

各バンクのDecimationレンジを128～1024、64ステップ

32 チャネル DDC

各バンクのDecimationレンジを16～8192、8ステップ

2or4 チャネル DDC

各バンクのDecimationレンジを2～256、1ステップ

## 受託開発コーナー

弊社ではハード & ソフトの受託開発も承っています。是非ご利用下さい。

(お問い合わせは)

sales@mish.co.jp

<http://www.mish.co.jp/>

MISH

INTERNATIONAL

株式会社ミッシュインターナショナル

TEL 042-538-7650 FAX 042-534-1610

〒190-0004 東京都立川市柏町4-56-1

# MicroBlaze v7 Gets an MMU

# MicroBlaze v7 が MMU (メモリ管理ユニット) を装備

メモリマネージャが本格的な Linux をザイリンクス プロセッサ コアに導入

Tom R. Halfhill

Senior Analyst