# Xcell journal

SOLUTIONS FOR A PROGRAMMABLE WORLD

通信およびオート

モーティブにおける

**FPGA** がもたらす

高速革新

## INSIDE

4G ワイヤレス ネットワークで

重要な役割を担う FPGA

ザイリンクス FPGA プラット

フォームで ドライバ アシスタ

ンス システムのアルゴリズムを

構築

FPGA I/O ピンの割り当てに

おける課題を解消

XILINX®

[japan.xilinx.com/xcell/](http://japan.xilinx.com/xcell/)

出力3.3V以上の

システム電源用

超低ノイズの

汎用モジュール

### 超低ノイズファミリ

**LTM4612**

I<sub>OUT</sub> **5A**

V<sub>IN</sub> **5~36V**

V<sub>OUT</sub> **3.3~15V**

15×15×2.8mm

New

New

**LTM4606**

I<sub>OUT</sub> **6A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

New

New

### デュアルアルファミリ

**LTM4614** \*近日発売

I<sub>OUT</sub> **4A×2**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4615** \*近日発売

I<sub>OUT</sub> **4A×2 1.5A VLDO**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4616**

I<sub>OUT</sub> **8A×2**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM8024** \*近日発売

I<sub>OUT</sub> **1.2A×2**

V<sub>IN</sub> **3.7~36V**

V<sub>OUT</sub> **0.8~10V**

9×15×2.8mm

### 36V高電圧ファミリ

**LTM8020**

I<sub>OUT</sub> **200mA**

V<sub>IN</sub> **4~36V**

V<sub>OUT</sub> **1.25~5V**

6.25×6.25×2.32mm

**LTM8021**

I<sub>OUT</sub> **500mA**

V<sub>IN</sub> **3.6~36V**

V<sub>OUT</sub> **0.8~5V**

6.25×11.25×2.8mm

**LTM8022**

I<sub>OUT</sub> **1A**

V<sub>IN</sub> **3.6~36V**

V<sub>OUT</sub> **0.8~10V**

9×11.25×2.8mm

**LTM8023**

I<sub>OUT</sub> **2A**

V<sub>IN</sub> **3.6~36V**

V<sub>OUT</sub> **0.8~10V**

9×11.25×2.8mm

### 低電圧ファミリ

**LTM4604**

I<sub>OUT</sub> **4A**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.8~5V**

9×15×2.3mm

**LTM4608**

I<sub>OUT</sub> **8A**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

9×15×2.8mm

### 昇降圧型ファミリ

**LTM4605**

I<sub>OUT</sub> **5A (12A 降圧モード時)**

V<sub>IN</sub> **4.5~20V**

V<sub>OUT</sub> **0.8~16V**

15×15×2.8mm

**LTM4607**

I<sub>OUT</sub> **5A (10A 降圧モード時)**

V<sub>IN</sub> **4.5~36V**

V<sub>OUT</sub> **0.8~24V**

15×15×2.8mm

**LTM4602**

I<sub>OUT</sub> **6A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4603**

I<sub>OUT</sub> **6A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4600**

I<sub>OUT</sub> **10A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4601**

I<sub>OUT</sub> **12A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

# FPGA高速シリアルI/Oの電源に最適

- 例えば12V入力から1V/5Aの出力を、低ノイズで実現

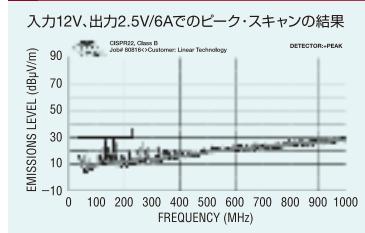

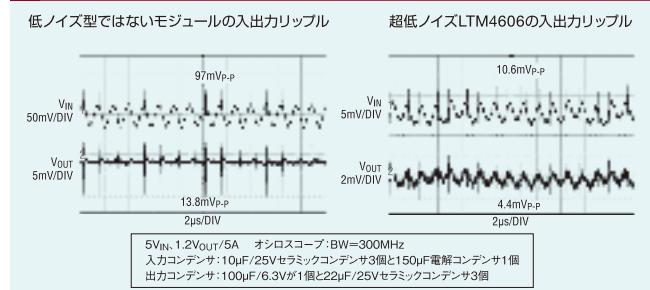

- 低EMI(CISPR 22 Class Bに準拠)、低入出力リップル電圧

- 高効率(低発熱)。サイズは、わずか15×15×2.8mm

- 電源回路の実装面積を大幅削減、設計時間も大幅低減

- 簡単、すぐに使えるスイッチモードの電源モジュール

## 実現したのは、LTM<sup>®</sup>4606 μModule™

マイクロ・モジュール

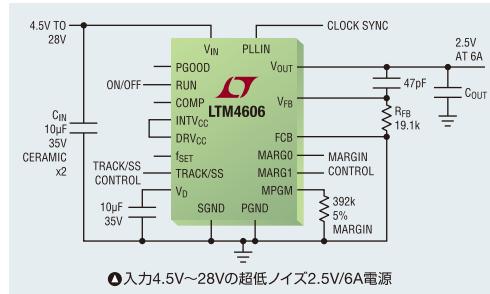

### LTM4606 超低EMIの28VIN、6A DC/DC μModule

LTM4606はFPGAの高速I/OやSERDESに最適な、超低EMI、高効率(低発熱)、そしてリニアレギュレータのようにシンプルな小型スイッチングDC/DCソリューションです。従来のリニアレギュレータでは発熱により不可能だった、12Vから1V/5Aといったような低ノイズ電源が実現できます。

- 完全な低EMIスイッチモード電源

- 広い入力電圧範囲: 4.5V~28V

- 標準6AのDC出力電流、8Aのピーク出力電流

- 出力電圧範囲: 0.6V~5V

- ±1.5%の全DC誤差

- 入力電圧5V、出力電圧3.3V時の効率: 最大93%

- 低い入出力換算ノイズ

- 出力電圧トラッキングおよびマージニング

- PLL周波数同期

- パワーグッド出力

- 並列接続/電流分配

- 超高速過渡応答

- 電流モード制御

- プログラム可能なソフトスタート

- 電流フォールドバック保護(起動時にディスエーブル)

- 出力過電圧保護

- 55°C~125°Cの動作温度範囲(LTM4606MPV)

- 15mm×15mm×2.8mm

- 表面実装LGAパッケージ

#### ■ 超低EMI

#### ■ 低い入出力ノイズ電圧

#### ■ ザイリンクス社RocketIO™検証済み電源

LTM4606はザイリンクス社によって同社のラボで、2.65Gbpsのライン・レートでPRBS-15データ・パターンを使ってテストされました。回路がLTM4606から給電されている状態で、トランシミッタのジッタとレシーバのジッタ耐性を測定して、トランシーバの性能を評価する方法です。テストセットアップ、テスト装置およびテスト結果の詳細な報告はFPGA Journal Chalk Talkウェブキャスト([https://admin.acrobat.com/\\_a700655680/xilinx080826](https://admin.acrobat.com/_a700655680/xilinx080826))をご覧いただけます。

検証に使用された

LTM4606テストボード

#### 評価ボード

お問い合わせは、

下記販売代理店まで

リニアテクノロジー国内ニュースサイト

[www.linear-news.jp](http://www.linear-news.jp)

LT、LTC、LTMは、リニアテクノロジー社の登録商標です。μModule、LINEAR EXPRESSは、リニアテクノロジー社の商標です。他の商標はそれぞれが所有するものです。

オンラインストア リニアエクスプレス

**LINEAR EXPRESS™**

0120-7291-22

株式会社 トーメン エレクトロニクス

本社 TEL 03-5462-9615

大 阪 06-6447-9644 名古屋 052-582-1591

福 岡 092-713-7779 宇都宮 028-625-8331

松 本 0263-34-6131 北関東 048-221-9011

仙 台 022-221-8061 浜 松 053-452-8147

立 川 042-548-9871

東京エレクトロンデバイス株式会社

本社 TEL 045-443-4024

大 阪 06-6399-1511 名古屋 052-562-0825

東 京 03-5908-2621 北関東 048-600-3880

水 戸 029-227-6555 立 川 042-548-0255

浜 松 053-459-2204 松 本 0263-36-8112

福 岡 092-474-4121 仙 台 022-298-7184

株式会社 三 共 社 本社 TEL 03-5298-6201

株式会社 ジ ェ ピ コ 本社 TEL 03-6362-0411

東京電子販売株式会社 本社 TEL 03-5350-6711

株式会社 信 和 電 業 社 本社 TEL 06-6943-5131

伊 藤 電 機 株 式 会 社 本社 TEL 052-935-1746

# Xcell Journal 創刊 20 周年

# 20

年前、Zilog 社や Fairchild 社に籍を置き、さらに AMD 社を経てザイリンクスに加わったあるアプリケーション エンジニアが、ザイリンクス ユーザー向けに技術誌の創刊を手がけました。彼はそれを、Xcell、「The Newsletter for Xilinx Programmable Gate Array Users」と名付きました。

それが、ザイリンクスの伝説的人物、Peter Alfke です。彼は、当時すでに廃刊になっていたフェアチャイルドの季刊誌「Progress」にその内容の由来をうけ Xcell Journal を創刊したと当時を振り返っています。「当時 FPGA は、まったく新しくしかも異例の技術でしたので、その最良の利用方法をユーザーに伝えたかったです。」と Alfke は述べています。「年に一度データ ブックを刊行していましたが、更新情報も多く、もちろん当時はまだインターネットなどありませんでしたので、Xcell Journal を四半期ごとのアプリケーション誌として、技術的な詳細記事や設計のハウツー、革新的なアイディア、さらにシリコンや設計ツール、IP コアの入手情報などを掲載することにしました。」

Peter は、当時まだバークレイ校の学生だった彼の娘 Karen と共に、1988 年第 4 四半期に Xcell の創刊号を発刊しました。「彼女は Mac をオフィスに持ち込み、創刊号から 5 号までのタイプ入力と編集を担当したのです。」と Alfke は述べています。

創刊号の巻頭記事は、当時発行されたばかりのデータブックに関するもので、XC2000 や XC3000、XC2000 のミリタリ バージョン製品のデータ シートも掲載しました。その他には、DOS 関連記事（“All DOS Are Not Created Equal”：すべての DOS は同じようには作られていない。）や XACT FPGA デザインツールと当時の ISE の紹介記事が掲載されました。XACT を「巨大で要求の厳しいプログラム、対話型グラフィックスを使用し、メガバイトの RAM を必要とする。」と評した記事は、当時 640 kb しかアドレスできなかった IBM PC を未知の領域へ導いたのでした。

Alfke は現在もザイリンクスに在籍し、アプリケーションや技術資料の作成に携わっています。彼は、当時の記事のなかには今でも新鮮で有用なものだと感じる内容のものもあると指摘しています。過去 Xcell がどのように発展してきたかを延々と述べるより、今後もさらに 20 年は継続していくことを願ってやまないこのすばらしい遺産の作成を開始した男の功績を称えようではありませんか。右表は、1 ~ 28 号に掲載された Peter 執筆の特選記事です。

Mike Santarini

発行人

## 特選記事 (\* 米国で発行された英語版のみ)

|                             |                                           |

|-----------------------------|-------------------------------------------|

| 1993 年第 4 半期<br>11 号 31 ページ | SPROM のスタンバイ電流の LDC を介した接地によりゼロ削減         |

| 1994 年第 2 半期 13 号 25 ページ    | ショート チュートリアル：キャリーとオーバーフロー                 |

| 1995 年第 2 半期 17 号 30 ページ    | 3 つの CLB 内マンチェスター デコーダ                    |

| 1995 年第 3 半期 18 号 30 ページ    | オーバーシュートとアンダーシュート                         |

| 1995 年第 3 半期 18 号 36 ページ    | 4 文字単語「Hold」とは一ホールド時間すなわち…                |

| 1995 年第 4 半期 19 号 34 ページ    | 2 本のピンと 2 個の抵抗を使用したユーザー定義のシムット トリガー       |

| 1996 年第 2 半期 21 号 35 ページ    | 10 衍の完全同期 BCD カウンタ @87MHz                 |

| 1996 年第 2 半期 21 号 40 ページ    | なぜ理解しにくい？ミニマム遅延の考察                        |

| 1996 年第 3 半期 22 号 28 ページ    | 消費電力とパッケージと性能、そしてそのトレードオフ                 |

| 1997 年第 1 半期 24 号 20 ページ    | トラブル フリーでグリッチのないクロック間切り替え                 |

| 1997 年第 1 半期 24 号 21 ページ    | 200MHz データ ストリームのデマルチブレキング                |

| 1997 年第 4 半期 27 号 27 ページ    | 分散スペクトル クロックで EMI を低減                     |

| 1997 年第 4 半期 27 号 28 ページ    | ホット プラグインの危険性について                         |

| 1998 年第 1 半期 28 号 22 ページ    | PC 基板設計の考察                                |

| 1998 年第 1 半期 28 号 28 ページ    | 自己初期化されるグローバル リセット                        |

| 1998 年第 1 半期 28 号 29 ページ    | CMOS I/O の特性                              |

| 1998 年第 1 半期 28 号 33 ページ    | XC4002XL 搭載の周波数カウンタにより低消費電力 400MHz の性能を達成 |

## 新発行人 Mike Santarini より

2008 年夏に新しく Xcell の発行人となりました。電子業界専門の媒体誌 EDN や EE Times、Integrated System Design にて EDA や FPGA、ASIC、IP コア、メモリ分野関連記事の編集に 13 年従事した後、2006 年 3 月にザイリンクスに入社しました。

私はこれまで、IC やシステム、デザインのコミュニティに、新しいデザイン開発と課題を提供することに専念してきました。今後は、常に成長を続けるザイリンクス ユーザー コミュニティにそのミッションを移すことになりました。ザイリンクスからこの仕事の話があつたときに、私は喜んでこの大きなチャンスを引き受けることにしました。

Xcell Journal の発行人としての私の役割は、ザイリンクスの経験豊富なエンジニアやユーザー エンジニアにおける最新技術動向をお伝えすることで、読者の皆さんの設計の一助となることがあります。

Xcell の製作には、さらに魅力的な媒体にすべく、多くの社員が関係し日々努力を重ねています。読者の皆さんからの忌憚のないご意見やご感想もお待ちしています。(mike.santarini@xilinx.com : 英語のみ)

# Xcell journal

|               |                                                                |

|---------------|----------------------------------------------------------------|

| 発行人           | Mike Santarini<br>mike.santarini@xilinx.com<br>+1-408-879-5270 |

| 編集            | Charmaine Cooper Hussain<br>Jacqueline Damian                  |

| アートディレクター     | Scott Blair                                                    |

| デザイン/制作       | Teie, Gelwicks & Associates                                    |

| 日本語版統括        | 全英守<br>hidemori.zen@xilinx.com                                 |

| 制作進行          | 竹脇美優紀<br>miyuki.takegoshi@xilinx.com                           |

| 日本語版 制作・広告・印刷 | 有限会社エイ・シー・シー                                                   |

japan.xilinx.com/xcell/

Xcell Journal 日本語版 65・66 合併号

2009 年 2 月 27 日発行

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400

ザイリンクス株式会社

〒 141-0032

東京都品川区大崎 1-2-2

アートヴィレッジ大崎セントラルタワー 4F

©2008 Xilinx, Inc. All Right Reserved.

XILINX や、Xcell のロゴ、その他本書に記載の商標は、米国およびその他各国の Xilinx 社の登録商標です。PowerPC は、米国または他の国における IBM 社の商標です。ほかすべての名前は、各社の登録商標または商標です。

本書は、米国 Xilinx, Inc. が発行する英文季刊誌を、ザイリンクス株式会社が日本語に翻訳して発行したもので。

米国 Xilinx, Inc. およびザイリンクス株式会社は、本書に記載されたデータの使用に起因する第三者の特許権、他の権利、損害における一切の責任を負いません。

本書の一部または全部の無断転載、複写は、著作権法に基づき固く禁じます。

Printed in Japan

## VIEWPOINTS

2

### Letter from The Publisher

Xcell Journal 創刊20周年 … 2

### Xpert Opinion

ピコセル ベース ステーション市場で FPGAが担う役割 … 10

ドライバ アシスタンス システムにおけるFPGAの可能性 … 14

### Xpectations

ユーザーそれぞれのニーズに応じたツールを使って

「パーソナル ベース設計」をしよう! … 44

単なるシリコンの提供にとどまらないザイリンクス

FPGAプラットフォーム … 47

## XCELLENCE BY DESIGN APPLICATION FEATURES

### Xcellence in Automotive & ISM

ザイリンクス FPGA プラットフォームで

ドライバ アシスタンス システムの

アルゴリズムを構築 … 17

ザイリンクス Spartan-3A DSPを使用した

セキュリティビデオ分析システム … 24

## THE XILINX XPERIENCE

### Xperts corner

JTAG チェーンを使った高精度システム

およびダイ内部の消費電力 … 30

FPGA I/Oピンの割り当てにおける

課題を解消 … 34

## XTRA XTRA

Tools of Xcellence … 39

## XCELLENCE IN COMMUNICATIONS

### Cover Story

4G ワイヤレスネットワークで

重要な役割を担うFPGA … 4

### 広告索引

リニアテクノロジー株式会社 … 表2-1

株式会社コンピューテックス … 13

株式会社ミッショナルテクノロジーズ … 29

アルデック・ジャパン株式会社 … 38

有限会社ヒューマンデータ … 43

メンター・グラフィックス・ジャパン株式会社 … 表3

Xcell Journalのご送付先住所等の変更は：

<http://japan.xilinx.com/xcell/henko/>

Xcell Journal の新規定期購読のお申込みは：

<http://japan.xilinx.com/xcell/toroku/>

# FPGAs: Primed for a Prominent Role in the 4G Wireless Network

## 4G ワイヤレス ネットワーク で重要な役割を担う FPGA

今後ベース ステーション市場はどのように展開するか

Mike Santarini

Publisher, Xcell Journal

Xilinx, Inc.

[mike.santarini@xilinx.com](mailto:mike.santarini@xilinx.com)

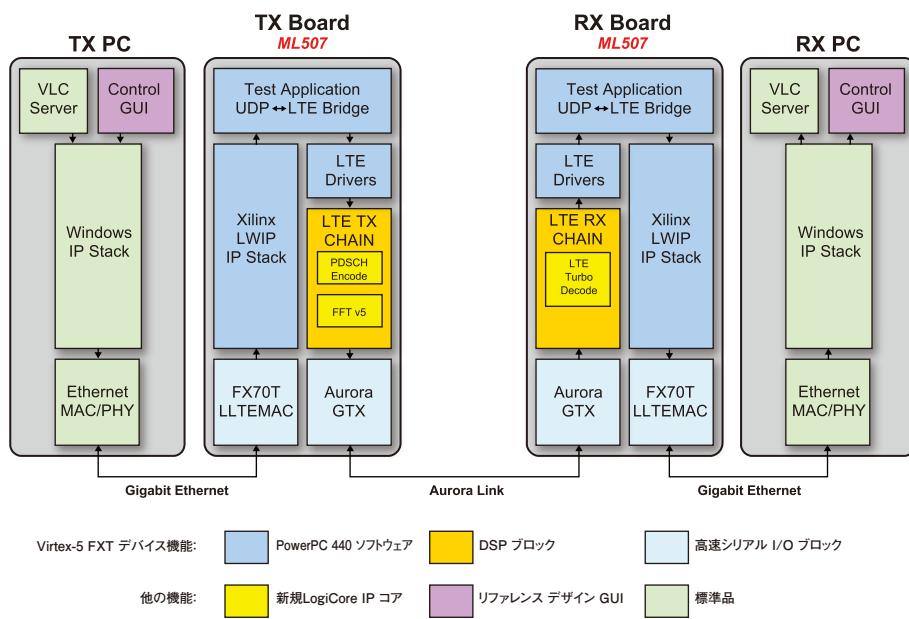

第3世代(3G)のCDMA2000やWCDMA/GSMのワイアレスネットワーク標準を3.9G LTE(Long Term Evolution)ワイアレスネットワーク標準に収束させる動きは、次世代ベースステーション(基地局)の開発者に少なからぬ課題を提示しています。現在の3G通信標準と次世代標準をサポートしながら、競合他社に勝てる次世代ベースステーションを開発し、さらに通信業界が採用するLTEに続く新しい標準に対応可能なソリューションを提供するには、どうしたらよいのでしょうか。

現在、この課題への対応として、多くの設計グループでは3G標準と4G標準をサポートし、マルチ標準としても知られているマルチモードベースステーション(この標準の変更型も含む)の開発に取り組んでいます。そのデザインには、システム仕様やターゲットのデザインがワイアレス標準の変化に対応できるように、十分な柔軟性が求められます。設計者の多くは、マルチモードベースステーションの設計に、今後はFPGAが中心的な役割を担うだろうと考えています(図1参照)。

## 4G標準の展望：LTEとWiMAX

LETはワイアレス市場向けに、現在の3Gネットワークの10倍の高性能を誇る100Mbps以上のデータレートを提供します。このデータレートでは、通信事業者やモバイルハンドセットメーカーは、各ネットワークやインターネット、Eメール、音声に加えてモバイルTV、先進ビデオ、ゲームなどのモバイルデバイスに先進機能を搭載して提供が可能です。

これは、モバイル機器メーカーはより進んだ電話機を通信事業者に販売できることを意味しています。また、通信事業者はさらに高級モバイル電話回線を提供し、加入者あたりの平均売上(ARPU)を増大させる

ことができます。

もちろんこの計画を遂行するには、通信事業者はワイアレスネットワークのインフラを整備する必要があります。

現在、全世界の70%はGSMベースのネットワーク(特に3G WCDMA)が使用され、北米や韓国では主に3G CDMA2000ネットワークが使用されています。日本の通信事業者は、今年の末にLTEの基礎となる直行周波数分割多重アクセス(OFDM)変調の試運転を計画しており、これは実質上LTE標準の採用を意味しています。

ザイリンクスワイアレスビジネス部門のシニアマーケティングマネージャであるManuel Uhmは、CDMA2000の次世代標準として、クアルコム社が提唱しているUMBは業界からの支持を得るのが困難な状況にあり、通信事業者が現在採用しているCDMA2000ネットワークもLTEに移行するものと考えています。

実際に、CDMA2000を採用している通信事業者のベライゾン(Verizon)社は、北米で周波数帯域700MHzのLTEを設置することを最近発表しました。また同社は最近、連邦通信委員会のオークションで、周波数帯域700MHzの入札にも成功しています。

業界関係者の多くは、2012年のタイムフレームまではLTEの大規模導入は行われないだろうとみているため、次世代ベースステーションを求めるワイアレス通信事業者は、より高速な4Gワイアレスネットワークへの性能向上のパスを提供する一方で、現在のネットワークベースで機能拡張が可能なハードウェアを探しています。同時に、ベースステーションの消費電力、すなわち光熱費の削減を含めて、各々のシステムやネットワーク全体の運用経費を最小にしたいと考えています。

CDMA2000とWCDMAはLTEに間違いなく収束されると見込まれますが、他の各国が同様にLTEネットワークを採用するかどうかは、今のところはっきりしていません。韓国のある通信事業者は、WiMAXとWiBroのようなデータ処理中心のネットワークを採用して、パケットによる音声

搬送機能を強化しようとしています。

EE Times社のマーケットインテリジェンスユニットのディレクタで、長年通信関連の編集を担当しているLoring Wirbel氏は、LTE標準とWiMAX標準はかなり酷似していると指摘しています。同氏の報告によると、ベースバンド機能の80%は同じ標準を採用しており、ベースステーションのベンダにとって、一基のベースステーションで、従来の3Gネットワークをサポートしながら4G標準もサポートできるシステムを構築する道が開かれています。

世界がLTE標準に収束するにしても、世界中のネットワーク通信事業者が1社残らずすべてがこの標準を採用するとは限りません。「過去に、エアーインターフェイス標準がWCDMAに収束するものと大方の予想では考えられていましたが、実際にはそうなりませんでした。」と、Uhmは指摘しています。

もちろん、歴史的に将来動向への兆候が考えられるなら、LTE標準が確立されると直ちに新しいニーズが提起されるでしょう。そのニーズが、ネットワークの性能であり、新しい機能/サービスであり、あるいは政治色の強いものであれ、5Gソリューションのニーズに拍車をかけるものであることは間違いないでしょう。またLTEの寿命を引き延ばすために、断続的な仕様の微調整が行われることもあるでしょう。

事実、3GPP(LTEを含むGSMのネットワーク標準を定義している国際団体)はLTEの定義を未だ完了していません。また、業界がLTE機器の展開を始めたばかりだというのに、団体はさらに上級標準のLTEなどの5Gネットワーク用の土台をすでに築きつつあります。

どのネットワークが最善で、実際どの標準がどのような形式で実現化されるのか、また、どのようなアプリケーションをサポートする必要があるのかなど詳細については、まだまだ不透明なところが多分にあります。従って通信事業者は、より高いリスクを回避するという意味でも、4G標準の仕様が変更された際に、より高い適応性と拡張性があり、最終的には低コストで修正可能なシステムに傾きつつあります。要す

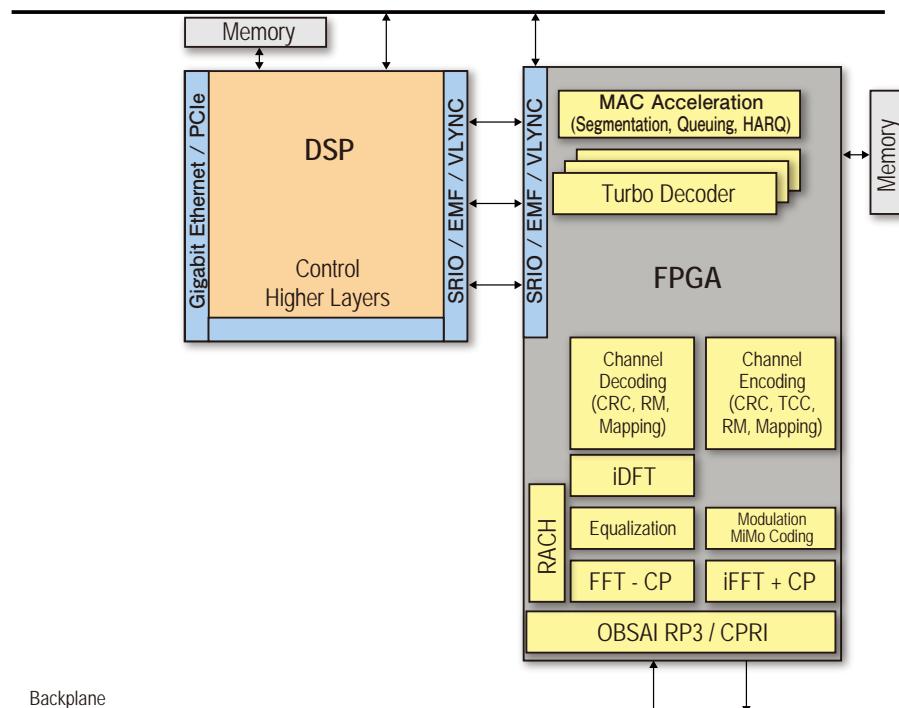

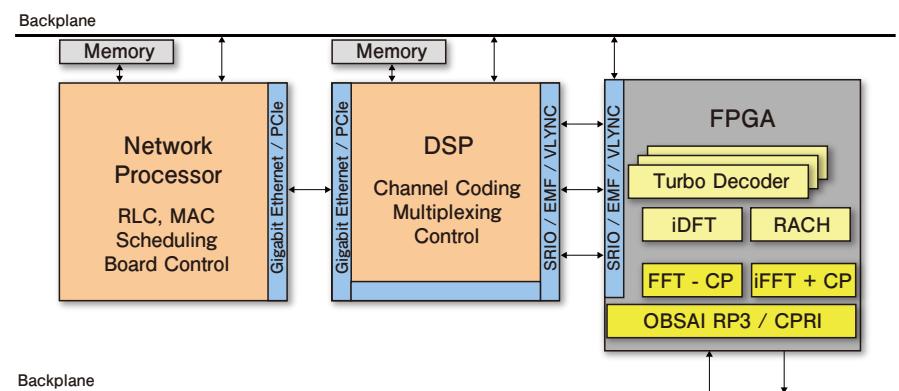

図1・ザイリンクスのLTEベースバンド用リファレンスデザイン

るに、いずれのシナリオでも、次世代ベースステーションには高い柔軟性が必要なのは明白です。

## 未定義の標準とマルチモードの機会

3GPP が未だにその標準化を完了していない現状もあって、今日、ベースステーションのベンダのなかで、特に市場への一番乗りを目指している企業は、デザインに高い柔軟性を取り込む必要があります。問題は、その柔軟性の程度をどこまで持たせるかです。

伝統的には、各ベースステーションベンダが全カードを交換する保守要員を派遣し、カード上で動作するソフトウェアを微調整するところに、その柔軟性を求めてきました。しかし、4G を導入しようとしている通信事業者は、これまで以上に高いレベルの柔軟性を要求しています。

実際、ワイヤレスネットワーク標準とネットワークそのものは、ハードウェア(PHY)とソフトウェアの2つの基本層で構成されています。それは PHY 層、すなわち物理層で、ネットワークがその標準

をサポートする際に必要となるハードウェアの性能要件と機能要件とを定義しています。一方ソフトウェア層は、各種のアプリケーションソフトウェアが、基本的ネットワーク標準を順守するために必要な機能を定義しています。

通信事業者は、同社の特定ネットワークを利用者に十分にアピールできるように、標準で基本的な PHY 要件とソフトウェア要件を凌ぐソフトウェアと強化用ハードウェアを追加しています。しかし 4G 標準では、ベースステーションにはこれまで以上に高い柔軟性が必要になると、多くの人が考えています。

将来、ベースステーション分野で、聖杯(至高の目標)となる製品を生産する時代が来ると予測している人もいます。この聖杯とは、どんな入力信号にも十分対応できるように、ベースステーションのハードウェアをソフトウェア化し、高速に再プログラミングすることにより、1つのシステムですべての標準をサポートできるソフトウェア定義無線(SDR)システムのようなものです。

3G ネットワーク時代の夜明けに、かつ

て新興企業の数社がプログラマブルロジックコアと配線接続された高性能ブロックを搭載した、特殊なチップを提供したことがある、と Wirbel 氏は指摘しています。しかし、これらのチップは、「驚くほどにプログラミングが難しく、かつ非常に高価なものでした。」完全に聖杯の観点に基づいた SDR は未だ発表されていませんが、ベンダの中には、標準の FPGA デバイスを使用して革新的な SDR サブシステムの生産を開始しているところもあります。近い将来には、SDR のサブシステムがベースステーションの分野に登場することになるでしょう。

しかしながら、Wirbel 氏を含む複数のアーリストは、次世代ベースステーションが、開発者の多くが予測し期待しているような拡張性の高いマルチモード対応になる、との確信が持てるにはもう少し時間がかかるだろうと予想しています。

「4G ネットワークは、OFDM をサポートしている WiMAX と LTE の2つの標準が調和をとって1組の標準に統一されることから、3G ネットワークよりも利用者の暮らしにもっとゆとりを持たせてくれそうです。最終的に WiMAX と LTE のいずれをサポートするかは、ソフトウェアで簡単に制御できます。」と、Wirbel 氏は述べています。「同時に両標準は、GSM と CDMA2000 の RF とベースバンド処理の全ての機能をサポートする必要があります。こうなると、ベースステーションがありにも複雑になってしまふので、ある時点で何をサポートするかの決断をする必要があります。」

「RF コンポーネントに起こる変化は、必ずしも魅力的なものばかりとはいませんが、ベースバンドと同様に重要です。」と、Heavy Readings 社のシニアアーリストで、ワイヤレス市場のスペシャリストの Gabriel Brown 氏は述べています。「理論的には、マルチモードに対応したアップグレードが可能なベースバンドが得られればよいのですが、適正な出力電力やバンド幅、あるいは周波数を備えた完全な RF チェーンでなければ、何も改善されたことにはならないのです。しばしばこの点が曲解され

ことがあります、多くの場合、これはなかなか実現不可能なことです。」

「もちろん、ソフトウェアでのアップグレードは可能ですが、そうするには RF チェーンがサポートされる必要があります。アップグレードが可能であるということは、それは同一技術分野内でのアップグレードを意味します。たとえば、ソフトウェアをアップグレードすることにより、同一のベースバンド ハードウェア上で、WCDMA から HSPA へ、あるいは HSPA+ へのアップグレードは可能です。しかし、異なる変調技術の世代間を移行できると考えるのは、少し楽天的過ぎます。実際は、そのようなことはありえないことです。」

## ■ ベース ステーションの中心部での戦い

ベース ステーションの心臓部には、ワイヤレス ネットワーク機能の多くを制御する一連の電子システムがあります。伝統的に、これらのシステムは、ASIC/ASSP や DSP などの標準品で構成されています。しかしこれらの技術は、設計グループが標準でしかも最新の仕様に合わせて修正するのは困難で、限界があります。また市場でハードウェアをアップグレードするには、さらに難しい技術が要求されます。

従って、ベース ステーションのベンダが、3G ネットワークをサポートしながら、未だ定義が完了されていない LTE 標準をもサポートする 4G ベース ステーションの設計を開始し、このシステムの制御に FPGA 技術に重要な役割を担わせるようになってきていることもうなずけるでしょう。

「5 年前のベース ステーションでは、FPGA はほとんど採用されていませんでした。」が、「今日 FPGA は、無線カードやチャネル カードにおいて重要な役割を担っています。」と Uhm は述べています。その理由の一つには、ベース ステーションのデザインでは、これまで以上に高い柔軟性が求められている市場ニーズを FPGA が満たしているためです、と Uhm は付け加えています。

従来の 3G ベース ステーションに変更を加えるにしても、当時は企業が選べるオプションはほとんどありませんでした。ソフトウェアの問題の修正やハードウェアの欠点を補うのに、ソフトウェアで継ぎ合わせることはできますが、これではハードウェアの処理時間が遅くなりベース ステーションの計算全体が遅くなってしまいます。LTE が登場した折には、逆にスピードを上げる必要があるのです。あるいは、技術者を作業現場に送り込んで、これらのデバイスを搭載した不具合基板や旧基板を新しいものと交換し、ソフトウェア パッチを追加することも可能です。

数年前、GSM から WCDMA に移行する際に AT&T が行ったように、追加の標準にサポートが必要なほど大きな仕様変更が生じた場合、通信事業者には新しいベース ステーションを設置する必要性が生じる場合もあります。もちろん、技術者を全世界の作業現場に派遣してハードウェアとソフトウェア プログラムを交換するとなれば、通信事業者のネットワークには莫大な維持費用が必要になってきます。たとえばその現場が、山の頂上、ビルの屋上、あるいは崖の端だとしたら、新しいベース ステーションを追加し、各現場においてリース契約を維持する費用は飛躍的に増加しますので、ことさらに大変なことになってきます。

「ベース ステーションのベンダは、各標準に準拠した個別のベース ステーションのネットワークを通信事業者に売り込みたいと思っているようですが、それでは通信事業者がアップグレードする機会は失われてしまいます。」と、Uhm は述べています。「通信事業者は、新しい収入源となるサービスや高いデータ レート、低消費電力、低メンテナンス コストに加えて、低コストで新機能を追加できる柔軟性を求めているのです。」

業界アナリストによると、何年も前のベース ステーションの価格は約 \$250,000 と非常に高額でしたが、昨今は \$15,000 ~ \$25,000 の範囲です。また、ベース ステーション ハードウェアのコストが全体のコストに占める割合はわずかで、リー

ス期間と維持コストがベース ステーションそのものの価格よりもはるかに高い、とアナリストは指摘しています。

さらに、ベース ステーションが複数の標準をサポートする必要がある場合、通常設計者は各標準に対して、ASIC と関連した基板を作成する必要があるのと同時に、既存のアンテナやボード間の通信を制御する追加回路の作成も行う必要があります。

特に、ベース ステーション市場のような比較的生産台数の少ない分野では、ASIC はますます高価なデバイスとなり、最先端のプロセス技術で製造するのは困難になってきます。従って、マクロセル、マイクロセル、ピコセルの各ベース ステーション市場での ASIC への魅力はますます薄れてきています。

65nm の ASIC マスク 1 枚で約 150 万米ドルの作成費用がかかり、45nm マスクではその倍になります。EDA と IP コアのコストを追加すれば、デザイン コストにさらに数百万米ドルが加算されることになります。シリコン ベンダにとっては、ASSP も同様に高価で、かつ製造技術も複雑で、通常のソフトウェア レベルでの変更しか行えません。ベース ステーションのアプリケーションに ASIC、ASSP、あるいは DSP のいずれかを選択するなら、DSP が最も融通性に富み、4G ベース ステーションの開発でも確かな地位を確保することでしょう。しかしながら、ソフトウェアのみの変更しかできないため、フィールドでデザインを変更する場合、その柔軟性には制約が生じます。

「問題が音声を扱う GSM 対 CDMA のみに限られていた場合は、すべてを DSP で処理するのが最善の方法でした。しかし EDGE や HSDPA などのデータ サービスを追加するようになると、FPGA ソリューションに目を向けるのが、実際には理にかなっていることだとわかってきました。」と、Wirbel 氏は述べています。「この FPGA への移行は、2002 年から 2003 年にかけて始まりました。」

デザイナが、マルチモード ベース ステーションの設計において、FPGA で中心的な役割を処理させるようになったのは、こ

ういった理由に起因します。マルチモードベース ステーションでのソフトウェア無線のインプリメンテーションで、FPGA を主要デバイスとして採用するケースさえあります。

「FPGA を採用した場合、ASIC や ASSP、DSP では不可能だった新しいレベルの柔軟性や性能をベース ステーションに追加でき、オペレータは新しいバンド幅指向のアプリケーションを追加することで、ARPU を増やすことができます。」と Uhm は述べています。「FPGA には、高性能信号処理用に複数のリコンフィギャブル リソースが混在しているため、マルチモード ベース ステーションにとっては非常に魅力的なデバイスです。」

Linley Group のシニア アナリストの Joe Byrne 氏は、FPGA がベース ステーション市場でより魅力的に思える理由の一つは、LTE が OFDM 変調を採用しているからだと指摘しています。「LTE のダウンストリーム変調スキームは OFDM であり、これは WCDMA とは異なるスキームです。」と、同氏は述べています。「次世代ベース ステーションは、基本的に 2 種の処理モジュールを装備した一台の機器になるものと考えられます。その 1 種は従来のプロトコルを処理し、一方他の機種では新しいプロトコルを処理します。この際よい機会なので、両方の処理を行う機器を作つてみはというのが私の考えです。それには何かプログラマブルな機能が必要になります。プログラマビリティについては FPGA の機能から得られますが、より伝統的なソフトウェア プログラマビリティを提供するもの、たとえば DSP などからも得ることができます。」

「OFDM についてですが、多くのキャリアがあるので、多くの信号をそのキャリア上で並列に搬送することができます。これは、並列に処理されなければならないことを意味しています。FPGA の側からみれば、処理すべきキャリアが数千ある場合、規模の大きな FPGA を使用し、これを小さな処理ユニットに並列に分割して、それぞれのキャリアの処理を行うことになります。シーケンスに処理するのではなく、並列に

処理するには FPGA を用いることが最適な手法であるといえます。」

「DSP のようなソフトウェア ベースのアプローチとは対照的に、FPGA のようなロジック ベースのアプローチは、システムとして微調整を常に行う必要がある場合に最適なアプローチになります。物理層自体はかなりよく理解されていると思うのですが、その物理層から最大の性能を引き出す実際のアルゴリズムは変わる可能性があり

ます。特に、市場に投入して間もない時期には、柔軟性を残しておいたほうがよいでしょう。」

Wirbel 氏は Byrne 氏と同意見で、次世代ベース ステーションは、DSP と FPGA タイプが混合し、それらが進化するものと信じています。「私は、将来のベース ステーションは、主要 DSP アーキテクチャをトップに置き、複数の FPGA 用の個別チャネルを中間に置いて、それらを混合／

## ベース ステーション 101

これまで、ワイヤレス ネットワークの通信事業者は、伝統的に、2 種類のベース ステーション（一般的にセルとも呼ばれる）を採用していました。第 1 のタイプはマクロセル（写真参照）で、これは通常高いタワーで構成され、タワーの上部に送信用無線アンテナと受信用無線アンテナを装備しています（通常受信用アンテナが最上部に位置します）。

これらのアンテナは、タワーの上部から下に向かって張られた光ファイバ ケーブルを経由して、従来のベースに設置されている電子システムへ信号を送ります。電子システムは、アンテナまでの送信機能と受信機能を調整し、他のベース ステーションと受信地域情報を交換し、利用者が一つのベース ステーションの受信地域から他のベース ステーションの受信地域に移動すると、ネットワーク上の残りのベース ステーションにコール データを送信して通話時間を記録します。通常、マクロセルの受信地域の範囲は広いので、通信事業者は農村地域やハイウェイの基盤に沿って展開しています。

従来型ベース ステーションの第 2 のタイプはマイクロセルと呼ばれています。ワイヤレス通信事業者は通常、これらを市街地などの人口過密地域で展開しています。マイクロセルの受信地域は、マクロセルの受信地域よりも狭いのですが、マイクロセルを多く使用すると、より多くの利用者がその通信事業者のワイヤレス ネットワークにアクセスできます。

近年この業界では、次に挙げる 2 種類のベース ステーション、すなわちピコセルとフェムトセルを生産しています。ピコセルは通常、空港や会議場、スポーツ会場のようにより狭い範囲で、しかも人口密度のより高い地域で使用されています。一方フェムトセルは、家庭や小さなオフィスをターゲットにしています。マクロセル、マイクロセルそしてピコセルは、伝統的にネットワークの通信事業者により販売されていますが、フェムトセルは、利用者に直接販売されたり、ケーブル TV や衛星 TV のような通信サービスと組み合わせて販売されたりしています。

「これまでフェムトセルは、過剰な宣伝をした割には、出荷台数はさほど伸びていません。」と Wirbel 氏は述べています。「このセルが実際に新しい市場として確立できるのか、あるいは価格帯をどこに設定したらよいのかも分かっていません。」それでも近年は、家庭でもより多くの電子機器がワイヤレス化しているため、フェムトセルの展開は興味ある試みといえるでしょう。

**典型的なマクロセル ベース ステーション：** 最上部は受信用アンテナで、その下に送信用アンテナがあり、そのベースの部分には制御システムが設置されています。

調整するようなタイプになると想っています。またそこが、将来ベースステーション市場が向かうゴールだと想っています。」と Wirbel 氏は述べています。

多くの設計者は、4G ベースステーション向けに、次のアーキテクチャを検討しています。図 2 と図 3 は、これらアーキテクチャにおける FPGA の使用例を示しています。柔軟性に加えて性能も 4G ネットワークの鍵となる、とアナリストは指摘しています。実際この性能改善には、多くの次世代ベースステーションの設計者が、計算機能をベースステーションタワー上部のアンテナのより近くに移動して、アンテナとベースステーション制御システム間の通信に必要な物理的時間を短縮できるよう努力しています。

Uhm によると、最新の FPGA は性能要件の向上を目指しており、その多くは高速 I/O を採用する傾向にあります。

## 5G 以上の場合

アナリストたちの間では、FPGA が 4G ネットワークで重要な役割を担うということでは意見が一致しているように思えます。しかし、どのメーカーが、5G ベースステーションのデータレートと機能セットの要件を予測して、処理可能なマルチモードベースステーションを構築できるかについては、多くのアナリストが疑問を抱いています。

「通信事業者は、ここ数年にかけて、3G ベースステーションに継続的なアップグレードを行ってきました。」と Byrne 氏は述べています。また「通信事業者は、7.2 Mbps から 10 Mbps に機能拡張するため、ベースバンドプロセッサ（現在は DSP か FPGA）のソフトウェアをアップグレードしています。私の考えでは、LTE では、もっと多くのアップグレードが行われるでしょう。大量のアップグレードを行うには、基本的に、新しいハードウェアが必要になります。」

5G が主流になるころまでは、非常に新しいハードウェア性能と機能要件が現れることになるだろう、と Byrne 氏などが指

摘しています。これは、ワイヤレスネットワークのすべての領域で、設計者に課題と機会があることを意味しています。

ザイリンクスはこれまで、ベースステーション市場向け FPGA 製品のみならず、設計ツールや IP コア、エンベデッドソフトウェアにも莫大な投資を行っている、と Uhm は述べています。またザイリンクスは、多くの IP コアパートナーやソフトウェアパートナーとの共同作業を積極的に

展開しています。これは、設計者が設計課題に対してより容易に対処でき、4G ワイヤレスネットワーク、特に世界的規模のワイヤレス通信の心臓部となるベースステーションに革新をもたらすことを支援するためです。ベースステーション市場に対するザイリンクスのソリューションの詳細については、<http://japan.xilinx.com/esp/wireless> をご覧ください。 ●

図 2 - DSP アーキテクチャでの FPGA の前処理

図 3 - LTE での FPGA のコプロセッサとしての使用例

# What Role Will FPGAs Play in the Picocell Base Station Market?

## ピコセル ベース ステーション 市場で FPGA が担う役割

ピコセル ベース ステーションが設置された空港で快適な旅を

Richard Wawrzyniak

Senior Market Analyst,

ASIC and SOC

Semico Research Corp.

[richw@semico.com](mailto:richw@semico.com)

2008 年後半に入って、原油価格高騰等により航空機の燃料費の上昇や、このコストを吸収するために航空会社各社において実施されたサービスの合理化などによって、空の旅がなかなか困難で、しかもあまり快適なものではなくなってきた。ある航空会社では、委託手荷物への追加費用を請求したり、サービスに使用する航空機の削減によって当然のように利用できる座席数が減ってきたりしています。

このような状況により、飛行機を利用する一般旅行者の心中は当然複雑で、ビジネスで利用する旅行者にとってはさらに深刻です。

では、FPGA はこれらの諸問題とどのような関係があるのかみてみましょう。

### 旅行者の緊張

世界のどこかゲート数の多い大規模空港を思い描いてください。おびただしい数の航空機が離着陸しています。多くの人々が

行き交い、連絡通路はその人々であふれています。そして旅行者は、乗り継ぎするために手荷物受取所に向かい、あるいは休憩場所を探しています。

あなたが同乗した便は、たった今到着したばかりと仮定します。あなたは一人で旅行している場合や、同僚と一緒にいる場合、あるいは家族と一緒にいる場合もあるでしょう。この空港にはなじみがなく、人々はみな外国语を話しているかもしれません。空港内のサインは、見なれない言語かもしれません。あなたの乗った便は遅れて到着するかもしれません。そんな時はいろんなことを瞬時に意思決定する必要があつたりします。

- ・次の便のゲートはどこにあるのか？

- ・私が今いる場所からゲートまでの距離は？走らなくてもそこに行けるだけの時間はあるのか？

- ・途中で食事（できればそれなりのレストランで）をする時間はあるのか？

- ・途中でどんな食事ができるのか？そこに、私や同僚、あるいは家族の口に合うものはあるのか？

- ・航空機内で、同僚が私の後ろの遠い席に座った場合、売店やレストラン、ゲート、およびフライト時間に関する必要な情報を得た際、時間をロスせず簡単に連絡する方法はあるのか？

- ・私のオフィスに連絡を取って、次の顧客訪問に必要なファイルを送ったりダウンロードしたりする必要があった場合、携帯電話の受信機のデータレートは、適度な時間で処理できるよう十分に高速なのか？それをしながら食事をする時間はあるのか？

- ・出発時に時間がなくて買えなかった誕生日プレゼントを購入できるようなショッピングはあるのか？限られた選択肢しかないのか？他に簡単に行けるショップがあつたりしないのか？

- ・一番近いトイレはどこなのか？

これらは、今日の多くの旅行者が経験する事例をかなり的確に反映したものでしょう。これは、私たち旅行者が飛行機を利用するたびに遭遇する一連の意思決定事例で

す。着陸する空港が我々にとって新しくてなじみがない場合は特にそうです。

四方八方から人に押されながら、乗客全員が同時に同じ行動をとっている場合、限られた時間内ですべてのデータを収集するにはどうすればよいでしょう。これは、多くの人々にとって、困難でストレスがたまる事柄で、そして確実に、今日の飛行機での旅の楽しみを多く奪い取ってしまうことでしょう。

## 平穏な空の旅

旅行者がこれらの課題を解決できるように、私が考えているソリューションのシナリオを紹介しましょう。

携帯電話市場が発展を続ける状況下で、常に新種の技術が生まれています。これには、広域を高速でカバーする WiMAX や WiFi などの通信インターフェイス ソリューションがあります。また、ピコセル ベース ステーションという新しい技術も出現してきました。

ピコセル ベース ステーションとは、携帯電話のベース ステーションとよく似ています。その違いは、ピコセルは大きな局地的ビルや空港、スポーツ スタジアムなどの大きな商業地区での利用を目的としている点です。現在の大規模な携帯電話の基地局とは異なり、ピコセル ベース ステーションは、それぞれの限られた利用者にサービスすることを目的にしています。ピコセル ベース ステーションの受信範囲は 30 ~ 60m と狭い範囲であるため、同時にサポートできる利用者数は 100 から 1,000 です。

このような制限があるため、国際空港や大きなスポーツ スタジアムなどの施設全体をカバーするには、ピコセル ベース ステーションがたくさん必要になるでしょう。この種のソリューションは、利用者が非常に高速なデータ レートを利用でき、サービスの品質を上げることがアイデアとなつて生まれたものです。

高速なデータ レートを利用できることで、たとえば、高品質のモバイル TV を提供することができます。また、ビデオ会

議が可能な環境も提供できます。これは、ビジネス旅行者にとって、旅行中でも生産性を上げる機会が得られるため、代価を支払う価値のあるものでしょう。

この記事を書いている時点（2008 年夏）では、ピコセル ベース ステーションは、次に挙げる多くの項目が解決されていないことを指摘しておかなければなりません。どのエリアにどの通信プロトコル（WiMAX あるいは WiFi）を使用するのが最適か、また、各ベース ステーションが最大どれだけの利用者をサポートできるのかもまだ分かっていません。加えて、そのステーションへの対価は誰が支払うのか、またそのサービスにアクセスするにはどのくらいコストがかかるものなのかも決定していません。

この種のサービスへのアクセスを可能にするには、携帯電話の側でも変化が生じるでしょう。事実、インテルを含む数社のベンダは、エアー インターフェイスを複数同時にアクティブにしてこれに対応可能な半導体ソリューションの開発を計画しています。

これらのソリューションは、2008 年末から 2009 年にかけて市場への導入が開始されるでしょう。適切な手段と機能の組み合わせには、まだまだ解決しなければならない課題があり、もうすこし時間が必要ですが、このソリューションは確実に市場価値を見出せるでしょう。

ピコセル ベース ステーションを設置した空港は、乗客にこれまでよりずっと快適な旅を提供できるでしょう。ベンダ企業は種々の新しい製品を開発して、その製品を多くの航空会社に販売できるでしょう。現時点では、ほとんどのベンダは、積極的な広告宣伝は行っていませんが、導入対象となる空港や企業への売り込みは既に開始しています。

ピコセル ベース ステーションを介してインターネットにアクセスし、ベンダが提供する製品やサービスを利用する状況を想像してみてください。旅行者は、空港レストランのメニューに遠隔地からアクセスでき、食事を注文し、必要であればテーブルの予約もできるでしょう。乗り継ぎのゲー

トに移動する際に、食事の代金を事前に支払っておいて、食事の準備をさせておくこともできるでしょう。

前述のリストに指摘したその他の問題に対しても、同じようなソリューションが適用できるでしょう。次のゲートはどこか、そこへ行くにはどの程度の時間が必要か、途中にどんなショップやレストランがあるのか、この情報を同僚に伝えるにはどうしたらよいのか、などです。これらすべての問題は、このようなシステムを設置することでその回答が得られるのです。

このようなシナリオを実現するには、金融取引に対して適切なレベルの安全性が確保できるように、ミドルウェアを追加する必要があります。これによって、ソフトウェア会社と施設所有者の双方は、一般旅行者へのサービス レベルを改善する作業に共同参画する機会が得られるでしょう。

### ピコセル ベース ステーションでの FPGA の役割

話を FPGA に戻しましょう。この記事に概要を示したタイプのシステムでは、各ピコセルのカバー範囲がかなり制限されているため、ピコセル ベース ステーション

の数が重要な意味を持ちます。全範囲をカバーしようとすると、システムの数が当然増加します。

このようなシステムに必要な機能に制限がある場合は、状況に応じて利用者の好みの変化を先取りし、提供するサービスの種類を素早く変更する必要があります。プログラマブル ロジックは、このような状況での使用において最適です。

ピコセル ベース ステーションは、大規模商業空間の天井のような高く、しかも比較的狭い場所に取り付けられることが予想されます。このようなケースでは、その設置場所の周りの空間はすでに使用されている可能性が高いので、新しい機器の設置に大掛かりな工事は行えないでしょう。建物の電源にシステムを接続することはできるでしょうが、そのシステム用に大規模な冷却装置などが用意されることは考え難いので、周囲温度条件で動作させる必要があります。これは、高性能化を保ちつつ低消費電力化を図るという今日のプログラマブル ロジックの動向にぴったりマッチします。

最後に、さまざまな環境下でピコセル ベース ステーションの設置数が多くなると、アップグレード用に回路基板を交換する際に制限が生じます。プログラマブル ロジック

は、再プログラミングが可能で、このようなニーズにも対応できる非常に最適なソリューションです。

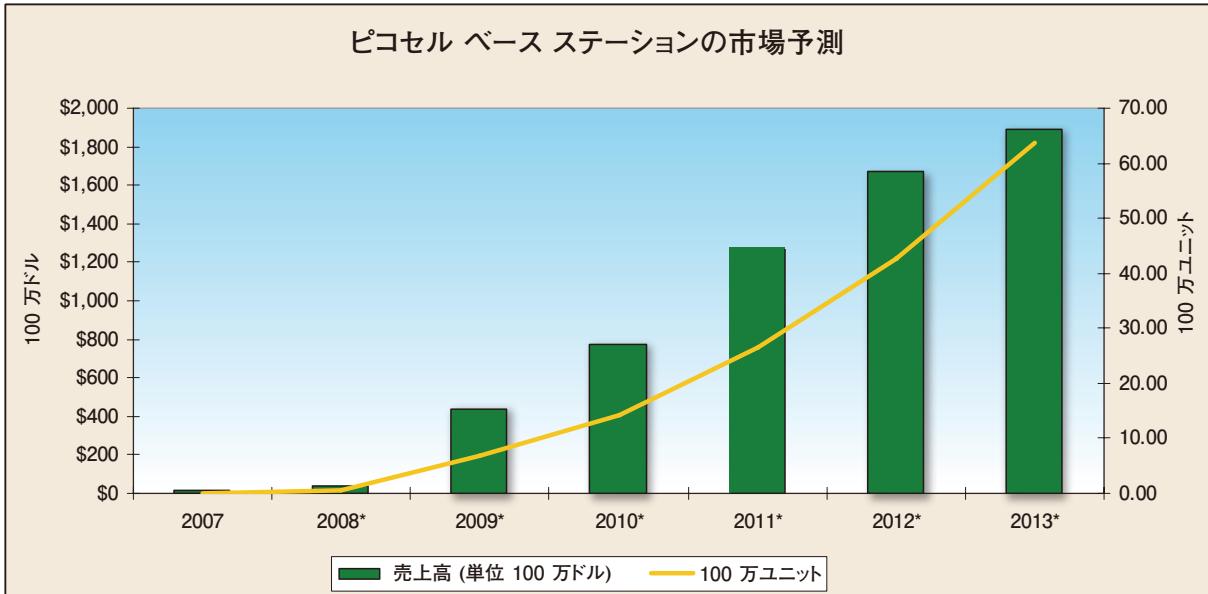

Semico Research 社は、この市場に対するリサーチにより、ピコセル ベース ステーションの概念とその中でプログラマブル ロジックが担う役割の双方に、現実的な可能性があると結論を下しました。

図 1 は、ピコセル ベース ステーション市場全体で、プログラマブル ロジックを含む半導体の使用予測を示します。プログラマブル ロジックの総売上の少なくとも 15% を占めるものと考えてよいでしょう。各システムには最少でも 1 個のプログラマブル ロジック デバイスが使用され、大きなシステムには 2 個以上が使用されると考えられます。

Semico 社の予測とおりこの市場が実際に実現されれば、プログラマブル ロジック 業界には、将来大きな成長の可能性と収益源が見込まれます。

プログラマブル ロジックにとってその将来は、輝かしいものとなるでしょう。また、旅行者には、ピコセル ベース ステーションで提供されるサービスにより、快適な空の旅が戻ってくるものと期待してよいでしょう。

図 1 - ピコセル ベース ステーションの市場予測

出典 : Semico Research 社

# F-Sight Xstick

エフサイト・スティック

ザイリンクス製 ソフトコアプロセッサ

MicroBlaze専用

FPGA

CPU

エミュレータ

## おいしいとこだけ いただきました♥

マルチ機能を誇るF-Sightから

ニーズの高い『おいしい』機能を抽出することで

シンプルな操作感とリーズナブルな価格を実現!

より多くの皆様に本格的デバッグ環境を

ご提供いたします。

- ソフトコア・プロセッサ MicroBlaze 専用

- CPU プログラムの Go/Break/Step 実行制御

- フラッシュメモリ・エリアでのデバッグOK(フラッシュメモリをサポート)

- アナライザで観測する信号を簡単に端子に引き出せるプローブング機能

- USB2.0 電源レス(Vbus)対応

- ロジック・アナライザ機能

- コンピューテックス製品共通のオペレーション 操作性抜群のデバッガソフト「CSIDE」装備

NEW

### 対応デバイス

Virtex-II / II Pro / Virtex-4 / Virtex-5

Spartan-3 / 3E / 3A / 3AN / 3A DSP

### 製品価格

155,400円 税込

(税抜/148,000円)

ライセンス費

サポート費込み

NEW

F-Sight Xstick

バンドル版

さらにおいしいロープライスな評価版(ボード限定)

F-Sight Xstick + ザイリンクス製 Spartan-3ファミリースターターキット

- コンピューテックス製デバッガソフトCSIDEを標準装備!

- 購入したその日からMicroBlazeの評価とデバッグを体験!

おいしいとこだけじゃなく全部いただきたいという方へ

手のひらサイズに一台三役マルチ機能搭載!

F-Sight

- CPUエミュレーション

- 高速コンフィギュレーション

- ロジック・アナライザ

CPUデバッグ

FPGAデバッグ

同時進行

**Computex** 株式会社 コンピューテックス

<http://www.computex.co.jp>

〒101-0047 東京都千代田区内神田二丁目15-2 内神田DNKビル7F

TEL 03-3253-2901 FAX 03-3253-2902 E-mail [sales@computex.co.jp](mailto:sales@computex.co.jp)

記載の会社名および商品・製品名は各社の商標または登録商標です。

コンピューテックス

※詳しくは、弊社ホームページをご覧ください。

検索

# Driver Assistance Systems Pose FPGA Opportunities

## ドライバ アシスタンス システム における FPGA の可能性

自家用車にも話題のインテリジェンス機能がまもなく登場

Colin Barnden

Principal analyst

Semicast

[colin.barnden@semicast.net](mailto:colin.barnden@semicast.net)

\* 本記事は 2008 年 10 月に米国にて発表されたものです。本文中に記述のある市場予測などの情報は現在のそれと差異がある場合があります。あらかじめご了承ください。

過去 10 年間で自動車業界における最も重要な課題の一つに、安全システムの迅速な導入が挙げられます。エアバッグ、アンチロック ブレーキやタイヤ空気圧監視などの機能は、今後ますます多くの新車に標準装備されるようになってきます。その背景には、それら機能の利点がドライバに認識されしてきたことに加え、道路の安全性の向上を確保して自動車事故による死亡者数を削減できるように、法規制により装着が義務化されたこと等が考えられます。ドライバの安全性への取り組みは、衰える兆しはまったくみれず、むしろドライバは一般的に「ドライバ アシスタンス」と呼ばれている新世代システムにますます興味を抱き始めています。

新しいドライバ アシスタンス システムは、従来の安全システムとは少し異なります。このシステムの主な目的は、事故につながる可能性のある条件を検出した場合、ドライバに向けて警報を出し、予防的処置をとることにあります。これとは対照的に、

従来のエアバッグのような安全システムは「最後の防御線」で、衝突事故が発生した場合のみに起動します。

ドライバ アシスタンス システムの機能やユーティリティとして最も求められるのは、日常の運転経験を観察し、ある問題が発生した際にそれを事前に支援して予防できるシステムでしょう。

## 車線逸脱警報

一日中会議をした後に、車で家に戻るところをイメージしてみましょう。あなたは高い緊張状態から開放され、多少リラックスし、道路の前方に完全に集中していないでしょう。そんな状況で、iPod のプレイリストを変更している間に、車が車線から外れ、危険にも隣の車線の車にどんどん接近します。これを十分チェックできないと、あなたは安全に家に戻れなくなるでしょう。

このような状況下での支援システムとして、車線逸脱警報システムは車の前方に搭載されたセンサを使用して道路前方のマークを「監視」し、高速演算を行う複雑なコンピュータと組み合わせてハイウェイ上の車の位置を検出します。車が車線の範囲内にとどまっているればよいのですが、インジケーターやこのシステムを使用していて右や左に大きくぶれると、システムはこの動作を検出して警報音を自動的に鳴らします。

車線逸脱警報はいささか必要以上の無駄な機能にも思えますが、実際これは非常に重要です。それは、幹線道路交通安全局(NHTSA)の統計によれば、米国だけでも車線変更による事故で毎年負傷者の数は約13万人にものぼります。自動車メーカーはこの安全性の利点にすでに気づいているはずです。

新しい技術では、多くの場合がそうであるように、欧州の自動車メーカー数社が一歩先に進んでいます。現在車に車線逸脱警報を搭載しているのは、欧州勢では Audi Q7 SUV と BMW 5シリーズ、米国勢では GM 社がこのようなシステムを搭載した Buick とキャデラックをすでに出荷しています。一方日本勢では、日産とトヨタの両

社が車線逸脱警報を搭載した車の製造を開始しています。

## 死角と暗視

別のシナリオを考えてみましょう。ハイウェイを車で一時間運転して、カーステレオを大音量で流し、車速制御装置を使用しているとします。トラックを追い越すときに、車線からはみ出しが安全かどうかの確認を忘れ、あなたを同時に追い越そうとしている小型車がミラーの死角に入ったために、一瞬その車を見失いました。

死角監視システムを搭載している車では、このようなアクシデントは避けられるでしょう。死角監視技術は、カメラモジュール、あるいは、車の左右の死角を常に追跡する短距離レーダーを使用します。車線を外れて追い越そうとすると、このシステムは死角に車があることを検知して、そのような危険を警報にて知らせます。

別のドライバ アシスタンス技術としては、夜間でも走行できるように設計されたものがあります。暗視アシスタンス システムは、その名が示すように、夜間に従来のフロント ヘッドライトの照射距離よりもずっと遠い前方の物体を認識するためのシステムです。暗視アシスタンス システムは、IR(赤外線) 照射カメラもしくは熱画像カメラを使用して、道路前方の強調画像をコソール中央のスクリーンに表示します。

## インテリジェント自動速度制御装置

ドライバ アシスタンスのもっとも有用な例は、おそらくインテリジェント自動速度制御装置でしょう。従来の自動速度制御装置の最大欠点の一つは、「設定してそのことを忘れてしまう自動システムであることで、ドライバがボーッとして道路の前方に注意を払っていないと、文字通り壁にぶつかってしまいます。これとは対照的に、インテリジェント自動速度制御装置システムは一般的にレーダーを使用して、車の直接前方にある物体までの距離をリアルタイムに測定し、スロットルを制御してブレーキをかけ、速度を調節します。

さらに安全性を高めるための最も進んだシステムには、インテリジェント自動速度制御機能とエアバッグ システム機能を組み合わせた予測衝突警報があります。このシステムは、間もなく衝突すると判断した際に、衝突が起こる前にシートベルトのプリテンショナーを駆動してドライバと前部座席の乗客をもっとも安全な体勢に保持させます。

## 活況を呈する市場予測

表1は、ドライバ アシスタンス システムの世界市場をシステムの出荷台数で表したものです。

ここでわかるように、ドライバ アシスタンス システムへの興味が今後ますます強くなることが見て取れます。車線逸脱警報 システムの出荷台数は、たとえば、2007年の100万台以下から、2012年ではほぼ1,150万台にまで上昇すると予測しています。さらに、インテリジェント車速制御は、次の5年間で急速に受け入れられるものと期待されます。それは、現在は高級車にのみ搭載されているこの機能が、大量生産の大衆車へ移行が加速されると予想されるためです。Semicast 社の予測では、ドライバ アシスタンス システムの出荷台数は、昨年は全体で約300万台であったのに対して、2012年には2,300万台にも増加します。

出荷台数の伸びは、半導体部品の付随的な上昇を意味しています。表2は、ドライバ アシスタンス システムで使用される半導体の世界市場を、売上高で示したものです。

Semicast 社の予測では、ドライバ アシスタンス システムにおける半導体の売上高は、2007年から2012年までのCAGR(年間平均成長率)が約33%、2億2千9百万米ドルから9億2千6百万米ドルと予測されています。つまり、総合車載半導体市場では、2007年で合計200億米ドルだったものが、年に約5.5%成長すると仮定すると、2012年には270億米ドルになるということです。明らかに、ドライバ アシスタンス シ

**表 1 - ドライバ アシスタンス システムの出荷台数

(単位 : 百万台)**

|              | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | CAGR  |

|--------------|------|------|------|------|------|------|-------|

| 車線逸脱警報       | 0.9  | 2.5  | 4.5  | 6.9  | 9.9  | 11.5 | 65.9% |

| 死角監視         | 0.3  | 0.6  | 1.1  | 1.6  | 2.6  | 3.6  | 60.9% |

| 暗視アシスタンス     | 0.8  | 1.3  | 1.4  | 1.9  | 1.9  | 2.4  | 24.4% |

| インテリジェント車速制御 | 1.1  | 1.7  | 2.6  | 3.6  | 4.9  | 6.1  | 41.8% |

| 合計           | 3.1  | 6.1  | 9.6  | 14.0 | 19.3 | 23.6 | 49.9% |

**表 2 - ドライバ アシスタンス システムでの半導体に対する世界市場 (単位 : 100 万米ドル)**

|                     | 2007 | 2008 | 2009 | 2010 | 2011 | 2012 | CAGR  |

|---------------------|------|------|------|------|------|------|-------|

| MCU/MPU/DSP         | 54   | 94   | 136  | 182  | 232  | 260  | 36.8% |

| ASIC/ASSP/ その他のロジック | 12   | 28   | 46   | 63   | 82   | 89   | 49.8% |

| FPGA                | 55   | 107  | 133  | 155  | 173  | 182  | 26.8% |

| オプトエレクトロニクス         | 93   | 144  | 185  | 240  | 284  | 318  | 28.0% |

| その他の半導体             | 15   | 28   | 39   | 54   | 67   | 77   | 38.2% |

| 合計                  | 229  | 400  | 540  | 693  | 838  | 926  | 32.2% |

システムは、次の 5 年間の車載半導体市場で、これまでに最も成長率の高い領域の一つになるでしょう。

ドライバ アシスタンス システムで半導体の売上高の成長率が最も高いのは、光電子工学の分野で、とりわけ、CCD と CMOS のイメージ センサとミリメータ波レーダー モジュールがその主要部品であると予測されています。次に成長率が高いものは、MCU や MPU、DSP で、これらは、ハイエンドの制御が要求されるため、成長は 32 ビット デバイスに限定されるでしょう。

## FPGA の可能性

歴史的に、自動車 OEM メーカが、特定アプリケーションの要求を満たすために、高度にカスタマイズされたロジック製品が必要になった場合、何のためらいもなく、メーカの要件に合わせてゲート アレイやスタンダード セル ベース製品の開発を行う ASIC ベンダに目を注いきました。過去 5 年間で、ASIC の開発コストは上昇し開発期間も長くなってきたため、自動車 OEM メーカは他のソリューションを考え

体企業にとってアプリケーションのコストや消費電力、信頼性の目標を満たす標準の ASSP 開発は非常に困難なものとなっています。

ドライバ アシスタンス システムを開発している自動車 OEM メーカは、コストや柔軟性、さらに Time-to-Market などの要件を満たすために、ますます FPGA に注目しています。FPGA は過去 10 年間、多くの車載システムの開発やプロトタイプに使用されてきましたが、量産コストを最小化する目的で、量産移行前に ASIC に置き換えられることがほとんどでした。しかし、FPGA のユニット コストが下がり続けた関係で、ずっと高い生産台数まで利用することが経済的に可能となりました。FPGA は、デザイン工程の後半で変更できるという他に類を見ない高い柔軟性を提供するだけでなく、多くのドライバ アシスタンス システムで要求される高速計算解析を実行するようにコンフィギュレーションした際卓越した性能を発揮します。この 2 つの組み合わせは非常に強い武器となります。

表 2 のデータが示すように、Semicast 社は、ドライバ アシスタンス システムにおける ASIC および ASSP の役割が早々

ざるを得なくなりました。

システムによって、たとえばエンターテイメントやナビゲーションなどには、一般的なニーズを満たす標準 ASSP を開発して成功している半導体ベンダもあります。しかし、ドライバ アシスタンス システムにおいては、デザイン変更が頻繁に行われることもあり、ASIC が採用されるのはまれなことです。また、各 OEM メーカは複雑で個人的な要件を抱えており、各半導

に終焉をむかえるとはまったく予測しておらず、システムのデザイン要件が安定してくれれば、ASIC/ASSP は引き続き使用され続けることになるでしょう。

しかし、Semicast 社は、次の 5 年間にドライバ アシスタンス システム向け FPGA の本格的な成長を予測しています。2007 年の 5,500 万米ドルから、2012 年には 1 億 8,200 万米ドルと、成長率は 25 パーセントを超えると予測しています。車載アプリケーションにおける FPGA 市場は、加速化しており、ドライバ アシスタンスはその分野のリーダー的な存在です。

平均的なドライバにとって、ドライバ アシスタンス システムは、不必要でしかも高価な贅沢品と思われるかもしれません。もちろん、エアバッグやアンチロック ブレーキが導入されたときもまったく同じようなことが言われましたが、事故等による死者や負傷者の数を減らし道路の安全性を改善する役割は、政治家に認められるまでに長い時間がかかったわけではありません。

ドライバ アシスタンス システムの重要性や需要の増大は確実なもののように思えます。この技術を駆使して道路安全性への関与のデモを行っている自動車メーカーはますます増えています。これらのシステムが、エアバッグや ABS (アンチロック ブレーキ システム) とまったく同じ方法で人命を救うわけではありませんが、重大な局面で道路の安全に貢献することは確実です。この技術は、最善の技術がすべてそうであるように、その必要性が認められるまではその存在を認識することはできませんが、あって良かったと心から感謝することになるでしょう。

## 著者について

Colin Barnden 氏は、Semicast 社の Automotive Electronics & Entertainment Systems Service の主席アーリストです。彼は 14 年間市場アーリストとして活躍し、1999 年から自動車工業界を調査報告してきました。彼は、英国、アストン大学から電子工学の学士号を取得しています。

# Building Automotive Driver Assistance System Algorithms with Xilinx FPGA Platforms

## ザイリンクス FPGA プラットフォームでドライバ アシスタンスシステムのアルゴリズムを構築

System Generator for DSP は抽象化レベルの高いデザインツールで、HDL コーディングを行うことなく Simulink ベースのアルゴリズミック リファレンス モデルから FPGA ハードウェアへのインプリメンテーションを効率的に実現

Daniele Bagni

DSP Specialist

Xilinx, Inc.

[daniele.bagni@xilinx.com](mailto:daniele.bagni@xilinx.com)

Roberto Marzotto

Design Engineer

Embedded Vision Systems, S.r.l.

[roberto.marzotto@evsys.net](mailto:roberto.marzotto@evsys.net)

Paul Zoratti

Automotive Senior System Architect

Xilinx, Inc.

[paul.zoratti@xilinx.com](mailto:paul.zoratti@xilinx.com)

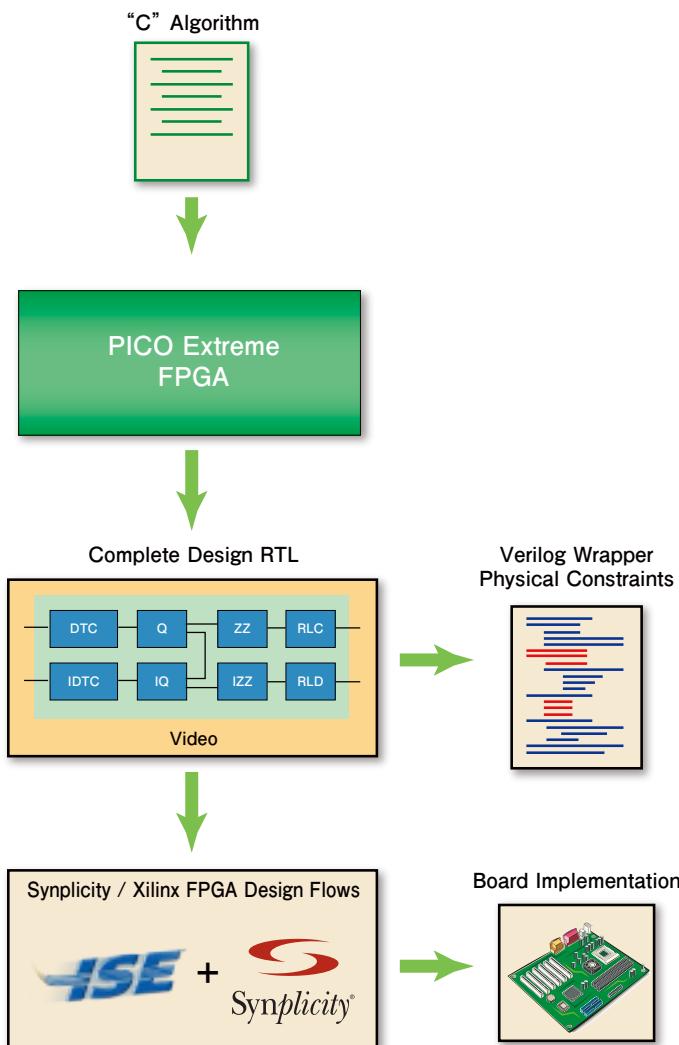

車載ドライバ アシスタンス システムのマーケットには、高性能デジタル信号処理と量産アプリケーションに見合う低コストデバイスが求められています（本誌内記事「ドライバ アシスタンス システムにおける FPGA の可能性」を参照）。ザイリンクス FPGA デバイスは、これら 2 つの対照的な要件を満たすプラットフォームを提供しています。しかし、FPGA のインプリメンテーション手法にじみの薄いアルゴリズム開発者のなかには、PC ベースのアルゴリズム モデルから FPGA ベースのハードウェア プロトタイプへの移行における複雑さに危惧の念を抱いている方もいるでしょう。そのような心配は、まったく無用です。

ザイリンクスの System Generator for DSP を使用すると、Simulink の PC ベース モデルから、リアルタイム FPGA ベースのハードウェア インプリメンテーションへ効率的かつ容易に移行ができます。この抽象化レベルの高いデザイン ツールは、ザイリンクスと Embedded Vision Systems 社間で共同運営されたプロジェクトにおいて、中心的な役割を担いました。このプロジェクトの目標は、ザイリンクス FPGA に自動車用車線逸脱警報システムを適用できる画像処理アルゴリズムをインプリメントすることでした。この作業には System Generator for DSP が使用されたのですが、全体的に高い性能を得ることと、低成本でしかも開発期間を短縮する

ことが焦点となりました。

## DA システム開発の課題

車載ドライバ アシスタンス (DA) システムは、適応型車速制御や車線逸脱警報、歩行者検知などの機能で、高い信頼性が必要とされるため、通常は PC ベースのモデルを使用して複雑な処理アルゴリズムを生成しています。PC ベースのアルゴリズムモデルが高い価値を得ている理由には、このようなモデルを使用すると、異なる処理オプションを実験し迅速に評価できることがあげられます。しかし最終的に、量産と市場への展開を実現するには、適切にデザ

インされた電子機器のソリューションが必要になります。

展開可能なターゲット ハードウェアとソフトウェア アルゴリズム モデルとの間でアルゴリズム性能の一貫性を検証するには、多くの開発者にとって難しい問題があります。浮動小数点から固定小数点の計算に移行（たとえば、三角関数に異なる計算方法を採用する）すると、リファレンス ソフトウェア アルゴリズムとハードウェア インプリメンテーション モデルとの間での出力に、かなりの差異を生じる場合があります。DA システム開発者にとって、アルゴリズム性能の一貫性問題をさらに複雑にしているのは、入力スティミュラスが極

めて非決定性であるという事実です。これは、一般的に、遠隔測定デバイス（カメラ、レーダーなど）からの入力に依存している DA システムにとって、ドライバが遭遇する車線条件と環境条件によって、入力には信じられないほどの多様な種類が存在するためです。エンジニアにとって、全ての状況に適合した処理用アルゴリズムを開発することは極めて困難で、またソフトウェア モデルとその電子機器インプリメンテーションとの間の整合性を検証することも大きな課題であることがわかります。

画像処理を含む多くのアプリケーションにとって、ザイリンクス Spartan®-3 FPGA デバイスのパラレル リソースは、VLIW DSP プラットフォームの価格性能比に比べ、高い性能を提供します (Xcell Journal 英語版 63 号掲載記事を参照：[http://www.xilinx.com/publications/xcellonline/xcell\\_63/xc\\_pdf/p16-19\\_63-block.pdf](http://www.xilinx.com/publications/xcellonline/xcell_63/xc_pdf/p16-19_63-block.pdf))。しかしながら、システム デザイナーのなかには、FPGA をプログラムする唯一の方法は VHDL のようなハードウェア記述言語を使用することだ、という間違った考えを今でも持っている方もいます。しかし、これは事実ではないのです。ザイリンクスのデザイン手法や Simulink モデリング ツール、System Generator for DSP FPGA 合成ツールを使用すると、FPGA デザインを容易にかつ効率的にインプリメントできるだけでなく、ハードウェアとソフトウェアの協調シミュレーションにより、アルゴリズムの整合性テストを加速することも可能になります。さらに、System Generator for DSP を使用するには、HDL に精通している必要は一切ありません。

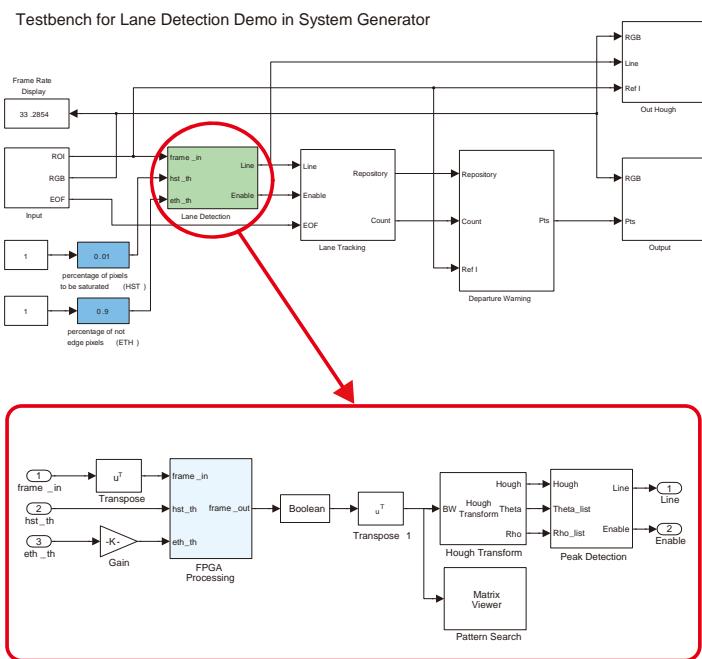

図 1 - LDW Simulink ハイレベル ブロック図

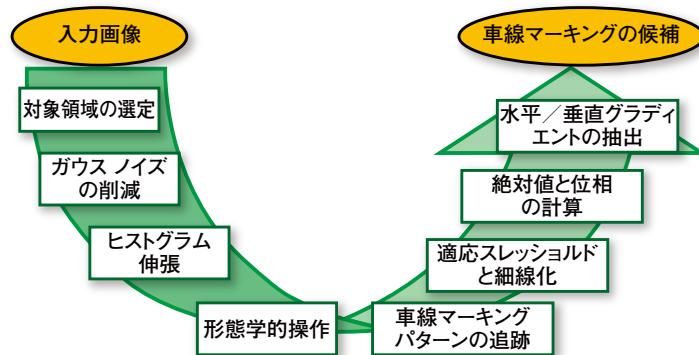

図 2 - LDW 処理機能チェーン

## 車線逸脱警報モデルの説明

車線逸脱警報 (LDW) システムは、車が不慮意にハイウェイの車線からそれた場合にドライバに警報を発します。車の先に設置したカメラが車道の画像を取り込み、車線の境界を示しているマーキングを識別します。このシステムは、これらの境界とそれに対する車の位置関係を継続的に追跡し

ます。車が車線の境界線をよぎると、このシステムは警報を発します。

自動車業界および研究機関では、アルゴリズムとシステムレベルのデザイン ツールとして MATLAB と Simulink を広く採用しています。特に、Simulink は、抽象化レベルが非常に高く、ツールのグラフィックス回路図入力機能を備えているため、自動車用アルゴリズム エンジニアは洗練された DSP アルゴリズムを迅速かつ容易に開発できます。

図 1 は、Simulink でデザインされたザイリンクスの LDW システム モデルのトップレベルのブロック図を示します。「Lane Detection（車線検出）」とラベル付けされた緑のブロックには、画像処理サブシステムが含まれています。このサブシステムの種々のステージは、図 2 に示されています。車線検出機能の目的は、車線の境界を表す可能性が高い車道画像の特徴を抽出することにあります。

ノイズに対するエッジ検出の性能を改善するために、パイプラインの最初のステージは、2 次元  $5 \times 5$  のガウシアンノイズ フィルタ です。第 2 のステージは、ヒストグラム伸張で (HST)、これはできる限り全体のグレー レベル範囲を利用して、開発者が画像のコントラストを強めるためのテクニックです。第 3 のステージは、水平／垂直グラディエント (HVG) で、局所的明暗度に大きな変化があった場所のピクセルを強調します。開発者は、画像の 2 次元  $5 \times 5$  のグラディエント（勾配）を計算することで HVG を実行します（2 次元ユークリッド距離経由で）。

エッジ細線化 (ETH) ブロックは、グラディエントの絶対値がある基準値でカットし、細い輪郭曲線（1 ピクセルの厚み）を生成するために非最大抑制を適用して、どのポイントがエッジなのかを判断します。車線マーキング パターン追跡 (LMPS) はフィルタとして動作し、車線マーキングと矛盾しない特定の構造を示すエッジ ポイントのサブセットを選択して、影、他の車、木、信号などの偽のエッジ ポイントを取り除きます。パイプラインの最後のステップは  $3 \times 3$  の形態学的フィルタリング

(MRP) で、システムはこれを車線マー킹候補者マップの最後のクリーニングとして使用します。

この Simulink モデルで、Simulink ブロックセット ファンクションと MATLAB ブロックを併用して画像処理サブシステムの各種ステージをインプリメントしました。FPGA は、並列ハードウェア パスにより大容量データを処理する能力を持っているため、ザイリンクスのモデルの車線検出ファンクションをインプリメントするのに適しています。従って、このファンクションを出発点のターゲットにして、LDW Simulink デザインから FPGA への移行を行います。

この作業分割により、FPGA はそれぞれのフレームの処理指向型ピクセル レベル解析を行い、その後の処理が容易になるよう、10 ビットの諧調画像から単純なバイナリ画像に変換してデータを削減することができます。全体のシステム設計には、XA Spartan-3A DSP 3400 をターゲットにしましたが、少し小さい 3A DSP 1800 や 3E 1600 でもこの設計に適合できます。

## System Generator for DSP の概要

System Generator for DSP デザインツールは Simulink 内で動作します。これは、Simulink 用ザイリンクス DSP ブロックセットにより、自動的にザイリンクス CORE Generator™ ツールを起動して、DSP ビルディング ブロック用の高度に最適化されたネットリストを生成します。ザイリンクス DSP ブロックセットは、Simulink ライブラリ プラウザからアクセスできますが、すなわち、標準 MATLAB ツールバーからの起動もできます。DSP システムの構築には、90 個以上の DSP ビルディング ブロックが使用できます。DSP システムとしては、FIR フィルタや FFT、FEC コア、エンベデッド処理コア、メモリ、数値演算ブロック、論理ブロック、ビットワイス ブロックなどがあります。すべてのブロックは、サイクル正確とビット正確になっていますから、それらをコンフ

ィギュレーションする際には、応答遅延、領域対スピード性能の最適化、I/O ポート数、量子化や丸めの設定が行えます。

Gateway-In と Gateway-Out と呼ばれる 2 つのブロックが、FPGA システムと Simulink シミュレーション モデルの境界を定義します。Gateway-In ブロックは浮動小数点入力を固定小数点数値に変換します。その後ツールは、固定小数点分解能で生じたビット数の増加のすべてを正しく管理します。その管理は、それに続くファンクション ステージの間にインプリメントされた数値演算オペレーションに依存します。

Simulink は MATLAB の上位に構築されているため、System Generator for DSP では、入力信号生成と出力解析に MATLAB 言語をフルに使用できます。Simulink の Source ライブラリと Sink ライブラリから From-Workspace と To-Workspace ブロックを使用して、MATLAB 変数 (From-Workspace) から入力信号を読み出し、あるいは信号の途中結果を MATLAB 変数 (To-Workspace) に格納できます。さらに、MATLAB 変数経由で System Generator ブロックのたくさんのパラメータを設定できるため、これらの変数をすべて含む MATLAB スクリプトを変更するだけで、デザインをカスタマイズできます (MATLAB ファンクションをこのモデルに割り当てることができるため、それをオープンする前にコールバックしたり、シミュレーションの開始前あるいは終了後でもコールバックしたりできます)。

System Generator for DSP の別の重要な機能は、ハードウェアとソフトウェアの協調シミュレーションです。デザインの一部をターゲット FPGA ボード（ハードウェア モデル）に合成し、残りの部分をソフトウェア モデルとしてホスト PC 内に留めておくことができます。これにより、ソフトウェア モデルからハードウェア インプリメンテーションへの増分的移行が可能になります。ツールの透過性が、イーサネットと共有メモリ経由で（ホスト PC とターゲット FPGA の間で）通信用インフ

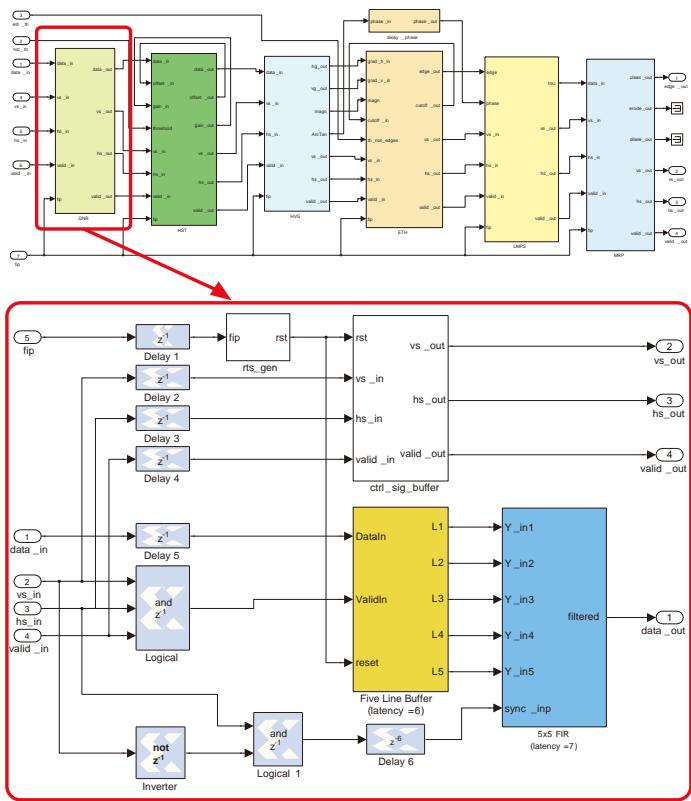

図 3- トップレベル処理とガウスノイズ削減のダイアグラム

図 4-4 ラインバッファの System Generator for DSP によるインプリメンテーション

ラを生成し管理します。このように、シミュレーションを行う際は、ハードウェアにインプリメントした部分は実際にターゲットシリコンデバイス上で実行され、ソフトウェアモデルは残りの部分をホストPC内でエミュレートします。共有メモリを使用して、たとえば、入力画像と生成された出力画像を格納しておくことができます。イーサネット通信は、擬似リアルタイム処理に必要な帯域幅を提供しています。この詳細に関しては、ユーザマニュアルをご覧ください。

ソフトウェアモデルとハードウェア処理の柔軟な分割と、ハードウェアとソフトウェアの協調シミュレーション機能を組み合わせることで、オリジナルなソフトウェアだけのアルゴリズムと生産目的のハードウェアインプリメンテーション間の整合性を測定することができ、しかも強力な検証ツールも利用できるようになります。Simulinkそのものを使用して、ソフトウェア処理データとハードウェア処理データの結果を比較することができます。この機能は、システム入力画像が非決定性であるドライバアシスタンスアプリケーションで、特に有用です。

それでは簡単に、画像前処理パイプラインの最初のモジュールである GNR の例を使って画像処理アルゴリズムを System Generator for DSP にモデル化する方法を詳細にみてみましょう。

### System Generator for DSP による GNR 機能のインプリメンテーション

明暗度の不規則変動 (aka ノイズ) は、画像を壊してしまうことがあります。このような変動はガウス分布、すなわち正規分布をしており、異なるセンサ (すなわち、CMOS カメラ) 間では非常に一般的なものです。線形平準化フィルタでガウスノイズを取り除くのがよい方法です。多くの場合、他のノイズも除去できます。このような機能を遂行するには、連続するウインドウ内のピクセルの加重和を使用する線形有限インパルス応答 (FIR) フィルタをインプリメントします。

図 5 - FIR (コンボリューション) フィルタの System Generator for DSP によるインプリメンテーション

GNR System Generator ブロックのインプリメンテーションを開始する前に、そのビヘイビア モデルを MATLAB 内に実現します。このインプリメントに必要なコード ラインは 2 行のみです。最初にカーネルを計算し、その後マスク サイズ（この場合は  $5 \times 5$ ）とガウス分布のシグマを指定します。そして、入力画像をコンボリューション（畳み込み）で次のようにフィルタリングします。

```

n_mask = fspecial('gaussian', 5, 0.8);

out_img = conv2(in_img, n_mask, 'same');

```

このビヘイビア モデルを使用してフィルタを実際のビデオ データでテストする

ことにより、マスクの係数を合わせることができます。System Generator for DSP サブシステムの出力が MATLAB ファンクションの出力に、指定の精度の範囲内で等しいことを検証することにより、ハードウェアの正当性を立証できます。それは、MATLAB が浮動小数点で動作するのに対して、System Generator for DSP は固定小数点演算を使用しているためです。

2 次元 GNR モジュールは、入力画像をストリーミング手法（すなわち、ラインごとに）で処理します。図 3 は、全体の処理チェーンに対するトップレベル System Generator ブロック図とガウス ノイズ削減機能特定のトップレベル ダイアグラム

を示します。

図 3 の data\_in と data\_out のポートは、それぞれ、ピクセルの入力ストリームを受信し、フィルタリングしたストリームを返します。残りのポートは、タイミングの同期と隣接ブロック間の処理制御に使用されます。

GNR ブロックの内部アーキテクチャを 2 つのメイン サブシステムに振り分けました。図で黄色と青色にハイライト表示されたものがそうです。これらのブロックそれぞれについて、System Generator デザインを詳細にみていくましょう。

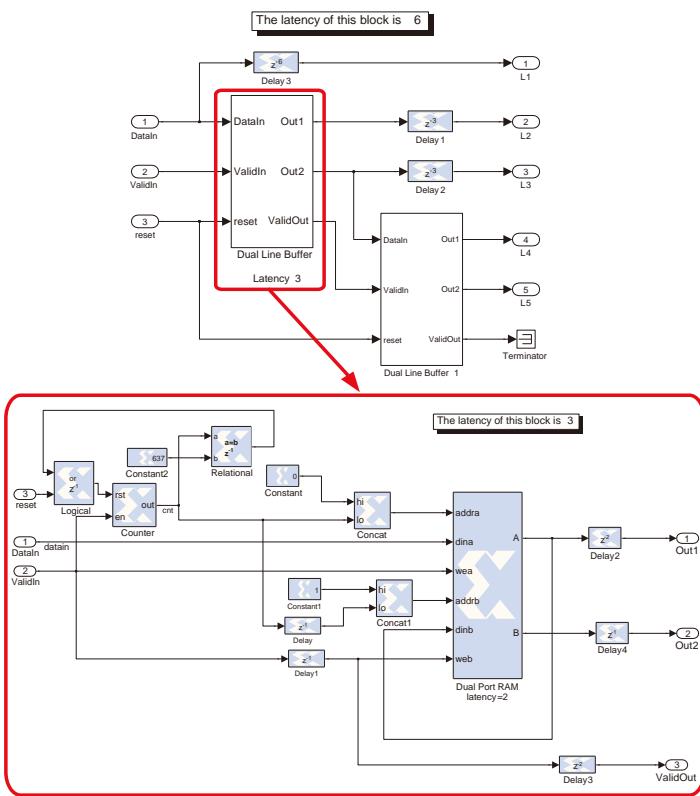

まずはメイン サブシステムです。ラインバッファ（黄色で表示）は、 $5 \times 5$  に整列したピクセルを出力するために、入力画像

図 6 - LDW 处理モデルの出力

ストリームを 4 ライン分バッファリングします。それぞれの入力ピクセル  $I(u,v)$  に対して、ラインバッファは、現在のピクセルと前の 4 つのピクセルと同じ行に並べて、すなわち  $[I(u,v-4); I(u,v-3); I(u,v-2); I(u,v-1); I(u,v)]$  で構成した  $5 \times 1$  のベクトルを返します。図 4 では、それぞれがデュアルポート ブロック RAM (FPGA デバイス内に在駐するメモリリソース) を使用する 2 つのデュアルラインバッファを連結することでラインバッファ ブロックをインプリメントし、また、メモリアドレッシング用カウンタや適切な遅延を作るためのいくつかの簡単なバイナリロジックとレジスタをインプリメントしました。

青色の陰影とザイリンクスのロゴは、System Generator のプリミティブ ブロックを示し、それぞれが最適化合成可能な HDL コードに対応しています。このグラフィカルインターフェイスにより、アルゴリズムの開発者は HDL コーディング技術の知識がなくても、System Generator for DSP を使って DSP アルゴリズムをハードウェアに容易にインプリメントすることができます。

第 2 のメインサブシステムとして、 $5 \times 5$  の FIR カーネル（図 3 に青色で表示）を、コンボリューション演算をインプリメントするために使用します。これは、

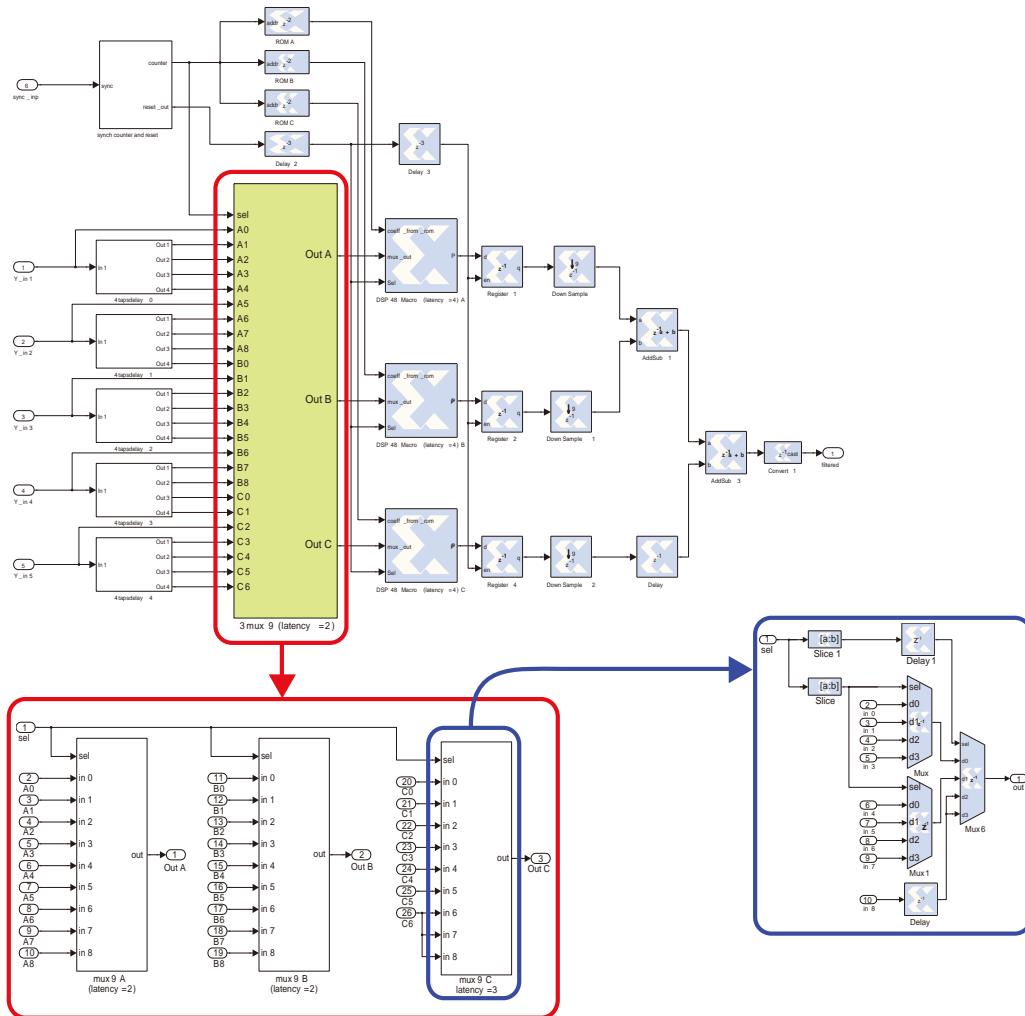

ラインバッファ ブロックからの 25 ピクセルのブロックを受け取り、ガウスマスクの 25 個の係数を乗算して、累算した結果をレジスタに入れます。図 5 にそのインプリメンテーションの詳細を示します。ターゲットデバイスの性能を指定されたサンプルレート、毎秒 900 万サンプル (MSPS) にあわせるために、3 つの乗算累算器 (FPGA の DSP48 プログラマブル Multiply Accumulator ファンクションユニットを使用してインプリメントしました) を並列に使用する手法を採用しました。それぞれに最大で 9 個の乗算を、時分割マルチブレクシング（図 5 のトップダイアグラムの大きな System Generator ブロックを参照）を介して割り当てました。マスクの 25 個の係数のセットを、分散 RAM (FPGA が提供する別のメモリリソース) でインプリメントされた 3 つの ROM に分けて格納しました。

このインプリメンテーションでは、マスクの係数をコンパイル時に固定することにしました。また、デザインを簡単にアップデータしてこれらの値をリアルタイム入力として受け入れるようにすることもできました。このようにすることで、環境条件に基づいて、フィルタリングのランタイム明暗度をダイナミックに変更できます。（インプリメンテーション上の注意：ガウス

分布が等方向性であることから、カーネルを 2 つの個別のマスクに分割して、フィルタリングを 2 つの連続したコンボリューションで行うこともできます。この際使用的マスクは、水平方向と垂直方向に沿った  $1 \times 5$  と  $5 \times 1$  のマスクとなります。このアプローチでは、必要な FPGA のリソースが少なくてすみますが、これを採用しなかったのは、汎用性が失われてデザインがわかり難くなるためです。）

System Generator for DSP が提供するこのほか強力な機能として、あらかじめ組み込まれた MATLAB ファンクションを使ってして、デザインをコンパイルする前にカスタマイズすることが可能です。System Generator モジュールのパラメータ（画像の解像度、FIR カーネル値や計算精度ビット数など）を設定し、ランタイム シミュレーション時に使用するワークスペース信号を初期化することで、異なる処理方法と異なる入力データセットで迅速かつ容易に実験を行うことができます。さらに、シミュレーションを完了した後に、MATLAB 関数 Stop を呼び出すことで、有用な情報を計算し、固定小数点結果を浮動小数点のリファレンス結果と比較して、その結果を表示します。この手法により、アルゴリズム開発者は、ハードウェアインプリメンテーションのどの部分でも綿密に解析し、それをオリジナルのソフトウェア モデルと比較して整合性を検証できます。

### System Generator を使った FPGA 合成結果

ドライバ アシスタンスシステムを開発する人々は、量産に見合うコストレベルでデザインをインプリメントする必要があります。あるレベルの処理性能を達成するのに必要なダイのリソースは、FPGA デバイスの必要サイズを決定するため、コストも決まってきます。

この車線逸脱警報のプリプロセッサインプリメンテーションでは、現在ザイリンクス自動車製品ラインで使用できる最大デバイス、XA Spartan-3A DSP 3400 をターゲットにしました。しかしながら、前処理機能で使用されるリソースを解析した

ところ、明らかに、このデザインはずっと小さいデバイスにも適用できることがわかりました。次の表は、GNR ブロックが XA Spartan-3A DSP 3400 デバイス上で占有するリソースを表しています。この予測には、VGA 解像度が 30Hz フレーム レート（この場合入力データ レートが 9.2 MSPS になります）で諧調レベル入力画像を仮定しています。

|       |           |    |

|-------|-----------|----|

| DSP48 | 3/126     | 2% |

| BRAM  | 3/126     | 2% |

| スライス  | 525/23872 | 1% |

タイミング性能の観点からすれば、GNR デザインは 168.32MHz のクロック周波数で動作するため、入力データ レートは最大 18.72 MSPS となります。

車線検出処理サブシステム全体に必要な全リソースを以下に要約します。

|       |            |     |

|-------|------------|-----|

| DSP48 | 12/26      | 9%  |

| BRAM  | 16/126     | 12% |

| スライス  | 2594/23872 | 10% |

対応するタイミング性能解析によれば、クロック周波数は 128.24MHz、最大入力データ レートは 14.2MSPS となります。

これらのリソース要件が与えられれば、予測される前処理機能は XA Spartan-3E 500 (XA Spartan-3A 3400A デバイスの約 1/7 の集積度) にも適合できます。

## 結果と将来性

図 6 は、車線マーキング候補者を抽出する FPGA ベースの画像前処理機能を含む、LDW システムの性能のサンプルです。右側に入力フレームとなる実際の画像が 2 つ表示されています。左側にある 2 つの画像は、FPGA にインプリメントした前処理機能の性能を示しています。左上の画像は、スレッショルド操作（ある基準値以下のものを捨てる）をした後のエッジ検出ファンクションの絶対値を示しています。左下のものは、エッジ細線化と車線マ

ーキング パターン追跡処理の後の画像です。LDW プロセッサは、車道の風景を取り込み、主な車線マーキングの候補だけにデータを減らしていることがわかります。右の上下画像のそれぞれ黄色と赤色のラインは、簡単な直線車道モデルに基づいて車線境界を瞬時に追跡予測したものです。

車線境界に対する車の軌道を正確に予測するために、将来の LDW システムには曲線モデルを使用するつもりです。現在は、車道の幅は局所的に一定で平面的であるものと仮定して、物体空間の放物線車道モデルを採用しています。位置や角度、曲率を考慮した 4 つのパラメータを生成することで放物線車線を記述します。厳密な意味の適合技術を使用すれば、ビデオ シケンスのそれぞれのフレームに対する 4 つのパラメータを予測することができます。

ノイズ、ライトの変化、カメラのジッタ、車線マーキングの欠落やタールの剥がれは、このモデルの抽出機能を弱めます。この情報のギャップを補完し、この段階の処理をより確実で信頼性のあるものにするには、トラッキング（追跡）ステージが必要になります。このトラッキングは、車線モデルのパラメータ空間で、カルマン フィルタを使用して行うことができます。

車線モデルの抽出と追跡は、まもなく我々が FPGA にインプリメントしようとしている次のステージです。この作業には、もう一つのザイリンクス ハイレベル DSP デザイン ツールである AccelDSP™ 合成ツールの使用を計画しています。これは線形代数ライブラリをサポートしているため、4 ステートから 6 ステートのカルマン フィルタをインプリメントすることができます。

AccelDSP は、MATLAB コードからゲートを直接生成できるため、相乗的に System Generator for DSP と一緒に使用することができます。さらに、AccelDSP 合成ツールは、実現可能性分析と高速プロトタイピングに適しています。AccelDSP は、オリジナルの浮動小数点 MATLAB を固定小数点に自動的に量子化し、種々の MATLAB 命令を FPGA リソース内にマッピングします。このツー

ルは、ザイリンクスがドライバ アシスタンス アルゴリズムのデザイナとシステム設計者に提供する最も使い易い DSP ツールといえるでしょう。

要するに、ドライバ アシスタンス技術に取り組むアルゴリズム デザイナとシステム設計者は、今日では、洗練度の高い DSP デザイン ツールを使用してリファレンス アルゴリズム モデルを構築し、これらのモデルをザイリンクス FPGA の低コスト デバイスに容易にインプリメントできるようになったというわけです。それによって、高品質、高性能かつ低コストが同時に得られます。

System Generator for DSP のもう一つの重要な機能として、デザインの一部をシリコン ターゲット デバイス（イーサネット経由で接続されている特定のボード上の）にインプリメントして、残りの部分をホスト PC 上で実行できます。このようなハードウェアとソフトウェアの協調シミュレーションにより、ハードウェア ビヘイビアの検証が容易になり、シミュレーションの処理速度を加速できます。

このように、LDW システムに対する画像前処理パイプラインの生成に、ザイリンクス System Generator for DSP を使用しました。ここでは、あるモジュール、GNR 2 次元 FIR フィルタ、の一部についての詳細を説明したに過ぎませんが、全体の車線検出前処理機能（図 2 参照）には、XA Spartan-3A DSP 3400 デバイスのわずか 12 個の DSP48、16 個の BRAM、2,594 個のスライスを使用し、128.24MHz の動作で、VGA 画像解像度に必要とされるより 50 パーセント高い 14.2MSPS の入力データ レートを実現しています。全体のアルゴリズム デザインと FPGA のインプリメンテーションには数週間の作業が必要でしたが、VHDL コードを書く必要はまったくありませんでした。

次は、AccelDSP デザイン ツールで車線モデルの抽出とトラッキングをインプリメントし、これらのステージを System Generator for DSP モデル内に統合するプロジェクトを行う計画です。 ●

# Security Video Analytics on Xilinx Spartan-3A DSP

## ザイリンクス Spartan-3A DSP を使用したセキュリティ ビデオ分析システム

ザイリンクス FPGA の並行処理機能とエンベデッド、DSP 処理をビデオ分析処理に活用

Csaba Rekeczky

co-CTO and Vice President

Eutecus, Inc.

[rcsaba@eutecus.com](mailto:rcsaba@eutecus.com)

Joe Mallett

Senior Product Line Manager

Xilinx, Inc.

[jmallett@xilinx.com](mailto:jmallett@xilinx.com)

Akos Zarandy

co-CTO and Vice President

Eutecus, Inc.

[zarandy@eutecus.com](mailto:zarandy@eutecus.com)

広範なセキュリティ分析アプリケーションに求められるバンド幅要件は非常に厳しく、システム ハードウェアへのアプローチ方法において課題を投げかけています。ある計算指向型分析演算を許容できるデータレートで行うには、1 つのビデオと画像用 DSP プロセッサでは不十分です。また、高品位 (HD) 解像度を完全なビデオ フレーム レートで取り扱い、信頼性が高く堅牢なソリューションはこれまでみたことがあ

りません。これは、システム エンジニアにとって、マルチチップ システムか代替のシングルチップ システムを考えるよう促していることになるのですが、両ソリューションには利点も欠点もあります。

複数の DSP で構成されるマルチチップ システムは、デザイナになじみの深いデザイン フローを提供しますが、反面 PCB (基板) のコストが上昇し、ボードやシステムに余分なスペースが必要となり、システム性能における課題が発生する可能性があります。他方、シングルチップ ソリューションは、一見して、コストやフットプリント、消費電力では有利にみえますが、潜在的には、デザイン プロジェクトが複雑化し、デザイナのラーニングカーブ (経験曲線) は厳しさを増し、そのエンジニアリング コストは跳ね上がります。以上のような要因により、製品のリリースは遅くなる可能性があります。

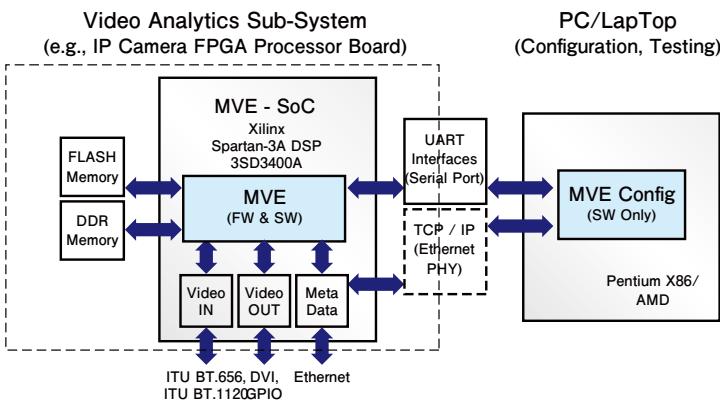

当 Eutecus 社は、カリフォルニア州、バークレーに本社を置くビデオ分析会社で、次世代分析製品、Multi-core Video Analytics Engine (MVE™) のシステム仕様を決定する際、同様なジレンマに直面しました。

第 1 世代の製品は、テキサスインスツルメンツ (TI) 社製の DaVinci Digital Media System-on-Chip プラットフォーム上にインプリメントされました。しかし第 2 世代については、さらなる処理能力とシステムの統合性が求められました。Eutecus は、マルチデバイスの DSP ソリューションは、費用対効果が低く、またあまり効率の良いシステムではないと判断しました。我々の旧製品で開発した IP コアが容易に移植でき、MVE 用にもっと追加・修正ができる、シングルチップのソリューションが必要でした。

調査開始後すぐに、ザイリンクスの

Spartan®-3A DSP 3400A を知りました。このデバイスは、126 個の専用 XtremeDSP™ DSP48A スライスを提供しているため、我々のシステム要件に十分対応できる性能を持っていました。加えて、魅力的な価格で提供されていました。

さらに、Spartan-3A DSP がザイリンクスのエンベデッド開発キット (EDK) でサポートされていることを知り、移行に伴う懸念事項はただちに払拭されました。この EDK を使用すると、ザイリンクスの MicroBlaze™ エンベデッド プロセッサベースのデュアル プロセッサ ハードウェア アーキテクチャを容易にインプリメントできます。これは、我々が TI 社の DaVinci プラットフォームで使用したデュアルプロセッサ ハードウェア アーキテクチャに似ています。

ここでデバイスが決定したので、従来の DaVinci コード ベースをザイリンクスのデュアルプロセッサ エンベデッド システムに移植し、シングルチップ分析のデザインに着手しました。高品位ビデオを完全なフレーム レートで処理し、我々の正確な性能要件を満たすように、アクセラレータ ブロックの的確なセットを FPGA ファブリック内に生成しました。その結果誕生した製品が MVE (Multi-core Video Analytics Engine) で、これは航空宇宙や防衛、マシーン ビジョンや監視などの市場向けに販売されています。

## ビデオ分析器の概要

Multi-core Video Analytics Engine は、InstantVision Embedded™ ソフトウェアで使用することが可能で、多くの機能と能力を備え、特化された Cellular Multicore Video Analytics (C-MVA™) によって構成されています。

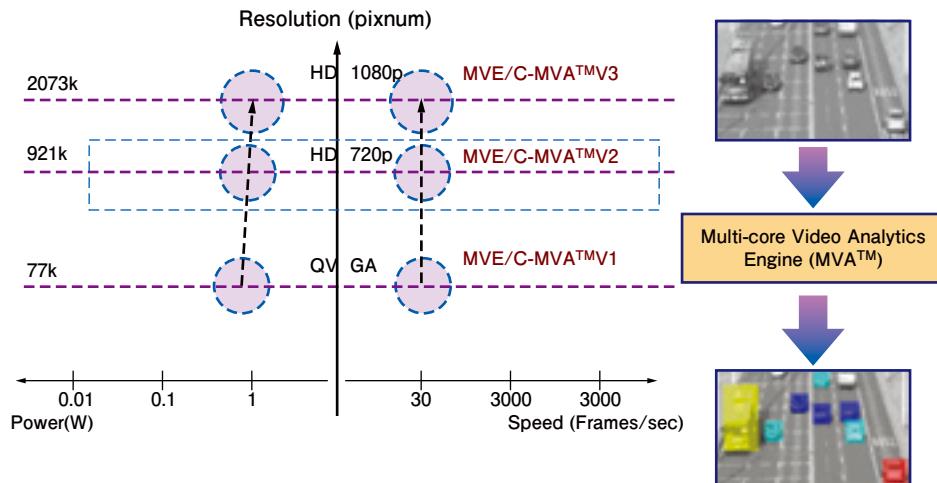

MVE/C-MVA の最新版は、ビデオ フレーム レートで HD の高解像度のデータを取り扱うことができます。しかも消費電力は 1 ワット以下で、複数の事象の検出と分類のアルゴリズムを平行して実行できます。図 1 は、ビデオ分析による交通監視の出力例を示しています。ここでは、車種、

図 1 - マルチコア ビデオ分析エンジン (MVE) とアプリケーション例のロード マップ

表 1 - 一般的な事象検出アプリケーションでサポートされているビデオ分析機能

| C-MVA で実行可能な事象検出例             | Ver. 1 | Ver. 2 | Ver. 3 |

|-------------------------------|--------|--------|--------|

| すべての移動する人物や車、その他物体の検出とカウント    |        |        |        |

| 人物や車、その他物体の検出、カウント、分類         |        |        |        |

| 指定された運動方向／逆方向に移動している物体の検出     |        |        |        |

| 遺失物や盗難物、禁止区域への乗り入れ、車線逸脱の検出と分類 |        |        |        |

| ジェスチャー や 特色のある運動経路の検出と分類      |        |        |        |

| 混雑時の特異な行動の検出と分類               |        |        |        |

進行方向、車線変更や車線逸脱などが、すべて異なる色で同時に示されています。

我々は、C-MVA プロセッサを有する理念の下に設計しました。それは、演算機能を大幅に拡大して、密集した物質空間での分析機能をサポートするというものです。これには、重なり合った不完全な物質／事象の分析が必要とされ、そこが特に難しいところでした。従来のアプリケーションを特定した DSP では、この種の機能とプロセッサ スケーリングをサポートするのは極めて困難でした。FPGA 内ではずっと柔軟に行えます。

ザイリンクス Spartan-3A DSP 3400A FPGA の 126 個の XtremeDSP DSP48A スライスは、30 GMAC の DSP 性能があり、ビデオ分析

の厳しいコストと性能要件によく適合しています。ザイリンクス FPGA を使用すれば、将来のビデオ分析機能と、当社製品に求められるニーズに関連した事象検出例を構築できます。それらを表 1 にまとめます。

さらに、ザイリンクス FPGA と ISE® Design Suite ツールは、ユーザーごとのソリューションにあわせてカスタマイズできる柔軟性も提供しています。標準ビデオと高品位ビデオ処理の両方を迅速にプロトタイピングすることにより、ビデオ分析エンジンとシステム オン チップ (SOC) ソリューションをニーズに合わせて調整できます。これにより、顧客ニーズに合わせて、Spartan-3A DSP 3400A と低コスト Spartan-3A DSP 1800A

デバイスで利用できるリソースを有効活用できます。

FPGA ソリューションはさらに、同じハードウェア プラットフォームを使用していろいろな形式の最終製品を設計できるという別の利点も提供します。我々はこれまで、VHDL を使用して複数の分析アクセラレータ エンジンをデザインしてきましたので、特定のコアを C-MVA コプロセッサに搭載することができます。このアプローチにより、デュアル MicroBlaze エンベデッド システムを再利用して、異なる FPGA プログラミング ファイルを作成でき、分析アプリケーションに合わせて容易に変更が可能でスケーラブルなソリューシ

ョンを手にいれることができました。

### DaVinci からザイリンクス FPGA への移行

当社のビデオ分析器の前世代製品は、ARM9x プロセッサと C64x+ DSP コプロセッサを含む TI 社の DaVinci Digital Media System-on-Chip TMS320-DM6446 をベースにしていました。我々のデザインでは、ARM9x を通信と制御に、C64x+ を分析アルゴリズムの DSP 処理に使用しました。しかしながら、この組み合わせでのシステムは、第 2 世代製品が必要とする処理要件には十分対応できませんでした。そこで、Spartan-3A DSP FPGA

ファミリに移行することにしました。

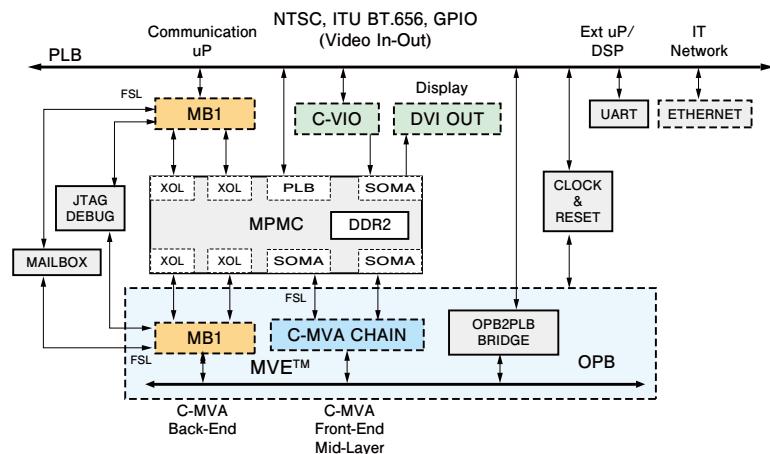

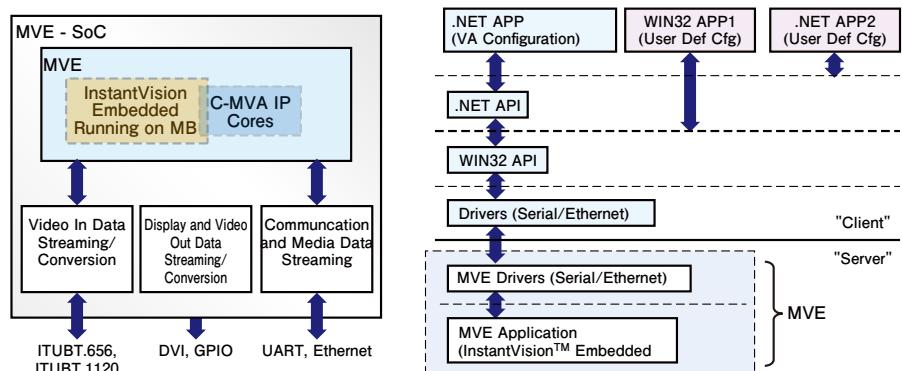

独立して動作する 2 つの MicroBlaze v7 ソフトコア プロセッサを含むザイリンクス エンベデッド システムを構築することで、デザインの移行作業は容易に実効できました。このアーキテクチャにより、ARM と DSP プロセッサのコードを別々に移植することができ、デザインの移行が大いに簡素化されました。図 2 は、Eutecus ハードウェア システムと MVE ベースのリファレンス SoC デザインのブロック図を示しています。

MVE エンジンは、MicroBlaze (MBO) で実行される InstantVision Embedded ソフトウェア、MidroBlaze (MB1) のシステム制御と通信、そして FPGA ファブリック内で実行されるハードウェア アクセラレータ IP コアのモジュール チェーンとして設計された C-MVA コプロセッサで構成されています。

ARM と DSP のコード移植は、ザイリンクス ISE Design Suite と MicroBlaze ソフト コアを使用することで、簡単に行えることがわかりました。Eutecus の InstantVision クロス プラットフォーム 環境の特筆すべき長所は、それが高級標準言語 C/C++ で書かれていることで変更の必要がないことです。

コードを移植した後、動作検証を行いその正確さを確認し、性能上のボトルネックを特定できました。まず、TI 社 プロセッサ用に開発した C/C++ コードを発展させることは、このプラットフォームのアセンブリ レベルの最適化の際に、DaVinci C64x+ コプロセッサ アクセラレータ ブロックを使用して行う必要があり、結構大変なチャレンジであることがわかりました。そこで、これらブロックを高級な C ファンクションで置き換えることから始めて、一連のステップを踏みました。最終的には、これらのファンクションの大部分を FPGA ファブリック上で動作可能な等価アクセラレータ ブロックで置き換えました。

機能の視点から考えると、我々のソリューションは MVE を構成する 3 つの層から成り、標準／高品位ビデオ フローを入力データとして受信し、事象検出用メタデー

図 2 - デュアル MiroBlaze システム オン チップ (SoC) アーキテクチャ MVE エンジン コプロセッサのブロック図

図 3 - ビデオ分析アルゴリズム構成ブロック図

タを生成します。この結果得られたメタデータは、物体／事象の追跡と分類を可能にすると同時に、分析の出力として、デバッグ用画像フローを提供します。我々は、機能的ブロックを MicroBlaze プロセッサ上で実行できるエンベデッド ソフトウェアもしくは特定 IP コアとしてインプリメントしました。これらのハードウェア アクセラレータを FPGA ファブリック内に配置し、これらアクセラレータのチェーンを C-MVA 分析コプロセッサに構築しました。

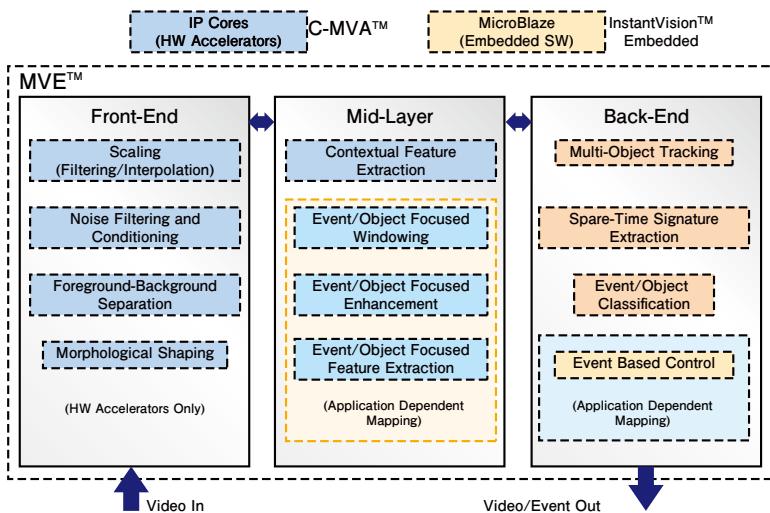

図 3 に示すように、MVE ビデオ分析エンジンの 3 層のアルゴリズムは、いくつかの主要機能ブロックで構成されます。これらブロックのほとんどは、FPGA に利用できるリソースをダイナミックにコンフィギュレーション可能な特別な IP コアを使用することで、その機能を向上します。C-MVA コプロセッサはこれらの IP コアを使用してデザインされているため、分析アルゴリズム全体の処理のフロントエンドと中間層（図 4 を参照）の処理機能を向上します。ザイリンクスの ISE Design Suite がサポートしているこのモジュールアプローチを採用することにより、性能と消費電力の両方において、システムのスケーリング（拡大／縮小）ができました。

## FPGA アクセラレータ ブロックを使用するターボチャージャー

FPGA ベースのビデオ分析システムを実現するには、ビデオ アクセラレータ エンジンをエンベデッド ベース システム内にデザインし統合する必要がありました。我々は事前に、性能上のボトルネックを予想していたため、VHDL を使用する一連のアクセラレータの開発を早期に開始できました。ザイリンクスの ISE Design Suite とエンベデッド開発キットの一部として同梱されているコード プロファイラは、さらなる性能上のボトルネックを特定し、デザインに必要なすべてのアクセラレータ ブロックを開発することに非常に有効であることがわかりました。表 2 は、IP コア ファミリのリストです。

Eutecus の開発チームは、多くの企業

がそうであるように、ハードウェア開発者とソフトウェア開発者を別個に構成していました。従って、このプロジェクトを成功させるには、両チームのそれぞれのデザイン領域で、双方がいかにして十分な抽象化を保持しながら高い生産性を維持するかが重要な課題でした。ハードウェア アクセラレータ ブロックに必要な RTL テンプレートとソフトウェア ドライバ ファイルを生成できるザイリンクス Platform Studio の Create IP Wizard に含まれている機能を使用することで、この作業をより簡素化することができました。これらのテンプレートには、デザインがエンベデッド システムからレジスタや DMA ロジック、FIFO

にアクセスする際に必要なインターフェイス ロジックが含まれています。テンプレートを使用して RTL を作成できるようになったので、RTL をエンベデッド IP カタログに登録して、開発者が必要に応じてそれを変更して使用できるようになりました。

IP コアの開発には、PLB46-MPMC-OPB ベースのバックボーン用に、汎用的にモジュール化された周辺機器ブロックの開発が必要です。これらの周辺機器は、シングル I/O プロトタイプとマルチ I/O プロトタイプ（SIMO、MIMO、MISO の各モジュール）の両方で構成されているため、厳しい画像フロー処理アルゴリズム用にマルチスレッド コプロセッサ パイプラ

図 4 - MVE 分析エンジン、InstantVision と ドライバ ソフトウェア

表 2 - MVE/C-MVA で使用可能なハードウェア アクセラレータ ブロックとして開発された IP コア ファミリ

| C-MVA IP コア ファミリ | Ver. 1 | Ver. 2 | Ver. 3 | Function                                |

|------------------|--------|--------|--------|-----------------------------------------|

| IPC-WSC          |        |        |        | 画像フロー、アップ／ダウン スケーリングとウインドウ化             |

| IPC-CNF          |        |        |        | 画像フローの調整とノイズのフィルタリング、ゲイン制御とコントラストの調節を含む |

| IPC-FBS          |        |        |        | 最前面と最後面の分離                              |

| IPC-BMF          |        |        |        | 2 進数の形態学的フィルタリング、サイズ分類と輪郭構造成形           |

| IPC-SFE          |        |        |        | 複数の事象／物体の形跡や特徴を抽出                       |

| IPC-EFE          |        |        |        | 事象／物体の強調                                |

| IPC-EBC          |        |        |        | 特定アプリケーション用の事象／物体ベースの制御                 |

| InstantVision™   |        |        |        | エンベデッド ビデオ フロー分析用アルゴリズムフレームワークと特定モジュール  |

図 5 - ハードウェア、ファームウェア、ソフトウェアのリファレンス デザイン

インを柔軟に生成できます。我々は、IP コアをほぼ任意の順序で組み合わせ、種々の分析エンジンのデザインとカスタマイズをする際にそれらをコンフィギュレーションすることにより、これを成し遂げました。

MVE 分析エンジンは、InstantVision Embedded ソフトウェア モジュールと C-MVA 分析用コプロセッサを形成するハードウェア アクセラレータで構成されています。MVE をザイリンクス Spartan-3A DSP 3400A にプロトタイピングして、SoC リファレンス デザインを生成しました。それには、通信やデータ ストリー ミングに必要なすべての I/O 機能が含まれています（完全なハードウェア／ファーム ウェア ブロック図については、図 2 を参照）。MVE 分析エンジンだけでなく、すべてのサポート用 I/O モジュールを網羅し

た SoC リファレンス デザインは、91 パーセントのロジック スライス、81 パーセントのブロック RAM および 32 パーセントの DSP スライスを使用しています。

MVE 分析エンジンのある機能を分離したものは（バックボーンの MPMC-PLB 部分と特定 I/O コンポーネントは除く）、46 パーセントのロジック スライス、44 パーセントのブロック RAM および 23 パーセントの DSP スライスのみを使用しているため、低コスト Spartan-3A DSP 1800A FPGA デバイスへの移行が容易になります。

関連処理をシングル クロック サイクルで完了できるように、C-MVA コプロセッサのすべての IP コアをデザインしました。この機能を非同期 FSL インターフェイスと組み合わせると、システムの別領域の異

なるクロックで C-MVA コプロセッサを実行できます。こうすることで、C-MVA を低ピクセル クロックで実行し、バックボーンを高周波内部システム クロックで実行するため、消費電力を大幅に抑えてシステムの性能要件を維持することができます。

### カスタマイズ、パッケージングおよびシステム統合

このシステムを検証さらに発展させる目的で、すべてのソフトウェア層にセキュリティ／監視のためのデモ用プログラムを作成しました。これにより、ユーザーは Eutecus の製品をシステムの種々の層に組み込むことができます（補足記事を参照）。ハードウェア IP コアやファームウェア、ソフトウェアを 1 つのリファレンス デザインに網羅した完全な SoC デザインのハイレベル ブロック図を図 4 に示します。

ハードウェア、ファームウェアそしてソフトウェアの各コンポーネント内で、種々のレベルの柔軟なカスタマイズによりシステムを統合できます。サーバー レベルのカスタマイズでは、そのシステムには完璧にあった SoC デザインを FPGA 内に取り込むことができますが、クライアント（コンフィギュレーション）レベルでは、デザインの変更を WIN32 や .Net API 層に適用することができます。このスキームにより、各種のコンフィギュレーションとテスト用インターフェイスを迅速にプロトタイピングできます。

ユーザーは、柔軟なコンフィギュレーション管理や性能の微調整、ステータスのモニタリングやファームウェアの更新を行うために、クライアント サーバー通信を UART や TCP/IP 上に構築することができます。

Eutecus は第 2 世代製品をリリースさせたばかりですが、第 3 世代の要件をすでに調査開始しています。このプロジェクトの経験から判断するに、ザイリンクスは信頼性の高い最新で最先端のデバイスや DSP 機能を、最先端のプロセス技術上に導入しようとしており、第 3 世代の新しい製品にもザイリンクスのデバイスを使用する計画です。

**XtremeDSP ビデオ スタータ キット – Spartan-3A DSP 版を使用して開発を加速**

Eutecus 社は、開発とデモ戦略の一部として、FPGA ベースのビデオ システムの迅速な開発とプロトタイピング プラットフォームとして、MVE ビデオ分析開発キットを作成しました。Eutecus の開発キットは、XtremeDSP ビデオ スタータ キット – Spartan-3A DSP 版 ([http://japan.xilinx.com/vsk\\_s3](http://japan.xilinx.com/vsk_s3)) 上に構築されました。このスタータ キットには、FMC ビデオ I/O ドーターカードや CMOS カメラ、ケーブル、ザイリンクス開発ソフトウェアが含まれています。

Eutecus は、MVE 分析エンジンの移植後、この開発プラットフォームを活用して、MVE 分析ソリューションとしてビデオ システム開発者へ提供を行っています。このソリューションは、評価用にも使用できますが、購入に際してのハードウェアの追加料金はありません。FPGA に一度プログラムされると、ビデオ スタータ キットが起動して Eutecus の分析操作が起動されます。その結果、FPGA ベースのビデオ分析システムの性能や機能、コストを評価するための迅速で容易な手段を手にいれることができます。

レーダ

無線

# 高速信号処理に最適!!

4ch 200MHz 16bit AD 塔載

Virtex-5 FPGA ボード

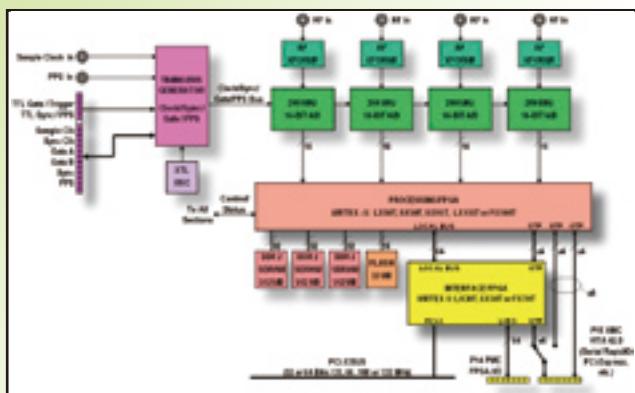

Model 7x50は通信システムのHF帯やIF帯の信号処理に適した4chの高速AD塔載FPGAボードです。その特徴はハイパフォーマンスなシステムの要求に応えるため、4ch 200MHz 16bit AD を搭載し、更にデータ処理用と I/O 制御用に 2 個 Virtex-5 FPGA を搭載しています。ボードは、PCI ExpressをはじめPCI、CompactPCI、PMC/XMCの各種と、複数枚のボードにClockを供給するための Clock Synthesizer ボードもございます。

Model 7150 ブロック図

## 【特徴】

- 4ch 200MHz 16bit AD

- 1.5GB まで DDR2SDRAM 塔載可能

- Xilinx Virtex-5 FPGA を 2 個塔載

- 200MHz で 2.56 秒のデータキャプチャが可能

- 複数枚のボード間同期を可能とするLVDS clock / sync バス

- カスタムIOのためFPGAと 32PairのLVDS接続

- VITA42.0 対応 XMC インターフェースを用意

- PCI Express をはじめ、PCI/CompactPCI/PMC ボードを用意

- FPGA 開発のための Design Kit を用意

- VxWork / Linux / Windows をサポート

## ■ ■ ■ DDC の IP コアインストール製品も用意 !!! ■ ■ ■

MATLAB/Simulink を使ったアルゴリズムの開発・検証や VHDL コードの自動生成等に運動した専用アダプテーションキットにも対応予定

256 チャネル DDC

各バンクのDecimationレンジを128～1024、64ステップ

32 チャネル DDC

各バンクのDecimationレンジを16～8192、8ステップ

2or4 チャネル DDC

各バンクのDecimationレンジを2～256、1ステップ

## 受託開発コーナー

弊社ではハード & ソフトの受託開発も承っています。是非ご利用下さい。

(お問い合わせは)

sales@mish.co.jp

<http://www.mish.co.jp/>

MISH

INTERNATIONAL

株式会社ミッシュインターナショナル

TEL 042-538-7650 FAX 042-534-1610

〒190-0004 東京都立川市柏町4-56-1

# Using the JTAG Chain for Accurate System and Intra-Die Power and Thermal Analysis

## JTAG チェーンを使った高精度 システムおよびダイ内部の消費電力

ザイリンクス System Monitor を使用した新しいバウンダリ スキャン技術により、システム挙動の多くの側面がテスト可能

Dominic Plunkett

Chief Technical Officer

XJTAG

[dominic.plunkett@xjtag.com](mailto:dominic.plunkett@xjtag.com)

Pádraig Kelly

IC Design Engineer

Xilinx, Inc.

[padraig.kelly@xilinx.com](mailto:padraig.kelly@xilinx.com)

通常、CPLD やフラッシュ メモリなどのプログラムは、バウンダリ スキャン チェーンを使用して行いますが、一人でも多くのエンジニアがバウンダリ スキャンの強力な機能を利用して、ボードやシステムの動作に関する詳細情報を抽出できるとよいでしょう。

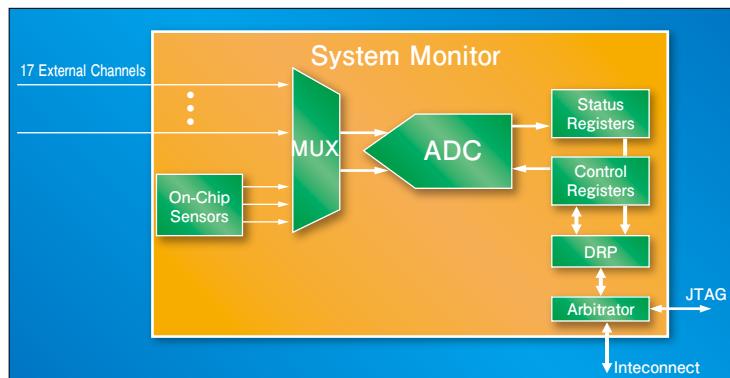

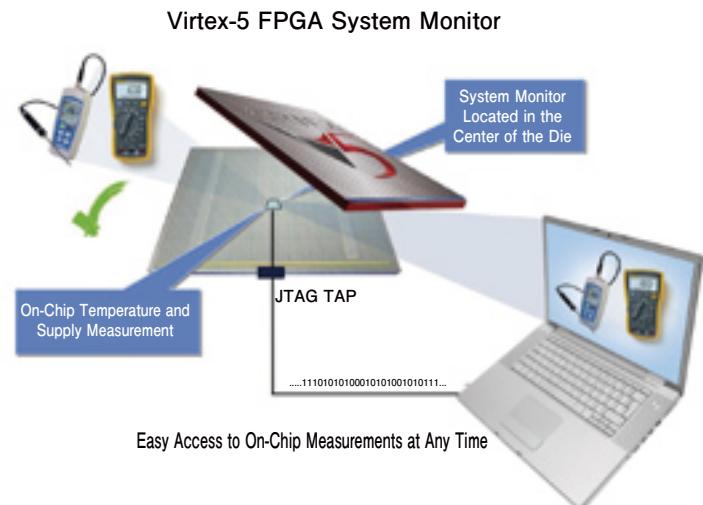

Virtex™-5 FPGA の最新プラットフォームに搭載された新しいザイリンクス System Monitor を使用すれば、従来バウンダリ スキャン機能とデバイスのプログラミングに使用していたものと同じ Joint Test Action Group (JTAG) のテスト アクセス ポート (TAP) で、FPGA 内部の電圧と温度情報が容易に収集できます。

また、ザイリンクスのパートナーである XJTAG 社が提供している製品では、テスト用スクリプトを使用するか自分でスクリプトを書くことにより、バウンダリ スキャン テスト環境下で種々のポイントでのアナログ信号をこれまで以上に容易に検証できます。XJTAG 社のバウンダリ スキャン テスト システムでは、ディスクリートの温度センサや DAC ポート、VGA ポートなどのデバイスをテストできます。

### System Monitor : デバイス レベルのテスト プローブ

System Monitor はザイリンクス Virtex-5 FPGA アーキテクチャ内のアナログ回路で、オンチップの温度と電圧をサンプリングします（図 1 参照）。専用の System Monitor 回路（デフォルトで 200 ksps の ADC を使用して構築されている）は、FPGA のダイ温度と VCCINT と VCCAUX の供給電圧レベルの連続測定シーケンスを実行します。Virtex-5 デバイスに搭載のこの機能は、システムに外部モニタ用部品をインプリメントする時の余分な煩雑さやコストを削減

します。

さらに、System Monitor の機能で、パッケージ内部のダイそのものの電圧測定が可能です。ただしこれは、外部の ADC を使用する場合は測定できません。

System Monitor を使用すれば、正確な温度の読み取りも可能です。従来、ダイの温度のモニタリングには熱ダイオードを使用していました。その場合、ダイオードによる測定は、他のデバイスからのノイズや PC 基板の構造に、信号のオフセットや許容量などの実装上の詳細情報と同様に、十分な注意を払う必要がありました。新しい System Monitor は、FPGA のダイ上に温度センサがあり、ダイからの正確な温度読み取りが可能で、そのような問題を回避することができます（図 2 参照）。

これら System Monitor の強力な機能や熱モニタ機能を使用することで、パワーオン セルフチェックや過熱によるパワーダウンなどの安全機能を容易に実装できます。System Monitor の内部電圧測定の精度は ±1% 以内で、オンチップ温度センサのモニタ精度は -40°C ~ 125°C の動作範囲で ±4°C です。

System Monitor の回路にはマルチプ

レクサも集積されており、2つの電圧検知チャネルと温度センサをサポートするだけでなく、FPGA外部のアナログソース入力を最大17個まで受け付けることができます。これは、System Monitorを使用して、各種のオフチップアナログ信号のモニタが可能であることを意味しています。また、最大振幅が1.0Vまでのオフチップのシングルエンドと差動の入力信号をサポートしているため、シャント抵抗ベースの電流センサや加速度計、位置センサや外部温度センサなどの多種類のセンサに接続できます。

System Monitorの制御システムには、自動チャネルシーケンサが搭載されているため、モニタしたいパラメータを定義できます。制御レジスタを設定することで、System Monitorを構成できます。これを行うには、デザインの中にSystem Monitorを単にインスタンシエートするか、JTAG経由で制御レジスタに書き込みます。ザイリンクスの設計ツールISE®Design Suiteには、System Monitorアーキテクチャウィザードというユーティリティがあり、これを使用してインスタンシエーションプロセスを検証しながら作業ができます。

## TAPを作動させる

System Monitorは、このデータをFPGAのJTAG TAPに直接送れるように設計されているため、ザイリンクスはプロトタイプシステムや生産システムから詳細情報を引き出すための新しい機会を増やしたことになります。さらに、高度な抽象化レベルで動作するバウンダリスキャンテストギアにデータの移植もできます。

多くのエンジニアは、バウンダリスキャンを使用して、デバイスをプログラムするという本来の機能に慣れてはいますが、デバッグとテストソリューションの目立たない機能については認識さえしていない場合が多いようです。JTAG TAPを介してテストを入力するだけで、もはや、開発ボードや生産用アセンブリにテストプローブを物理的に装着する必要はありません。

プローブの装着は、時間を要し、テスト戦略はプローブ接続に起因する物理的なエラーに対し脆弱な状態に陥ります。

さらに重要な点として、最新のBGAとCSPタイプのデバイスパッケージは、ボールの間隔が非常に狭くパッケージの下に配置されているため、物理的にプローブを当てるることは不可能です。業界では新しいICにこれらのパッケージを採用する機会が増えてきているため、従来のテストテクニックで行えるテスト範囲は、実際には少なくなっています。

Joint Test Action Group (JTAG)によって定義されIEEE1149.1として批准されているバウンダリスキャンのテスト手法は、4線TAPを指定しており、バウンダリスキャンアーキテクチャの仕様を決める際には、IC開発サイクルの後半での製品テストを容易にする目的で、ICデザインにインプリメントできる仕様になっています。4線TAPインターフェイスを使用すると、JTAGデバイスのピンや内部レジスタへの読み込み／読み出しを行うことができます。これらのピンにアクセスする

図1 - System Monitorは、Virtex-5 FPGAのダイと17個までの他のアナログソースの電圧と温度をモニタすることが可能で、システム性能全体にインパクトを与える

図2 - Virtex-5デバイスダイの中心に配置されたSystem Monitorセンサは、貴重なオンチップ電圧と温度データの提供を、製品開発段階やデバイスの量産時、あるいはフィールドに展開した後でもアクセス可能

ことで、FPGAやEEPROM、RAM、そしてフラッシュメモリなど回路基板上の他のデバイスをデバグしたりテストしたりできます。

バウンダリスキャンテスト機器を使用すると、エンベデッドテストソフトウェアやファンクショナルテストに依存せずに、迅速なネットレベルの診断が可能になります。使用する際には、必ずしもPC基板が稼動している必要はありません。したがって、最初のプロトタイプがアセンブリから戻ってくるとすぐに、基本的機能を迅速に検証できます。その際、基本的なチ

エックを実行し、個々のピンやバスをトグルさせることで、短絡、断線、接触不備、あるいは間違った接続を見つけることができ、ボードのブートを行う必要がありません。

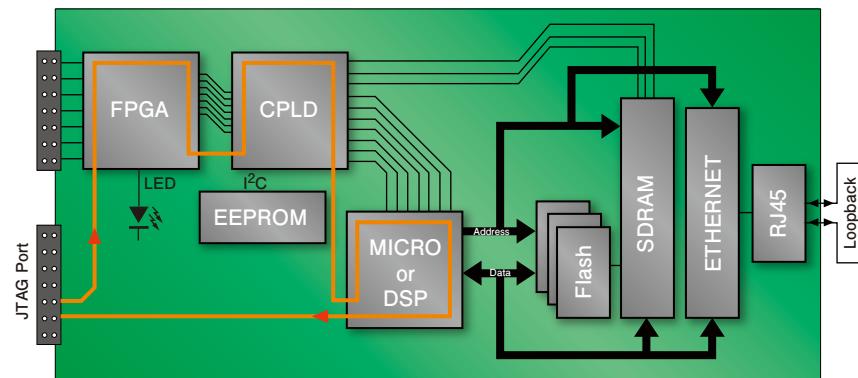

システム内のすべての JTAG デバイスのテストポートはボードレベルで相互接続されており、シリアルスキャンチェーンを設定すると、ボードの端の 1 つのコネクタからそのチェーンにアクセスできます。ボード 1 枚あたりの JTAG 準拠デバイスの数が増えても、この新しい JTAG テスターはネット全体のより広い範囲にアクセスできるため、テストでカバーできる範囲全体が広がることになります。

スキャンチェーンを操作して適切なテストパターンを設定すると、バウンダリスキャンテストインターフェイスを装備していないコンポーネントからの応答を収集することもできます。これには、アクセスしようとしているコンポーネントが準拠デバイスとして同じネットに接続されている必要があります。このテクニックは、しばしば、クラスタ テスティングとも呼ばれ、外部コネクタやビデオチップ、I<sup>2</sup>C デバイス、イーサネットコントローラ、LED、あるいはスイッチなどの非 JTAG デバイスのテスト手段を提供します。

たとえば、JTAG チェーンを使って、イーサネットのテスト用パケットをボード上の非 JTAG イーサネットコントローラに駆動し、その応答を検証することが可能です(図 3 参照)。同様に、SRAM デバイ

スや SDRAM、DDR や DDR2 チップなど、JTAG を使用できないデバイス/チップでもテストすることができます。このように、XJTAG システムのような最新バウンダリスキャン機器は、JTAG チェーンを使用して、実行可能なテスト範囲をその最大限の潜在能力まで高めています。実際、XJTAG のユーザーは、現在、複雑なボードに対して 90% 以上のテスト項目に成功しています。

### バウンダリスキャン機能の拡張

ザイリンクスの System Monitor は、Virtex-5 FPGA 内部のアナログ値を容易に収集可能で、バウンダリスキャンのテストに慣れているユーザーは、TAP を介してまた別の一組の価値あるテストを実行できます。Virtex-5 デバイスのユーザーは、System Monitor を使用して、17 個の外部アナログチャネルからバウンダリスキャンテスト環境へデータを移植できます。

Virtex-5 の System Monitor を使用するには、PC 基板の設計が最小限のデザインガイドラインに従っている必要があります。これらのガイドラインは、「Virtex-5 System Monitor ユーザー ガイド」のアプリケーションを扱っている章に記載されています([http://www.xilinx.com/support/documentation/user\\_guides/ug192.pdf](http://www.xilinx.com/support/documentation/user_guides/ug192.pdf))。

PC 基板の準備ができたら、いよい

よ System Monitor の多くの機能を利用してみましょう。たとえば、System Monitor の ADC は、パワーアップ時に動作可能状態にあるため、FPGA をコンフィギュレーションする前でもバウンダリスキャン チェーンを使用して、価値あるシステム情報を抽出できます。これにより、FPGA のコンフィギュレーションを最終決定する前にシステムの電源電圧を検証して、基本的な冷却設備を評価したりできます。

ザイリンクスは、FPGA 上にサンプリング回路をハードウェアでインプリメントしているため、製品のライフサイクル中はいつでも System Monitor 機能を適用できます。たとえばシステムが恒常に過熱状態にあったり、あるいは研究室やフィールドで電源が正常な電圧を維持できないような場合、FPGA を再度コンフィギュレーションすることなく、System Monitor のデータを読み出すためのテストを JTAG TAP を介して直ちに実行できます。

### XJTAG は新生バウンダリスキャンの使用を簡素化

XJTAG 社とザイリンクスが共同で Virtex-5 LXT ML505 開発ボードを使用して、XJTAG バウンダリスキャンソリューションのユーザー向けに System Monitor からデータへのアクセスが可能な包括テスト用スクリプトを開発しました。XJTAG は、ダイの温度や供給電圧、オフチップのアナログ値をワークステーション上に直接表示できるため、System Monitor と XJTAG が収集したデータが指定許容範囲内にあるかどうかを検証できます。

図 4 は、Virtex-5 FPGA の動作パラメータをチェックするために、XJTAG の高級記述言語 XJEase で生成できる一組の簡単なテストの断片的なコードを示しています。「Test」のファンクションコールで、最初に System Monitor をコンフィギュレーションします。その後、そのテストで個々の入力を読み取りチェックします。

図 5 は、デバイスの温度をチェックする

図 3 - 最新の PC 基板のデザインでは JTAG 準拠のものが増えてきているため、バウンダリスキャンを使用することで多種多様のタスクとテストの実行が可能

コードを示します。温度が許容範囲から外れると、このテストはエラーを表示します。この例は、XJTAG の Web サイト上で提供されている簡単なファンクションの使用による、Virtex-5 の System Monitor へのアクセス方法を示しています。

XJTAG は、たとえば障害検出やトレース目的で、System Monitor データを記録できるカスタマイズ テストをサポートしています。XJTAG が、System Monitor からのデータに対してピーク値をチェックし、スレッショルドに応答し、あるいは平均化アルゴリズムを適用するようなスクリプトを書くこともできます。

XJTAG 環境の一部として、XJTAG に含まれている XJEase を使用してスクリプトを作成できます。XJEase では、生のバウンダリ スキャン データを高度に抽象化して作業を進めることができます。あるデバイスがバウンダリ スキャン チェーンにサポートされているか否かにかかわらず、デバイスに特定のテスト スクリプトを書くこともできます。これらのスクリプトを格納し、さらに将来のプロジェクトにおいて再利用が可能です。

XJTAG は、ネットリスト データがボードへの変更を反映しているときはいつも、新しいテスト シーケンスを自動的に生成します。これにより、テスト ルーチンを手作業で書き換える手間が省けます。これは対照的に、従来のバウンダリ スキャン テスト機器は、一般的にボード中心のテスト シーケンスを生成するため、デザイン変更のたびにアップデートする必要がありこれは大変な作業です。

開発したものをテストするデバイス中心のこのスキャン手法は、エンジニアのコミュニケーションでも評判が高く、多くの XJTAG ユーザーが書いた実証済みのスクリプトを XJTAG の Web サイトに投稿し始めています。現在 XJTAG 社とサポート契約を結んでいるユーザーは、これらのスクリプトを [www.xjtag.com](http://www.xjtag.com) から無償でダウンロードでき、自分のテスト ルーチンに組み込むことができます。Web サイトに对象のデバイスがなかった場合でも、類似スクリプトをダウンロードして、それをテスト

しようとしているデバイス用にカスタマイズして使用できます。

## 将来の展望

System Monitor と XJTAG 間で可能な対話の作用域が、検証、デバッグ、パラメータ化、較正をサポートする革新的のチップ機能を支援するバウンダリ スキャン テスト システムの可能性を浮き彫りにしています。FPGA (あるいはプロセッサ、メモリ、制御用 IC などの他のデバイス) の中にインプリメントされたシリコン機能にアクセスすることにより、バウンダリ スキャンが、DIP スイッチの仮想化やデジタル フィルタの較正、あるいはアナログ設定やスレッショルド値の調整などの機能を実行することが可能になります。加えて、製品が開発段階や量産段階、フィールドで稼動中のいずれの状態でも、迅速にこれらを実行することができます。

System Monitor は、すでにバウンダリ スキャン チェーンをプロトタイプや生産アセンブリのファンクショナル ネットのテストに使用している場合に対して、今度は、バウンダリ スキャン環境内からモニタリングできるという重要な機能を提供できるようになりました。より熱心なユーザー

は、この新しい機能を利用してさらにステップアップして、このシステムをもっと深く理解したいと思うことでしょう。将来このテクニックが主流になったとき、カスタマイズされたテスト スクリプトが製品設計に対する重要な技術成果になっているでしょう。 ●

図 4 - XJEase 記述用言語を使用して、System Monitor 入力のいくつかをセットアップしてテストする様子を示したコード断片

```

-----

Test()(INT result)

-----

INT temp;

result := 0;

Config_SysMon()();

Read_Internal_Temp()(result);

Read_VAUX()(result);

Read_VINT()(result);

Read_RefP()(result);

Read_RefN()(result);

IF (result != 0) THEN

result := RESULT_FAIL;

ELSE

result := RESULT_PASS;

END;

END;

```

図 5 - Virtex-5 FPGA の温度をテストするためのコード断片

```

-----

Read_Internal_Temp()(INT result)

-----

INT temp;

Read_Temp()(temp);

IF ((temp < (Die_Temp - Temp_Margin)) || (temp > (Die_Temp + Temp_Margin))) THEN

PRINT("Die temperature = ",temp,"C. ** OUTSIDE LIMITS **\n");

result := result + 1;

ELSIF (DEBUG) THEN

PRINT("Die temperature = ",temp,"C\n");

END;

-----

Read_Temp()(INT temp)

-----

Read_Channel(0)(temp);

temp := ((temp * 20159) / 40960) - 273;

END;

```

# Solving FPGA I/O Pin Assignment Challenges

## FPGA I/O ピンの割り当てるにおける課題を解消

FPGA の複雑なピン配列の課題を解消する段階的手法を紹介

Brian Jackson

Product Marketing Manager

Xilinx, Inc.

[brian.jackson@xilinx.com](mailto:brian.jackson@xilinx.com)

I/O ピンの割り当ては、大規模 FPGA デバイスを PC 基板上に実装する際に遭遇する主な課題の一つです。デザイナにとって、大規模 FPGA における BGA パッケージの I/O ピンのコンフィギュレーションを定義する作業は、その問題点が常に増えている状況にあり、ますます困難になっています。しかし、スマートな I/O プランニングと新しいツールを組み合わせることで、ピン配列プロセスの苦悩を取り除くことができます。

FPGA から PC 基板への I/O ピン配列を定義する作業は、デザインの成功を左右する重要な課題です。FPGA と PC 基板の両方を同時にデザインするには、FPGA 側の要件と PC 基板側の要件のバランスをとる必要があります。もし、デザインの初期段階で、ピン配列を PC 基板か FPGA

のどちらかに特定して最適化すると、他の領域でデザイン上の問題に突き当たります。

ピン割り当て選択の効果を理解するには、まず、FPGA 内部の I/O パッドとそれに関連するリソースとともに、PC 基板の配置と FPGA の物理的デバイス ピンの両方をイメージする必要があります。残念ながら、これら協調デザインの懸案事項のすべてに対応できるツールや手法は現在のところありません。

しかし、各種のテクニックと戦略を組み合わせてピン ブランディング プロセスを最適化し、効率的なピン配列手法を立案することは可能で、これにザイリンクスの PinAhead テクノロジのような新しい協調デザイン ツールは最適なソリューションです。PinAhead は、ザイリンクスの最新ソフトウェア、ISE® Design Suite 10.1 に標準で装備されています。

ザイリンクスは、ピン配列の定義において、PC 基板と FPGA の双方の要求を考慮したピン配列を初期の段階から用いるルー

ル ドリブン手法を開発しました。これにより、各デザイン グループは、最終バージョンに近いピン配列を使用してできるだけ早く各自のデザインを開始することが可能になります。PC 基板の配線性の問題や FPGA の性能の問題でデザインに変更が必要な場合、この手法では、それらの問題は局所的で、小さな変更のみで対応が可能です。

### ステップ 1 : デザインのパラメータを評価する

最初にやるべきことは、できるだけ早く I/O マッピングの公式化を開始することです。これは、この作業に必要な最適ツールや完全なネット リストがなければ、困難な作業となるでしょう。

まず、少し質問に答えながら PC 基板の物理的パラメータとその限界を調べてみましょう。

- ・希望する基板層数やトレース幅、ビアのサイズは？

- ・PC 基板のパラメータが、使用できる FPGA パッケージの種類は、たとえば BGA などに制限されていますか？

- ・PC 基板上の FPGA に対するインターフェイスの位置は固定されていますか？他のチップ、コネクタ、あるいは配置場所に制限がありますか？

- ・特に注意が必要な高速インターフェイスはどれですか？

- ・相互接続を最短にできる配置方法を思い描くことができますか？

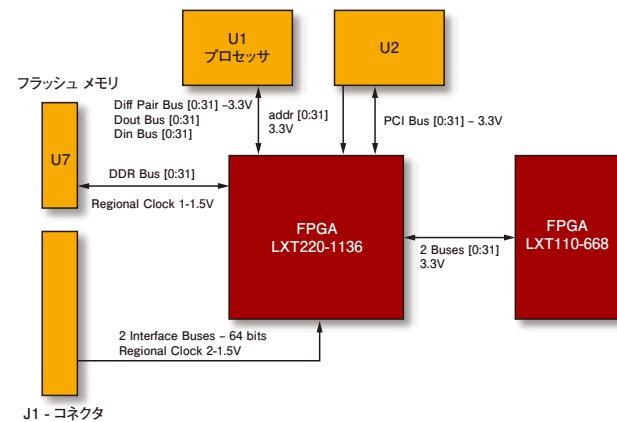

最善の FPGA ピン割り当てを行うには、提起された PC 基板の配置図（クリティカルなインターフェイスとバスを有するすべての主要コンポーネントを含む）を描いてみるとよいでしょう。コンポーネントを描く際は、実際のボード上でコンポーネントの実装を予定している場所に描くようにします。高速バスや差動ペアなど、特に注意が必要なインターフェイスには気をつけてください（図 1）。

次に、物理的リソースがシリコン上のあるのかを理解するために、FPGA のレイアウトを調べます。デザインに必要なインターフェイスの分離を開始するのに、デザインで使用する各種の電圧とクロックをリストアップします。その後、デザインが、ギガ トランシーバ (GT)、BUFR、IODELAY、およびデジタル クロック マネージャなどの特定 I/O インターフェイスリソースを使用する必要があるかどうかを決めます。これらの I/O には定義が必要で、I/O ピンをお互いの近くに配置する必要があります。

次に、デザインで PowerPC や DSP48、RAM16 などの FPGA リソースを配置します。関連する I/O をそのリソースに最も近い I/O バンクに割り当てることが重要です。I/O 信号をグループにして、インターフェイスにできるかどうかを考えてみてください。これができるれば、ピンの割り当てに非常に役立ちます。最後に、FPGA のコンフィギュレーション モードを決定します。

## ステップ 2： ピン配列の要件を定義

FPGA の主要インターフェイスを理解し、物理的レイアウトのモック アップを作成したら、ピン配列の定義を開始できます。すべての I/O 信号を含んでいるスプレッドシートを使用して、ピンをトレースしたいと思うケースもあるでしょう。それらを、電圧、クロック、インターフェイス、あるいはバスごとにグループ化します。この方法は、近接して割り当てる信号グループの公式化を開始できるので、非常に役に立ちます。この段階で、特定のエッジでデバイスから出てくるクリティカル インターフェイスと、PC 基板の最適化配線を行うために、外部の物理ピンを使用するクリティカル インターフェイスを特定する必要があります。

FPGA と PC 基板の両要件を調べ主要インターフェイスの場所を定義した次のステップは、前述のすべての制限事項に基づいて、ピンの I/O バンクへの割り当てを行うことです。ここからが実際の作業です。現在のフローでは、ピンの割り当てには、性能と信号インテグリティに関して解決すべき多くの試行錯誤が必要で、非常に時間のかかる作業です。従来デザイナは、この作業をフリーハンドで行っていました。これは、EDA ツールとチップのベンダ企業から、2 つの領域を思い描ける効率的なツールが提供されていなかったためです。

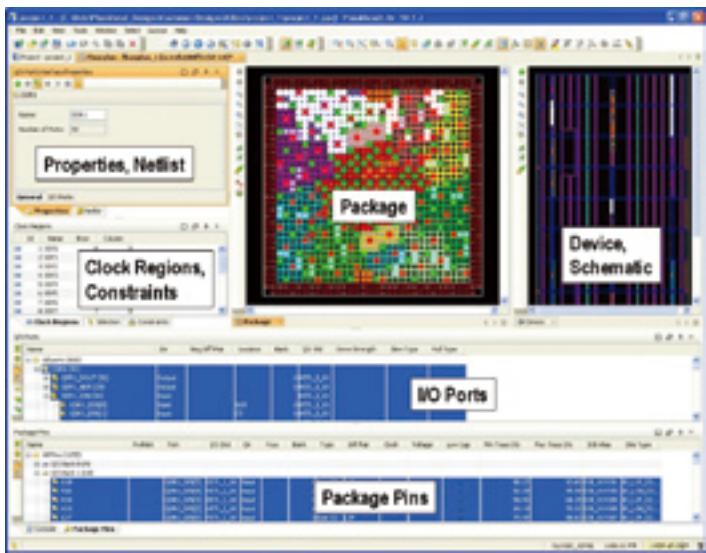

ついに、ザイリンクスがこの作業に最適な新しいツールを開発しました。ISE Foundation™ ソフトウェアのリリース 10.1 に含まれる PlanAhead™ Lite は、ソフトウェアの設計、解析およびフロアプラン ツール PlanAhead のサブセットです。PlanAhead Lite には、PinAhead というツールが同梱されており、PC 基板と FPGA の両デザイン懸案事項に対応し、デザイナの I/O

ピン配列コンフィギュレーション作業をこれまでより大幅に容易にします。

ツールの個々の機能を詳細を調べるではなく、I/O ピン割り当ての手法について、どのように各ツールを使用するかを見てみましょう。PinAhead の詳細情報は、<http://japan.xilinx.com/planahead> をご覧ください。

## ステップ 3 : PinAhead を使用してピン配列を割り当てる

PinAhead 環境は、I/O ポート信号を調べ、物理的パッケージ ピンやダイ上の I/O パッドに割り当てる作業に適用できる一連のビューを表示します（図 2）。

PinAhead は、PlanAhead ソフトウェアと事実上同じグラフィカル環境を持っているため、シリコンの I/O パッドは、そのパットに関連したリソースを「Device」ビューに、また物理デバイスのピンを「Package」ビューに明確に表示します。これらのビューは、I/O ポートと物理ピン情報を提供するため、ロジック デザインと物理デバイス リソースを調査するのに、対照しながら選択できます。

デザインのネットリストがない場合でも、PinAhead を使用して、デバイス リソースを調査し、I/O ピンのプランニング プロセスを開始できます。「Package Pins」ビューは、デバイスのデータ シートに対応したデバイス パッケージ仕様をリストアップしているため、ピン配列を構成す

図 1 - PC 基板 接続図の作成

図 2 - PinAhead 環境

るほとんどの場合、デバイスのデータシートを相互参照する必要はありません。Package Pins ビューのテーブルは I/O バンクを分類しており、相互に選択が可能で、Device ビューと Package ビューの両方で I/O バンクをハイライト表示しています。このビューは、物理的ピン位置とダイ上の I/O パッド位置間の関係を明確に示しており、最適な I/O バンクの選択が容易になります。Package Pins の「Pin」ビューは、I/O バンク内のそれぞれのピンに対する情報も表示します。

PinAhead を使用してスクラッチから I/O ポートの作成を開始することができますが、カンマで区切られたバリュー (CSV) フォーマット スプレッドシートや、HDL ソース ファイル ヘッダ、あるいは合成ネットリストと UCF フォーマット制約ファイルなどからそれらを読み込むことでも I/O ポートの作成を開始できます。「I/O Ports」ビューは、現在のデザインで定義されたすべての I/O ポート信号を表示し、バス ホルダーはグループ化されたバスや差動ペア信号を表示します。

Package Pins ビューと I/O Ports ビューは、種々の方法でソートすることができます。リスト ビューをトグルすることで、カテゴリ ベースでリストを表示したり、フラットでリストを表示したりできま

す。マウスをクリックするだけで、Package Pins ビューをソートし、利用できるすべてのグローバル クロックやローカル クロックに使用可能なピンを表示します。この情報を書き出して CSV フォーマットでスプレッドシートに出力し、ピン配列コンフィギュレーションの出発点として使用することもできます。

PinAhead にはインターフェイス機能があり、これを使用すると、I/O ピンや I/O ピン グループ、あるいは I/O バンクを、PinAhead によって I/O ポートとして割り当てられないよう選択的に禁止することができます。Package Pins ビュー や Device ビュー、Package ビューで、ピンを選択的に禁止できます。たとえば、Package Pins ビューをソートして、すべての VREF ピンを I/O として選択されることを禁止することができます。

PinAhead を使用すると、関連した I/O ポートとバスを「インターフェイス」にグループ化できます。このグループ化は、関連の I/O ポートをひとつの単体として扱うことができるので、I/O ポートの管理をより簡素化します。インターフェイスのグループ化は、特定のロジックインターフェイスに関連したすべての信号を視覚化して管理するため、ずっと容易になります。

インターフェイスは、デザインからデザインへ容易にコピーが可能で、そのインターフェイスを使用してインターフェイス特有の回路図シンボルを生成できます。インターフェイスは、I/O Ports ビュー内で拡張可能ホルダーとして表示されているので、そのビュー内で追加したい I/O ポートを選択してインターフェイス ホルダーにドラッグすることで、インターフェイスへの追

加ができます。

I/O ポートを作成する際に、それをパッケージ ピンや I/O パッドに割り当てることができます。その際は事前に、各種の I/O ポート インターフェイスを配置する際に好ましい配置場所やその他の考慮事項を理解するために、I/O ポートの初期 PC 基板上の相互接続スケッチを調べて、PC 基板の設計担当に相談することをお勧めします。適切なバス順序やエッジ近接処理は、PC 基板の配線に大いに寄与し、デザイン時間の短縮にもなります。

個々のピンやバス、インターフェイスを Device ビューか Package ビューのいずれかにドラッグすることで、I/O ピンに割り当てることができます。各種の割り当てパターン モデルを使用して、ピンのグループ全体を、選択した I/O ピンに割り当てるることができます。利用できるモデルには、「Place I/O Ports in an I/O Bank」や「Place I/O Ports in Area」、および「Place I/O Ports Sequentially」があります。

各モードは、ピンを割り当てようとする I/O ポートに異なる割り当てパターンを提供しています。これらのモードを使用すると、マウス カーソルの先端でポップアップ ウィンドウを開くことで、配置しようとしている複数のポートの情報を見るることができます。選択したすべての I/O ポートの配置が終了するまでは、このモードはアクティブになりました。

PlanAhead ソフトウェアは、ユーザーが指示した割り当て修正規則を維持しようと試みます。PlanAhead は、指示されたガイダンスに従って、差動ペア ポートを適切なピンペアに割り当てます。ユーザーが対話形式で I/O ポートの割り当てを行うことで、PlanAhead ツールはデザイン ルール チェック (DRC) を走らせて、適切な配置かどうかを確認していきます。

ツールのデフォルト設定では対話形式の DRC モードを実行しますが、それをトグルしてオフにすることもできます。ツールは、電圧、VREF ピン、あるいは I/O 標準の競合をチェックし、同時に GT デバイスの近くに配置されたノイズに敏感なピン

のチェックも行います。エラーを検出すると、Tooltip を表示して、I/O ポートをある特定ピンに割り当てることができない理由を指摘します。

PinAhead の「Autoplace」コマンドをアクティブにして、すべて、あるいは選択した I/O ポートのみを自動的にパッケージ ピンに配置するようにツールに指示することが可能です。Autoplace コマンドは、すべての I/O 標準と差動ペア規則に従って、グローバル クロック ピンを適切に配置します。このコマンドは、複数のインターフェイスをできる限りグループ化しようと試みます。

Device ビューは、すべてのクロック領域とクロック関連のロジック オブジェクトをグラフィックで表示します。これにより、クロックに基づく I/O ピン割り当てを大幅に容易にし直感的なものにします。クロック領域を選択すると、すべての I/O バンク、クロック関連リソース、およびそれに関連したデバイス リソースが表示されます。これは、利用可能なリソースを物理的な関連で説明できるため、局所的なクロック プランニングを大幅に容易にします。

PinAhead を使用して、BUFG、BUFR、IODELAY、IDELAYCTRL、および DCM などの他の I/O と関連するロジックをデザイン内に配置することもできます。PlanAhead にある「Find」コマンドを用いて、I/O に関連するロジックのオブジェクトと配置できる位置を簡単に見つける出することができます。選択的に調査し、ロジックとロジック接続を拡張するには、ツールの「Schematic」ビューを使用してください。

特定 I/O 関連ロジックの配置を固定させることもできます。PlanAhead ソフトウェアで、各々のビューからロジックを選択して、Device ビューのサイトにドラッグすることで実現します。

PlanAhead ソフトウェアでは、ロジックを適切な位置への配置のみ実行します。ダイナミック カーソルは、デザイン上でロジック オブジェクトをドラッグする際に、適切な位置を特定してくれます。

## ステップ 4：合法的な承認のため に DRC と WASSO を実行する

ピンの割り当てが完了したら、PlanAhead ソフトウェア インプリメンテーション ツールを使用する前に、PinAhead の広範な DRC ルール セットを使用し、承認用 DRC を実行してデザインにエラーがないことを確認しておきます。このツールは、I/O 配置が合法的であることを確認するために、I/O とクロック関連の多くの規則を持っています。PlanAhead ソフトウェアの DRC ダイアログを使用して、種々の規則を選択できます。

ツールが規則違反を検出すると、DRC 結果テーブルにエラーを表示します。そのエラーを選択して、より詳しく調べることができます。

PlanAhead ソフトウェアは、重み付け平均同時スイッチング出力 (WASSO) 解析機能を提供しており、このピン配置コンフィギュレーションで潜在的な信号インテグリティの問題を特定する際に効果的です。PC 基板デザインの寄生的特性をこのツールに入力すると、PlanAhead ソフトウェアは各種の I/O バンクとその近辺を解析して、各 I/O バンクの利用方法とステータスを報告してくれます。

## ステップ 5： I/O ピン配列を外部に移植する

PlanAhead ソフトウェアからの I/O ポート リストとパッケージ ピン情報を、CSV フォーマット ファイル、HDL ヘッダ、あるいは UCF ファイルに移植できます。CSV ファイルには、デバイスのすべてのパッケージ ピン情報と特定デザインの I/O ポート割り当て、またそのコンフィギュレーションに関する情報が含まれています。パッケージ ピンのセクション リストは、スプレッド シート内で I/O ポートの定義を開始する際の、重要な出発点になります。

スプレッド シートを使用して、PC 基板のレイアウトを開始するのに必要な回路図のシンボルを自動的に生成することもできます。しかし、このシンボルが回路図に

はあまりにも長すぎて、いくつかのシンボルに分ける必要性がでてくる場合もあります。PinAhead に生成されるインターフェイス グループを使用すれば、これを非常に効率的に行うことができます。

回路図のシンボルでこの I/O ピン配列コンフィギュレーションを提供することにより、設計者は、効率的な基板レイアウトの開発を行うための、良い礎を得ることになります。PC 基板インターフェイスで開発した初期ピン配列を意識することで、最終ピン配列コンフィギュレーションにかなり近いものができるでしょう。

また、レイアウト時に配線を容易にする目的でピンの交換が必要な場合、振り換えを必要としているピンは、都合よく I/O バンク内に配置されているため、容易にこれらのピンの変更を行うことができます。この手法は、FPGA デザインにあまり影響を与えないようになっています。PC 基板と FPGA デザイナ間で、ユーザーの変更を共有する目的で、変更したピン配列スプレッドシートや UCF ファイルを転送することができます。

信号ノイズの懸案事項を支援し適切な FPGA の機能を容易にする目的で、未使用ピンやある種のコンフィギュレーション ピンを VCC や GND (グランド) に接続したいと思う場合があるでしょう。ザイリンクスはこのような課題に応えるべく、PinAhead の次のバージョンで、FPGA デザイナが指定するピン接続を出力 CSV スプレッドシートに含められるよう、新しい機能の提供に現在取り組んでいます。これにより、PC 基板の設計者はピンを容易に特定でき、適切に接続することができるなります。

FPGA がより複雑な機能を取り入れ、より新しいパッケージ技術を導入するようになれば、より確固とした FPGA と PC 基板のピン配列手法の開発は必要不可欠です。PinAhead は、今日可能な協調デザインに精通したピン配列策の提供を行っていますが、ザイリンクスは、ユーザーがピン配列の課題に取り組んでより良い仕事ができるよう、新しい改良作業にもすでに着手しています。

# FPGA Designs Made Easy

## Active-HDL

Active-HDLは、高速シミュレーションエンジン、グラフィカルデザインエントリ、ドキュメント作成支援機能を搭載し、大規模かつ複雑化するFPGAの設計生産性を大幅に向上します。

### 特 長

#### ■ 高速シミュレーションエンジン

- Windowsベース業界最高水準のパフォーマンス

- VHDL/Verilog/SystemVerilog/SystemC/EDIF混在

- 豊富なHDLデバッグ機能

#### ■ グラフィカル・デザイン・エントリ

- ブロックダイアグラム、ステートマシンエディタ

- HDLからブロック図、ステート図生成

- 波形ファイルからのテストベンチ生成

#### ■ コードカバレッジ

#### ■ MATLAB/Simulink協調検証

#### ■ SWIFTインターフェース

#### ■ EDK、SOPC Builder、CoreConsoleサポート

#### ■ マルチFPGAベンダサポート

詳細情報はこちらから

<http://www.aldec.co.jp/products/active-hdl/>

### アルデック・ジャパン株式会社

東京都新宿区新宿1-8-4 JESCO新宿御苑ビル7F

TEL: 03-5312-1791 FAX: 03-5312-1795 Email: info@aldec.co.jp

<http://www.aldec.co.jp>

# Tools of Xcellence

## ザイリンクス パートナー ニュースおよび最新製品情報

新しく始まった「Tools of Xcellence」のコーナーでは、毎号ザイリンクス スタッフが、ツールや IP コア、開発ボードのベンダに取材を行って集める製品の最新情報やアップグレード情報、時には、ザイリンクスのユーザー コミュニティに大きなインパクトを与えるビジネス動向などもご紹介します。

Mike Santarini

Publisher, *Xcell Journal*

Xilinx, Inc.

[mike.santarini@xilinx.com](mailto:mike.santarini@xilinx.com)