# Xcell journal

SOLUTIONS FOR A PROGRAMMABLE WORLD

ターゲットデザイン

プラットフォームで

技術革新を加速

## INSIDE

FPGA が有線通信機器の

中心的な役割を担う

3GPP-LTE 向けベース

バンドの開発がより容易に

Virtex-5 は超広帯域

(UWB) 通信と正確な測距

を実現

FPGA 搭載のプラット

フォームで産業用モーター

を最大効率で制御

出力3.3V以上の

システム電源用

超低ノイズの

汎用モジュール

### 超低ノイズファミリ

**LTM4612**

I<sub>OUT</sub> **5A**

V<sub>IN</sub> **5~36V**

V<sub>OUT</sub> **3.3~15V**

15×15×2.8mm

### デュアルアルファミリ

**LTM4614**

I<sub>OUT</sub> **4A×2**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4615**

I<sub>OUT</sub> **4A×2 1.5A VLDO**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4606**

I<sub>OUT</sub> **6A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4616**

I<sub>OUT</sub> **8A×2**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM8024**\*近日発売

I<sub>OUT</sub> **1.2A×2**

V<sub>IN</sub> **3.7~36V**

V<sub>OUT</sub> **0.8~10V**

9×15×2.8mm

### 36V高電圧ファミリ

**LTM8020**

I<sub>OUT</sub> **200mA**

V<sub>IN</sub> **4~36V**

V<sub>OUT</sub> **1.25~5V**

6.25×6.25×2.32mm

**LTM8021**

I<sub>OUT</sub> **500mA**

V<sub>IN</sub> **3.6~36V**

V<sub>OUT</sub> **0.8~5V**

6.25×11.25×2.8mm

**LTM8022**

I<sub>OUT</sub> **1A**

V<sub>IN</sub> **3.6~36V**

V<sub>OUT</sub> **0.8~10V**

9×11.25×2.8mm

**LTM8023**

I<sub>OUT</sub> **2A**

V<sub>IN</sub> **3.6~36V**

V<sub>OUT</sub> **0.8~10V**

9×11.25×2.8mm

### 低電圧ファミリ

**LTM4604**

I<sub>OUT</sub> **4A**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.8~5V**

9×15×2.3mm

**LTM4608**

I<sub>OUT</sub> **8A**

V<sub>IN</sub> **2.375~5.5V**

V<sub>OUT</sub> **0.6~5V**

9×15×2.8mm

### 昇降圧型ファミリ

**LTM4605**

I<sub>OUT</sub> **5A(12A降圧モード時)**

V<sub>IN</sub> **4.5~20V**

V<sub>OUT</sub> **0.8~16V**

15×15×2.8mm

**LTM4607**

I<sub>OUT</sub> **5A(10A降圧モード時)**

V<sub>IN</sub> **4.5~36V**

V<sub>OUT</sub> **0.8~24V**

15×15×2.8mm

**LTM4602**

I<sub>OUT</sub> **6A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4603**

I<sub>OUT</sub> **6A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4600**

I<sub>OUT</sub> **10A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

**LTM4601**

I<sub>OUT</sub> **12A**

V<sub>IN</sub> **4.5~28V**

V<sub>OUT</sub> **0.6~5V**

15×15×2.8mm

# FPGA高速シリアルI/Oの電源に最適

- 例えば12V入力から1V/5Aの出力を、低ノイズで実現

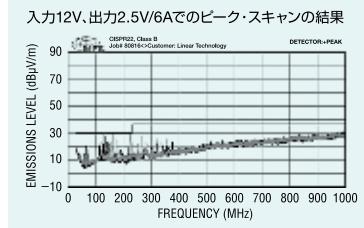

- 低EMI(CISPR 22 Class Bに準拠)、低入出力リップル電圧

- 高効率(低発熱)。サイズは、わずか15×15×2.8mm

- 電源回路の実装面積を大幅削減、設計時間も大幅低減

- 簡単、すぐに使えるスイッチモードの電源モジュール

## 実現したのは、LTM<sup>®</sup>4606 μModule™

マイクロ・モジュール

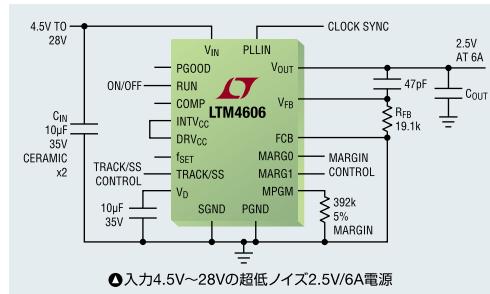

### LTM4606 超低EMIの28VIN、6A DC/DC μModule

LTM4606はFPGAの高速I/OやSERDESに最適な、超低EMI、高効率(低発熱)、そしてリニアレギュレータのようにシンプルな小型スイッチングDC/DCソリューションです。従来のリニアレギュレータでは発熱により不可能だった、12Vから1V/5Aといったような低ノイズ電源が実現できます。

- 完全な低EMIスイッチモード電源

- 広い入力電圧範囲: 4.5V~28V

- 標準6AのDC出力電流、8Aのピーク出力電流

- 出力電圧範囲: 0.6V~5V

- ±1.5%の全DC誤差

- 入力電圧5V、出力電圧3.3V時の効率: 最大93%

- 低い入出力換算ノイズ

- 出力電圧トラッキングおよびマージニング

- PLL周波数同期

- パワーグッド出力

- 並列接続/電流配分

- 超高速過渡応答

- 電流モード制御

- プログラム可能なソフトスタート

- 電流フォールドバック保護(起動時にディスエーブル)

- 出力過電圧保護

- −55°C~125°Cの動作温度範囲(LTM4606MPV)

- 15mm×15mm×2.8mm

- 表面実装LGAパッケージ

### ■ 超低EMI

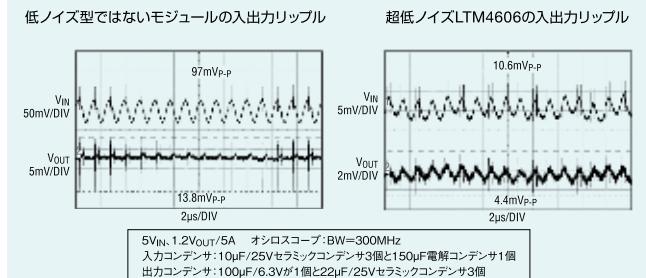

### ■ 低い入出力ノイズ電圧

### ■ ザイリンクス社RocketIO™検証済み電源

LTM4606はザイリンクス社によって同社のラボで、6.25Gbpsのライン・レートでPRBS-15データ・パターンを使ってテストされました。回路がLTM4606から給電されている状態で、トランシミッタのジッタとレシーバのジッタ耐性を測定して、トランシーバの性能を評価する方法です。

テストセットアップ、テスト装置およびテスト結果の詳細な報告はFPGA Journal Chalk Talkウェブキャスト([https://admin.acrobat.com/\\_a700655680/xilinx080826](https://admin.acrobat.com/_a700655680/xilinx080826))をご覧いただけます。

検証に使用されたLTM4606テストボード

### 評価ボード

お問い合わせは、下記販売代理店まで

LT、LTC、LTMは、リニアテクノロジー社の登録商標です。μModule、LINEAR EXPRESSは、リニアテクノロジー社の商標です。他の商標はそれぞれが所有するものです。

オンラインストア リニアエクスプレス

**LINEAR EXPRESS™**

0120-7291-22

株式会社 トーメン エレクトロニクス

本社 TEL 03-5462-9615

大 阪 06-6447-9644 名古屋 052-582-1591

福 岡 092-713-7779 宇都宮 028-625-8331

松 本 0263-34-6131 北関東 048-921-9011

仙 台 022-221-8061 浜 松 053-452-8147

立 川 042-548-9871

東京エレクトロンデバイス株式会社

本社 TEL 045-443-4024

大 阪 06-6399-1511 名古屋 052-562-0825

東 京 03-5908-2621 北関東 048-600-3880

水 戸 029-227-6552 立 川 042-548-0255

浜 松 053-459-2204 浜 松 0263-36-8112

福 岡 092-474-4121 仙 台 022-298-7184

株式会社 三 共 社 本社 TEL 03-5298-6201

株式会社 ジ ェ ピ コ 本社 TEL 03-6362-0411

東京電子販売株式会社 本社 TEL 03-5350-6711

株式会社 信 和 業 留 本社 TEL 06-6943-5131

伊藤電機株式会社 本社 TEL 052-935-1746

リニアテクノロジー国内ニュースサイト

[www.linear-news.jp](http://www.linear-news.jp)

## Xcell journal

|               |                                                                |

|---------------|----------------------------------------------------------------|

| 発行人           | Mike Santarini<br>mike.santarini@xilinx.com<br>+1-408-879-5270 |

| 編集            | Jacqueline Damian                                              |

| アートディレクター     | Scott Blair                                                    |

| デザイン/制作       | Teie, Gelwicks & Associates                                    |

| 日本語版統括        | 秋山一雄<br>kazuo.akiyama@xilinx.com                               |

| 制作進行          | 竹脇美優紀<br>miyuki.takegoshi@xilinx.com                           |

| 日本語版 制作・広告・印刷 | 有限会社エイ・シー・シー                                                   |

japan.xilinx.com/xcell/

Xcell Journal 日本語版 67・68 合併号

2009 年 11 月 16 日発行

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400

ザイリンクス株式会社

〒 141-0032

東京都品川区大崎 1-2-2

アートヴィレッジ大崎セントラルタワー 4F

© 2009 Xilinx, Inc. All Right Reserved.

XILINX や、Xcell のロゴ、その他本書に記載の商標は、米国およびその他各国の Xilinx 社の登録商標です。PowerPC は、米国または他の国における IBM 社の商標です。ほかすべての名前は、各社の登録商標または商標です。

本書は、米国 Xilinx, Inc. が発行する英文季刊誌を、ザイリンクス株式会社が日本語に翻訳して発行したもののです。

米国 Xilinx, Inc. およびザイリンクス株式会社は、本書に記載されたデータの使用に起因する第三者の特許権、他の権利、損害における一切の責任を負いません。

本書の一部または全部の無断転載、複写は、著作権法に基づき固く禁じます。

Printed in Japan

# プラチナ時代を予感させる半導体の黄金時代

## IC 上で展開される技術革新への序章

何年も前のことですが、EDN 誌でのかつての同僚が、Gordon Moore 氏の画期的な論文「Cramming More Components onto Integrated Circuits (より多くのコンポーネントを集積回路 (IC) に組み込む)」のコピーを送ってくれました。それは、廃刊となつた Electronics 誌の 1965 年 4 月 19 日号に掲載されたものの再版で、以来ずっと私の机の上にあります。この論文を読んだことのない方は、是非読んでみてください。Moore 氏はこの論文を「集積回路の将来は、エレクトロニクスの将来そのものである」と述べるところから始め、さらに続けて、多くの卓越した予想を展開しています。すなわち、パーソナル コンピュータの発明、今日のインターネットや携帯端末市場など現在でも進化を続ける集積回路の成果を先見していたのです。

論文の中で Moore 氏は、IC 上のトランジスタ数は 1 年ごとに約 2 倍になる（後に、2 年ごとに 2 倍と修正）と記述しており、この論文が画期的だと考えられている理由は、まさにこの発想にあります。そして、彼のこの言葉こそ、当時カリフォルニア工科大学の教授であった Carver Mead 氏が「ムーアの法則」と名付け、広く知られるようになったものなのです。半導体と同様に、エレクトロニクス産業は過去 44 年間まさにムーアの法則に従ったペースで急成長を遂げてきました。2005 年のことになりますが、Mead 氏がムーアの法則について Moore 氏にインタビューを行つた、Computer History Museum イベントを取材し、EDN 誌にその記事を掲載するという素晴らしい機会に恵まれました（この対談は次のビデオで見ることができます。<http://www.youtube.com/watch?v=MH6jUSjpr-Q&feature=PlayList&p=6B12AOFACFA35D1F&index=7>）。さらに、ごく最近になって、半導体業界における多大な功績を認められた 15 名が National Inventors Hall of Fame に殿堂入りした、この業界にとって非常に重要な式典に出席することができました（<http://www.dspdesignline.com/news/217400639> から私のブログ [pldesignline.com](http://pldesignline.com) をお読みください）。

Moore 氏、Mead 氏も殿堂入りした 15 名に含まれていましたが、私はザイリンクスの共同創設者である Ross Freeman 氏に非常に大きな敬意を払っていました。彼は亡くなられた後に殿堂入りしたわけですが、その同僚と家族から本人について、多くを知ることができました。Freeman 氏は 1984 年に FPGA を発明し（特許番号 4,870,302）、残念ながらそのわずか 5 年後に 45 歳の若さで亡くなりました。Freeman 氏や彼の共同創設者、突き詰めれば、ザイリンクス創設期の投資家たちがムーアの法則を信じていなければ、FPGA が商品化されることなく、されていましたとしてもこれほどの成功には至らなかつたであろうことを、この素晴らしい式典を通して知ることになりました。

ザイリンクスの共同創設者

Ross Freeman 氏

Freeman 氏が発明した初期の FPGA 回路は、独創的でユニークではありましたが、本質的に、トランジスタの最も効率よい利用法とは考えられませんでした。当時トランジスタを製造するには、多額の製造コストが必要だったのです。これに対して Freeman 氏は、トラ

ンジスタを最小化することではなく、柔軟に使用できること、開発期間が短期であること、そして製造を外部委託することの利便性を優先させたのでした。Freeman 氏は、時が過ぎムーアの法則がさらに進化すれば FPGA は継続的に発展し、少なくともロジック セル数は倍増すること、それによってトランジスタのコストが劇的に下がり、プログラマブル デバイスが多くのユーザーにとって魅力的な製品になることを 1984 年の時点で予見していたのです。

Moore 氏が集積度の周期的傾向を特定したのと同様、Freeman 氏は、同僚で共同創設者の Bernie Vonderschmitt 氏および Jim Barnett 氏とともに、IC 製造の経済動向を的確に把握しています。つまり、ムーアの法則に従って 2 年ごとに新しいプロセス技術が導入されるとすれば、プロセスが新しくなるごとに製造工場の設備を揃えていくコストを考えると、チップ メーカーが増えていく中で製造工場を所有することは賢明ではないと判断したのです。

Vonderschmitt 氏はザイリンクス最初の製品 XC2064 FPGA の製造をセイコーエプソン社に委託するという、画期的なビジネス モデルを展開しました。ファブレス メーカーのビジネス モデルはここから始まったのです。今日、半導体とシステム メーカーの多くは、自社で IC を製造するのではなく、外部半導体工場と契約する形でビジネスを行っています。これは、Freeman 氏と Vonderschmitt 氏が予測したように、新しいプロセス技術の導入に伴う製造コストが急速に増加したためです。

この非常に高い製造コストは顧客に転嫁され、ファブレス製造の ASIC や ASSP でさえ、コスト的に採用が難しいものとなっています。つまり、多くのエンジニアは採用するデバイスを FPGA に変更しつつあるのです。

FPGA の価値が高まるであろうという Freeman 氏の予測は、これまで以上に強く共感されるようになっています。ザイリンクス社員と顧客が過去 20 年にわたり、並外れた方法で協力関係を築き、FPGA 技術の発展を促してきたこともまた、ザイリンクスが世界最先端のプロセス技術を導入し、世に広めることに貢献してきたのでした。この技術革新を継続した結果、今日の FPGA は数十万のロジック セル、マイクロプロセッサ コア、DSP スライス、高速 I/O などが搭載されるまでになりました。FPGA は幅広い用途で利用されるようになり、新しい技術を素早く現実のものにする手段として、ますます活用されるようになっています。

2009 年 Inventors Hall of Fame の式典で称えられた革新への精神は、単に半導体の黄金時代を称賛するだけのものではなく、将来もたらされるであろう無数の発明に対する祝典でもあったのです。過去 50 年が半導体の黄金時代だとすれば、次の 50 年は確実にプラチナの時代になるでしょう。カリフォルニア工科大の Mead 氏は、「これはほんの始まりにすぎない…」。そう演説の中で述べていました。

Mike Santarini

発行人

National Inventors Hall of Fame の式典では、Freeman 氏の兄弟、Fred Freeman 氏（右側）が家族を代表してザイリンクスの共同創設者賞を受賞し、母親、Ethel さんがこれを掲げています。

## VIEWPOINTS

### Letter from the Publisher

プラチナ時代を予感させる

半導体の黄金時代 ...2

### Xpectations

ターゲット デザイン プラットフォームが

FPGA の革新を新たなレベルに ...56

## XCELLENCE BY DESIGN APPLICATION FEATURES

### Xcellence in Wireless comms

3GPP-LTE 向けベースバンドの

開発がより容易に ...20

### Xcellence in Aerospace & Defense

Virtex-5 がリコンフィギャブルで

堅牢な PC 開発を支援 ...23

### Xcellence in Wireless comms

Virtex-5 は超広帯域 (UWB) 通信と

正確な測距を実現 ...27

### Xcellence in Automotive & ISM

FPGA 搭載のプラットフォームで

産業用モーターを最大効率で制御 ...32

27

## Cover Story

ターゲット デザイン プラット

フォームで技術革新を加速 ...6

6

## THE XILINX XPERIENCE FEATURES

### Xplanation: FPGA 101

ザイリンクス FPGA の消費電力を最適化 ...38

### ASK FAE-X

補間ロックアップ テーブル (ILUT) により、

DSP ファンクションのインプリメントが容易に ...46

## XTRA READING

### Xamples...

アプリケーション ノート ...52

## Cover Story

FPGA が有線通信機器の

中心的な役割を担う ...12

46

## 広告索引

リニアテクノロジー株式会社 ...表2-1

マイクレル・セミコンダクタ・ジャパン株式会社 ...11

株式会社グレープシステム ...19

株式会社ミッシュインターナショナル ...31

有限会社ヒューマンデータ ...45

Xcell Journalのご送付先住所等の変更は：

<http://japan.xilinx.com/xcell/henko/>

Xcell Journal の新規定期購読のお申込みは：

<http://japan.xilinx.com/xcell/toroku/>

# Targeted Design Platforms Put Innovation on Fast Track

## ターゲット デザイン プラットフォームで技術革新を加速

最新の Spartan-6 および Virtex-6 FPGA 用に最先端のインフラを開発

Mike Santarini

Publisher, Xcell Journal

Xilinx, Inc.

[mike.santarini@xilinx.com](mailto:mike.santarini@xilinx.com)

2008 年に Moshe Gavrielov がザイリンクスの社長兼 CEO に就任した際、彼は数十年におよぶ半導体企業の経営幹部や IC 設計者としての知識・経験を持ち、多くの経済的実態がそうであるように、電子製品の将来においてプログラマビリティは避けられないものであり、いずれはこれに収束するだろうという見解を持っていました。

Gavrielov は、ザイリンクスの経営に携わる前、長年 LSI Logic 社で ASIC グループを率いており、その後 EDA 企業である Verisity 社の CEO に就任しました。これらの企業ビジネスに係わっていた期間、厳しい開発予算内で新しい市場と恒常に発展する標準規格に迅速に対応しようと懸命に努力しつつも、IC 設計の複雑さや製造コストが上昇していく状況を目の当たりにしてきたのです。

Gavrielov は、FPGA によって製造コストの負担が軽減されるという理由から、これらの要因がザイリンクス発展の好機になると結論付けました。FPGA デバイスはリプログラマブルであるため元来柔軟性が高く、設計上のエラーも容易に修正できるものです。

しかし、実際にザイリンクスにとっての発展の機会を逃さないようにするには、業界最良の FPGA を提供するだけではなく、世界クラスの設計ツール、豊富な知識的設計資産 (IP コア)、評価キット、サービス、ドキュメント、ターゲットのリファレンス デザインなどを補うことで、シリコンを完全なものにする必要があります。これら各エレメントは、カスタマが革新的な製品をいち早く市場に投入するようするために、なくてはならないものです。

Gavrielov の理念を実現するため、ザイリンクスとパートナ企業が協力し、ターゲット デザイン プラットフォームというアプローチを開発しました。これは、FPGA の初心者から経験豊富な設計者まで、あらゆるユーザーに対して、FPGA の設計プロセスを簡素化することを目的としているものです。

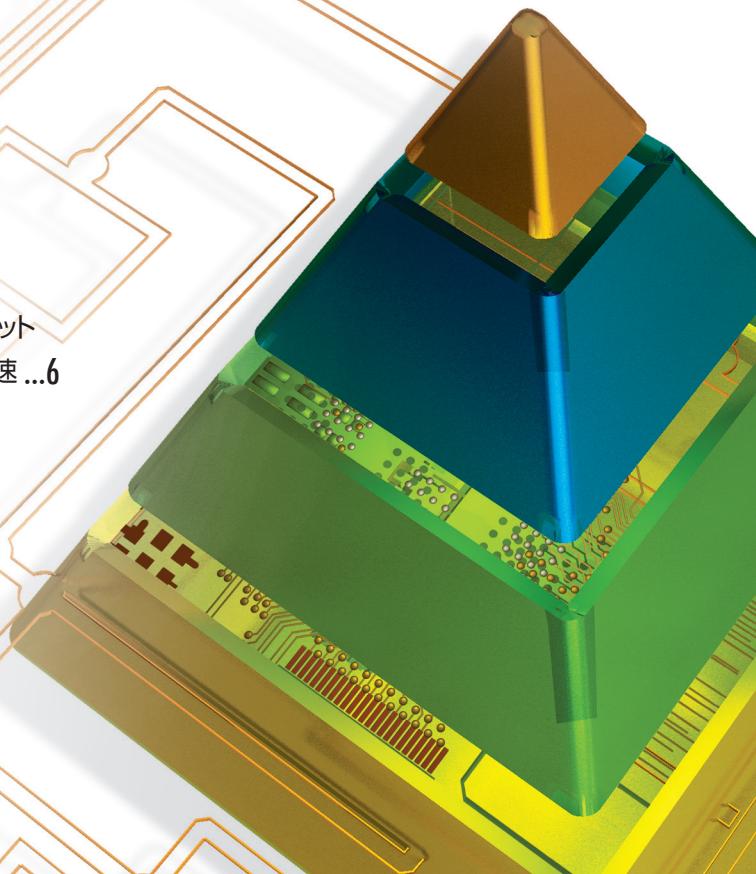

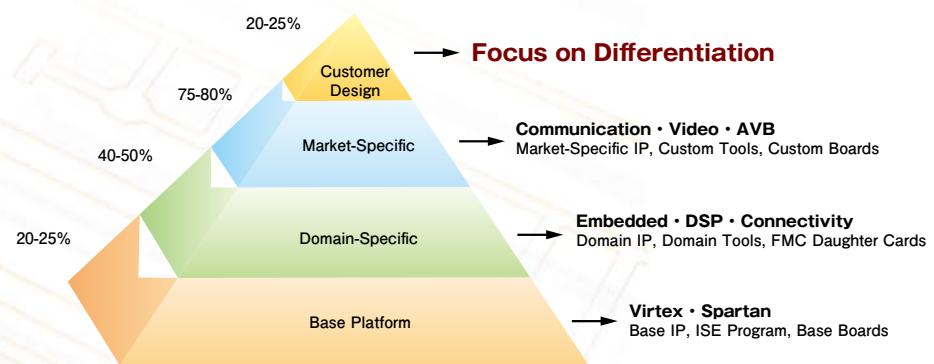

## ザイリンクスのターゲット デザイン プラットフォーム

このアプローチを具体的にするため、ザイリンクスは 4 層から成るピラミッド型の戦略を採用しました。これは最下層部から、ベース ターゲット デザイン プラットフォーム (ベース プラットフォーム)、ドメイン特化プラットフォーム、マーケット特化プラットフォームとなっており、最上部にはユーザーによる差別化層が位置します (図 1)。ザイリンクスが提供するドメイン特化プラットフォームおよびマーケット特化プラットフォーム製品を、ベース ターゲット デザイン プラットフォームに追加することで、基本的な設計部分のより多くの自動的に構築することが可能となります。このアプローチによって製品の市場投入時間が短縮され、

図 1 - ザイリンクスのターゲット デザイン プラットフォームは、ユーザーの生産性向上を目的としています。

デザイン開発期間の多くを、製品の差別化作業に注力できるのです。

この点について Gavrielov は次のように語っています。「今日、ザイリンクスの高性能 Virtex®-6 および量産用 Spartan®-6 FPGA は、数十万個のプログラマブル ロジック セルに、最大 11.2Gbps のトランシーバ、38M ビットのブロック RAM および 2,000 の DSP スライスを備えています。これらの機能を活用することで、アプリケーション数にかかわらず、革新的なデザインが可能となるのです。つまり、ASIC と ASSP の市場シェアを奪取する機会は熟しており、ザイリンクスこそが次世代電子機器の技術革新において中心的な役割を果たしていくのです。ターゲット デザイン プラットフォームは、FPGA の開発プロセスを容易にし、FPGA が持つ利点を最大限に引き出して、革新的な製品をいち早く市場に投入することが可能となるのです。」

ピラミッドを構成するベース層はベース ターゲット デザイン プラットフォームです。ザイリンクスは、2009 年 2 月に Virtex-6 (<http://japan.xilinx.com/products/virtex6/index.htm>) と Spartan-6 (<http://japan.xilinx.com/products/spartan6/index.htm>) FPGA ファミリ製品発表し、その後 6 月にベース ターゲット デザイン プラットフォームの提供を開始しました。4 月には、ターゲット デザイン プラットフォーム サポート用 ISE® Design Suite Edi-

tion 11 ([http://japan.xilinx.com/support/documentation/white\\_papers/wp307.pdf](http://japan.xilinx.com/support/documentation/white_papers/wp307.pdf)) がリリースされています。

6 月に発表された Virtex-6 と Spartan-6 FPGA 用ベース ターゲット デザイン プラットフォームの最初の製品は評価キットという形で、新しいプラットフォーム アプローチの利点を実現するために必要なすべてのエレメントを組み合わせています。この評価キットには、最新の ISE Design Suite 11.2 と Virtex-6 LX240T および Spartan-6 LX16 FPGA 評価ボード、検証済みのベース IP コア、ベース プラットフォーム リファレンス デザイン、およびドキュメント一式が含まれています。このドキュメントを参考にすると、ハードウェアのセットアップからソフトウェアのインストールと設計開始に至るまでのプロセス全体を把握することができます ([http://japan.xilinx.com/products/targeted\\_design\\_platforms.htm](http://japan.xilinx.com/products/targeted_design_platforms.htm) を参照)。

ザイリンクス プロダクト マーケティングのディレクタ Brent Przybus は、次のように語っています。「ベース ターゲット デザイン プラットフォームのリリースは、Virtex-6 と Spartan-6 FPGA のデザインを開始できる準備が整ったことを意味しています。つまり、ISE Design Suite 11.2 をダウンロードし、Spartan-6 と Virtex-6 FPGA 用のベース評価キットを注文して、包括的なドキュメントにアクセスすることでデザイン開発に

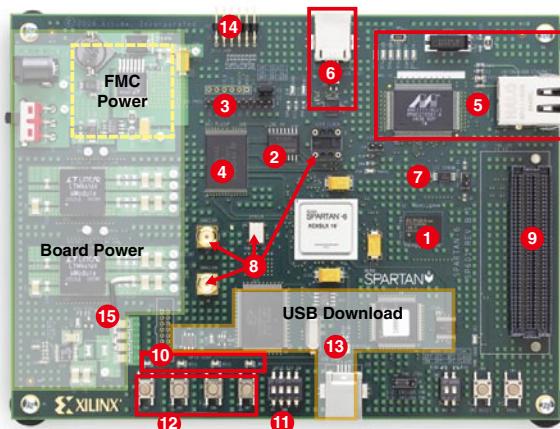

図2 - Spartan-6 SP601 評価キットのボードは、豊富なシステム ファンクションを搭載しています。

| #  | Feature                           |

|----|-----------------------------------|

| 1  | DDR2                              |

| 2  | SPI x4, x1, Ext. x4 Configuration |

| 3  | SPI Header                        |

| 4  | Parallel Flash                    |

| 5  | 10/100/1000 Ethernet              |

| 6  | USB UART                          |

| 7  | IIC                               |

| 8  | Clock, Socket, SMA                |

| 9  | FMC LPC connector                 |

| 10 | LED                               |

| 11 | DIP Switch                        |

| 12 | Pushbutton                        |

| 13 | USB JTAG                          |

| 14 | 12-pin (8 I/O) Header             |

| 15 | VCCint Voltage Selection Header   |

着手できるのです。」

## ターゲット デザイン プラットフォームのメソドロジ

ターゲット デザイン プラットフォームのメソドロジでは、ベース ターゲット デザイン プラットフォームを使用してプロジェクトに着手し、ほぼすべてのアプリケーションに共通な基本的ファンクションにアクセス可能となります。作業する設計領域（ドメイン）に基づき、ロジック設計者、DSP 設計者、エンベデッド ソフトウェアのプログラマ、あるいはシステム エンジニアは、ザイリンクスのドメイン特化キットから必要なものを選択し、それらをベース ターゲット デザイン プラットフォームに追加できます。

これらのキットからは、ISE Design Suite 11 Edition に含まれるドメイン特化ツール、ザイリンクスや重要な IP コアパートナが検証したドメイン特化 IP コア用ライブラリ、ドメイン特化ドーター カードが入手可能です。ベース プラットフォーム評価ボード上の FPGA メザニン コネクタ (FMC) を介してベース ターゲット デザイン プラットフォーム評価ボードにカードを挿入すれば、デザインを迅速にインプリメントできます（12 ページの補足記事を参照）。また、各ドメイン特化キットには、リファレンス デザインが含まれ

ているため、使用するファンクションをインプリメントする際の参考になります。

これらドメイン特化キットに加え、ザイリンクスとパートナーはマーケット特化 プラットフォームも開発しました。特定のマーケットに特化したドーター カードを FMC コネクタを介してベース プラットフォームに装着することで、マーケット特化ボードが使用できます。各マーケット特化キットには、ドメイン特化キット同様に、検証済みの IP コアとリファレンス デザインが含まれているため、デザインにファンクションを容易に追加できます。

Przybus は、ターゲット デザイン プラットフォームについて、さらに次のように説明しています。「ターゲット デザイン プラットフォームのエレメントを多く追加するほど、設計を早く完成できることになります。たとえば、ベース プラットフォームで入手可能なファンクションをすべて利用すると、プロジェクト全体の最大 25% がインプリメント可能で、貴重な時間を節約されることから、その他の部分の開発に注力することができるのです。また、ドメイン特化キットも利用すれば設計の約 50% を、さらにマーケット特化キットを使用することで最大 75% をインプリメント可能です。そして、残りの 25% の設計に集中することで最終製品の差別化に集中することができるのです。」

ゼロからスタートして FPGA 全体をイ

ンプリメンテーションしたいと思うユーザーがいることも、また、それが可能であることも指摘した上で、大多数はターゲット デザイン プラットフォームの全エレメントを利用して最大の利益を得る方を望むであろうと述べています。

## ユーザーのニーズをターゲットに

「ターゲット デザイン プラットフォームは、すべての層のカスタマを対象にして開発されたものです。つまり、プログラマブル デバイスを長年徹底して使用してきた FPGA 設計のエキスパートから、これまで ASIC と ASSP に携わってきた設計者で、大部分を FPGA に移行しようとしている設計者などがここに含まれています。また範囲を拡大して、FPGA の経験のまったくない ASIC 設計者や、スタンダードアーロン プロセッサのプログラミングの経験しかない初心者も対象としています。」

「ターゲット デザイン プラットフォームでは、初心者が設計を素早く開始するために必要な FPGA、IP コアおよびツールに加え、参考となるリファレンス デザインも提供しています。これらリファレンス デザインに設計者自身のコンテンツを追加することで、製品の差別化を図ることができます。ターゲット デザイン プラットフォームを使用すれば、初心者でも FPGA の設計に素早く馴染むことができ、さらに経験を積めば設計における差別化に貢献することが可能となります。」

「FPGA 設計の知識や経験があり、FPGA 設計の取り組みをさらに拡大したいと考えている場合もターゲット デザイン プラットフォームを使用すれば、開発時間の大縮短および迅速な市場投入也可能となるでしょう」と Przybus は述べています。「FPGA の設計には馴れていても、大きな課題の 1 つは、デザイン全体もしくはその一部を新しい FPGA に移行することです。ターゲット デザイン プラットフォームでは、新しい機能の使用方法を示すリファレンス デザインや有用な移行テクニックが利用できるため、これが

非常に簡単になります。また、ザイリンクスが実施した方法を確認でき、その具体例を活用すれば、設計への取り組みが拡大できます。」

「FPGA のエキスパートもデザインの移行には関心を持っていますが、彼らは通常、FPGA の性能を最大限に引き出すことと電力効率を最大にすることに焦点を当てて設計しています。」と Przybus は述べています。「ターゲット デザイン プラットフォームでは、新しい FPGA とツールを利用して FPGA から最大の効率を引き出せるような具体例をユーザーに提供しています。電力効率を最適化するために消費電力を監視できる設計環境、および最高速のマルチギガビット トランシーバと DSP スライスをインプリメントして解析する際の設計環境を提供しています。また、それらの要素を評価するために使用されるシステム中心の設計手法を導入するのは、これが初めてです。この組み合わせにより、開発時間が短縮されます。」と、Przybus は述べています。

## Spartan-6 と Virtex-6 評価キット

ベース ターゲット デザイン プラットフォームの中心となるエレメントは、評価キットです。具体的には、Spartan-6

SP601 評価キットと Virtex-6 ML605 評価キットです。現在、これら新製品の注文を受け付けています。

Spartan-6 FPGA SP601 評価キット（図 2）は、Spartan-6 LX16 FPGA を使用して民生機器、インフォテインメント、ビデオ、およびコストと電力を重視するその他アプリケーションを開発するための、低コスト、エントリ レベルの環境です。このキットのシステム レベルの機能には、DDR2 メモリ制御、フラッシュ、イーサネット、汎用 I/O および UART などが含まれています。またこのキットには、ISE Design Suite 11.2 WebPACK、リファレンス デザイン、デモ、ボード デザイン ファイル、ケーブル、電源が含まれています。

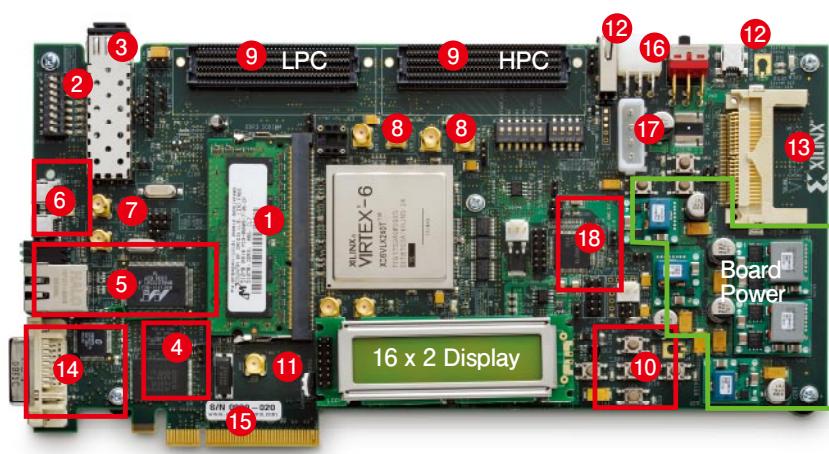

また、Virtex-6 FPGA ML605 評価キット（図 3）は、Virtex-6 LX240T FPGA でシステム デザインを開発するためのスケーラブルな環境です。このキットに含まれるシステム レベルの機能には、高速シリアル トランシーバ、PCIe® Gen2 ブロック、ソフト DDR3 メモリ コントローラ、ギガビット イーサネット、DVI などがあります。ISE Design Suite 11.2 Logic Edition、リファレンス デザイン、デモ、ボード デザイン ファイル、ドキュメント、ケーブル、電源もこのキットに含まれています。

## 簡単な 3 ステップでデザインをキックスタート

本キットは、ユーザーが箱からソフトウェアを取り出して走らせるまでに、3 ステップの処理で行えるよう簡単に設計されています。

ステップ 1 では、ボードと PC をケーブルで接続し、ボードの電源を入れ、リファレンス デザイン インターフェイス ソフトウェアをコンピュータにロードし、リファレンス デザイン デモを見て、そして作業を開始します。

ステップ 2 では、リファレンス デザインを評価します。このリファレンス デザインには、別のデザイン インプリメンテーションが含まれており、共通のファンクションをインプリメントするためにハード IP コアとソフト IP コアが使用されています。カスタマは、直接、基本となるリファレンス デザインから機能を評価でき、結果を視覚的に観察でき、同時に重要な性能統計を見ることができます。

ステップ 3 では、ISE Design Suite のデザイン ツールを起動し、リファレンス デザインをカスタマイズし、新しいデザインをソフトウェアで生成します。次に、それを評価ボードにダウンロードし、そのデザインを FPGA 上で実行します。「実際この作業は非常に簡単です。」そし

図 3 - Virtex-6 ML605 評価キットは、世界トップ クラスの機能性を有します。

| # Feature                     |

|-------------------------------|

| 1 DDR 3                       |

| 2 GPIO Dip Switch             |

| 3 SFP                         |

| 4 Flash                       |

| 5 10/100/1000 Ethernet        |

| 6 USB UART & USB JTAG         |

| 7 MGT Clock                   |

| 8 User Clocks                 |

| 9 FMC Connectors              |

| 10 Pushbuttons                |

| 11 MGT                        |

| 12 USB 2.0                    |

| 13 Card Reader for System ACE |

| 14 DVI Output                 |

| 15 PCI Express                |

| 16 12V Wall Adapter Power     |

| 17 12V ATX Power              |

| 18 Power Regulator Control    |

て「わずか数分で、セットアップして走らせることが可能です。」と Przybus は語ります。

ISE Design Suite 11.2 のリリースにより、ザイリンクスのツール スイートは Virtex-6 と Spartan-6 FPGA ファミリをサポートできるようになりました。全体の走行時間は 2 倍改善され、XST を使用したときの合成時間は 2 倍以上の改善、また配置・配線の最適化により全体の動的消費電力は 10 パーセント低減されています。加えて、以前の ISE バージョンと比較して、本ツールがワークステーション上で必要とするメモリは 28 パーセント少なくなっています。

ISE 11.2 は、SecureIP シミュレーション モデルをサポートしています。したがって Cadence 社、Mentor Graphics 社、および Synopsys 社からのサードパーティ シミュレータとの互換が容易です。また、Mentor Graphics 社の Precision RTL および Precision RTL Plus 製品はベース ターゲット デザイン プラットフォームをサポートしています。Synopsys (Synplicity) 社からの Synplify Pro と Synplify Premier ツールも同様です。

実際、ベース ターゲット デザイン プラットフォームおよび全体のターゲット デザイン プラットフォーム戦略における他の重要な要素として、IP コアのサポートがあります。ベース ターゲット デザイン プラットフォームのリリースに合わせて、ザイリンクスとこの IP コア パートナーは Spartan-6 と Virtex-6 FPGA ファミリをサポートする多くのコアを開発してきました。

次期 ドメイン特化製品とマーケット 特化製品には、これらの IP コア が搭載されることになるでしょう。たとえば、Northwest Logic 社 からの PCI Express® DMA Engine があります。ザイリンクスと Northwest 社は、この DMA Engine とデモ用アプリケーション およびドライバをパッケージにし、完全な Connectivity Targeted Reference Design を構築して、新しい Spartan-6

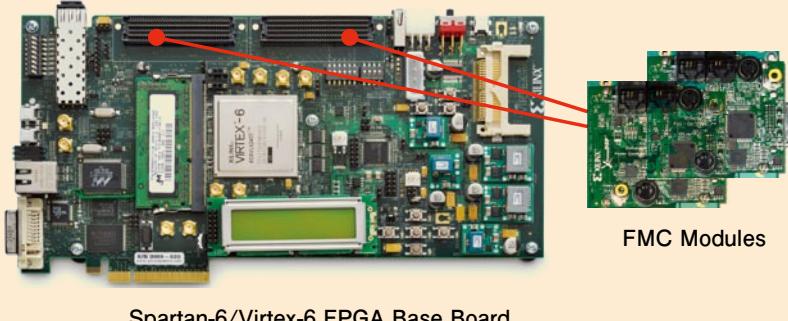

## FMC カードによるデザイン開発の促進

ターゲット デザイン プラットフォーム アプローチの成功への鍵の一つに、ザイリンクスと販売代理店および IP コア パートナーのネットワークが、VITA 標準化団体の FPGA Mezzanine Card (FMC) を相互に採用したことがあげられます。FMC は、ザイリンクスとパートナーによる ドメイン特化キットと マーケット特化キットをベース評価キットに取り付ける際の標準的なインターフェイスです (図 4 参照)。

この標準をベースにしたアプローチにより、ザイリンクス、およびサード パーティ コンポーネントやボードのサプライヤ (Avnet Electronics、Curtiss-Wright Controls Embedded Computing、Linear Technology および Northwest Logic の各社が含まれます) におけるザイリンクス ネットワークは、相互のカスタマに対して最新の優れた製品を提供できるようになります。

ANSI 承認の VITA 57.1 標準では、パラレル I/O、シリアル I/O、クロック、JTAG、制御信号および電源にあらかじめ定義された固定のピンを割り当てています。本標準に準拠した接続では、明確な高性能 Samtec SeaRay を使用しており、ローピン カウント (LPC) 4 × 40 並びと ハイ ピン カウント (HPC) 10 × 40 並びとなります。従来のザイリンクス FPGA ボードとの互換性を保つために、電圧互換 FMC HPC/LPC モジュールが含まれています。

— Mike Santarini

図 4 - FPGA Mezzanine Card (FMC) 接続により、IP コア とキットの迅速な開発が容易になります。

Spartan-6/Virtex-6 FPGA Base Board

と Virtex-6 およびザイリンクスのベース プラットフォームをサポートできるよう にしています。

ザイリンクスが販売する Spartan-6 FPGA SP601 評価キットの価格は \$295 で、Virtex-6 FPGA ML605 評価キットの価格は \$1,995 です。Spartan-6 FPGA SP601 評価キットは現在入手可能です。Virtex-6 FPGA ML605 評価キットは 7 月より発売開始しています。←価格と供給状況を確認してください。

い。

第 3 四半期に、ザイリンクスと販売代理店の Avnet 社は、コネクティビティ、エンベデッドおよび DSP スペース用に ドメイン特化キットの開発を予定しており、それに続いて通信、ビデオおよびブロードキャスト用のマーケット特化キットも予定されています。

詳細は、最寄りのザイリンクス オフィスまたは販売代理店にお問い合わせください。•

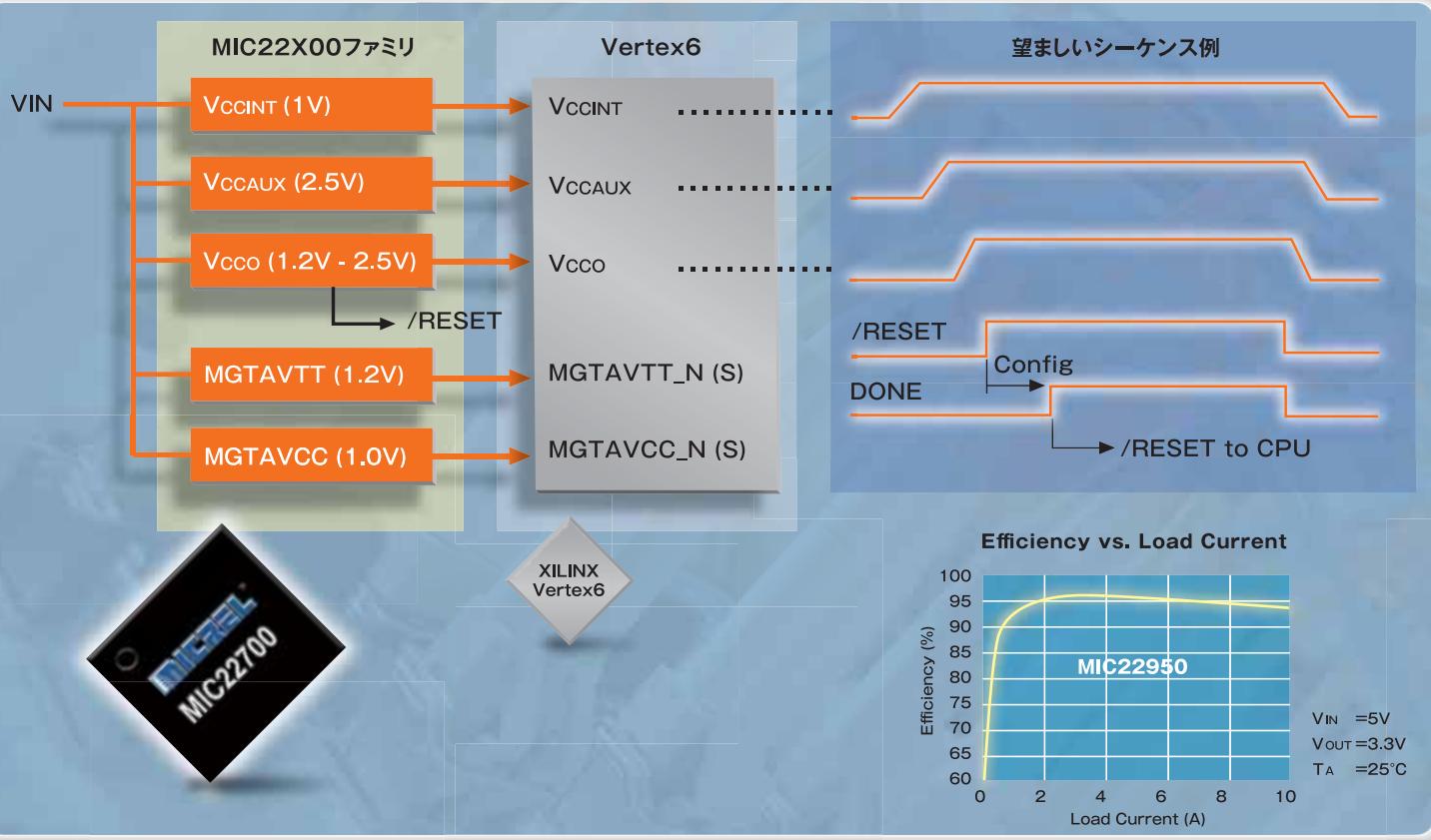

# MIC22000高効率/多機能BUCKレギュレータ

## FET内蔵、同期整流型、POL向け高機能2次電源IC

「FPGAの電源ON/OFFシーケンスは別に気にしなくても良いと言われた。」本当にそれでいいのですか？DS302, DS202, DS152, DS123を再度熟読してみて下さい。電源ON/OFFには順序が必要で電圧のランプ速度も規定があります。ランプ速度によってはコンフィギュレーションROMのRESET解除タイミング回路の設計に影響を与えます。高速通信向けのGTX用電源そしてPLL電源には、ノイズの無いLDOも考慮したいですね。高価な開発基板が電源トラブルではデバッグも開始できません。マイクレルMIC22000シリーズなら、専用のシーケンス制御ICを必要とせずにFPGAやASICが要求する電源要件を満たせます。

## 特長

- 統合されたMOSFET スイッチ

- 超高速応答で小型出力コンデンサ対応

- 2Aから15A超までの出力電流

- 0.7Vまでの出力電圧調整

- ランプ速度/遅延/POR出力調整可能

- 混載アナログ回路用にMIC68000ファミリLDOとも連動可能

- 2.6~5.5Vの入力電圧範囲

- 過電流保護/過熱保護/減電圧保護機能内蔵

## MIC22200 シリーズ製品

| 型番         | 出力電流 | スイッチ周波数       | パッケージ          | インダクタ       | 出荷状況 |

|------------|------|---------------|----------------|-------------|------|

| MIC22200   | 2A   | 2MHz,5MHz固定   | MLF12/ETSSOP16 | 1μH, 0.47μH | 量産中  |

| MIC22400   | 4A   | 800KHz-4MHz可変 | MLF20/ETSSOP20 | 2.2-0.47μH  | 量産中  |

| MIC22600/1 | 6A   | 1MHz,4MHz固定   | MLF24/ETSSOP24 | 1μH, 0.47μH | 量産中  |

| MIC22700   | 7A   | 1MHz固定        | MLF24/ETSSOP24 | 1μH         | 量産中  |

| MIC22950   | 10A  | 800KHz-4MHz可変 | MLF32          | 2.2-0.47μH  | 量産中  |

| MIC221500  | 15A  | 400KHz-2MHz可変 | MLF32          | 2.2-0.39μH. | 開発中  |

FPGAs Take Central Role in Wired Communications

# FPGA が有線通信機器の 中心的な役割を担う

高速化への要求とマルチメディアの出現により次世代ネットワークにおける高度なプログラマブル デバイスの必要性が急増

Mike Santarini

Publisher, Xcell Journal

Xilinx, Inc.

[mike.santarini@xilinx.com](mailto:mike.santarini@xilinx.com)

有線通信ビジネスには、スピードに関して飽くことを知らない高いニーズがあります。15年前、データ転送レート（帯域幅とも呼ばれる）は毎秒数100Kビット（数100Kbps）でした。しかし今日のネットワークでは、10Gbpsのスピードで世界中にデータを配信することができ、ネットワーク送信の特定の場所ではテラビット（=1000Gbps）にも達します。FPGAはこの進化の過程で一定の役割を担ってきましたが、その技術がムーアの法則をベースに進化するにつれて、次世代有線ネットワークでもより中心的な役割を担うことが考えられます。

AT&TやVerizonなどの通信機器メーカーは、マルチメディアコンテンツを配信する最新の高帯域幅ネットワークに多額の出費をいとわない加入者を呼び込むために、音声サービスに加え、何種類かの高速データ通信が可能な高速システムの構築を、ネットワーク機器メーカーに要求しています。市場調査会社であるiSuppli社のブロードバンドとInternet Protocol TV(IPTV)分野の主席アナリストSteve Rago氏は、電話会社の多くは音声のみのネットワークからビジネス転換を図ろうと緊急に模索していると指摘しています(12ページの補足記事を参照)。同様に、大手企業も従業員が世界的な規模で効率よく通信できるような高速ネットワーク機器を要求しています。たとえば金融業界では、高速ネットワークがあれば遠隔地のトレーダーは素早い発注が行えるようになります。より高速なデータ通信が可能になれば、文字通り売り上げ増加につながるというわけです。

Cisco SystemsやAlcatel-Lucent、Nokia-Siemens Networks、Juniper Networksなどのネットワーク機器メーカーは、データ転送スピードが40Gbpsと100Gbpsの機器の通信業者や一般企業への売り込みで先陣を競っています。そ

れにはまず、最先端でしかも最新世代のICで機能強化された次世代のルーターとスイッチを開発する必要があります。さらに、次世代ネットワーク標準、すなわち40Gと100G標準規格が進化していく過程でこの作業を行うことが重要です。

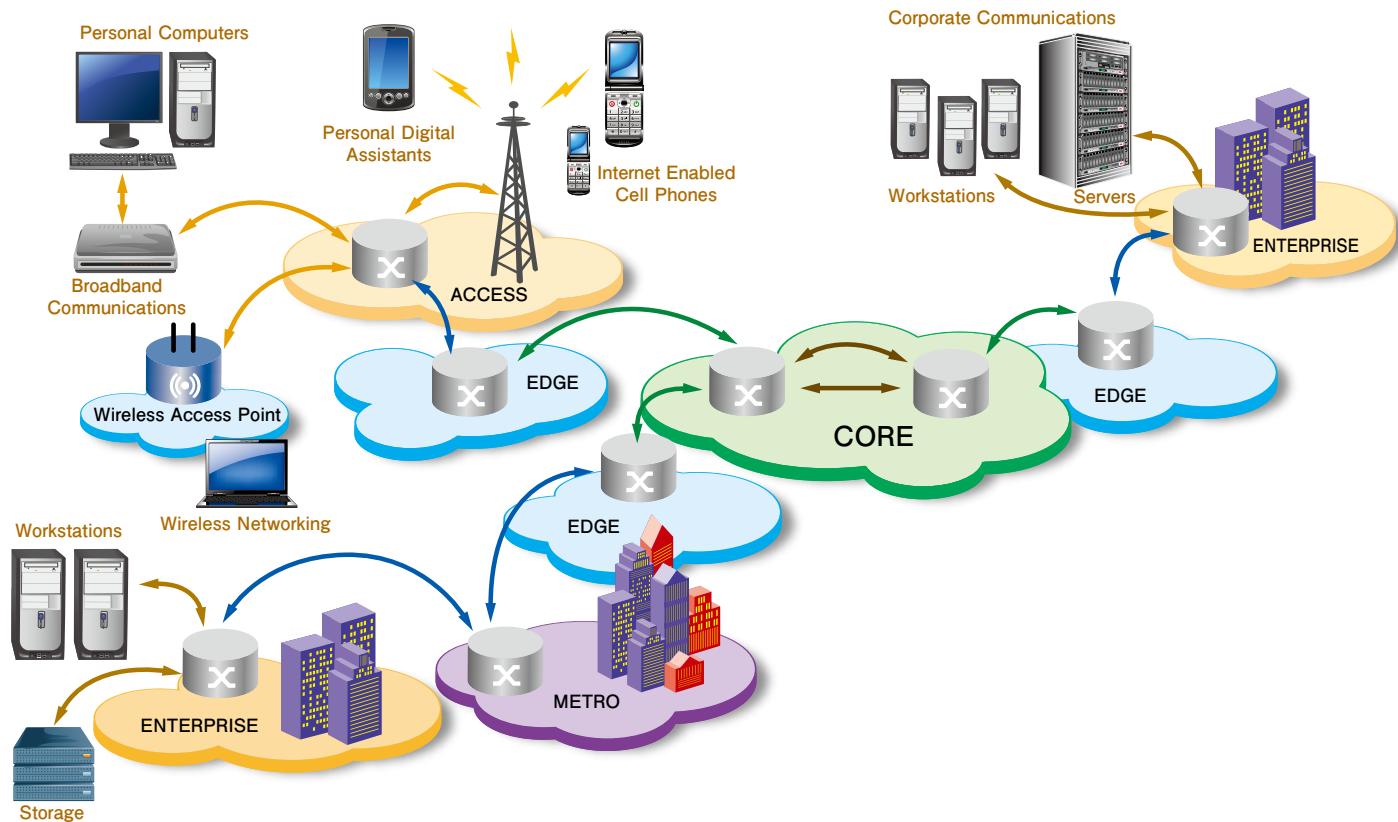

## ■ 有線ネットワークの基礎

今日の有線通信ネットワークは、一つの情報を他の目的地に結び付けるための、一般道路やハイウェイ、スーパー ハイウェイで構成される道路網のようなものです。道路の種類によりスピード制限は異なり、狭い裏道は全体の交通状況を悪化させ、かえって情報が目的地に届くまでに大変な時間がかかるかもしれません。

一般的のユーザーが家庭のPCからインターネットのサイトにアクセスしてファイルをダウンロードする場合、PCからのデータ要求はデータパケットの形式で最大1Gbpsの速度で行えます。この速度は、PCを通信事業者のアクセスネットワークに接続している銅配線により制限されます。このアクセスネットワークは、データパケットの特に転送先とサイズを読みだし、メトロネットワークに転送します。メトロネットワークは、一連の高速なルーターとスイッチで構成され、パケットを読みだして回線上の次のルーターへデータを転送します。メトロネットワーク上でのルーターからルーターへのデータ転送速度は10Gbpsです。

長距離ルートの場合、メトロネットワークは最終的にコアと呼ばれるデータのスーパー ハイウェイに接続されることになります。このコアは光ネットワークで、Webページやビデオクリップ、音楽などのインターネットファイルを保持するデータサーバーに近いメトロネットワークへ高速にデータ転送を行います。それを受けたデータサーバーは、要求されたデータファイルをネットワークを介して送り返します(図1)。

それぞれの交点、すなわちハブにおけるルーターは、データパケットに含まれる転送先やサイズなどの情報を読み、ネット

図1-40～100Gbpsの帯域幅で動作する次世代有線通信ネットワークは、新世代のブロードバンドサービスや多くの新しい電子デバイスに拍車

ワークの現在のトラフィック条件下で最も早いルートを決定する必要があります。そしてそのデータを次の交点に送り出します。長距離ルートを光ネットワークに接続するには、光ネットワークの一番前のルーターが、電子ルーター用のデジタル信号で書かれたデータを光領域で使用できるプロトコルに変換する必要があります。最終的に、コアネットワークの終端では他のルーターが逆の作業を行います。すなわち、光データを再変換して電子パケットの形式に戻します。そして、ネットワークの現トラフィック条件下で最も速いルートを探して、次の電子ルーターあるいはデータサーバーへそのデータを送り出します。

アクセスやダウンロードは、ファイルのサイズやロケーションにより異なりますが、通常数秒から数分で終了します。FPGA技術が常に進化していることにより、将来のネットワークはさらに高速化されます。

### テレコムとデータコムのコンバージェンス

現在有線ネットワークには、コンピューティング用とテレコム用の2種類があります。従来これらのネットワークは別々のものでした。各々が独自のプロトコルを持ち、ルーター用の機器や、帯域幅に対する要件および帯域幅の成長率も異なっています。たとえば、一般的にテレコム業界での帯域幅の増加は4倍ずつ(2.5Gbpsから10Gbps、現在は40Gbpsに移行中)行いますが、コンピュータネットワーキングではそれが10倍ずつ(100M、1G、10G)となっています。しかしながら、ザイリンクスのエンジニアであるGordon Brebnerによると、有線ネットワークの改革が行われた数年前から10Gbpsで2つのネットワークの融合が始まっています。これは、両ネットワークがそれぞれ最高帯域幅レートを増大させる過程で、イーサネットの物理信号方式とテレコム信号方式

が融合していくことを指しています。これらのネットワークは、現在は独立しているとはいうものの、ネットワーク業界では過去数年前からそれらを特にイーサネットに融合しようと努力してきました。

「イーサネットは、単にユーザーをユーザーのIT部門に接続するための手段であると考えられていました。」と、Brebnerは述べています。「現在ではイーサネットはどこにでも存在するが、それが通信事業者間のイーサネットに発展して、通信業界はこのイーサネット技術を自社のネットワーク上で使用するようになりました。」10Gbpsイーサネット(10GE)技術については、「ここ数年間で標準化が行われてきました。」と、Brebnerは述べています。「そして現在は、40GEと100GEと一緒にIEEE 802.03baへの起草が進められており、最終的にこの標準化作業は2009年後半に完了すると期待されています。」

Brebnerは、40GEがテレコムの次の

ステップになるのではないかと主張しており、業界でも 40GE は初期の企業内ネットワークに最適であると考えられています。通信事業者は、長距離送信に 100GE 標準を使用するでしょう。しかし競争が激化し、機器メーカーが企業内ネットワークにも 100GE を採用する事例もでてくることでしょう。

## ルーターの内部

ネットワーク機器メーカーが高速データを転送するには、最新の設計回路によって非常に高度な電子機器（ルーター、スイッチ、転送システムなど）を製造する必要がでてきます。

たとえば、メトロ ルーターの心臓部は一連のライン カードで構成されていますが、それぞれのライン カードは、種々のプロトコルで書かれたデータ パケットを受信し、パケットの発信元やサイズ、転送先を調べると同時に、ネットワークのその他の部分に関する情報も調べた上でパケットをスイッチに送ります。次にスイッチは、そのパケットをネットワーク上の次の転送先に送ります。ライン カードは、これらすべての計算を数ナノ秒という非常に短い時間で実行する必要があります。

従来のライン カードは、1 つの CPU、専用ネットワーク プロセッサ ユニット (NPU) および複数の高速 FPGA で構成されていました。パケットがライン カードに入ってくると、FPGA でルーターが読めるフォーマットに変換します。プロセッサは、NPU がデータを送受信できるようにする必要がありますが、FPGA が CPU と NPU 間のプロトコル変換を行います。

ルーターはパケットを適切に処理するのに、複数のプロトコルを解読する必要があります。実際には、1 つのパケット内に重層配置されている各種のプロトコル（従来のものから最新のものまで）をサポートする必要がある、と Brebner は述べています。もちろん、世界全体が 1 つのプロトコルあるいはプロトコルのセットで統一することができれば、ネットワークのスピードアップも可能でしょう。ネットワークが競

合他社より優れていることをアピールするための差別化の多くは、ルーターが使用するプロトコル上で行われていると Brebner は指摘しています。通信事業者は、この競争上の優位性を追求していくことでしょう。

次世代有線ネットワークは、音声やインターネット データ、ビデオを同時に転送できるようになっていきます。いわゆるこのトリプル プレイには新しいプロトコルの開発が必要で、通信事業者はこのデータの転送をより効率よくより安全に行うために、一連の微調整や変更は避けられないでしょう。

すなわち、ハードウェアを修正して機能性を変更する能力が重要になってくるわけです。その能力によって通信機器が新しいプロトコルを利用できるようになり、結果

OEM メーカーに大きなメリットを提供できるようになります。多くの企業は、自社の通信システムでは ASIC や ASSP は自身のソフトウェアのみを変更するだけの機能しかないという理由でその使用を避けています。これとは対照的に、FPGA を使用すればハードウェアの変更も可能で、しかもソフトウェア領域でソフトウェアの機能性をテストすることもできます。また、アルゴリズムのハードウェア インプリメンテーションを FPGA 内に生成することで、さらなる高速化が図れます。

NPU の機能性をプログラマブル ロジックのファブリック内に統合することにより、ルーター内で FPGA により中心的な役割を担わせることに期待を寄せている機器メーカーもあります。傾向として、FPGA ベンダは半導体ベンダのなかでも先

表 1 - ザイリンクス SERDES の豊富な Virtex-5 TXT は、次世代有線通信機器の開発者に革新的なプログラマブル プラットフォームを提供

| Virtex-5 TXT FPGA プラットフォーム                           |                |            |

|------------------------------------------------------|----------------|------------|

| 製品番号                                                 | XC5VTX150T     | XC5VTX240T |

| スライス                                                 | 23,200         | 37,440     |

| ロジック セル                                              | 148,480        | 239,616    |

| CLB フリップフロップ                                         | 92,800         | 149,760    |

| 分散 RAM の最大数 (Kbit)                                   | 1,500          | 2,400      |

| ブロック RAM/ECC 付 FIFO (各 36Kbit)                       | 228            | 324        |

| トータル ブロック RAM (Kbit)                                 | 8,208          | 11,664     |

| デジタル クロック マネージャ (DCM)                                | 12             | 12         |

| フェーズ ロック ループ                                         | 6              | 6          |

| シングルエンド ピンの最大数 (4)                                   | 680            | 680        |

| DSP48E スライス                                          | 80             | 96         |

| PCI Express エンドポイント ブロック                             | 1              | 1          |

| 10/100/1000 イーサネット MAC ブロック                          | 4              | 4          |

| RocketIO™ GTX 高速トランシーバ                               | 40             | 48         |

| パッケージ (7, 8) エリア                                     |                |            |

| FFA パッケージ (FF) : フリップチップ フайнピッチ BGA (ボールピッチ 1.0 mm) |                |            |

| FF1156                                               | 35 x 35 mm     | 360 (40)   |

| FF1759                                               | 42.5 x 42.5 mm | 680 (40)   |

|                                                      |                | 680 (48)   |

駆者として新しいプロセス技術の採用を行なってきました。ムーアの法則に基づくと、同じ面積に実装できる FPGA のロジック容量は 2 倍になっていきます。それにより従来では搭載できなかった新たな機能の追加が可能になります。FPGA の世代が新しくなるたびに、従来 NPU が実行していた機能を FPGA に代替できる可能性が高まります。プロトコル変換やインターフェイ

スの機能性をワンチップ上に統合することにより、ルーターの処理能力が向上し、全体の部材コストの低減に加え消費電力も低減されることから、最終的にはネットワーク全体の運用コストが削減されます。さらに、FPGA はソフトウェアと同様にハードウェアのリコンフィギュレーションができ、その結果フィールドでの仕様変更が可能になります。したがってネットワーク機

器のベンダは、自社製品が稼動中でも市場でアップグレードする機会が得られます。

FPGA は、さまざまな分野のなかでも特に有線通信アプリケーションに最適な形で急速に進化しており、ネットワーク機器設計者が次世代ルーターに採用する機会はますます増えています。ネットワークインターフェイスのスピードが増加している状況に対応するため、新世代 FPGA には数

## ブロードバンドの大金をめぐる戦い

最近電話会社では、競合するケーブル会社に音声サービスの利用者を横取りされ、収益の落ち込みに直面しています。この打開策として、ネットワークを補強してマルチメディアサービスの提供を急いでいます。これは潜在的に、次世代ブロードバンド製品の新たな成長を後押しすることになるでしょう。

「ここ数年間、電話会社は驚くべき割合で加入者数を減らしてきました。」と、iSuppli 社のアナリスト Steve Rago 氏は述べています。「毎年、およそ 4 ~ 10 パーセントの加入者が他のサービスに奪われています。」

この現象にはいくつかの理由が考えられます。「まず第 1 は、多くの人々が携帯電話を唯一の電話回線として使用していることです。」そして、「第 2 の理由は、インターネット用の第 2 の回線の必要性の有無が挙げられます。場合によってはファックスの必要性さえ無くなりつつあります。ブロードバンドがあればインターネット向けの第 2 の回線は不要です。」と Rago 氏は述べています。加えて、ケーブル マルチサービス オペレータ (MSO) は、音声サービスをケーブル TV やインターネットと一緒にまとめるこによって、従来の音声サービスの利用者の獲得に成功している、と指摘しています。昨年の第 4 四半期に、「米国だけで、ケーブル会社は 100 万人におよぶ音声サービスの加入者を獲得しました。」と、Rago 氏は述べています。今、同様の変化が世界的な規模で起きています。音声ネットワークが採用されて 12 年位しかたっていない中国本土でさえ、同じ現象が起きていると指摘しています。

Rago 氏の指摘によると、通信事業者だけは現在提供しているブロードバンド サービスからの売り上げ増加を享受しています。しかし、音声サービスの売上高の損失を相殺するまでには至っていません。「彼らの最終結果は、売上高の成長でみればほとんど変わらないか、多少成長は減衰しています。したがって、ウォール街に対してはあまり良い立場にあるとは言えません。」と、述べています。「通信事業者がビジネスに対する基本方針を変えない限り、彼らは消滅してしまうでしょう。もはや彼らを必要としている人は誰もいません。」

その一方で、有線分野での彼らの競争相手である MSO もさほど大きな成長をしているわけではない、と Rago 氏は述べています。「実際に、競争相手である衛星通信会社と通信事業者の参入により、売上高は横ばいか、やや低落傾向にさえあります。」と、同氏。

世界中の電話会社は、会社を成長軌道に戻すために、音声サービスに他のサービスとともにビデオを付加価値サービスとして追加することを同業他社と決定したようだ、と Rago 氏は述べています。彼らは、インターネットベースのサービスの一つ、特にタイム シフティング TV に期待をかけています。これは、見たいプログラムをいつでも見たい時間に見ることができるようになるサービスです。「現在見ていく TV 方式からのパラダイムのシフトと言えます。それは、テレコム

会社が IPTV を採用することによる MSO にはない利点の一つです。」

さらに通信事業者は、毎秒あたりのビット数を基準にして顧客に請求するのではなく、MSO が今日やっているものと同じ方式を採用することに決定した、と Rago 氏は述べています。「ビデオ サービスに対しての支払い（たとえば、IPTV）や、音声その他サービスに対しても料金を支払う必要があります。プランにどんなサービスを追加するかによって、支払額が決まります。」ほとんどの電話会社がこの新しいサービスをすでに提供しているか、今後提供を計画している、と Rago 氏は述べています。

### 数 10 億ドル争奪への課題

一方で、MSO は従来の音声サービスの加入者を彼らのマルチメディア ミックスに引き込もうとする試みを今後も続けることでしょう。おそらく MSO は、彼ら独自の付加価値サービスを用意しているでしょう。

電話会社と MSO が共通に抱える数 10 億ドル争奪戦の課題は、いかに成長を達成するかではなく、いかに持続可能な成長を達成するかにあります。

その方法の一つは、「新しいサービスをすべて提供できる十分な機能を家庭に引き込むことです。」と、Rago 氏は述べています。世界的に DSL、とくに ADSL はユーザー規模で最大級のものだと彼は述べています。「しかし、ブロードバンド DSL や光ファイバーを家庭に引くことが多くなっています。あるいは、家の近くまでは光ファイバーで、縁石の近くまでは BDSL のような形式もあります。新しいサービスでいうと、光ファイバーを家庭に引くのは 2 番目となり、それは、ケーブル モデムをはるかに凌ぐ勢いです。」

もちろん、アクセス機器をアップグレードして新しいサービスに対応することが、これらを可能にする鍵となります。「我々は 30Mbps ~ 100Mbps のスピードに対応した機器に注目しています。」と Rago 氏は述べています。タイム シフティング TV やビデオ オン デマンドなどの新しいサービスは、ネットワークのバンド幅にかなりのプレッシャーをかけることになります。「革新と強化に対する主なニーズは、長距離とメトロ ネットワーキングの分野で求められているでしょう。」それはまた、高速データ通信向け民生用デバイスの成長をもたらす可能性もあります。逆に、そのデバイスが次世代サービスの形態要件を決定するかもしれません。

実際、「ブロードバンドの大金をめぐる争奪戦」は新しい技術とサービスを生み、究極としてその技術は関連分野の技術革新につながります。誰がその戦いに勝利するかは、現時点では推測の域を出でていない、と Rago 氏は述べています。

詳細は iSuppli 社の民生通信に関する最新レポートで確認してください。

多くの高速トランシーバ機能が提供されており、ネットワーク全体のバンド幅が増加しても対応可能です。たとえば、Virtex® -5 TXT デバイス（表 1）には、6.5Gbps で動作する RocketI/O™ マルチレートトランシーバが最大で 48 個搭載されています。このトランシーバをすべて使用するとデバイスの総バンド幅は 312 Gbps となり、高速ネットワーク ブリッジの構築には十分なものとなります。

高速トランシーバに加えて、最新 FPGA のロジック セル数はほぼ 2 倍になっており、これはムーアの法則にかなうものです。新しく追加されたロジック セルを使用することで、FPGA により多くの機能性を配置することが可能となり、従来 NPU に割り当てていた機能を FPGA に実装することも可能になります。

機器メーカーにとって、設計する機器の世代ごとに NPU を開発したり、設計内容に応じて適切な NPU を選択することは最も困難な課題である、と Brebner は述べています。ルーターの世代ごとに、NPU の性能を最大限になるよう設計することでシステム統合時に新たな問題が生じたり、最適な NPU の選択が複雑化し難くなったりしています。「NPU は市場で最も手に負えない分野です。NPU はそれぞれ、いろいろな特定分野の機能を満たすよう特殊な方法で設計されています。」と、同氏。NPU ベンダの業界は不安定で、NPU の設計会社も参入や撤退を繰り返しています。その結果、Cisco Systems 社などの大手ベンダのみが独自の製品を開発することになったのです。

FPGA は世代ごとに進化を重ねており、設計者自身が NPU の知的設計資産（IP コア）を FPGA に構築する機会が増えてきています。OEM メーカーは FPGA をシステムにあわせてリコンフィギュレーションすることが可能なため、異なるプロトコルのデータ パケットが入ってきた際、そのプロトコルに最適な NPU アーキテクチャを FPGA に実装することができます。また、FPGA でセキュリティ チェックを実行し、転送先までの最速ルートを探索して、そこにデータを送ることもできます。

図 2 - Virtex-5 FPGA にインプリメントされた Sarance Technologies 社の 100GE MAC ソリューション

「従来 FPGA は、エンベデッド RISC 機能や簡易な制御機能の実行に使用されてきました。」と、長期間通信分野に従事し、EDN 誌の新しい FPGA Gurus Web サイトのモデレータでもある Loring Wirbel 氏は述べています。「今日の FPGA は多くのデータパス機能を取り扱えるようになってきています。FPGA 1 チップで、企業内のアグリゲーション ボックス用途や、大規模スイッチング センタのブレードの機能を担うことができます。FPGA に実装する機能を適切に分割することで、コプロセッシングする必要はなくなります。大きな流れとして、ネットワーク プロセッサ（NPU）はゆっくりではあるが確実に終焉を迎えつつあり、一方 FPGA が NPU の機能に取つて代わる時代を迎えていきます。」

従来、新世代の機器が市場投入された際、NPU ベンダが提供するパケット転送エンジンを市場に送り出せる機会は、ほんのわずかな期間しかありませんでした。瞬きする間に機会は通り過ぎ、その転送エンジンは FPGA によって取つて代わられてしまう、と Wirbel 氏は指摘しています。

「40G や 100G ネットワークに移行する際には、パケット通信のみを行う非常に高速なエンジンが一時的に使用されることがあります。これは、1G と 10G ネットワークへの移行時にも起こった現象で

す。」と、Wirbel 氏は述べています。「しかし、新しい標準への移行時期は限られていて、多くの人は ASSP を顧みることなく、FPGA に目を向けることでしょう。すべての世代で ASSP が使用されるわずかな機会がありましたが、それもどんどん少なくなってきており、最終的にはまったく使用されなくなるでしょう。」

## 有線通信向け先進 FPGA 技術

ザイリンクスの大規模 Virtex-5 TXT XC5VTX240T FPGA には、37,440 のロジック スライスが搭載されており、ロジック セル数の合計は 239,616 になります。設計チームや IP コアのベンダは、今日先進の FPGA アーキテクチャを使用することで、XAUI や RXAUI、Interlaken、Sonet、ODN をはじめ多くの標準規格に対応できる革新的なソリューションを開発する機会が得られます。

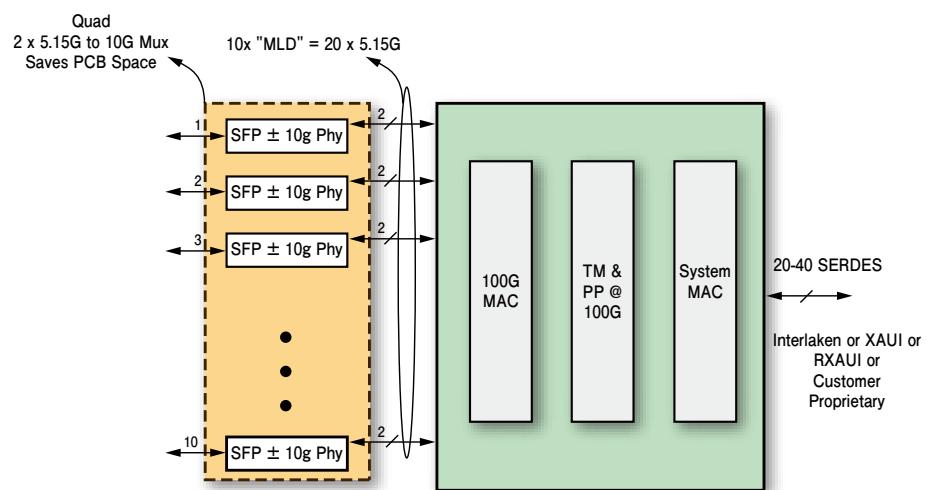

ザイリンクスは、その他にも Sarance Technologies 社との協業により業界初の 100GE メディア アクセス コントローラ（MAC）を開発しました。これは、IEEE 802.3ba に準拠した全機能を搭載したソリューションで、Virtex-5 FPGA にインプリメントされています（図 2）。

Sarance 社は、2008 年の中ごろに

100GE MAC ソリューションの完成を発表しました。これは、世界的装置ベンダの次世代機器のハードウェアプロトタイプ上で動作するもので、Virtex-5 FXT FPGA を 2 個、外部 10Gbps 物理層デバイスを 10 個、それに各種のシステム側インターフェイスを使用しています。

新しい Virtex-5 TXT FPGA プラットフォームがサポートしている 100GE MAC から Interlaken へのブリッジソリューションは、1 個の FPGA と 3 個の外部クワッド SERDES マルチブレクサに機能性を凝縮した低リスクの手法です。このインプリメンテーション手法では、64 B / 66 B、64 B / 67 B エンコード/デコードギアボックスが GTX トランシーバ内に構築されているため、回路設計に必要なロジック数は約 1/5 に削減され、消費電力も低減されます。

2008 年 6 月、通信機器の最大手 Comcast Corp. 社は、業界初の 100GE ルーターインターフェイスを使用して、フィラデルフィアとバージニア州マックリーンを結ぶ既存の基幹インフラ上で

100GE 技術のテストに成功しました。このシステムでは同じく Sarance Technologies 社の High Speed Ethernet IP Core (HSEC) を使用しており、現在は Virtex-5 TXT プラットフォーム上に実装されています。

100GE 分野でのデモは、これ以前にも行われています。2006 年 11 月、ザイリンクス FPGA を使用したシステムで、実運用されているネットワークを介して世界初の 100GE 送信テストが行われました。このデモは、高性能コンピューティングやネットワーキング、ストレージおよび解析を扱う SC06 国際会議のショーケースで行われました。

Finisar 社は、Level 3 Communications 社、Internet2 社およびサンタクラーズのカリフォルニア大学チームと共同で 100GE トラフィックの送信を実演しました。使用した回線は、フロリダ州タンパにある展示サイトとヒューストンを結ぶ Level 3 社の DWDM ネットワークで、折り返しの総距離は 4,000 マイルに及びます。

このデモでは、ザイリンクス FPG A は 10 本の電気信号から、10 本の 10Gbps XFP 光トランシーバへの変換をしています。この光トランシーバを通して、Infinera 社の商業的に利用可能な DTN Switched WDM System に送られ、これが Level 3 ネットワークに伝送されました。

FPGA の技術は加速度的に発展しています。発展を重ねるごとにムーアの法則により高集積化が達成されています。通信機器の設計者は、FPGA により高バンド幅の次世代ネットワークを構築することが可能となります。ネットワークの設計者は、遠くない将来、FPGA にシステム設計の中心的な役割を与えることになるでしょう。その役割がどの程度重要なものになるかは、シリコンだけではなく、設計者が自由に使用可能な IP コアやハードウェア、ソフトウェアツールにも依存します。ザイリンクスは、今後も業界を牽引しながら新しいプログラマブルロジックソリューションを確立し、有線通信市場に技術革新をもたらすための努力を続けます。 ●

## GET ON TARGET

**パートナーの皆様御社の製品・サービスを

Xcell journal 誌上で PR してみませんか？**

Xcell Journal は、プログラマブルロジックユーザーへ、ザイリンクス製品/ツールの最新情報をはじめ、システム/アプリケーションの解説、サービス/サポート情報、サードパーティ各社のツール情報などをお届けしています。

現在では日本各地の 10,000 名を超える幅広い分野のエンジニアの皆様に愛読いただいており、ザイリンクスが主催・参加するイベントでも広く配布しています。

貴社製品/ソリューションのプロモーションに非常に効果的なメディアです。

広告掲載に関するお問い合わせ先

Xcell Journal 日本語版への広告出向に関するお問い合わせは

e-mail にてご連絡下さい。

有限会社 エイ・シー・シー sohyama@jcom.home.ne.jp

**Xcell**

PUBLICATIONS

# ThreadX for Xilinx

MicroBlaze, PPC405, PPC440 に対応済み！

軽い！早い！

業界最高速の

リアルタイムOS

TH R E A D X®

TH R E A D X μITRON

高性能な FPGA の複数のコンポーネントを同時に動作させるためには、リアルタイム OS は欠かせません。

ThreadX は、米国 Express Logic 社が組み込み用に設計開発した高速なリアルタイム OS (RTOS) です。ThreadX はこのクラスのRTOSとしては業界最高速であり、PicoKernel(TM)と名づけた小さなフットプリントでリアルタイムのレスポンスを要求する組み込みアプリケーションには最適な環境を提供しています。

ThreadX-μITRON は、ThreadX に対応したμITRON ライブライアリです。ユーザアプリケーションは ThreadX を意識せず、純粋な μITRON RTOS として使用することができます。

N E T X™

- ThreadX 専用ネットワークプロトコルスタック

- コンパクトで高速

- プロセッサに非依存

- DNS や FTP などの上位プロトコルも提供可能

- BSD 互換ソケットレイヤも用意

NETX

F I L E X™

- ThreadX 専用 FAT ファイルシステム

- コンパクトで高速

- プロセッサに非依存

FILEX

ThreadX の評価版 (MicroBlaze 版、PPC405 版) を用意しています。ぜひお試しください！

<http://rtos.jp/download/demo.html#Xilinx>

株式会社 グレープシステム® 営業部

横浜市西区みなとみらい 2-3-3 クイーンズタワー B 8F 〒220-6108

TEL:045-222-3761 FAX:045-222-3760

e-mail [threadx@info.grape.co.jp](mailto:threadx@info.grape.co.jp)

URL <http://rtos.jp/>

\*各製品名は各メーカーの登録商標または商標です。

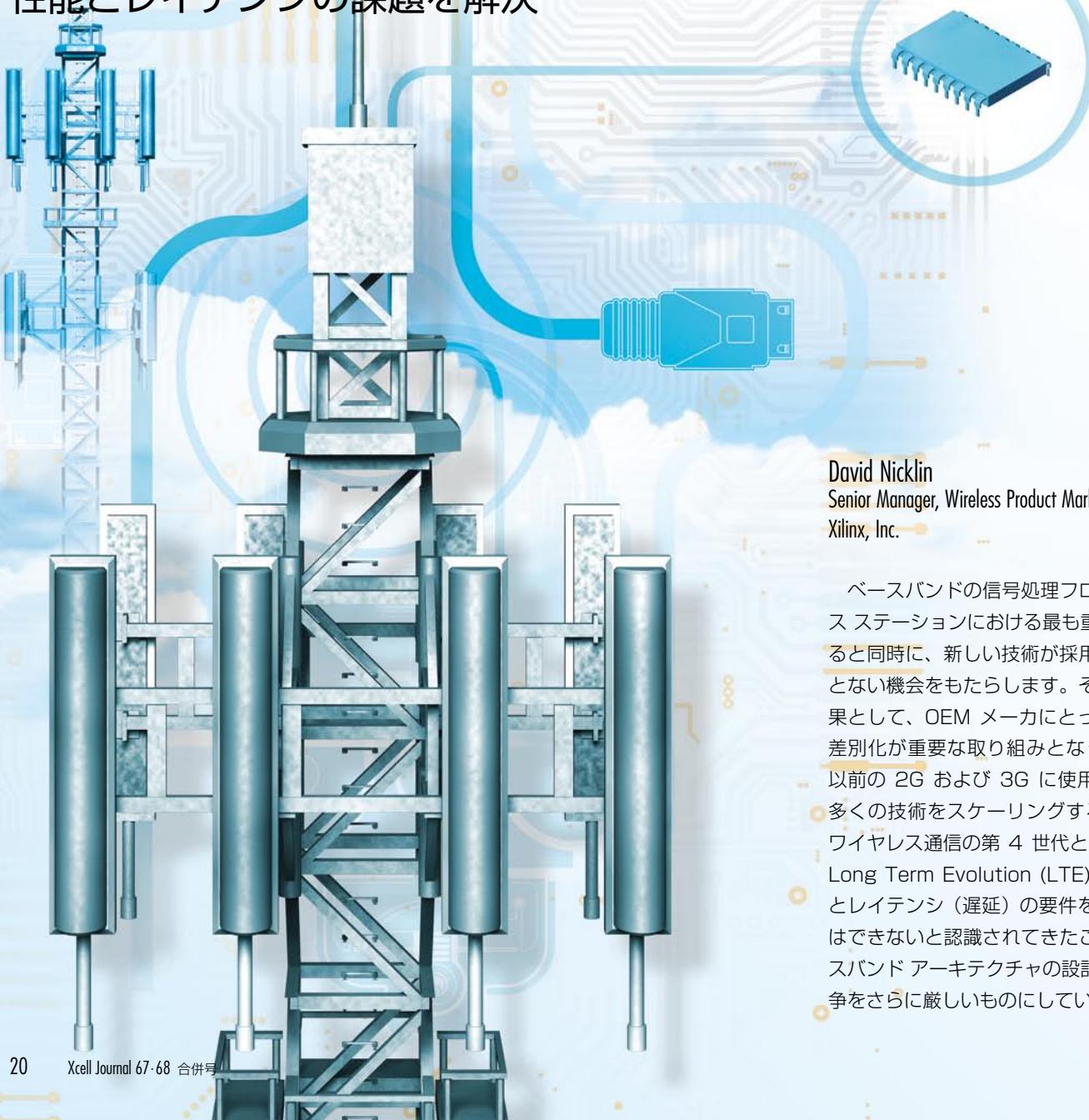

# Baseband Development for 3GPP-LTE Just Got Easier

## 3GPP-LTE 向けベースバンドの開発がより容易に

ザイリンクスの LTE-Channel Encoder と Decoder により、Layer-1 サブシステムの開発を加速し、4G ワイヤレス通信における性能とレイテンシの課題を解決

David Nicklin

Senior Manager, Wireless Product Marketing

Xilinx, Inc.

ベースバンドの信号処理フローは、ベースステーションにおける最も重要な鍵であるとともに、新しい技術が採用されるまたない機会をもたらします。その当然の結果として、OEM メーカにとって製品の差別化が重要な取り組みとなっています。以前の 2G および 3G に使用してきた多くの技術をスケーリングするだけでは、ワイヤレス通信の第 4 世代となる 3GPP Long Term Evolution (LTE) 技術の性能とレイテンシ（遅延）の要件を満たすことはできないと認識してきたことも、ベースバンドアーキテクチャの設計における競争をさらに厳しいものにしています。

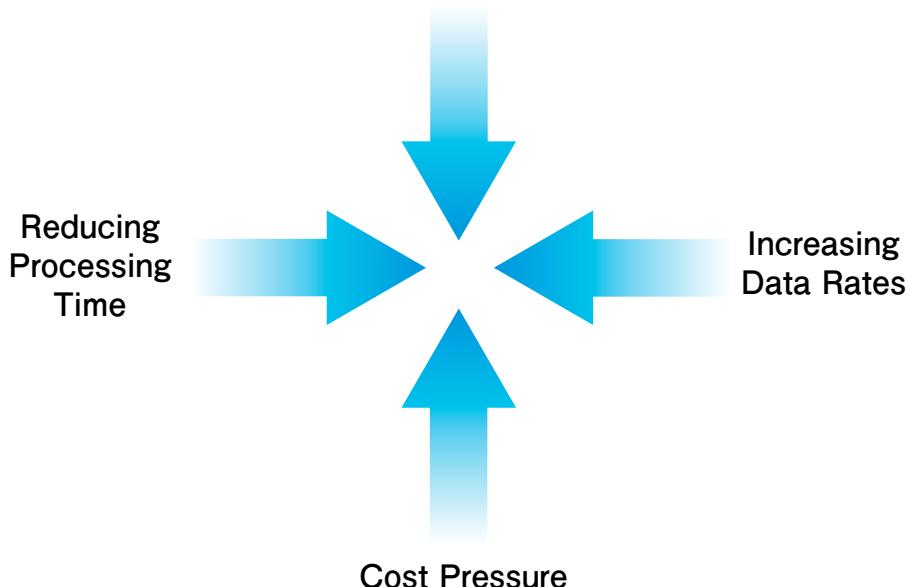

一連の信号処理には、これまで以上の処理量が要求されているだけでなく、すべての信号処理を短時間で完了させる性能が求められています。さらに、システム設計者は、オペレーターからのシステムコストや運用コストの削減目標を達成するシステムを開発する必要があります。このためベースバンド信号処理システムの設計は、図1に示すような条件や課題をクリアしなければならないのです。

FPGAベースのソリューションでは、先述の要求すべてを満たすことができ、通常問われる性能の問題やボトルネックが解されます。ザイリンクスが新たにリリースしたLTE Uplink Channel DecoderおよびLTE Downlink Channel Encoder LogiCORE™は、Layer-1で必要とされる多数のファンクションを1つにまとめIPコアソリューションとして提供するもので、このようなシステムへのFPGAの導入を容易にします。

シリコン技術の進歩は、今まで以上に複雑なアルゴリズムの実現が可能となり、それがワイヤレス通信分野における成功の鍵となっています。この成功例の1つは、3Gネットワークにおけるターボ符号によるエラー訂正テクニックの普及であり、これは10年を待たずして市場製品に広く採用されるようになった設計方法です。技術革新は日々加速化しており、MIMO(Multiple-Input, Multiple-Output)アンテナ技術によって、ワイヤレス通信に空間次元が用いられるようになったことは、その顕著な一例です。

しかし、4Gエアインターフェイスの登場により、従来のDSPプロセッサ中心のチャネルカードアーキテクチャではこのような現実への対応が難しくなっています。従来どおりFPGAとDSPで機能分割していくには、莫大な量のデータが両デバイス間を行き来するために生じるボトルネックにより、十分なパフォーマンスを出すことができません。

それでは、このボトルネックはどのように解決すればよいのでしょうか。その鍵は、Layer-1システムアーキテクチャを簡素化し、チップ間の不要なデータ転送をすべ

図1 - ベースバンド信号処理における課題

## More Complex Algorithms Iterative Techniques

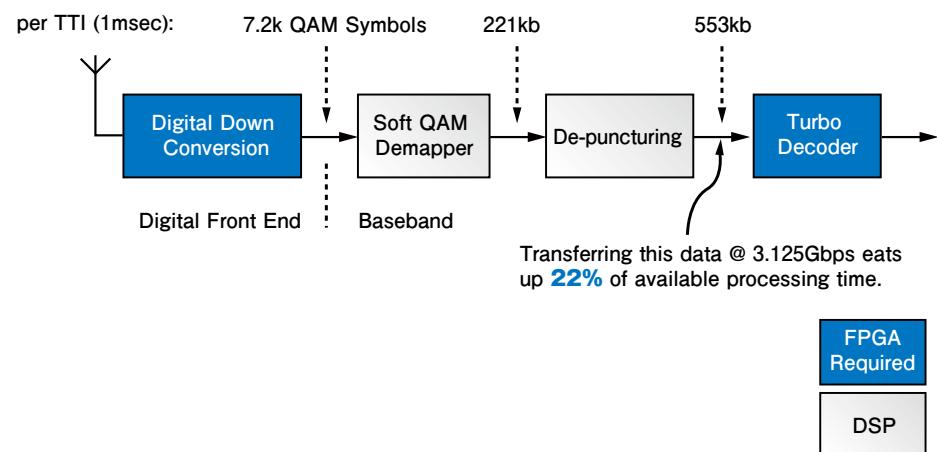

図2 - 典型的なLTEシステムでFPGAとDSP間に必要なデータレート

てなくすることになります。ただし、DSPプロセッサで実現するアーキテクチャのスケーラビリティでは問題が生じます。Layer-1のファンクションのほとんどをDSPではなくFPGAに移行するには、多数のIPコア、ソフトウェア、サポートなどが必要となります。

## Layer-1デザインの簡素化

FPGAを1つのコプロセッサとして採用し、DSPプロセッサではなくFPGAにターボデコーディング機能を持たせる際に生じうる問題点について詳しく考察してみましょう。ザイリンクスのシステム設

計者が、典型的な LTE ベースバンド デザインで図 2 のように処理を分割させていける場合の効率を解析したところ、SRIO 接続を介した DSP プロセッサと FPGA 間のデータ伝送だけで、許容レイテンシの 20% 以上が使用されることがわかりました。しかも、これはワースト ケースとはほど遠い状況です。たとえば、64-QAM、1/3 コード レートの 2 MIMO コード ワードなど、高次変調方式でコード化されたデータを 20MHz LTE のフル バンドで追加すると、許容レイテンシに占める割合はさらに大きくなります。

この問題に対して、より高速な数ギガビット トランシーバを追加接続することでバンド幅を増やし、データを伝送するという単純な回避策が考えられます。確かにこのようなシステムは構築可能ですが、システムの消費電力が不必要に増大してしまいます。その理由は、相対的に消費電力が多い高速シリアル接続でデータを伝送するだけでなく、ブリッジ ファンクションが複製されることで、より多くのハードウェア リソースが使用されるためです。

ここに上記の方法よりも効率的で最適化されたソリューションがあります。Layer-1 ファンクションのほとんどを FPGA に取り込むことにより、この不必要的オーバーヘッドを解消してシステムのスループットとレイテンシを改善すると同時に、消費電力の要件を下げることができます。

消費電力の低減だけでも、信頼性の改善に直接つながり、システム コストと運用コストの削減になります。

このようなアーキテクチャでは DSP は不要となります。必要に応じて、DSP で低レートのファンクションを実行させることも可能です。そのための機能分割は Layer-1 ベースバンド処理全体を FPGA に実装し、メディア アクセス制御 (MAC) や HARQ 処理など上位 Layer のファンクションを、より費用対効果の高い汎用プロセッサやネットワーク プロセッサに任せることです。これらのプロセッサは、バックホールとの接続に必要なファンクションを追加することも可能です。高い性能と短い処理時間が必要とされるファンクションすべてを 1 つの FPGA に効率よく統合することで、遅延とバンド幅に対する制限を軽減させることができ、分割もずっと容易になります。

このようなアプローチを採用する際の主な障害は、設計構想からハードウェア実装までのプロセスをいかに簡潔にできるかにあります。また、DSP 中心のデザイン フローに慣れた設計者にとっては、FPGA の性能を最大限に生かしながら、そこにベースバンド処理機能を迅速かつ効率的に開発できるようにサポートする IP コアと開発ツールが必要になります。

ザイリンクスの LTE Uplink Channel Decoder および LTE Downlink Channel

Encoder LogiCORE は、重要な Layer-1 ファンクションの多くを 1 つの IP コア ソリューションとして提供するもので、先に述べたような障害を克服できます。この IP コア ソリューションは、ザイリンクス CORE Generator™ ツールの GUI でカスタマイズ可能です。このデザイン フローにより、FPGA の設計経験が浅いエンジニアであっても広範なシステム デザインに従事できるため、開発とデザイン統合にかかるコストが大幅に削減されます。

## 来るべき世界へ

より高速な接続と低レイテンシの実現は、LTE および 4G を超えた将来のシステムでも、重要な要件として常に求められます。より新しいデータ中心のワイヤレス通信システムが発展するに伴い、DSP と FPGA 間の機能分割に従来の方法を採用してきた多くの企業は、分割したチップ間でデータを伝送させる場合のオーバーヘッドが許容範囲を超えた負荷になることに気付きます。FPGA ベースのソリューションは、製品設計を優位に進めたい設計者にとって、より手の届きやすいアプローチになっています。従来のシステム設計手法にとらわれない設計者は、競合他社が経験している性能の問題とボトルネックを克服した製品を市場に提供することが可能になるのです。 ●

## LogiCORE について

先頃ザイリンクスは、LTE Channel Encoder および Decoder LogiCORE 製品をリリースしました。本製品は、3GPP TS 36.211 v8.2.0 と TS 36.212 v8.2.0 (2008-03) 規格に準拠し、3GPP rel8 E-UTRA eNB ベースバンド処理用に設計されています。これらの製品は、ノーマル (ショート) CP、64-QAM 変調、2 MIMO コード ワードで、最大バンド幅が 20MHz までの異なるコンフィギュレーションをサポートします。エンコーダとデコーダはともに FDD と TDD フレーム構造に対応可能であることから、TD-SCDMA 規格から発展してきたシステムにも最適です。

これらはスタンドアロンで、パラメータ指定された IP コア

ブロックとして提供され、Coregen ソフトウェア ツールでお客様のデザインに容易に組み込むことができます。さらに、デザインへの統合を容易にするため、RTL シミュレーション環境、システム シミュレーション用の C モデル等をセットにして提供しています。

新しい LogiCORE 製品の詳細は、ザイリンクス ウェブ サイトの IP コア ページ ([japan.xilinx.com/ipcenter](http://japan.xilinx.com/ipcenter)) をご覧ください。ワイヤレス通信のページ ([japan.xilinx.com/esp/wireless](http://japan.xilinx.com/esp/wireless)) からは、リファレンス デザインやソリューションにアクセス可能です。

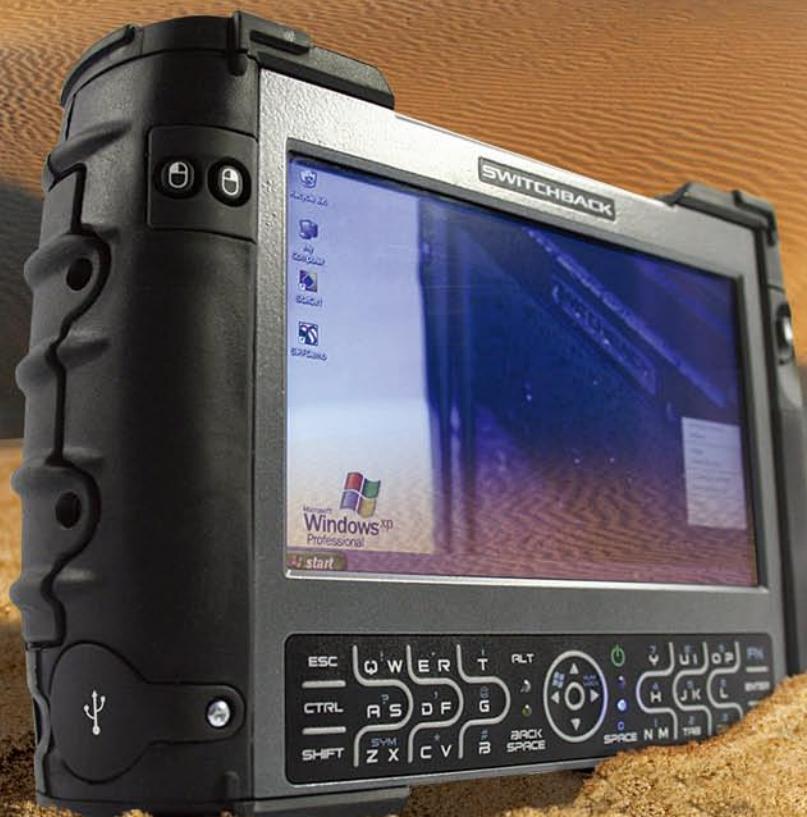

## Virtex-5 Powers Reconfigurable, Rugged PC

# Virtex-5 がリコンフィギャブルで堅牢な PC 開発を支援

RMT 社の SwitchBack はザイリンクス Virtex-5 FPGA を PC に採用し、フィールドでのカスタマイズや使用中のアップグレードに対応

Shane Lewis

Director of Technology Development

RMT, Inc.

[slewis@ropermobile.com](mailto:slewis@ropermobile.com)

米軍および鉱工業、運輸、倉庫、物流および公安などの重工業に携わる企業では、採用するパーソナル コンピュータに、極めて厳しい条件を設けています。PC は何よりもまず、物理的外圧、極暑、極寒、湿気への暴露、水没に対する十分な耐性を備えていなければなりません。同時に、コンピューティング関連の機能が市販されている最新の PC と同程度でも、セキュリティと世界規模の通信機能においては最新の PC 以上の性能を持つ必要があります。この種のコンピュータのユーザーは、極めて重要なタスクをターゲットにした特別なペリフェラル機能も要求しますが、近年まで、これらニーズを完全に満たしていない標準 PC の使用を強いられてきました。

このような不足点は、モジュラーでカスタマイズできるコンピューティング ソリューションを設計するという非常に大きな課題とともに、RMT 社の設計グループに提起されました。このソリューションは、顧客の厳密な要求事項を満たし、彼らの期待に応える「共通のプラットフォーム」でなければなりません。経験豊富な R&D チームは、「万能タイプ」のデバイスを構築する際に陥る問題点について知識を有していました。それは、動作はしても最適化され

ではないデバイスを構築してしまい、苦しい妥協案でその場をしのぐ結果になるということです。設計チームは、不利な条件を克服し、真に受容可能なコンピュータ プラットフォームの設計に着手しました。結果、このコンピュータ プラットフォームは、回路レベルをフィールドでリコンフィギュレーションしたり、カスタマイズでき、しかもエレガントで、堅牢かつユーザー フレンドリーなシステムになっています。

この取り組みの結果得られたのが SwitchBack です。これはあらゆる点で従来型 PC とは異なり、ザイリンクス Virtex®-5 FPGA の技術革新を生かし、PC のアーキテクチャを再定義します。従来型 PC と SwitchBack との間には非常に大きなアーキテクチャ上の相違があります。

### 従来のオープン PC アーキテクチャ

現状の従来型 PC のベースは、x86 プロセッサとそれに関連したチップ セットで、Linux や Windows (Windows XP や Vista) がオペレーティング システムとして使用されています。このコード セットに埋め込まれた過去の技術に対するサポートが、PC における支配を可能にし、オペレーティング システムとプロセッサ技術がさらに細分化されるエンベデッド コンピュータ空間に制約を与えています。Windows XP や Vista が動作可能なデスクトップ、ラップトップあるいはタブレット PC 本体のカバーを外してみると、チップ セットと CPU の回路の接続形態 (トポロジー) が

良く理解できます。

ほとんどの PC において長年事実上の標準である、この堅牢で商業性に富んだアーキテクチャには、基本的な制限があります。タスク実行には、ある特定のプロセッサ向けに記述されたプログラムを実行させる、あるいは利用可能な多くの拡張ポートに外部ハードウェアとして差し込む必要があります。何ができるかは、チップ セットそのものを構成する専用 ASIC の配線で厳密に定義されているのです。

### SwitchBack のアーキテクチャ

RMT チームは、この設計を再考する必要がありました。開発チームは、特許出願中の SwitchBack のアーキテクチャを起案し、このアーキテクチャがフィールドでリコンフィギュラブルであると同時に Windows ベースのアプリケーションと互換性がとれるよう設計しました。エンベデッド コンピューティングの分野では、フィールド リコンフィギュレーションの概念は今日広く利用されており、その傾向は FPGA によって作られたものです。

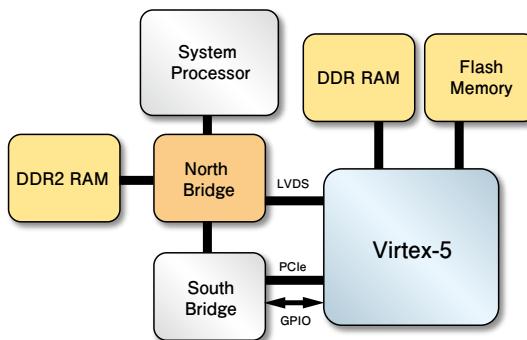

プログラマブル ロジックは、現在、x86 PC ベースのマザーボード上で各種のサポートの役割を担っていますが、SwitchBack では FPGA が主たるものであり、コンピュータ ファンクションの指揮をとっています (図 1)。Virtex-5 は、すべての主要サブシステムの第 1 のコントローラです。ユーザーが電源ボタンを押した瞬間から、FPGA はディスプレイを含むす

べてのペリフェラル、またデータの流れのほとんどを制御します。本スキームでは、Windows オペレーティング システムをブートせずに、データにアクセスしてデータを表示できます。これは従来の PC では事実上不可能であった功績と言えます。SwitchBack では、さらに機能を進化させ、プロセッサやオペレーティング システムなしでも、カスタム ファンクションやペリフェラルにアクセスし、制御できるようにしています。これらは BackPack、いわゆるモジュラー システムにプログラムされ、SwitchBack の後部側に取り付けられるもので、速度の遅いプロセッサやオペレーティング システムに合わせることなく、ペリフェラルを完全に制御できます。

### SwitchBack の核心部

SwitchBack の驚くべき高い柔軟性と制御機能は、ザイリンクス Virtex-5 LX30T に基づくアーキテクチャ上の設計により可能となりました。RMT チームは、豊富な内部リソースのみならず RocketIO™ と PCI Express® エンドポイント ブロックを備えていることから Virtex-5 を選択しました。そして、PCI Express インターフェイスをエンベデッド システムとインテル x86 システム間の主要な接続ポイントにしました。コンポーネント間にほかのインターフェイス ブリッジもありますが、PCI Express インターフェイスが、処理と制御のための主要なデータ パイプラインです。

図 1 - 従来型 PC アーキテクチャ (左) と革新的な SwitchBack (右) の相違 : SwitchBack では FPGA を最上位コントローラとして使用しています。これにより処理時間を改善し、さらに SwitchBack をリコンフィギュラブルでカスタマイズ可能にします。

図 2 - SwitchBack のアーキテクチャでは、最上位のシステム制御機能は Virtex-5 FPGA が有し、メイン x86 CPU プロセッサではありません。

## ハードウェアの設計

SwitchBack ハードウェア設計の基本的なレイアウトは、本質的に、独立した 2 つのシステムで構成されます。この場合、x86 CPU プロセッサではなく、Virtex-5 FPGA が最上位の制御システムとなります(図 2)。システムがブートアップすると、直ちに実際のコンフィギュレーションが実行され、続いて第 2 のシステムのブートが許可されます。

さらに、FPGA はコンフィギュレーションとプログラムのストレージ用に、RAM とフラッシュ メモリを内蔵しており、これらは初期設定とは別のオペレーションを FPGA に書き込む場合に使用されます。この革命的なアーキテクチャと FPGA 定義のアルゴリズムは、通常の PC がなしえない重要な機能を提供します。その機能には、メイン プロセッサや当該ベース チップ セットの許可の元でのシステム リソースの制御、また SwitchBack の BackPack にプログラムされたものを含むペリフェラルを独立かつ自主的に制御する 2 つの機能があります。さらに FPGA には、メイン プロセッサを支援する、プロセッサから独立したファンクションもあります。

図 3 - FPGA 内に形成されたすべてのリコンフィギュアブル ハードウェアはメイン プロセッサに接続でき、プロセッサは拡張ポートに挿入された実ハードウェアに対するのと同様に、これらへアクセス可能です。

システム リソースとペリフェラルの制御は複雑ではなく、エンベデッド業界ではよく理解されています。しかし、プロセッサから独立したファンクションの使用には、SwitchBack が持つ性能を生かす必要が生まれてきます。オプションには、リコンフィギュアブル ハードウェア、オープン アーキテクチャ向けのオープン FPGA、BackPack による追加のカスタマイゼーション、BackPack モジュラー開発キットなどがあります。

## リコンフィギュアブル ハードウェア

Virtex-5 の内部リソース アレイ (ExpressFabric アーキテクチャ、ブロック RAM、1.25G ビット / 秒 Select I/O および DSP48E スライス) では、通常メイン プロセッサのソフトウェアで実行されるファンクションやプロセスを、これら FPGA のリソースで生成し実行することで、数多くの可能性が提供されます。FPGA が備えるこれらの特長を活用し、多くの機能を FPGA にインプリメントすることでメイン プロセッサの負荷を軽減したり、標準 PC の物理的拡張カードのように機能する全く新しいサブシステムを生成す

ることができます。

2 つのシステム間に PCI Express バスを使用することで、FPGA 上に形成された新しいハードウェアを拡張ポートに差し込まれた物理的なハードウェアのように、メイン プロセッサに接続できます(図 3)。これにより、メイン x86 プロセッサとは独立して動作する新しいタイプのデバイスの構築が可能となります。デバイスあるいはファンクションには、データ フォーマット変換、カスタム ロジック インターフェイス、ハードウェア エミュレーション、独立したマイクロプロセッサ、通信用デバイス、数値演算用コアおよび自立した BackPack 制御などが含まれます。

実際、これらのファンクションは、ファンクションを実装した物理的な回路カードがないにもかかわらず、オペレーティングシステムでは個別のハードウェアに見えるため「仮想デバイス」と呼ばれています。複数のデバイスを同時に実装できるため、オンボードのチップ セットが認識する機能をはるかに超えたプラットフォームへと拡張することになります。

## オープン アーキテクチャのためのオープン FPGA

理念の一部として、PC のオープン アーキテクチャ プラットフォームを維持し、その柔軟性を拡大しながら FPGA をその中に含めるという考えがありました。Virtex-5 FPGA の集積度は、SwitchBack が主要制御機能に必要とするものよりも大きなものです。意図的に大きな FPGA を選ぶことで、顧客のプログラミングと機能性を SwitchBack に追加できるようにしました。これにより、複数の独立したサブシステムの並列動作で得られるものと同じ成果を実現できる、真にカスタマイズされた精度の高いツールの開発が可能となります。

我々は意図的に、SwitchBack のシステム マスターである Virtex-5 FPGA のリソースを使用しないようにしました。たとえば、Virtex-5 LX30T FPGA には 32 の DSP48E スライスがありますが、SwitchBack で使用しているのは 1 つのみで、残りの 31 はエンド ユーザー用と

なっています。ユーザーが必要とするリソースの量と購入時の SwitchBack のコンフィギュレーションによりますが、レジスタ、LUT、BRAM、DCM および PLL など残りのリソースはユーザーの特定用途向けに使用可能となっています。一般に、SwitchBack がシステム管理と汎用処理に使用しているのは FPGA の容量の半分以下で、残りのリソースの大半はユーザー ファンクションの定義用です。

カスタム アップデート インターフェイス ツールにより、SwitchBack 内のフラッシュ メモリを容易にアップデートできます。この簡単なソフトウェア アップデートには、FPGA のコンフィギュレーション ファイルを変更するための JTAG や特別な機器は必要ありません。新ハードウェアのインストールは迅速かつ容易で、SwitchBack システムをリブートした際に Hardware Manager 内に新しいハードウェアが表示されれば、直ちに使用できます。

また FPGA に対する SwitchBack の要件を、インプリメントが容易なコアに統合しました。したがって、エンド ユーザーは FPGA の未使用領域にロジック、レジスタやバスを簡単に追加できます。

さらにファームウェア開発キット (FDK) を使用することで、ミッションの変更に伴う特別なニーズ向けに SwitchBack を修正し、リコンフィギュレーションできます。FPGA に対してユニーク モジュールのアップグレード機能や、カスタム ロジック 変更機能（あるいはその両機能）を使用すれば、SwitchBack を現場の状況に素早く適合させることができます。このスキームにより、フィールドでシステム効率の高い再設計が可能となるのです。FDK にこの機能を追加することで、FPGA の豊富な経験を持ち、相応の配置・配線ツールを使用するユーザーは、そのニーズを十分に満たした SwitchBack を開発できます。

## BackPack によるさらなるカスタマイゼーション

SwitchBack をさらにカスタマイズするには、BackPack 技術を利用します。BackPack はユーザー固有のモジュール

で、SwitchBack の後部にしっかりと取り付けることができます。SwitchBack は、RMT チームが当初は、外部ペリフェラルの必要性を排除し、複数のポートを追加する目的で開発されました。BackPack では、そのサイズ、形状、複雑性において無限の配列が可能で、付加的な処理機能を取り扱うことができます。たとえば、このパーソナル コンピュータにスーパーコンピュータ並の計算能力を与えることが可能となります。このように、BackPack はフィールドでカスタマイズ可能なシステムで、SwitchBack を高度に統合化された精密なツールへと変身させます。

RMT チームは、FPGA の GPIO を BackPack ポートに直接接続しました。したがって、FPGA 内のロジックは BackPack に直接アクセス可能となり、メイン システム プロセッサを介在せず、すべてのタイプのデバイスを制御できるようになっています。リプログラマブル FPGA と外部接続性への無限の潜在能力を組み合わせることにより、SwitchBack の仕様は完全に達成されます。

## モジュラー開発キット

BackPack の成功を踏まえると、適切なツール キットを提供すれば、FPGA の知識が豊富な設計者は各自の BackPack を開発しプログラムできることがわかりました。SwitchBack のモジュラー開発キット (MDK) を使用することで、SwitchBack 独自のアーキテクチャを利用するカスタム BackPack が設計可能です。多くの場合、顧客は電子デバイスや回路カードを持っており、それらを短時間にテストしたり展開したりするために、システム上に統合したいと思っています。こういった企業は MDK を使用すれば簡単に行えます。MDK では実動作する回路基板、ケーブル、回路図と配線 CAD データを提供しているので、BackPack を数日で完成させることができます。

また、SwitchBack のオンボード FPGA と BackPack 技術を使用すれば、特別な機能のサブシステムを構築してコ

ンピュータに素早く結合できます。BackPack はコンピュータの一部ですが、完全に自立して動作し、また処理データのみを共有することで、従来の方法 (USB など) でデバイスを追加した場合に生じるメイン プロセッサへの過負荷状態を回避できます。したがって、メイン プロセッサに一切負担をかけずに、同等あるいはそれ以上の処理機能を持つ BackPack をインプリメントできます。

ザイリンクス Virtex-5 は DSP48E スライスを内蔵しているため、これらを使用すれば機能強化に加え、効率を改善した上で追加の信号処理を行うことができ、画像処理、ソフトウェア ラジオ、暗号作成、ネットワーク セキュリティおよびアナログ モデムなどが、その応用例として挙げられます。

また、特定のファンクション内のアナログ部を BackPack に構築し、演算処理を SwitchBack に任せることで、そのファンクションの性能を向上させることができます。

設計グループは Virtex-5 を革新的に駆使し、SwitchBack を完成させました。したがって、完全に最適化されていないコンピュータに接続された種々のペリフェラルの取り合せに妥協する必要はありません。SwitchBack を使用すれば、ミッション クリティカルなアプリケーション用の素早いシステム設計や展開が短期間に達成できます。

SwitchBack は、コンピュータ技術進化の次のステップを具現化するものです。リコンフィギャブルな PC プラットフォームにより、フィールドでカスタマイズできるだけでなく、動作中のアップグレードをサポートします。これは、極めて重要なアプリケーションを中断させることなく実行できるため、米軍、鉱工業、運輸、倉庫、物流そして公安などの重要な市場での運用に特に適しています。

SwitchBack の詳細とその革新的なアーキテクチャについては、[www.ropermobile.com/products/switchback](http://www.ropermobile.com/products/switchback) をご覧いただかず、RMT, Inc. の著者に E メール ([slewis@ropermobile.com](mailto:slewis@ropermobile.com)) または電話 (480) 705-4200, ext. 306) でご連絡ください。

## Virtex-5 Propels Ultrawideband Comms and Ranging

# Virtex-5 は超広帯域 (UWB) 通信と正確な測距を実現

欧州の PULSERS プロジェクトでは、インパルス無線 UWB システムにザイリンクスの MicroBlaze プロセッサ搭載 FPGA を採用

Guy Eschermann

Research Engineer

Sennheiser electronic GmbH & Co. KG

*Guy.Eschemann@gmail.com*

Heinz Lüdiger

Project Manager

IMST GmbH

*luediger@imst.de*

Birgit Kull

Senior Scientist

IMST GmbH

*kull@imst.de*

2002 年に連邦通信委員会が、ライセンスなしで超広帯域 (UWB) 無線技術の使用を認可して以来、この技術を利用したワイヤレス USB などの商業アプリケーションの多くで、高いデータ レート送信は周波数領域変調技術 (OFDM など) をベースとしてきました。この確立された方法と並行する形で、UWB は、パルス幅が約ナノ秒である超短パルスに基づく別のデータ送信の可能性を提示します。いわゆるインパルス無線 (IR) システムでは、位置や振幅

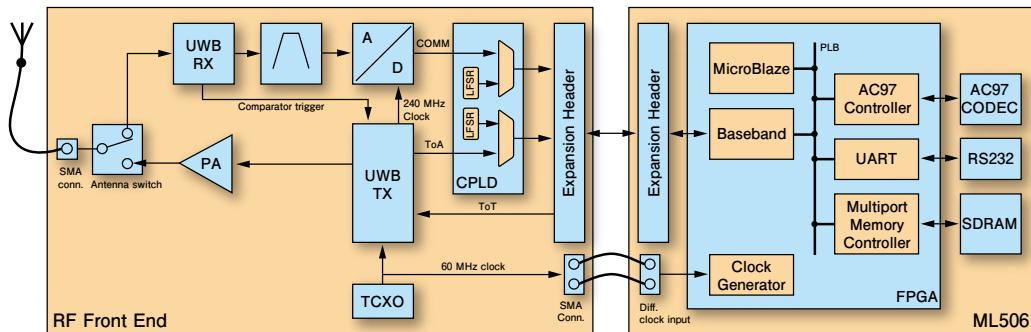

図 1 - システムは、カスタムの UWB ドーター ボードに接続された標準のザイリンクス ML506 ボードで構成されています。

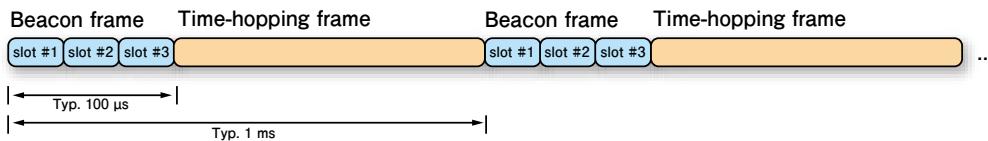

図 2 - 3 つのビーコン スロットで構成される周期的ビーコン フレームは、時間ホッピング フレームと交互に配置されています。

表 1 - UWB 通信と測距システムの特性

|                         |                                         |

|-------------------------|-----------------------------------------|

| Center frequency        | 7.68 GHz                                |

| Baseband bandwidth      | 750 MHz                                 |

| Expected range          | 25 - 30 meters                          |

| Actual range            | 3 m (due to local-oscillator crosstalk) |

| Ranging resolution      | 3.9 cm                                  |

| Communication data rate | > 1 Mbit/s                              |

などパルスのパラメータのうち 1 つ、または複数を変調することで情報を送信します。同時にパルスの伝送時間を計測することにより、センチメータ (cm) 単位で正確な測距（距離測定）機能をインプリメントできます [1]。これにより UWB は、物流（パッケージの追跡）、製造、捜索救助（消防士との連絡と位置確認）あるいはハイテクを用いたツアー ガイドのような種々の分野で、位置認識アプリケーションの新しい領域を開拓しています。

欧州の PULSERS Phase II Project は、UWB 無線技術のための産業主導の共同体 (30 の主要な企業と学術組織で構成)

であり、IR-UWB の通信と測距システム [2] の設計とインプリメンテーションに着手しました。このシステムのデータ送信機能は約メガバイト / 秒単位で、測距精度は 4cm です。我々が開発しているシステムは、等価な一組の個別ノードで構成され、各ノードはネットワーク上の他ノードと通信してノード間の距離を測定できます。各ノードは、標準のザイリンクス ML506 開発ボードにカスタムの UWB ドーター ボードが接続されている構成です（図 1 参照）。また、高性能 Virtex®-5 SXT アーキテクチャと柔軟性の高い MicroBlaze™ ソフト プロセッサを組み合わせることにより、ベースバンド信号チェーン全体とシステム内のすべての高層レイヤを 1 個の FPGA にインプリメントできました。

## IR-UWB 通信と測距

このシステムでは、情報を送信するためには、実行可能な 4 つのパルス位置 (4PPM) による簡単なパルス位置変調を採用しています。また、ここでは各パルスが 2 ビットをエンコードします。図 2 に示すように、パルスはそれぞれのフレームにグループ化

され、ビーコン フレームと時間ホッピング フレームのあらかじめ定義されたラスターで送信されます。各ビーコン フレームは 3 つの等価なビーコン スロットで構成されているため、ユーザーは測距や通信の目的で使用できます。当初、時間ホッピング コードに基づいた、時間ホッピング フレームを使用した高速データ送信を考えましたが、この技術の採用を今後の製品で検討しています。現段階では、すべてのデータ送信は、ビーコン フレームで行われます。

距離の測定については、双方向測距として知られる方法で行いました。この方法では、測距リクエストの送信と遠隔ノードからのアンサー受

信との間で発生する遅延時間を計測します（補足記事を参照）。測距リクエストは常にビーコン スロット 1 で送信されますが、測距アンサーはスロット 3 で戻ってくることを想定しています。したがって、遠隔ノードには、受信した測距リクエストの処理用に、また測距アンサーを送信するスケジューリング用に、ビーコン スロット 1 個（スロット 2、約 33 マイクロ秒）分の時間が与えられます。

## システム アーキテクチャ

UWB ドーター ボードは、インパルストランスマッタ用 ASIC とインコヒーレント レシーバ用 ASIC の両方を搭載しています。これらの ASIC は、IHP 社の 0.25 ミクロン SiGe: C BiCMOS 技術を駆使し、本プロジェクト用に特別に設計されたものです [3, 4]。

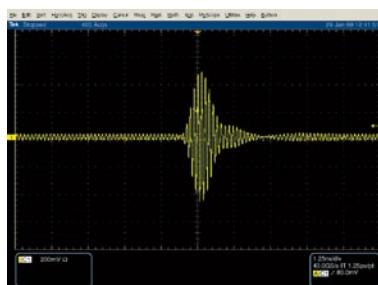

図 3 に示すように UWB パルスを生成するトランスマッタ ASIC は、生成されたパルスの振幅および位置の両方の変調が可能です。トランスマッタ ASIC には 3.84GHz のカウンタが内蔵されており、送信パルスの送信時間を正確にスケジュー

リングし、受信パルスの到着時間を測定するために使用されます。

レシーバ ASIC の内部では、受信経路が 2 つに分かれています。比較的バンド幅が狭い (120MHz) 第 1 の経路は、通信目的とおおよそのパルスタイミング目的に使用されます。インパルス バンド幅全体 (750MHz) を利用している第 2 の経路では、正確なタイミングでパルスを発生します。ここは、高速コンパレータが到来パルスを検出し、このコンパレータの出力で、トランスマッタ ASIC 内部で動作している 3.84GHz カウンタの読み出しがトリガれます。したがって、各受信パルスの到着時間は、260ps の分解能で測定されます。これを空間分解能に置き換えると約 8 cm に相当します。

ドーター ボードでは Virtex-5 FPGA 内のベースバンド モジュールに 120MHz で動作する 2 本のデータ バスが接続されています。通信 (COMM) バスは ADC のサンプルを伝達し、一方で到着時間バスは受信パルスに関連した高分解能のタイム スタンプを伝えます。両バスは XC95144XV CPLD に組み込まれていますが（厳密には必要ありません）、デバッグ用途には役立ちました。バス上の一連の疑似乱数を FPGA に出力するよう、CPLD を設定できます。次に、この CPLD の出力を利用して FPGA の入力タイミングを調整し、さらにバス ラインのインテグリティを検証します。この 2 つのタスクは、送信されたデータ シーケンスの演繹的知識がなければ実行が難しいものでした。

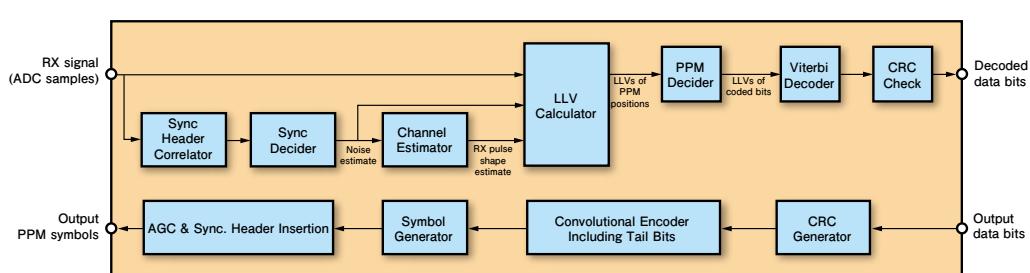

#### FPGA 内部のベースバンド モジュー

図 3 - UWB パルスは、ガウス分布包絡線を有する 7.68GHz の搬送波で構成されています。

ル（図 4 参照）は、送信されるパルスのエンコードと受信したパルスのデコードの両処理を引き受けます。ベースバンド モジュールの送信部分は比較的簡単な構成で、多くが外部 (CRC) コーディングおよび内部（畳み込み）コーディングで構成されています。受信部分のインプリメンテーションには、特に、チャネル推定器とカスタムのビタビ デコーダが含まれていますので、非常に多くのリソースを消費します。ベースバンド モジュールとプロセッサは、Processor Local Bus (PLB) インターフェイスによって接続されています。

ソフトウェアのデバッグと比較して、プログラマブル ロジックのデバッグは非常に難しいのですが、ChipScope™ Pro ツールを統合ロジック アナライザやバス アナライザ コンフィギュレーションと併せて使用したため、デバッグ作業に役立ちました。ロジック アナライザは、COMM のバーストおよび到着時間のサンプルを同時にキャプチャし、実環境データを MATLAB® シミュレータに供給するため有用です。またベースバンド モジュールの PLB インターフェイスに関連する問題のデバッグには、バス アナライザが役立ちました。

## プロセッサ システム

プロセッサ システムは、Xilinx Platform Studio (XPS) デザイン ツールに含まれるベース システム ビルダーウイザードを使用して生成されたものですが、最初から完全に動作するシステムとなっ

ていました。その後、ベース システムに少しづつ変更を加え、最終的には図 1 の FPGA セクションに示されたシステムを得るに至りました。特に、差動クロック入力へのスイッチングおよびベースバンド モジュールの PLB への接続が、これら変更の例として挙げられます。

ソフトウェア アプリケーションは、Xilkernel のトップに位置するエンベデッド MicroBlaze プロセッサで実行されます。この Xilkernel は、小さなアプリケーションに完全に適合した最小のリアルタイム オペレーティング システムです。本ソフトウェア アプリケーションは、同時に実行される次の 3 つのスレッドに分割されます。

- UWB スレッドは、ベースバンド モジュールのコンフィギュレーションおよび動作を管理します。

- アプリケーション スレッドは、システムがデータ送信モードで使用された場合に、オーディオ データの収集およびブレイバック動作を担います。

- RS232 スレッドは、グラフィカル ユーザ インターフェイス (GUI) 機能を実行する外部 PC と通信します。

XPS が使用する GNU 開発チェーンはほかの複数プラットフォームで利用できます。したがって、エンベデッド ターゲット上ではなく、ホスト PC 上（たとえば、Cygwin 環境を使用して）でハードウェアとは独立したコード モジュールを容易にコンパイルし、テストも可能でした。このため、デバッグがずっと容易になりました。最終テストのみエンベデッド ターゲッ

図 4 - ベースバンド モジュールの受信チェーン（上）と送信チェーン。

ト上で行う必要がありましたが、GDB のようなソース レベルのデバッガを利用できることは、本当に幸いでした。さらにザイリンクスのアプリケーション ノート XAPP1037 [6] を参照し、ソフトウェアをデバッグする上で有用な多くの手段入手することができました。

UWB ASIC に関するハードウェア上の問題が発生したため、このシステムの公称測定距離は、最初に設定していた 25 ~ 30m から現在は 3m に制限されています。とはいえ、本システムの通信および測距の機能を実証できたことは、このプロジェクトは大いなる成功といえます。

将来的には、UWB ASIC を再設計してシステムの動作範囲を広げること、さら

に多角的機能をインプリメントすることによって単なる測距システムから実際の室内位置決めシステムへ昇格させることを目標としています。

詳細は、[http://www.imst.de/de/forschung\\_pul.php](http://www.imst.de/de/forschung_pul.php) をご覧いただけ、luediger@imst.de に E メールにてご連絡ください。

#### 謝辞

EADS の Erwin Stenzel 氏と Daniel Kotzor 氏、IHP の Gunter Fischer 氏、IMST の Thorsten Kohl 氏、Jac Romme 氏、Norbert Schmidt 氏、Hannover にある Leibniz University の Maria Dolores Pérez-Guirao 氏、Sennheiser の Axel Schmid 氏、および RadioLabs の Dajana Cassioli 氏に対して、こ

のプロジェクトに貢献していただいたことに謝意を申し上げます。また、この記事のドラフトをレビューしていただいた Sennheiser の Steven Backer 氏に感謝いたします。

この研究は、Information Society Technologies 社の統合プロジェクト PULSERS Phase II の下、欧州委員会により共同設立されたものです。

#### 参考資料

- [1] S. Gezici, Z. Tian, G. B. Giannakis, H. Kobayashi, A. F. Molisch, H. V. Poor and Z. Sahinoglu, "Localization via Ultra-Wideband Radios," IEEE Signal Processing Magazine, July 2005.

- [2] H. Lüdiger, B. Kull, M. D. Perez-Guirao, "An Ultra-Wideband Approach towards Autonomous Radio Control and Positioning Systems in Manufacturing & Logistics Processes," Proceedings of the 4th Workshop on Positioning, Navigation and Communication, Hannover, Germany, March 2007.

- [3] G. Fischer, O. Klymenko, D. Martynenko, "Time-of-Arrival Measurement Extension to a Non-Coherent Impulse Radio UWB Transceiver," Proceedings of the 5th Workshop on Positioning, Navigation and Communication, Hannover, Germany, March 2008.

- [4] O. Klymenko, G. Fischer, D. Martynenko, "A High Band Non-Coherent Impulse Radio UWB Receiver," Proceedings of the IEEE International Conference on Ultra-Wideband, ICUWB 2008, Hannover, Germany, September 2008.

- [5] P. Alfke, "Efficient Shift Registers, LFSR Counters, and Long Pseudo-Random Sequence Generators," XAPP052 application note.

- [6] B. Hill, "Introduction to Software Debugging on Xilinx MicroBlaze Embedded Platforms," XAPP1037.

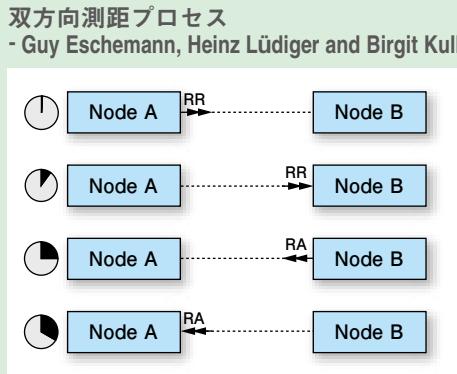

#### 双方向測距の補足説明

インパルス無線 UWB システムに採用した技術、すなわち双方向測距では、ノード A とノード B 間の距離を次の技術を使用して決定します（図を参照）。

1. ノード A がノード B に測距リクエストを送り、高分解能クロックを起動します（3.84GHz）。

2. ノード B は、信号の伝播遅延時間  $t_{\text{prop}}$  の経過後、測距リクエストを受信します。 $t_{\text{prop}}$  はノード A、B 間の距離に比例します。

3. ノード B は、決められた処理遅延時間  $t_{\text{proc}}$  の経過後、測距アンサーをノード A に送り返します。

4. 測距アンサーを受信すると、ノード A は時間  $t_{\text{rtt}}$  でクロックを停止させます。その後、単方向信号伝播遅延の  $t_{\text{prop}} = (t_{\text{rtt}} - t_{\text{proc}})/2$  を使用した計算が可能となり、これに光の速度（約 30 万キロ / 秒）を乗算すると、A – B 間の距離が得られます。

3.84GHz クロックの時間分解能は 260 ピコ秒であるため、約 8cm が空間分解能となります。ただし、無線信号は 2 つのノード間を往復するため、距離は 4cm の分解能で決定できます。

移動するノードおよび同一直線上にない 3 つの固定ノード間の距離がわかると、移動するノードは、2 次元（平面）での自身の位置を計算できます。同一平面上にない 4 つの固定ノードを使用すれば、3 次元（立体）での自身の位置さえ見つけることが可能です。

# 無線 画像 リアルタイム処理に最適!!

## \* 無線&画像処理用大規模FPGA搭載ボード

ユーザアルゴリズムをインプリメントするための大規模FPGAとデータIF用FPGAを搭載したボード

ADM-XRC-5T2

| 分類                                   | 仕様                                                                                                            |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------|

| FPGA                                 | Virtex-5<br>LX220T, LX330T, SX240T, FX100T, FX200Tより選択                                                        |

| Memory                               | SDRAM<br>DDR II SDRAM 512MB ~1GB                                                                              |

|                                      | SSRAM<br>DDR II SDRAM 8MB                                                                                     |

|                                      | FLASH<br>4MB                                                                                                  |

| データ入出力<br>FPGA開発<br>サポートOS<br>ボードタイプ | 各種I/Oモジュールを搭載可能<br>Matlab / Simulink対応<br>Windows, Linux, VxWorks<br>PMC/XMC, PCI, PCIe x8, CompactPCIへの変換も可能 |

## \* FPGAボード搭載用各種I/Oモジュール

FPGAボードのフロント部に直接搭載可能な、無線信号や画像処理用のI/Oモジュールを各種用意

A/DやD/Aのほか、各種入出力IFを用意しているので、アナログからデジタルまでデータ取り込み可能

1.5GHz 8bit 2ch A/D

80MHz A/D & 160MHz D/A

Optical 4ch

Camera Link 2ch

| FPGAボード搭載用 XRM I/Oモジュール |                                         |                             |                                    |                      |                            |                                               |

|-------------------------|-----------------------------------------|-----------------------------|------------------------------------|----------------------|----------------------------|-----------------------------------------------|

| 分類                      | 仕 様                                     |                             |                                    |                      |                            |                                               |

| A/D & D/A               | 3GHz 8bit 1ch A/D                       | 1.5GHz 8bit 2ch A/D         | 500MHz 12bit 2ch A/D               | 250MHz 14bit 2ch A/D | 125MHz 14bit 2ch A/D       | 80MHz 14bit 1ch A/D &<br>160MHz 16bit 2ch D/A |

|                         | -                                       | 1GHz 16bit 2ch D/A          | -                                  | 275MHz 14bit 2ch D/A | -                          |                                               |

| その他                     | HD-SDI IN & OUT x2ch                    | S-Video & SVGA              | HSSDC2 4ch                         | Rapid I/O 2ch        | FPDP                       | MDR 26 I/O                                    |

|                         | Cameralink 1ch or<br>MiniCameralink 2ch | LVDS 146 I/O<br>LVDS 36 I/O | 10/100 Ethernet &<br>RS-232 & LVDS | Optical 1ch/2ch/4ch  | 128/256/512MB<br>DDR SDRAM | 2/4/8/16MB<br>ZBT SDRAM                       |

## \* FPGAボード搭載用キャリアボード

FPGAボードをPC環境下で利用する為のキャリアボード

2枚のFPGAボードを同時に搭載可能

PCI Express x8

PCI 66/64

(お問い合わせは)

sales@mish.co.jp

<http://www.mish.co.jp/>

MISH

INTERNATIONAL

株式会社ミッシュインターナショナル

TEL 042-538-7650 FAX 042-534-1610

〒190-0004 東京都立川市柏町4-56-1

# FPGA-Powered Platform Controls Industrial Motors for Maximum Efficiency

## FPGA 搭載のプラットフォームで 産業用モーターを最大効率で制御

National Instruments 社が、最適なモーター制御が必要な産業装置メーカーの CompactRIO 設計にザイリンクス FPGA を採用

Greg Crouch

Embedded Systems Business Director

National Instruments

[greg.crouch@ni.com](mailto:greg.crouch@ni.com)

規制強化で工場の運営経費削減が求められる中、機械メーカーは製品の電力効率を向上させるための解決策を模索しています。冷暖房空調設備と並んで、工場内で電力を多く消費するものとしては、温水暖房器、照明、オフィス機器、特に機械類が挙げられます。さらに具体的に言うと、工場内の機械で使用されるモーターの消費電力は、一般的な産業施設での全電気エネルギー消費の約 3 分の 2 を占めています。モーターは送風機、ポンプ、コンプレッサ、コンベヤ、工作機械、ミキサ、シュレッダなどあらゆる機器で使用されています。

機械類を制御するモーターから最大の効率を引き出す方法の 1 つは、効率の最適化を目指したより高度なベクトル制御 (Field-Oriented Control) を採用することです（補足記事「モーター効率がより良い結果を招く」を参照）。この効率の最適化に向けて、National Instruments (NI) 社の開発チームは、演算性能と柔軟性に優れたエンベデッド コントローラを設計するた

めに、リコンフィギュラブル I/O (RIO) と呼ばれる一般的なハードウェア アーキテクチャのベースにザイリンクスの FPGA を採用しました。NI のカスタマでもある機械メーカーは、モーター効率を改善するベクトル制御 (FOC) 技術を利用するためのプラットフォームとして RIO を使用しています。

現在 RIO アーキテクチャは EUROelectronics, Srl 社のシステムを含め、多数のシステムで展開されています。このアーキテクチャを利用することで、EUROelectronics 社はプロトタイプから最終的な機械の完成までをわずか 3 か月で成し遂げました（図 1）。

### 機械設計時間の短縮

米国エネルギー省のデータによると、モーターを 4 ~ 6% 効率の高いものに切り替えた機械メーカーは、それを年間 4,000 時間以上稼働させるとして、投資経費をちょうど 2 年間で取り戻しています。残念ながら、多くの機械で使用されるホストモーターは非常に大きく、置き換えるには高いコストがかかります。このような

場合、最新の駆動制御アルゴリズムとコントローラ ハードウェアの採用が経費削減につながります。

2 番目の課題は、ブラシレス DC モーターと永久磁石同期 AC モーター (PMSM) の統合制御は複雑であるという

ことです。この両モーターは一般的にブラシレス DC モーター (BLDC) に分類されます。多くの機械メーカーには、多様なアナログ センサとデジタル センサに対してリアルタイムの閉ループ制御ができる、エンベデッド コントローラの構築に必要なソ

図 1 - エンベデッド機械メーカー EUROelectronics 社は、FPGA ベースのベクトル制御により電力使用を削減

図 2 - NI 社のシングルボード RIO と CompactRIO コンフィギュレーションのためのモジュラー RIO アーキテクチャ ベース フレームワーク

ソフトウェアやハードウェア設計の専門知識がありません。

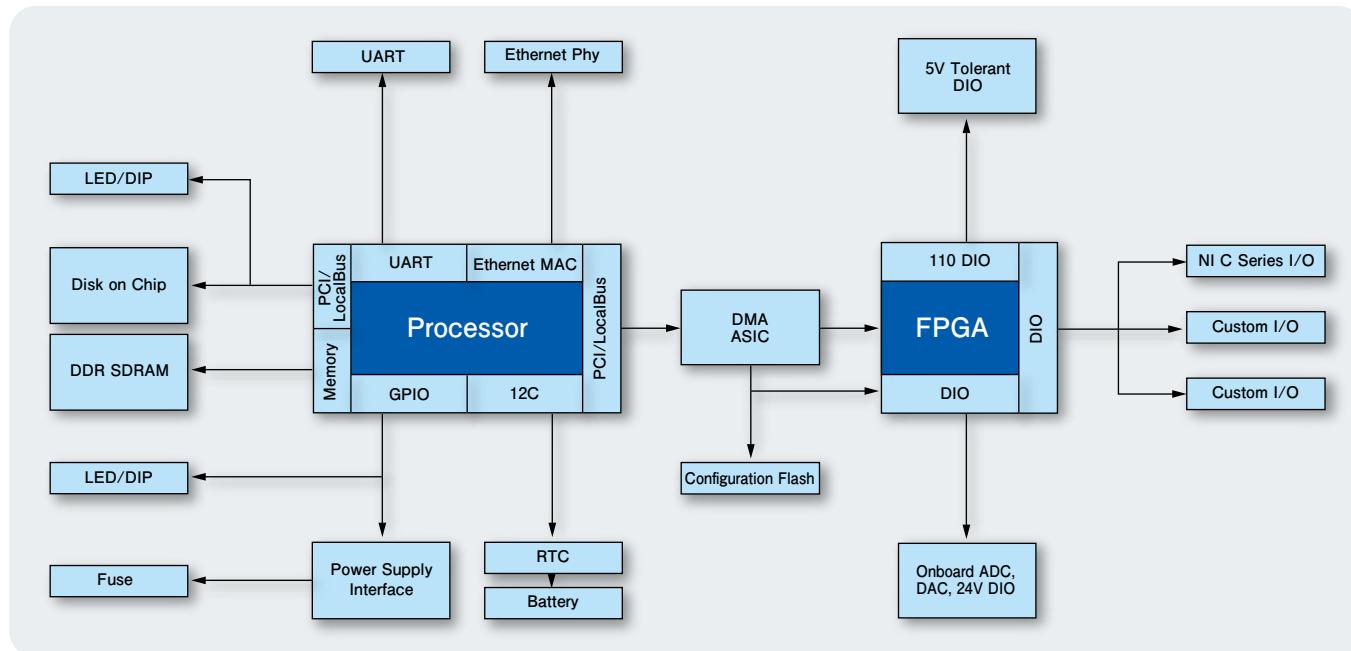

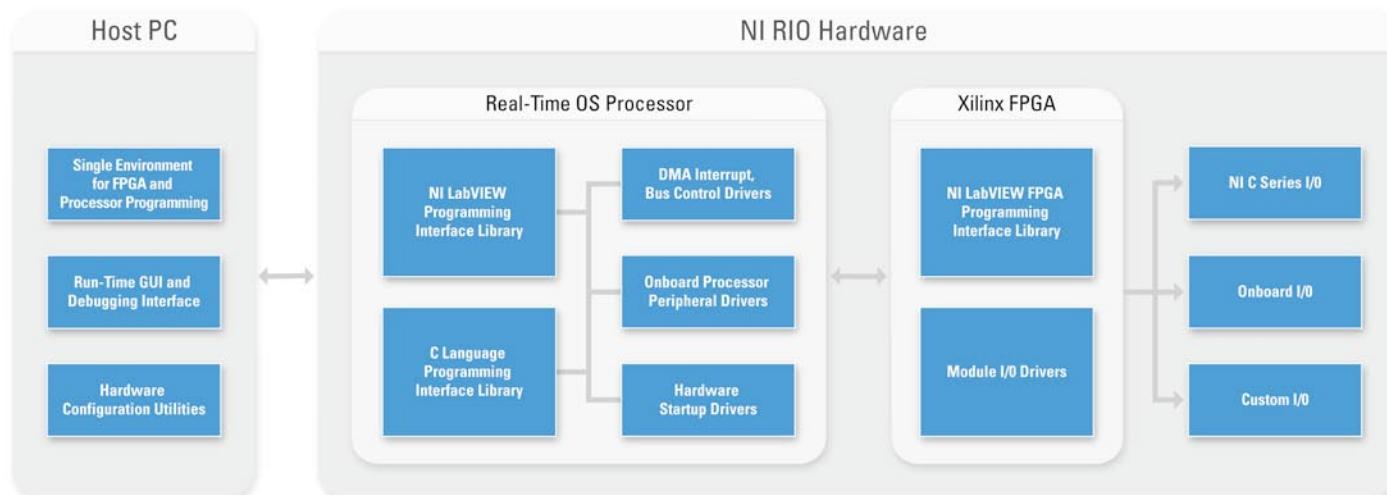

エンベデッド機械メーカーが設計に要する時間を短縮できるよう、RIO ベースのアーキテクチャの 1 つを採用して CompactRIO という製品を開発しました。これらの FPGA ベースの構造には、ザイリンクス Virtex® -5 LX85 や Spartan® -3 で構築されたシステムと Virtex-II 1M ゲート ベースのバックプレーンが含まれ、複数の周波数をサポートする PowerPC® 603e ベースのプロセッサが組み込まれています（図 2）。

RIO フレームワークには、コンフィギュレーション ソフトウェア ユーティリティとダイナミック I/O リコンフィギュレーション機能が構築されているため、最終的なアプリケーション プログラマやデジタル デザイン エンジニアは、セットアップや再利用に費やす時間を短縮できます。また、コンフィギュレーション ソフトウェアは、システムにインストールされたカスタム ハードウェアを自動検出でき、I/O ペリフェラルに付属の診断テストによって、I/O デバイスが正常に動作しているかを確認できます。設計者はカスタム回路をザイリンクス FPGA に直接接続し、ザイリンクス ツールや NI LabVIEW FPGA Module を使用して、ロジックを設計できます。

機械メーカーは、ダイナミック コンフィギュレーションを利用してことで、ハードウェアの再利用が可能になります。同時に、最終版の新規 I/O 設計が完成する前に、ハイレベル アプリケーションのコーディングに着手できます。

ドライバ ソフトウェアと関連する API が正しく実行されなかったり、I/O 回路がインストールされずにデバイス固有のエラーが返されるなどの問題を避けるため、ソフトウェア開発者は通常、アプリケーション内の I/O 回路コードを一時的に置き換えるシミュレーション用サブルーチンを作成します。しかし、この方法ではアプリケーションの開発が難しくなり、実質的にコードのデバッグが不可能となります。NI の RIO ミドルウェア ドライバ アーキテクチャには、シミュレーション コードをドライバに直接統合する機能が含まれているため、コードの再利用とデバッグが簡単に実行できます。

図 3 はエンベデッド ミドルウェアのソフトウェア設計の階層構造例を示します。ミドルウェア ドライバとシステム サービスの有効性は、機械メーカーの多方面に展開される数千にもおよぶアプリケーションで実証されています。パラレルおよびマルチスレッド セーフ エンベデッド ミドルウェア ドライバは、RIO に欠くことでの

きないエレメントです。これにより、マルチスレッド セーフ 関数とリエントラント（再入可能）関数をマルチスレッドから同時に呼び出しても、動作は中断することなく正常に実行されます。また、パラレルでコードを記述したり、性能を最適化するための重要な機能です。リエントラント機能がないドライバはパフォーマンスを低下させ、最悪の場合、クラッシュを引き起します。コードは、ほかのスレッドが各関数の使用を終了するまで、スレッドへのアクセスできません。このようなコード内での不必要的依存関係を取り除くという点でも、リエントラント機能は非常に重要です。

## FPGA 制御アルゴリズムによる支援

ブラシレス DC モーターと永久磁石同期 AC モーターは、ともにブラシレス DC モーターと考えられていますが、ステータ（固定子）の巻線方法が異なります。回転すると、BLDC のステータの巻線は台形状の逆起電力電圧を発生するように巻かれていますが、PMSM の電圧は正弦波の形状です。

ブラシレス DC モーターは AC インダクション（誘導）モーターよりも高価なものですですが、高度なアルゴリズムで制御すれば、

図 3-プロセッサ ミドルウェア ドライバを使用すると、機械メーカーはカスタムの回路設計に注力できます。これらのドライバは、標準ヘッダ コネクタを介して、ザイリンクスの FPGA にリンクできます。

優れたエネルギー効率と性能を発揮します。さらに、スケーリングにより、高出力かつ高速のアプリケーションへの対応も可能です。AC インダクション モーターが今のところ市場を独占していますが、ARC Advisory Group の調査によると、過去 5 年間でブラシレス DC モーターの販売台数

は 4 倍に増え、売上高は 12 億米ドルを超えていました。

BLDC モーターは同期モーターの 1 種です。つまり、ステータが作り出す磁場とローター（回転子）の外の磁場が同じ周波数で回転することを意味します。通常 BLDC は 3 相モーターで、このステータ

は積層鋼板で成り、巻線は内周に沿って軸方向にカットされたスロット（細長い穴）に配置されます。ほとんどの BLDC モーターでは 3 本のステータ巻線が星状に結合されています。この内部構造は巻線というよりも、ローター上に永久磁石のペアが配置されるインダクション モーターの構造

## モーター効率がより良い結果を招く

Wil Florentino

Product Marketing Manager, ISM Vertical Market, Xilinx

今日、工場内にあるモーターで駆動される装置の電気エネルギー消費量は、全体の 3 分の 2 を占めていると考えられています。この事実は、装置メーカーに対して、よりエネルギー効率の高いシステム開発を目指すよう課題を投げかけています。この課題には、高効率なモーターを選択する、設計負荷に見合った適切なサイズのモーターを使用する、高性能で高速なフィードバックと制御によってモーターの性能を改善するなど、さまざまな方法で取り組むことができます。

### 効率評価をチェック

既存のモーターをさらにエネルギー効率の良いモデルに置き換えるだけでも、初期コストのわずかな増分以上の効果をもたらします。年間 8,000 時間稼働する 500 馬力のモーターを、効率評価が 5% 高いモデルに切り替えた場合、年間の電気料金で \$12,000、170 キロワット時に相当する分が節約できます。あるユーティリティ企業と公的機関は、先行投資コストを相殺するよう、ユーザーに助成金を提供して NEMA Premium Motor（超高効率 NEMA モーター）にアップグレードすることを奨励しています。NEMA Premium Motor は、電子製造業の全米業界団体によって認定されています。

### サイズと負荷が問題

一般的に、モーター効率はモーターにかかる負荷の量によって変化します。全負荷でのモーター効率は 85 ~ 97% となり、負荷を 70 ~ 80% にすると効率は最大になります。モーターサイズをわずかに大きく（最大 25%）するだけで、実際に効率を向上できます。同様に、モーターの全負荷時の回転数をわずか 40RPM でも増やすと、モーターにかかる負荷が 3 ~ 6% 増加する結果となり、エネルギー消費が 7% 増加するために NEMA Premium Motor で期待されるエネルギーおよび費用の節約は相殺されてしまいます。

### FOC でさらにエネルギーを節約

モーターへの負荷は一定ではありません。したがって、モー

ターからのフィードバックは、少しずつ変化する負荷を追跡するのに役立ちます。3 相電気モーター可変速度動作に対する従来のスカラー制御技術は、インプリメンテーションは簡単ですが性能が制限されます。ベクトル制御とも呼ばれる FOC (Field-Oriented Control) は、フィードバックが高速で、すべての PWM サイクルで電流を制御することでトルクを厳密に制御できるため、より適した方法と言えます。FOC はこのように、電流が本質的に制限されることを前提として機能します。別の利点としては、トルクや回転速度を犠牲にせずに小さなモーターを使用できること、高速回転でもより好ましい動的応答が得られることが挙げられます。

小さなモーターを使用できるかどうかは別にしても、FOC はモーターのエネルギー消費を低減し、かつ効率を向上できます。たとえば、AC インダクション モーター内に FOC をインプリメントした場合、非ベクトル制御アプローチに対して、最大 25% までモーター効率を改善できます。米国エネルギー省は、FOC などのエネルギー節約技術をインプリメントすることで、動作マージンを 1 ~ 5% 下げることができます。この数値は、一般的なプラントの動作マージンが 16% であることを考えると、非常に大きな値と言えます。

### 科学と芸術

デザインに最も効率的なモーターと駆動システムを組み込むには、明確な科学と多少の芸術が必要です。選択肢としては、予期される負荷に適したサイズのモーターを選択することから、FOC のような複雑なモーター制御アルゴリズムを使用して性能の限界を押し上げることなどが考えられます。

モーター制御システムの効率を上げる利点は、製造コストの削減から始まります。流体を移動させているか、ドリルを使用しているか、あるいはロボット アームを制御しているかなどに関わらず、モーターの選択と制御技術は最終的な収益に影響を与えます。またエネルギー消費の削減が環境にもたらす影響は、限られた自然資源を一層効率的に活用することにつながります。

と類似しています。

その名前が示すように、ブラシレス DC モーターは、ブラシなしで動作するよう設計されています。つまり、ブラシが提供する整流（コミュニケーション）は電子的に処理する必要があり、BLDC モーターを回転させるには、1 つのシーケンスでステータの巻線に電流を流します。巻線に一度に流す電流量を計算するにはローターの位置を知る必要がありますが、通常、この位置はステータに埋め込まれたホール効果センサを使用して測定されます。これらセンサの信号を 3 つ組み合わせることで、制御機器は整流の正確なシーケンスを決定できます。

ブラシレスモーターでは、ローターに受動素子の巻線ではなく永久磁石を用いています。そのため、そのサイズと重量の割には、インダクションモーターよりも本質的に高出力を得ることができます。ただし、高効率動作は、FPGA ベースのコントローラに依存します。

FPGA ベースのアルゴリズム制御は、マイクロプロセッサによる制御よりも高効率で、台形制御、正弦波制御およびベクトル制御など、広範な制御システムアルゴリズ

ムが利用できます。

台形あるいは 6 ステップ制御は最も簡単な制御方法であると同時に、最も性能が低い方法でもあります。6 つの各整流ステップでは、モーター ドライバは、2 つの巻線間の電流バスにのみ関与し、第 3 のモーター フェーズは非接続状態です。しかし、トルクのリップルは、振動、ノイズ、機械の疲弊を誘起し、サーボ性能は大幅に低下します。

正弦波制御は、voltage-over-frequency 整流とも呼ばれ、上記の問題に対応します。正弦波コントローラでは、スムーズに変化する電流によって 3 つのモーター巻線を駆動することで、トルクのリップル問題は解消され、スムーズな回転が可能となります。正弦波整流の基本的な弱点は、時間とともに変化するモーター電流を基礎的な比例積分 (PI) 制御アルゴリズムで制御していることで、フェーズ（位相）間の相互作用が考慮されていません。その結果、高速回転の場合には性能が低下することになります。

ベクトル制御としても知られる FOC は、モーターの高速回転時に効率性を向上させるよう正弦波制御を改善します。これによ

り、ほかの制御技術と比較して、電源入力 1 ワット当たり最も大きなトルクを引き出し、さらに負荷が変動しても正確で応答速度の速い制御が可能となります。また FOC は、ステータとローターの磁束を完全に維持することで、過渡運転時でも効率を最適化します。

## FOC の詳細

FOC がどのように機能するかを理解する方法として、座標参照の変換過程を考えてみてください。ステータの観点から AC モーターの動作を想像すると、正弦波入力電流がステータに入っていることがわかります。時間とともに変化するこの信号が、回転する磁束を生成します。ローターの回転速度は回転する磁束ベクトルの関数です。固定された静止位置からのステータ電流と回転する磁束ベクトルは、AC（時間的に交互に変化する）量に見えます。

次に、モーターの内部において、ステータ電流が生成する回転磁束ベクトルと同じ速度で、回転するローターと一緒に動くところを考えてみてください。定常状態条件下で、上記の視点でモーターを観察すると、ステータ電流は一定値のように見え、回転する磁束ベクトルは固定されています。つまり、ステータ電流を制御して必要なローター電流を得なければならず、座標参照を変換することにより、簡単な PI 制御ループを用いて DC 値などのステータ電流を制御できます。

FOC アルゴリズムは、時間と回転速度の依存関係を取り除き、磁束とトルクそれぞれの直接的な独立制御を可能にすることで機能します。これは、クラーク パーク変換と呼ばれる数学公式を使用し、モーターの電気的状態を時不变の 2 次元回転座標に変換することで可能となります。

電力工学を制御する効率的な方法として、空間ベクトル パルス幅変調 (PWM) と呼ばれる手法がありますが、これはモーターの供給電圧を最大限利用し、高調波による損失を最小限にするものです。高調波は、モーターの鉄心内にエネルギーを消費する渦電流を引き起こすため、モーター効

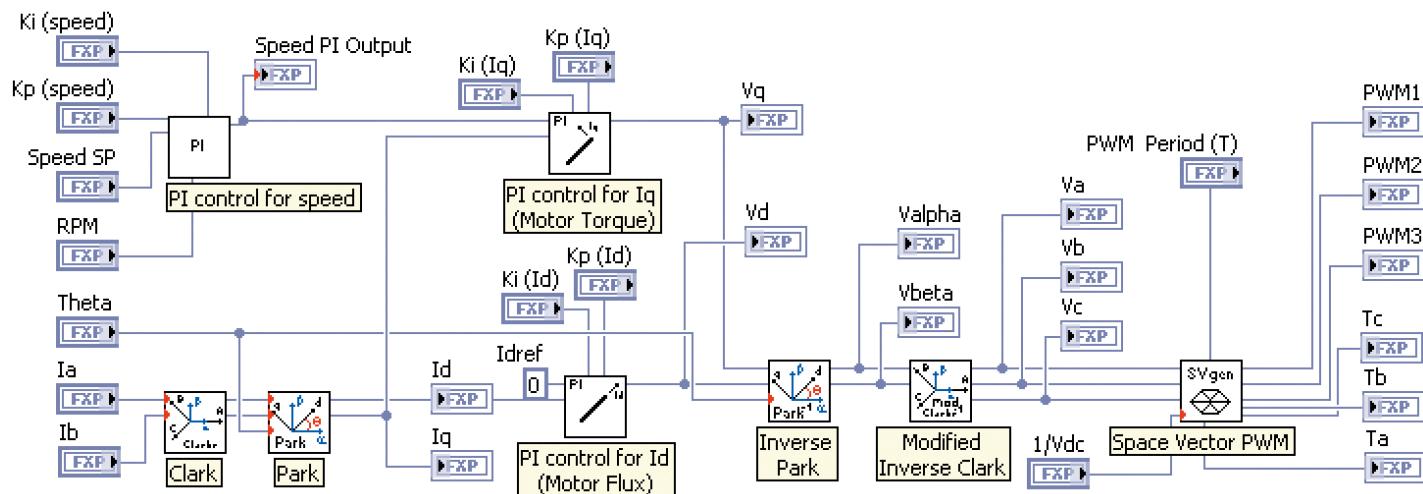

図 4 - ザイリンクス FPGA ベースの RIO ハードウェア プラットフォームを使用した FOC インプリメンテーションのシステム図

図 5 - LabVIEW FPGA のベクトル制御アルゴリズム

率を低下させる原因となります。

何よりも、AC インダクションとブラシレス DC の両モーターにベクトル制御を適用して、効率と性能を向上させることができます。また、FOC を既存のモーターに適用して、制御システムをアップグレードすることも可能です。実際、AC インダクションモーターに FOC と類似したベクトル制御技術を採用することで、サーボモーターのような性能が実現されます。

## FPGA で FOC の課題を解決

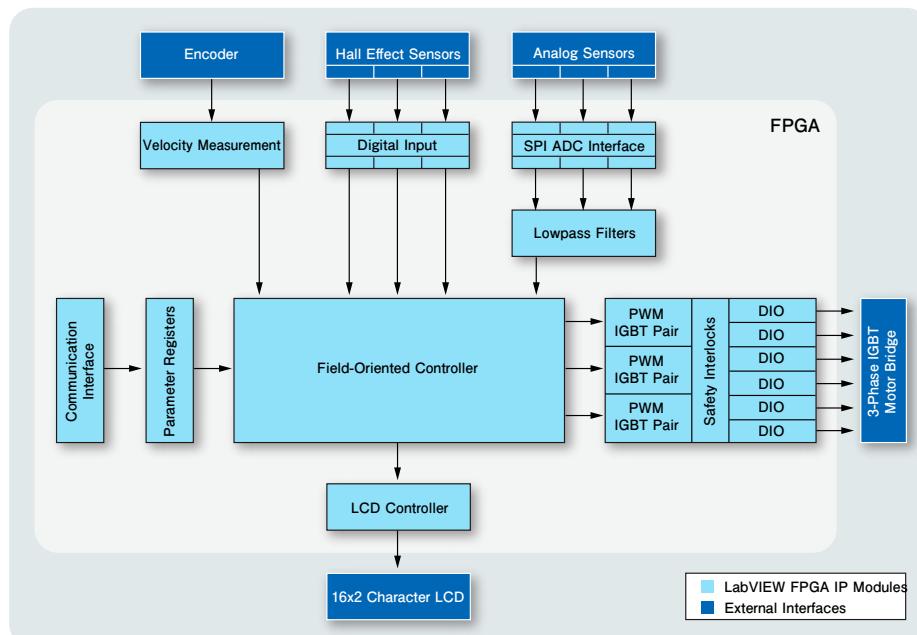

FOC をインプリメントするには強力な演算機能を持つデバイスが必要であり、この理由から FPGA はモーター制御に適していると言えます。FOC システムでは、10 ~ 100kHz のレートでベクトル制御アルゴリズムを連続的に再計算する必要があります。制御アルゴリズム処理と並行して、このアルゴリズムにタイミング上の影響を与えることなく、高速 PWM 出力などの知的財産 (IP コア) ブロックを実行しなければなりません。FPGA 生来の並列実行機能とハードウェアの信頼性により、最大 100kHz のループ レートで制御アルゴリズムを実行できます。また、同時に通信処理を行い、ホストマイクロプロセッサ上のユーザインターフェイス アプリケーションにデータを与えることができます。さら

に、FPGA はリコンフィギュレーション可能だから、必要に応じて随时、制御アルゴリズムを調整できます。

図 4 は、National Instruments 社の RIO プラットフォームでザイリンクス FPGA を用いて FOC をインプリメントするシステムを示します。実際の制御アルゴリズムのほかに、FPGA は、モーターを起動するための外部電子機器を駆動する PWM 信号を生成しながら、IP コア ブロックを実行し、3 つのホール効果センサ、エンコーダと 3 つの別のアナログ センサを読み出します。ホスト プロセッサとユーザー インターフェイスへの通信は、IP コア ブロックが並行して実行します。

図 5 は、FPGA ベースの FOC アルゴリズムを使用した LabVIEW FPGA のインプリメンテーションを示します。クラーク変換は、3 軸座標を  $120^\circ$  ( $I_a, I_b, I_c$ ) シフトして 2 軸直交座標 ( $I_a, I_b$ ) に変換します。第 2 のステップではパーク変換が、固定 ( $I_a, I_b$ ) 座標を切り離された 2 軸回転座標 ( $I_d$  と  $I_q$ ) に変換します。この 2 軸回転座標は、簡単な PI コントローラでも制御できます。FOC システムでは逆パーク クラーク変換を使用して、2 軸回転座標をステータ巻線の固定された 3 相 AC モーター フレームに戻します。NI 社は、完全なソース IP をウェブサイト [ni.com/ipnet](http://ni.com/ipnet) で提供しています。

NI 社のカスタマで、電子システムの設計と製造に携わる BAE Systems Avionics 社は、ザイリンクス FPGA を内蔵した RIO プラットフォームを使用して、既存のモーターの性能を 15% 引き上げ、さらにモーターの質量を低減することで宇宙電子工学製品の重量を削減しました。FOC の高効率性と厳重な電力制御によって、スコットランドのエジンバラにある BAE Servo Systems Technology Group は現在、以前の仕様よりも小さなモーターの仕様を採用しています。

機械メーカーの設計要件とはつまり、規制制限を満たしながらモーターの動作効率を改善し、迅速に投資に対する利潤を確保することです。制御システムのアップグレードを評価する際、エネルギーコストが低く見積もられることが多くありますが、実際に計算してみると、モーターの全寿命におけるエネルギーコストは、ハードウェアコストよりも一般的に数桁高いものになります。NI 社は、ザイリンクスの FPGA 技術に基づく標準のハードウェアソリューションを活用することで、高い演算性能に加え、柔軟性の高いエンベデッド コントローラの提供に取り組んでいます。この組み合わせにより、厳しいユーザーの要求、特に FOC の性能要件を満たすことができるのです。

# Optimizing Xilinx FPGAs for Power

# ザイリンクス FPGA の 消費電力を最適化

ツールや技術を活用しトータル消費電力を管理

Matt Klein

Principal Engineer, Technical Marketing

Xilinx, Inc.

[matt.klein@xilinx.com](mailto:matt.klein@xilinx.com)

IC のプロセス技術は、これまでの 6 年間で、130nm から 90nm、現在では 65nm ノードまで移行してきましたが、それぞれのプロセスで電力管理への重要性は増す一方です。トランジスタのリーク（漏洩）電流による電力損失がスタンバイモードでもかなりの量である、と各メーカーが気付き始めたのは 130nm ノードになってからでした。90nm では、IC の動作電圧は低下しましたが、リーク電流は増え続けデバイスの消費電力の大きな割合を占めました。65nm に移行してからも、この傾向は続いています。65nm ノードでのリーク電流は非常に顕著で、そのため多くの設計者は電力管理を FPGA の機能および性能の実現と同じくらい重要なと考えるようになっています。

従来 FPGA は、広範なアプリケーション向けに大量の高速トランジスタを使用して設計されたため、消費電力に関して、リーク電流の低減への努力が施されたデバイスであるといえません。リーク電流の多いトランジスタを使用しているという点では、最新のプロセス技術で設計している他

のシリコンも同様です。しかし、FPGA のプログラマビリティにおけるメリットに加え、消費電力を正確に見積もれる関連ツールの使用も可能で、最適化テクニックを施すことで FPGA を使ったデザインや、FPGA 搭載基板の消費電力をさらに最適化することが可能です。

FPGA の消費電力は、スタティックとダイナミックの 2 種類が存在します。スタティック電力はトランジスタのリーク電流が原因で発生するため、実際にデバイスが動作していない時でも消費します。ダイナミック電力は、デバイスが動作している時に消費する電力のことです。これはトランジスタのトグル（電圧の昇降の繰り返し）によるもので、電圧、周波数、静電容量の関数となります。2 種類の電力のそれぞれが異なる動作条件のもとでどのように変化するかを理解することは非常に重要で、それを理解することで設計するデザインの電力見積もりを最適化できます。

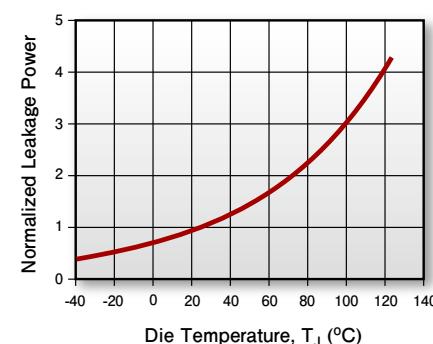

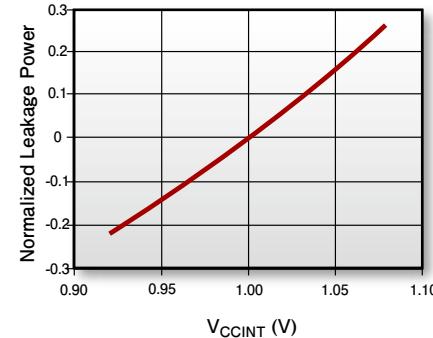

## ■ スタティックおよびダイナミック電力とその変動

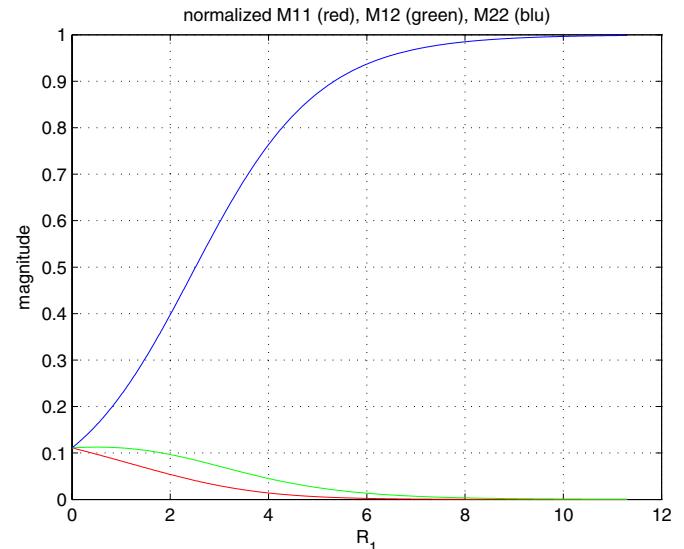

90nm の ASIC や FPGA でのリーク電流はかなり多くなりますが、65nm の場合はさらに深刻です。トランジスタから高性能を引き出すには、スレッショルド電圧を下げる必要がありますが、そうするとリーク電流も増えてしまいます。ザイリンクスはこれまでにリーク電流を減らそうと多くの試みを行ってきましたが、リークによるスタティック電力の変動は、ワーストケースと標準値との間で、およそ 2:1 となります。リーク電力はコア電圧 ( $V_{CCINT}$ ) による影響が大きく、 $V_{CCINT}$  の 3 乗で変化します。 $V_{CCINT}$  が 5 パーセント上昇しただけでも、スタティック電力は約 15 パーセント増えます。また、リーク電流はジャンクション（あるいはダイ）温度によっても大きな影響を受けます。図 1 と 2 は、リーク電流によるスタティック電力の変化を温度と電圧の関数で表したものです。

FPGA のスタティック消費電力の他の原因として動作回路の DC (直流) 電流がありますが、これはおおむねプロセス技術と

温度不变（プロセス技術と温度の影響を受けない）です。たとえば、I/O の DC 電流 (HSTL、SSTL、LVDS のような端末処理を有する標準での I/O 終端電圧など) と LVDS のような電流ドライバ I/O タイプの DC 電流があります。スタティック消費電力のソースとして FPGA のアナログ ブロックが挙げられますが、これもほとんどの場合プロセス技術と温度不变です。これらのアナログ ブロックの例としては、デジタルクロック マネージャ (DCM) があり、これはザイリンクス FPGA のクロック制御エレメントです。この他の例として、ザイリンクス Virtex® -5 FPGA で使用されているフェーズ ロック ループ (PLL) があります。また、ザイリンクス FPGA 内で入出力信号のプログラマブル遅延を選択するエレメントである IODELAY が挙げられます。

ダイナミック電力は、FPGA のコアや I/O でスイッチングの際に消費される電力です。ダイナミック電力を計算するには、トグルするトランジスタと配線の数や静電容量、トグル周波数を知る必要があります。トランジスタは、FPGA 内のロジックおよびメタル配線間のプログラマブル インターコネクトで使用されています。静電容量は、トランジスタのキャパシタンスとメタル配線のキャパシタンスからなります。ダイナミック電力の計算式は次のように表せます。

$$PDYNAMIC = nCV^2f$$

$n$  = トグルするノードの数、 $C$  = 静電容量、 $V$  = スイングの際の電圧幅、 $f$  = トグル周波数を示します。

ロジックをタイトにパッキングする (FPGA 内部でアーキテクチャの変更を行う) とスイッチングトランジスタの数を減らすことができます。小さなトランジスタを使用すると、トランジスタ間の配線長を短くできるため、ダイナミック電力を低減できます。そのため、Virtex-5 FPGA 内の 65nm トランジスタでは、ゲートのキャパシタンスは小さく相互配線長が短いため、この組み合わせでのノードの静電容量は 15 ~ 20 パーセント低減します。結果

図 1 - ダイ温度によるリーク電力の変化

Leakage Power vs. Junction Temperature

図 2 - コア電圧 ( $V_{CCINT}$ ) によるリーク電力の変化

Leakage Power vs. Core Voltage

的に、ダイナミック電力も低減できます。

電圧もダイナミック電力に影響します。90nm から 65nm プロセス ノードへの移行により、Virtex-5 FPGA のダイナミック電力は約 30 パーセント低減します。これは単に、 $V_{CCINT}$  を 1.2V から 1V に下げて得られた結果です。これに加えて、アーキテクチャ上の強化を図ることにより、ダイナミック電力の正味削減は、90nm 技術と比較して、40 ~ 50 パーセント減となります。（注：ダイナミック電力は  $V_{CCINT}$  の 2 乗で変化しますが、FPGA のコアでは温度とプロセス技術不变の傾向がさらに強くなっています。）

## ■ FPGA の電力解析ツール

ザイリンクスでは 2 種類の電力解析ツー

ルを用意しています。1つ目は、設計者がインプリメンテーションツールを使う前に使用する XPower Estimator (XPE) スプレッドシートツールです。また、デザインをインプリメントした後に使用する2つ目のツールが、XPower Analyzerです。これは、ユーザーが行った変更により、消費電力にどの程度影響したかをチェックするためのものです。

XPower Estimator は、ユーザーが記述した FPGA リソースの利用状況やトグルレート、負荷などの情報を元に、スプレッドシート上に電力見積もりを素早く行います。これは開発初期の電力評価に使用するツールで、電源やレギュレータ、システムの冷却方法(ヒートシンク、ファンなど)の選択基準になります。

この Microsoft の Excel ベースのツールでは、デバイス指向や設計指向、システム指向での消費電力の見積もりを行うことができます。単に予測される設計パラメータ、たとえばリソースの利用状況、動作環境、クロックやトグルレートなどを入力するだけで見積もりが行えます。これを入力すると、XPE は所定のデザインの電力見積もりを計算して、トータル消費電力や最大ジャンクション温度に加え、電源レールとブロックをベースにした電力などをレポートします。

見積もりプログラムを設定するには、ツ

ールの Process ファンクションが重要になります。これにより、ブロックごとの標準消費電力とワーストケース消費電力を知ることができます。主として、 $V_{CCINT}$  電源のリークによるスタティック電力はプロセス技術に大いに依存します。さらに、Voltage Source Summary により、電圧を変えた際に消費電力に及ぼす影響を素早く知ることができます。 $V_{CCINT}$  はすべてのコアロジックに供給されている電源の一つで、これを正しく理解しておくことが特に重要です。XPEツールのプロセス技術変動選択と電圧変動選択により、ワーストケースの電源規模を適切に決めることができます。

XPE のもう一つの価値の高い特長は Thermal Information/Summary で、ヒートシンクや PC 基板の特性と温度条件を指定できます。これは、そのデザインが民生用デバイスあるいは工業用デバイスの温度仕様を満たしているのかを確認するのに役立ちます。また、Block Summary はそれぞれのブロックの電力を表示し、Power Summary はスタティック電力とダイナミック電力の和を表示します。

XPE ツールのそれぞれのタブは、クロック、ロジック、I/O、ブロック RAM (BRAM)、PLL、DSP などの選択したりソースの利用状況やトグルレート等を入力するのに使用されます。

最後に、XPE の Graphs tab/sheet は、消費電力をプロセス技術や電圧、温度変動の関数としてグラフィカルに表示します。特に、Power by Function グラフィックは、それぞれの項目をリストアップしてその消費電力を示すため、最適化により最もメリットを受ける項目を特定できます。

2つ目のザイリンクス電力解析ツール XPower Analyzer は、インプリメンテーション時に抽出した正確なリソース情報に基づいて、より正確な視点からの

電力解析結果を提供します。このツールでは、テストベクタやシミュレーションベクタを使用することができますが、ベクタがなくても電力の見積もりは行えます。このツールは、FPGA デザインの物理的リソースに特長づけられた静電容量データを使用します。

XPower Analyzer は、ザイリンクスの統合ソフトウェア環境 ISE® Design Suite と連携し、内部のザイリンクスファイルフォーマットから配置／配線後の情報を受け取ることができます。これはまた、業界標準の Value Change Dump (VCD) や Switching Activity Interchange Format (SAIF) ファイルを扱うことができます。

VCD か SAIF フォーマットのいずれかを使用している場合は、代表するシミュレーションベクタを生成する必要があります。それにより、ツールはシステム内のノードのトグルレートを記録でき、またユーザーが後でこのデータにアクセスすることも可能です。これらのシミュレーションファイルがない場合は、XPower Analyzer ツールにベクタなしのシミュレーションをさせることができます。この種のシミュレーションでは、数学的統計的モデリングを使用して、始動トグルレートを実際のデザインロジック内に伝播させます。そして、デザイン内のそれぞれのノードのトグルレートを含んだ結果を生成します。

XPower は、ベクタベース (VCD と SAIF からの) ファイルでも、ベクタを使用しないシミュレーションでも、配置／配線の物理的接続性と正確なリソースの利用状況を考慮します。このツールは、各ノードの動作やトグルレートと、物理リソースの特長づけられた静電容量データおよび与えられたトグルレートでの各ブロック単独のダイナミック電力との相互参照を行います。図 3 は、総消費電力と最大ジャンクション温度を示しており、レールベース、ブロックベースおよび階層ベースでのそれぞれの電力レポートも表しています。

XPower は、デザインの部分ごとにどの程度電力を消費しているかを詳細に提示してくれます。また、「what if」解析により

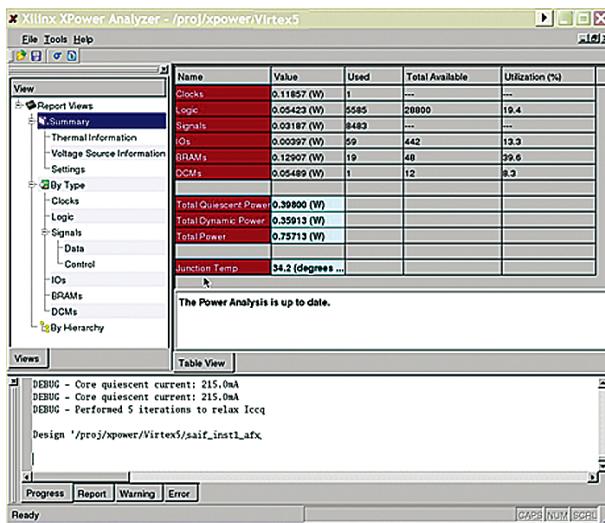

図 3 - ザイリンクス XPower Analyzer のサマリページ

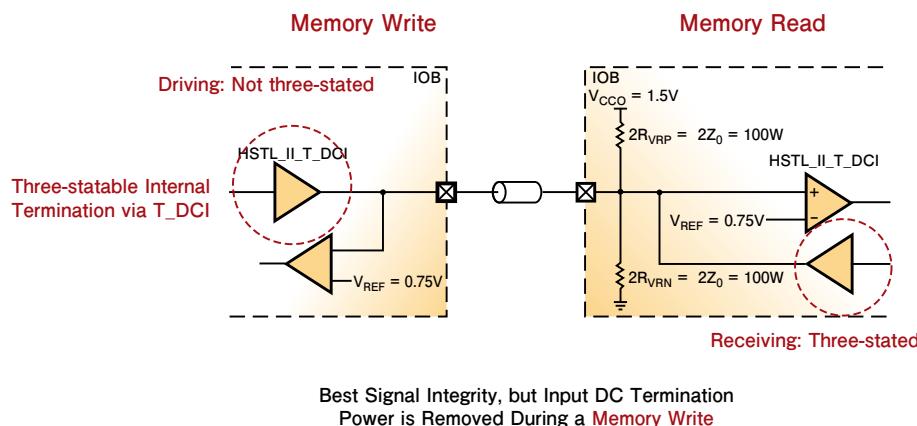

図 4 - T\_DCI を使用するメモリ リードとメモリ ライト時の FPGA のピン状態

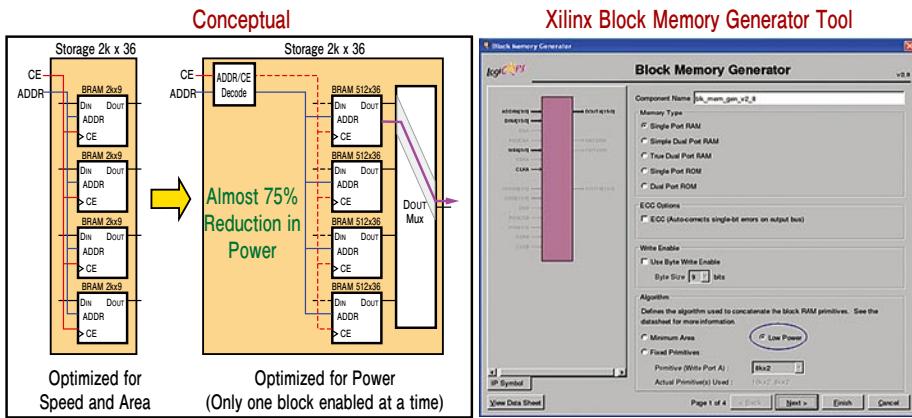

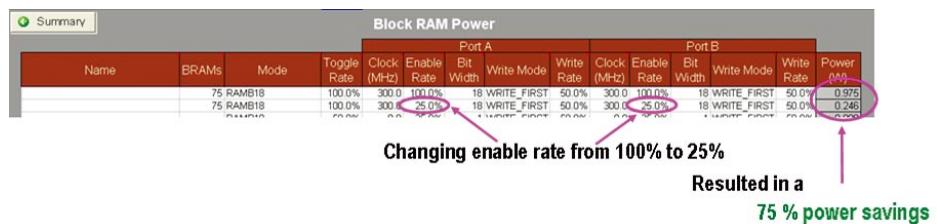

図 5 - パーツ サイズを 1 ランク下げる時のスタティック電力の削減

| VIRTEX™     | Static Power Reduction Going to Smaller Device |

|-------------|------------------------------------------------|

| 330k → 220k | -33%                                           |

| 220k → 110k | -51%                                           |

| 110k → 85k  | -24%                                           |

| 85k → 50k   | -46%                                           |

| 50k → 30k   | -33%                                           |

情報量を増やすことで、最適化によって最もメリットを受けるブロックがどこなのかを決定することができます。この最適化には、もっとも簡単なものから再設計が必要になるような複雑なものまであります。さらに、XPower では、デザインに対する実際の電力仕様を文書化することが可能で、その情報をボード レベルの作業チームに文書で伝達できます。

## FPGA のデザイン テクニックで消費電力を削減

プロセス技術が 65nm にシルクリングしたことにより、Virtex-5 の消費電力は必然的に削減されていますが、新しいツールや設計テクニックなどを使用することにより消費電力をさらに削減できます。

その一つの方法として、最適な大きさの FPGA を採用しそのプログラマビリティを利用することで、デザインの消費電力をさらに最適化することが可能です。デザイン上の各項目の選択により、スタティックとダイナミックの両消費電力は影響を受けます。

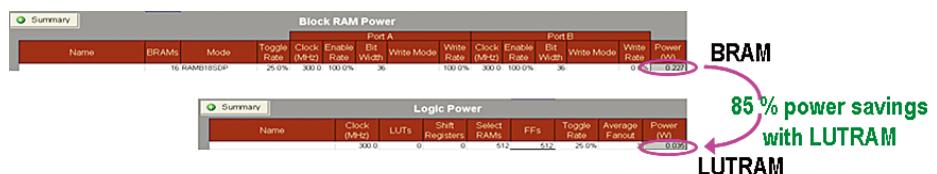

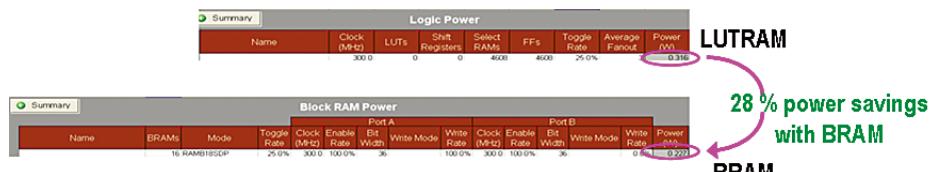

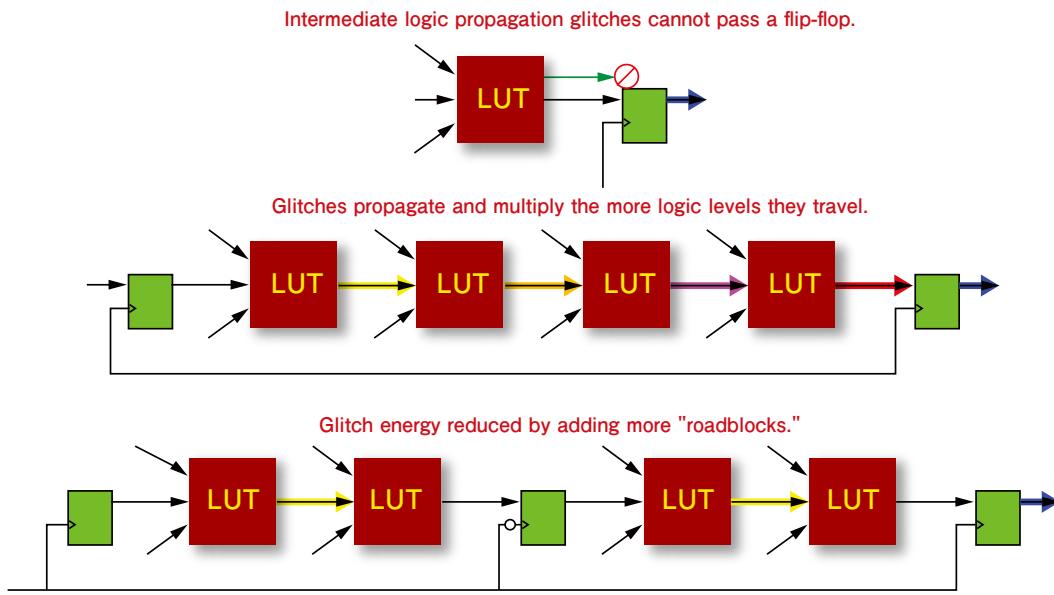

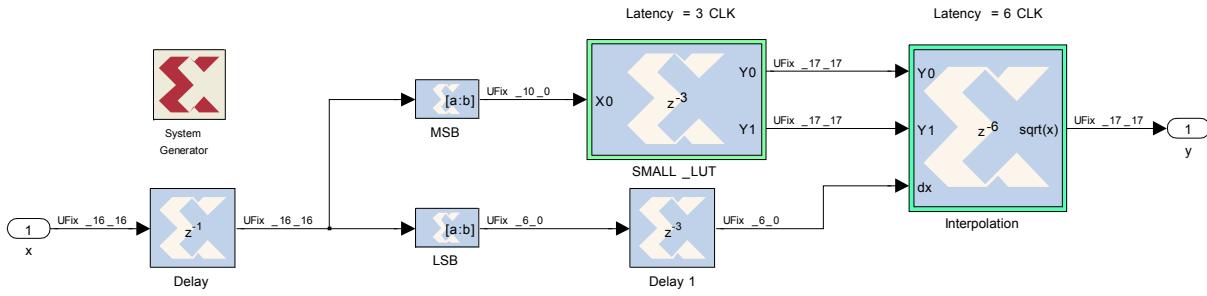

FPGA は数々のトランジスタによって構成されているために、リーク電流によるスタティック電力は、FPGA のロジック サイズに比例します。使用している FPGA のリソース数を削減できれば、より小さなデバイスにデザインをインプリメントでき