# Xcell journal

SOLUTIONS FOR A PROGRAMMABLE WORLD

## あらゆる分野で Smarter Vision を 実現する Zynq SoC

All Programmable デバイスで

Smarter Wireless Network を実現

OpenCV と Vivado HLS により

エンベデッド ビジョンを高速化

ザイリンクスのパワー エスティメーター

&パワー アナライザーツールの使用

ザイリンクスの

高位合成ツール

ページ 28

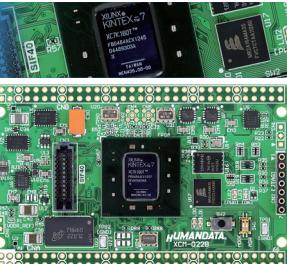

# FPGA / CPLD 評価ボード

すぐに使えるFPGAボードで、設計や試作コストが下げると思います。

- FPGAの動作に必要な最低限の機能を搭載単一電源ですぐに活用できます

- ACM/XCMシリーズはそれぞれ外形やコネクタ位置が同一で置き換えるが可能です

- 豊富なラインナップで100種類以上の製品をご用意しています

- 回路図、マニュアルは購入前でも自由に参照できます

- 豊富な納入実績で安心してお使いいただけます

- 基本的に即納体制で最短翌日からご活用いただけます

- スピードグレード変更などのカスタマイズもご相談ください

## Kintex-7搭載FPGAボード

Kintex-7 FBG484 搭載ブレッドボード

**XCM-022** シリーズ

クレジットカードサイズ Rocket I/O SIF40 DDR3 SDRAM MRAM

- XC7K70T-1FBG484C または XC7K160T-1FBG484Cを搭載

- ハートランシーバとメモリ搭載

- ユーザI/O 100本

- 3.3V単一電源動作、電源シーケンサ搭載

NEW

RoHS 指令対応品

Kintex-7 FBG484 搭載ブレッドボード

**XCM-022W** シリーズ

クレジットカードサイズ DDR3 SDRAM MRAM

- XC7K70T-1FBG484C または XC7K160T-1FBG484Cを搭載

- メモリ搭載

- ユーザI/O 100本

- 3.3V単一電源動作

- 電源シーケンサ搭載

- XCM-022から高速トランシーバ部分を除いた製品です

NEW

Kintex-7 FBG484 搭載ブレッドボード

**XCM-022Z** シリーズ

クレジットカードサイズ

- XC7K70T-1FBG484C または XC7K160T-1FBG484Cを搭載

- シンプル構成

- ユーザI/O 100本

- 3.3V単一電源動作

- 電源シーケンサ搭載

- XCM-022からメモリと高速トランシーバ部分を除いた製品です

NEW

RoHS 指令対応品

Kintex-7 FBG484 搭載ブレッドボード

**XCM-112** シリーズ

ハーフカードサイズ Rocket I/O DDR3 SDRAM

- XC7K70T-1FBG484C または XC7K160T-1FBG484Cを搭載

- ユーザI/O 128本

- 3.3V単一電源動作、電源シーケンサ搭載

NEW

RoHS 指令対応品

Kintex-7 搭載 USB-FPGA ボード

**EDX-008**

クレジットカードサイズ USB Config USB Comm DDR3 SDRAM MRAM HI-SPEED

- XC7K70T-1FBG484Cを搭載

- ユーザI/O 100本

- USB経由でFPGAコンフィギュレーション

- USBポートによりPCとUSB通信が可能

- 5V単一電源動作、電源シーケンサ搭載

NEW

RoHS 指令対応品

## Virtex-5搭載の新製品

Virtex-5 FFG676 搭載ブレッドボード

**XCM-113** シリーズ

ハーフカードサイズ DDR2 SDRAM

- XC5VLX30-1FFG676C、XC5VLX50-1FFG676C、XC5VLX85-1FFG676C または XC5VLX110-1FFG676Cを搭載

- ユーザI/O 128本

- 3.3V単一電源動作

NEW

RoHS 指令対応品

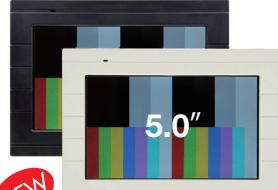

# LCDモジュール

タッチパネル付き5"カラーLCDモジュール

## UTL-021 シリーズ

- 3.3V 単一電源動作

- 内蔵圧電ブザーにより発音可能

- プラスチック製ベゼル付き

- I/F コネクタはTerasic 社のディスコン品(TRDB-LTM)に準拠したピンレイアウト

- 外形寸法 139 x 100 x 10 [mm] (W x H x D)

- 黒とグレーの2モデル

NEW

RoHS 指令対応品

タッチパネル付き3.5"カラーLCDモジュール

## UTL-024 シリーズ

- 3.3V 単一電源動作

- LCD コントローラ (セイコーエプソン社 S1D13781)

- 内蔵圧電ブザーにより発音可能

- プラスチック製ベゼル付き

- 外形寸法 94 x 78 x 9.5 [mm] (W x H x D)

- 黒とグレーの2モデル

NEW

RoHS 指令対応品

タッチパネル付き5"カラーLCDモジュール

## UTL-025 シリーズ

- 3.3V 単一電源動作

- LCD コントローラ (セイコーエプソン社 S1D13781)

- 内蔵圧電ブザーにより発音可能

- プラスチック製ベゼル付き

- 外形寸法 139 x 100 x 10 [mm] (W x H x D)

- 黒とグレーの2モデル

NEW

RoHS 指令対応品

# CameraLink 実験用ボード

## UTL-023

当社ACM/XCM-2シリーズにCameraLink用コネクタを接続するためのボードです。

電源付きユニバーサルボードZKB-106をベースに CameraLink入力用コネクタとCameraLink出力用コネクタおよび、LCD表示モジュールUTL-021用のI/Oコネクタを装備しています。

NEW

※その他 FPGA Boardやアクセサリを100種類以上ラインナップしています。詳しくはウェブをご覧ください。

# Xcell journal

|            |                                                                |

|------------|----------------------------------------------------------------|

| 発行人        | Mike Santarini<br>mike.santarini@xilinx.com<br>+1-408-626-5981 |

| 編集         | Jacqueline Damian                                              |

| アートディレクター  | Scott Blair                                                    |

| デザイン/制作    | Teie, Gelwicks & Associates                                    |

| 日本語版統括     | 秋山一雄<br>kazuo.okiyama@xilinx.com                               |

| 制作進行       | 周藤智子<br>tomoko.suto@xilinx.com                                 |

| 日本語版 制作・広告 | 有限会社エイ・シー・シー                                                   |

japan.xilinx.com/xcell/

Xcell Journal 日本語版 83 号

2013 年 9 月 10 日発行

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400

ザイリンクス株式会社

〒 141-0032

東京都品川区大崎 1-2-2

アートヴィレッジ大崎セントラルタワー 4F

© 2013 Xilinx, Inc. All Right Reserved.

XILINX や、Xcell のロゴ、その他本書に記載の商標は、米国およびその他各国の Xilinx 社の登録商標です。ほかすべての名前は、各社の登録商標または商標です。

本書は、米国 Xilinx, Inc. が発行する英文季刊誌を、ザイリンクス株式会社が日本語に翻訳して発行したものです。

米国 Xilinx, Inc. およびザイリンクス株式会社は、本書に記載されたデータの使用に起因する第三者の特許権、他の権利、損害における一切の責任を負いません。

本書の一部または全部の無断転載、複写は、著作権法に基づき固く禁じます。

## ザイリンクスの All Programmable ソリューションで、よりスマートな行動を

最近ザイリンクスのホームページをチェックされた皆様は、私たちが「Smarter System（よりスマートなシステム）」の新しいキャンペーンに全力を注いできたことにお気付きのことだと思います。ザイリンクスは、皆様がザイリンクスのデバイスを使用して開発してきた数々の製品に触発されつつ、未来をかたち作る、よりスマートなテクノロジの実現をサポートするツールをお届けしています。

ザイリンクスはこの 2 ル月間にわたって Smarter Network 構想を展開し、現在は、この号のカバーストリーに反映されているように Smarter Vision プログラムを推進しています。どちらのプログラムも、Smarter System の開発が可能なデバイスを提供するだけにとどまらず、これらのチップをサポートする IP コア、ツール、デザイン環境を合わせて提供するものです。

この号では、DSP の専門家として Chris Dick が、無線通信事業者がどのように迅速に Smarter Network を導入し、次世代ネットワークの収益力を高めているかについて記事を執筆しています。通信事業者が高速で高性能な基地局の増設によって帯域幅を拡張していた時代は過去のものとなりました。現在では、通信事業者はインテリジェント機能の追加と自己組織型ネットワーク アーキテクチャの導入により、状況に応じて最も必要とされる場所に対象範囲をシフトし、よりハードに行動するのではなく、よりスマートに行動しながら収益力を高めようとしています。

一方、筆者が担当しているカバーストリーでは、非常に魅力的なテーマである Smarter Vision について解説しています。この記事で述べたように、エンベデッド ビジョンの世界は飛躍的に成長し、ビジョン システムがあらゆる分野に広く普及するまでに至っています。現在、エンベデッド ビジョンは、ゲーム機から自動車、工場、病院に至るまで、あらゆるところで利用されています。製造・流通業者までがエンベデッド ビジョン テクノロジから利益を得ていますが、このテクノロジは、従来は FPGA とスタンドアロン プロセッサを組み合わせて利用していました。しかし私たちザイリンクスは、Zynq™-7000 All Programmable SoC などの高性能シリコン プラットフォームを使用すれば、2 つまたは 3 つのチップの代わりにワンチップで、はるかに高機能なエンベデッド ビジョン システム (Smarter Vision システム) を開発できると考えています。

ザイリンクスはこのような取り組みを容易にするために、Vivado Design Suite の Vivado™ HLS ツールを通じて非常に幅広いソフトウェア開発環境のサポートを提供し、高位合成テクノロジの普及をさらに推し進めています。システム設計者は、C/C++ で設計したビジョン アルゴリズムから、Vivado HLS を使用して RTL バージョンを作成できます。このプロセスでは、たとえば、特定のアルゴリズムまたはその一部が Zynq All Programmable SoC 内のプロセッサ システムと FPGA ファブリックのどちらで実行するのに適しているかを確認できます。

ザイリンクスは 2013 年 4 月、Vivado Design Suite のリリース 2013.1 に、さらに高度な Smarter Vision 自動開発機能を追加しました。これにより、IP インテグレーターと呼ばれるツールを使用して、業界最速でのインテグレーションが可能になりました。また、この Vivado リリースでは、ビジョン設計者のデザイン作業の生産性を向上させるザイリンクスの OpenCV コア ライブラリが発表されました。ライブラリの最初のリリースで、OpenCV ライブラリから 30 種類以上のよく使用されるアルゴリズムを用意し、RTL バージョンを作成しました。これらのアルゴリズムをデザインに追加すれば、Smarter Vision システムをいち早く設計できます。さらに、これらのアルゴリズムを使用して、Zynq All Programmable SoC 上およびほかの ARM+DSP および ARM+GPU ベースのハードウェア プラットフォーム上で関数を実行し、各種のハードウェア プラットフォームを評価できます。この号の 20 ページでは、Jose Alvarez と Fernando Vallina が OpenCV の利点について解説しています。

最後に、『Microprocessor Report』と『EDN』の前編集長であり、筆者の古い友人である Steve Leibson が先頃ザイリンクスに入社し、有線および無線の Smarter Network と Smarter Data Center に関する包括的な背景記事を執筆したことをお知らせします。この背景説明は、これらの市場におけるトレンドについて詳しく説明し、ザイリンクスの Smarter Network テクノロジが、これらのトレンドに対する顧客各社の対応に、どのように貢献しているかを論じたものです。この記事は、[http://japan.xilinx.com/publications/prod\\_mktg/smarter-networks-backgrounder.pdf](http://japan.xilinx.com/publications/prod_mktg/smarter-networks-backgrounder.pdf) から PDF 形式でダウンロードできます。

この号および関連するリソースを契機として、皆様が次の一步を踏み出し、Zynq All Programmable SoC をまだ試していない方々もこの製品をお試しになることを願っています。

Mike Santarini

発行人

# GET PUBLISHED

## 記事投稿のお願い

みなさんも Xcell Publications の記事を書いてみませんか？

執筆は思ったより簡単です。

ご自分の経験に著作物を追加し、帰属コミュニティ内の信用と認知度を高めることに关心がおありますか。各種の賞を受賞した、評価の高い世界的出版物である Xcell Journal に、記事を投稿してみてはいかがでしょう。Xcell 編集チームは、プランニング、コピー編集、グラフィックス開発、ページレイアウトなどの編集プロセスを通じて、アイデアの展開から記事の出版まで、新しい執筆者の方や経験豊富な方々を日頃からお手伝いしています。執筆者の皆様は、執筆者向けガイドラインと記事のテンプレートから得られる十分な方向付けによって、新製品、画期的な研究、あるいはデザインの一般的な問題に対する独創的なソリューションなど、選んだテーマを始めから終わりまでの確に表現することに集中できます。デザイン担当スタッフは、芸術的なアイデアを効果的な図版として実現したり、プロによる仕上げが必要な図版を描き直したりして皆様をお手伝いします。私たちは、編集プロセス全体を通じて執筆者との連絡を密にし、執筆者が記事を校閲して必要な修正を加えられるようにして、最高水準の技術的正確さを保証します。Web ベースの Xcell Online またはデジタル版の Xcell Journal に公開される、記事の最終稿をご投稿ください。指定された担当編集者とグラフィック アーティストが、執筆者との協力の下に、わかりやすく、専門的で、効果的な記事を実現いたします。このエキサイティングで実りの多いチャンスの詳細は、下記までお問い合わせください。

Xcell Publications 発行人

Mike Santarini

[xcell@xilinx.com](mailto:xcell@xilinx.com)

<http://japan.xilinx.com/publications/index.htm>

[japan.xilinx.com/xcell/](http://japan.xilinx.com/xcell/)

XILINX®

## VIEWPOINTS

**Letter From the Publisher**

ザイリンクスの All Programmable

ソリューションで、よりスマートな行動を ... 1

XCELLENCE BY DESIGN

APPLICATION FEATURES**Xcellence in Wireless Communications**

ザイリンクスの All Programmable デバイスで

Smarter Wireless Network を実現 ... 12

**Xcellence in Embedded Vision**

OpenCV と Vivado HLS を使用して、

Zynq SoC のエンベデッド ビジョン

アプリケーションを高速化 ... 20

**Cover Story**

あらゆる分野で

Smarter Vision を実現する

ザイリンクスの Zynq SoC

4

## THE XILINX XPERIENCE FEATURES

**Xplanation: FPGA101**

FPGA のデザインを迅速化する

ザイリンクスの高位合成ツール ... 28

**Xplanation: FPGA 101**

ザイリンクスのパワー エスティメーター

およびパワー アナライザー ツールの使用 ... 36

**XTRA READING**

**Xpedite**... ザイリンクス アライアンス プログラム

パートナーが最新の優れたテクノロジを提供 ... 42

**広告索引**

有限会社ヒューマンデータ ..... 表 2

Excellence in Magazine & Journal Writing

2010, 2011

Excellence in Magazine & Journal Design and Layout

2010, 2011, 2012

# All Eyes on Zynq SoC for Smarter Vision あらゆる分野で Smarter Vision を実現する ザイリンクスの Zynq SoC

Mike Santarini

Publisher, Xcell Journal

Xilinx, Inc.

[mike.santarini@xilinx.com](mailto:mike.santarini@xilinx.com)

Zynq SoC とザイリンクスの

新しいツールおよび IPコア の

組み合わせにより、

次世代のエンベデッド

ビジョン製品の基盤を構築

T

ドライバーの乗っていない自動車が自動的に駐車スペースを見つけて駐車する Audi の自動駐車テクノロジのデモをご覧になったことがありますか。Kinect コントローラーを使用して Xbox 360 のゲームをしたことがありますか。また、近所の食料品店で購入した傷のない果物を口にしたことがあるなら、あなたも Smarter Vision システムの時代の幕開けを目撃していることになります。Smarter Vision テクノロジは、極めて高度な電子システム製品からただのリンゴに至るまで、あらゆる種類の製品に影響を与えています。Smarter Vision システムの機能は現在でも十分に印象的ですが、10 年後には、自動車からファクトリー オートメーション、医療、監視、家庭用、航空宇宙、国防に至るまで、非常に多くの電子システムにさらに優れた機能を持った Smarter Vision システムが搭載されることを予測する専門家もいます。

Smarter Vision システムが複雑性を増すにつれて、ネットワーク化された高速道路を自律走行する自動車が一般的になるでしょう。また Intuitive Surgical 社の驚異的なロボット支援手術システムなどの医療機器もさらに進化を続け、外科医が遠隔地から施術できるようになるでしょう。テレビとテレプレゼンスはこれまでにない没入感と対話性を実現し、映画館や各家庭、店舗のスクリーンに表示される情報は、個々の消費者の興味だけでなく、そのときの気分に合わせて変化するようさえなるでしょう。

最先端のビジョン システムは、画像を強化したり分析したりするだけでなく、これらの分析に基づ

いてアクションを作動させます。このため、必要とされる処理能力は飛躍的に高度化しています。

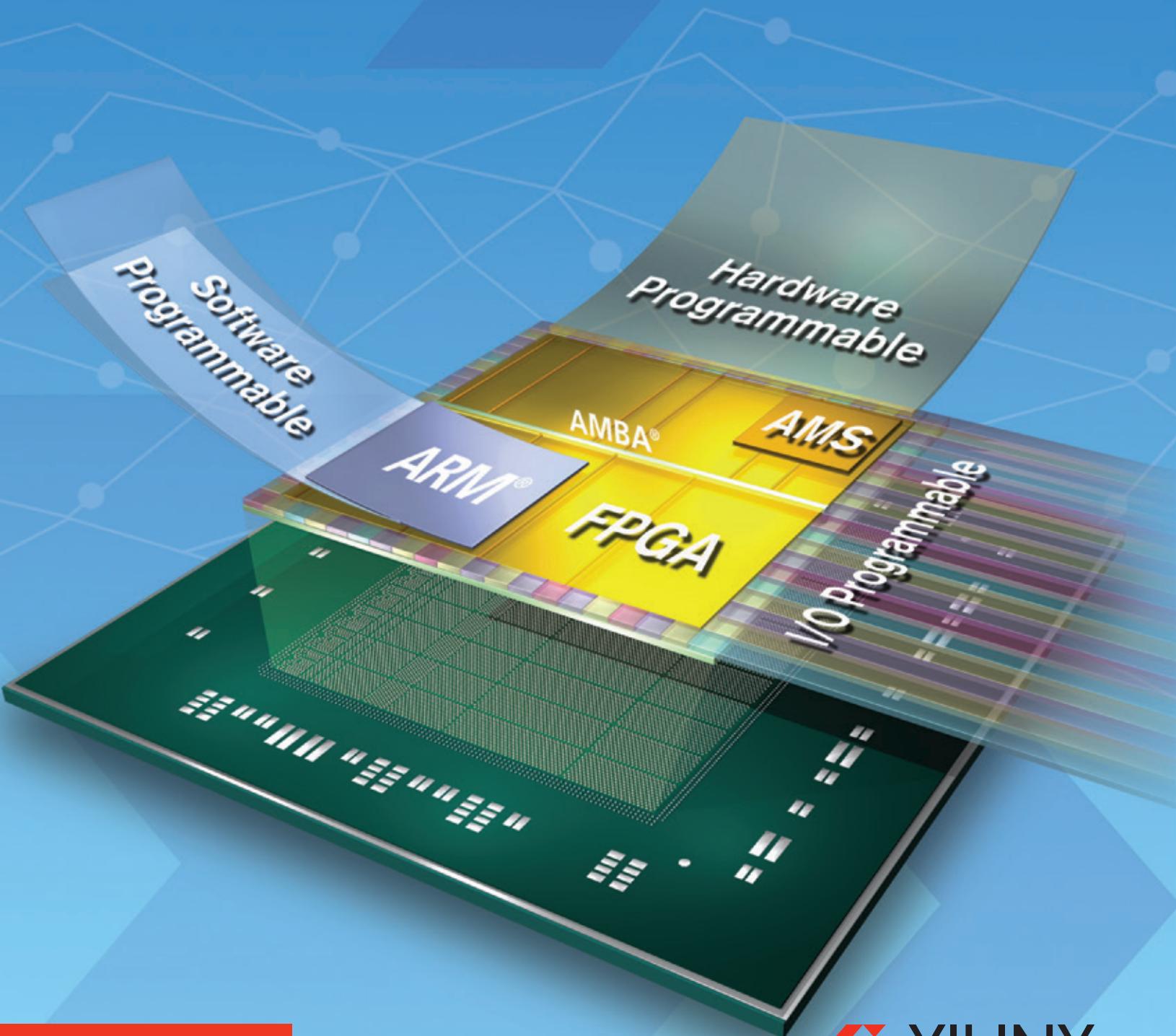

ザイリンクスの Smarter Vision 向け All Programmable ソリューションは、このような革新の最先端を担っています。ザイリンクスは、ARM® のデュアルコア Cortex™-A9 MPCore™、プログラマブル ロジック、および重要な周辺機器を初めてワンチップに統合した Zynq™-7000 All Programmable SoC を基盤として、こうしたビジョン システムにおける新技術の開発と迅速な提供を可能にするために重要な役割を担うツールと IP のサポート インフラストラクチャを発表しました。このインフラストラクチャには、Vivado™ HLS（ハイレベル合成）ツール、新しい IP インテグレーター ツール、OpenCV（コンピューター ビジョン）ライブラリ、SmartCORE™ IP および専用の開発キットが含まれます。

ザイリンクスのコーポレート ストラテジおよびマーケティング担当シニア副社長である Steve Glaser は次のように述べています。「ザイリンクスの All Programmable Smarter Vision テクノロジにより、次世代の Smarter Vision システムを他社に先駆けて開発できます。この 10 年、ザイリンクスの顧客は、従来のシステムで使用していたプロセッサでは十分な速度で実行できなかった機能を、FPGA によって高速化してきました。Zynq-7000 All Programmable SoC は、プロセッサと FPGA ロジックをワンチップに統合し、Smarter Vision アプリケーションに最適なシリコン プラットフォームを開発者に提供します。」

Glaser はこのデバイスの特長を次のように説明しています。「Zynq-7000 All Programmable SoC は、Vivado HLS、新しい IP インテグレーター ツール、OpenCV ライブラリ、SmartCORE IP および開発キットで構成される堅牢な開発環境によってサポートされます。これらの Smarter Vision テクノロジにより、次のデザインにいち早く着手し、これまでにないレベルの効率性、システムの省電力化、システム性能の向上、および BOM（部品）コストの劇的な削減を実現できます。こうしたイノベーションが急速に進むにつれて、収益の向上とともに、生活を豊かにし、生

命を救うことも可能となります。」

## ただのカメラから SMARTER VISION へ

Smarter Vision システムの根幹にあるのは、エンベデッド ビジョンです。急速に成長し続ける業界団体であるエンベデッド ビジョン アライアンス ([www.embedded-vision.com](http://www.embedded-vision.com)) の定義によれば、エンベデッド ビジョンとは、エンベデッド システム（プロセッサを使用する、コンピューター以外の電子システム）とコンピューター ビジョン（マシン ビジョンとも呼ばれる）を融合したものです。

エンベデッド ビジョン アライアンスの発起人で、コンサルティング会社 BDTI の CEO である Jeff Bier 氏は、次のように述べています。「モーター駆動でパン、チルト、ズームするアナログ カメラ システムの時代をはるかに超えて進化したこと、エンベデッド ビジョン テクノロジは業界に極めて大きな影響を与えました。デジタル時代に入ってから、既にかなりの時間が過ぎました。私たちは、カメラが見ているものを圧縮、保存、強化することに優れた初期のデジタル システムから、カメラがいま見ているものを知ることができる現在のスマートなエンベデッド ビジョン システムまで、エンベデッド ビジョンが急速に進化していくのを目の当たりにしてきました。」

最先端のエンベデッド ビジョン システムは、画像の強化や分析だけではなく、これらの分析に基づいてアクションを作動させます。このため、必要とされる処理能力や計算能力、アルゴリズムの洗練度は飛躍的に高度化しています。このような進化の例として、急速に進化している監視システム市場が挙げられます。

20 年前、監視システム ベンダーは、機械的システムによるオートフォーカスとチルト機能によって明瞭で幅広い視野を提供する最高のレンズを競い合って提供していました。このようなシステムは、基本的にはアナログ ビデオ カメラを同軸ケーブルでビデオ録画装置付きアナログ モニターに接続したもので、それを警備員が監視していました。これらのシステムの鮮明度、信頼性、および有効性は、光学部品やレンズの品質に制約され、カメラが映すものを監視する警備員の努力にも依存していました。

エンベデッド ビジョン テクノロジの登場により、監視装置会社は、デジタル テクノロジによる低コストのカメラを使用できるようになりました。デジタル処理により、レンズによるアナログ セキュリティ システムをはるかにしのぐ素晴らしい機能を、より低コストでシステムに実装できるようになりました。魚眼レンズとエンベデッド処理システム、さまざまなビジョン中心アルゴリズムを組み合わせることにより、カメラが作り出す映像が飛躍的に向上しました。照明条件の修正、フォーカスの改善、AOI（検知対象領域）の色の強化とデジタル ズームを実行するテクニックにより、パン、チルト、ズームの機械的モーター制御が不要になり、システムの信頼性が向上しました。デジタル信号処理により、1080p 以上のビデオ解像度も実現されました。

鮮明な画像をデジタル信号処理で編集できる能力は、ビジョン システムの機能向上の端緒に過ぎませんでした。高度化したピクセル処理を使用して、監視システムのメーカーは、デジタル システムでキャプチャされた高品質画像の分析をリアルタイムで実行する、より高性能なエンベデッド ビジョン システムの開発を始めました。これらのエンベデッド ビジョン システムの最も初期のものは、特定の色、形状、動きを検出する機能を持っていました。この機能は、カメラの視野内の仮想的フェンスを通り過ぎた物体を検出し、映像内のその物体が実際に人間であるかどうか判断して、データベースとのリンクによって個人の特定まで行うアルゴリズムへと急速に進化していました。

## 不審な振る舞いの検出

先進の監視システムは、セキュリティ ネットワークの視野を移動していく検知対象の個人が 1 つのカメラの視野から消えて死角に入り、その後監視ネットワーク上の別のカメラの視界に入るところを追跡できる分析機能を備えています。これらのシステムの中には、異常な動きや不審な動きを検出するように設計されたシステムもあります。ザイリンクスの ISM（産業、科学、医療）グループのシステム アーキテクトである Mark Timmons は次のように述べています。「現在の監視システム市場における最大のトレンドは分析機能です。この分析機能は、人為

ミスを見つけるだけでなく、有人での監視や意思決定さえ不要になります。ご想像のように、駅やスポーツ イベントなどの混雑した環境での監視作業は極めて困難な場合があるため、危険な密集状態を検知し、不審な振る舞いをする（おそらくは極端な動きを繰り返す）個人を追跡する分析機能には大きなメリットがあります。」

この分析機能をさらにアップさせ、これらのシステムの有効性を向上させるため、監視を始めとする多くの Smarter Vision 活用マーケットでは、カメラとサーマル ビジョン、レーダー、ソナー、LIDAR (Light/Laser Detection and Ranging) などのセンシング テクノロジを組み合わせた「フュージョン（融合型）」アーキテクチャの使用が増えています。この方法で、Smarter Vision システムは、暗視を有効にし、熱シグネチャを検出し、カメラだけではキャプチャも可視化できない対象を捕捉できます。この機能により、誤り検出が著しく減少し、はるかに高精度な分析が可能になります。言うまでもなく、複数のテクノロジの融合とその後のデータ分析のために複雑性が増大するため、分析にはさらに高い処理能力が要求されます。

Timmons は、このマーケットのもう 1 つの大きな潮流は、これらの複雑な解析をすべて監視システム ネットワークの「末端で」行うことだと述べています。これは、各カメラのデータを中央のメインフレーム システムに送信し、複数の供給源からのデータを使用してより精緻な分析を行うのではなく、各カメラ内で分析を行うという意味です。ローカル型の分析機能では、セキュリティ システム全体の耐障害性が向上し、システム内の各ポイントの検出がより高速かつ高精度になり、カメラが脅威を発見した場合は監視員により早く警報できます。

ローカル型の分析機能では、各ユニットが、見えている内容を拡張し分析するために大きな処理能力を持つ必要が生じると同時に、コンパクトでありながら高度に統合された電子機能を組み込む必要があります。各ユニットはネットワークのほかの部分と確実に通信する必要があるため、電子通信機能を内蔵する必要があります、計算処理はさらに複雑になります。これらの監視ユニットは、大規模な監視システムの一部として無線ネットワークで接続されることが多くなっています。

また、これらの監視システムは、大型のエンタープライズ ネットワーク、あるいは米軍の Global Information Grid のようなさらに大規模なグローバル ネットワークの一部になる機会が増えています (Xcell Journal (英文) 69 号 Page 8 COVER STORY を参照、<http://www.xilinx.com/publications/archives/xcell/Xcell69.pdf>)。

このような高度化したシステムは、歩兵のヘルメットから中央司令部にネットワーク接続された軍事衛星に至るまで、軍事防衛システム市場のあらゆる製品に採用されています。さらに注目に値するのは、Smarter Vision テクノロジがどれほどのスピードでほかの市場にも拡大し、生活の質や安全性を向上させているかということです。

## 食品分野における SMARTER VISION

たとえば、リンゴの例を考えます。リンゴがどのようにして良い状態で近所の食料品店に並べられるかを考えたことがありますか。ザイリンクスの ISM (産業、科学、医療) グループのアーキテクトである Giulio Corradi は次のように述べています。「現在、食品会社は、さらにスマートな Smarter Vision システムを食品検査ラインで使用して、たとえば品質の劣るリンゴを良品のリンゴから選別しています。高速食品検査ラインに実装された第 1 世代のエンベデッド ビジョン システムは、リンゴなどの産物の表面の欠陥を検出する 1 台または複数台のカメラを搭載していました。エンベデッド ビジョン システムが色の異常を検出した場合、そのリンゴはさらなる検査のためにマーキング / 選別されるか、あるいは廃棄されます。」

## 目に見えない箇所の安全性の確保

では、その前の段階で果物が落下し、目に見えない損傷を受けた場合はどうなるでしょう。Corradi は、「場合によっては、落下による損傷は、人の目は言うまでもなく、カメラでも簡単には検出できないことがあります」と述べています。「その損傷は、實際にはリンゴの果肉部分にあるかもしれないのです。そのため、より高度な一部の Smarter Vision システムは、カメラに赤外

線センサーを組み合わせて、リンゴの果皮の奥にある損傷を検出しています。傷のある果実が見つかると、機械的ソーターが作動して、そのリンゴをラインから排除し、食料品店への出荷を防ぎます。」損傷を受けたリンゴが Smarter Vision システムを介さずに通過した場合、損傷は食料品店の棚に並ぶ頃には目に見えるようになり、リンゴを廃棄せざるを得なくなるでしょう。もちろん、腐ったリンゴが 1 つあれば、ほかのリンゴにも悪影響が及びます。

分析機能はまた、傷のあるリンゴを、別の Smarter Vision システムを配備した新しいラインに送って、アップル ソースやドライ フルーツなどに転用するか、あまりにも状態がひどい場合には堆肥にするかを判断するのも役立ちます。

Corradi によれば、Smarter Vision は工場の生産現場における作業者の保護にも使用されています。現在、多くの工場がオートメーション化され、ロボット支援テクノロジ、または完全自動化されたロボット ラインを使用しています。既存のロボット ラインのツールを変更して、ほかの用途に転用することもあります。頻繁に変更される製造ライン上のロボットを従来の安全柵で囲んで保護すると、ゾーンが窮屈になり、十分な可動範囲を確保できません。

そのため、自動化された工場ラインの可動範囲を制限することなく作業者の安全を守るために、各企業は Smarter Vision を導入して安全システムを構築しています。カメラとレーザーが仮想フェンスまたはバリアを設置し、製品製造中に誰かが工場ラインの近くに寄りすぎると、作業者（および安全監視員）に音声で警告します。外側のバリアを人が通過したときは音声で警告し、ロボットに近い 2 つ目のバリアを人が通過すると自動的に全製造ラインをシャットダウンして事故を防ぐ、多重の仮想バリア システムを導入した例もあります。エンベデッド ビジョン アライアンスの Bier 氏は、この種の仮想バリア テクノロジは広い範囲に応用可能であると述べています。「仮想バリア テクノロジは、工場の事故件数の削減に大きく貢献できます。さらに、遊園地内や、家屋、プール、自動車の周囲に仮想バリアを設置することも考えられます。近い将来、私たちの身の回りで、より多くの仮想バリア システムを目にすることになると思います。」

仮想バリアは、工場の事故件数の削減に大きく貢献できます。さらに、「遊園地内や、家屋、プール、自動車の周囲に仮想バリアを設置することも考えられます。」

## SMARTER VISION による運転支援システム

自動車市場は、ストレスの少ない安全な運転のために Smarter Vision をフルに活用できる分野です。Xilinx Automotive のシステム アーキテクトである Paul Zoratti によれば、自動車市場における高性能ドライバー アシスタンス システム (ADAS) とは、Smarter Vision を含むリモート センシング テクノロジを使用してドライバーの運転をサポートする技術です (Xcell Journal 日本語版 65・66 合併号のカバー ストリーを参照、[http://japan.xilinx.com/publications/archives/xcell/xcell65\\_66\\_j.pdf](http://japan.xilinx.com/publications/archives/xcell/xcell65_66_j.pdf))。

この 10 年、自動車メーカーは、年々機能が向上した運転支援 (DA) 機能を高級車ラインで発表するとともに、多数のドライバー支援機能をスポーツ車や一般車ラインにも搭載してきました。死角検出、車線変更支援、歩行者および信号検出など、これらの機能の多くは、潜在的な危険のある状態を検出すると、ドライバーに警告を送ります。自動車メーカーによる最近の製品には、自動緊急ブレーキや車線維持など、さらに進んだシステムが搭載されています。これらは、自動車環境の潜在的な問題を監視するだけではなく、ドライバーが適切な行動を取れるようにサポートして、事故を回避したり、事故の深刻度を軽減したりします。

Zoratti によれば、最新モデルの自動車の一部は、左右、フロント、リアに 4 つのカメラを搭載し、自動車周辺の途切れのない 360 度の視界をドライバーに提供しています。第 1 世代の周辺表示システムは、これらのカメラを使用してドライバーに映像を提供していますが、将来のシステムには追加の運転支援 (DA) 機能が搭載されそうです。次世代のシステムは、同じ 4 つのカメラと画像処理分析機能を使用して車両の鳥瞰図を生成し、同時に歩行者の存在などの潜在的な危険を警告します。さらに、自動車が高速走行している場合、左右およびリアに搭載されたカメラを使用して死角検

出、車線変更支援、車線逸脱警告を行います。フロントガラスの裏側に前向きのカメラをもう 1 台追加することで、信号認識機能と前方車両衝突警告機能をサポートします。

最後に、ドライバーが目的地に到着し、自動駐車機能を起動すると、これらのカメラとほかのセンサーのサポートにより、半自動的に駐車スペースに駐車できます。

これらのタスクをすべてリアルタイムで実行するには、並列ハードウェア計算に最適化された極めて大きな処理能力が必要になると Zoratti は述べています。このため、初期の DA システムの多くは、FPGA とスタンダードアロンのマイクロプロセッサを組み合わせて、FPGA で並列計算の大部分を処理し、マイクロプロセッサで逐次的な意思決定を実行していました。

各カメラで分析機能を処理する監視システムなどの市場とは異なり、自動車市場では、コスト面の制約のために、分析機能は各カメラではなく中央のコンピューター ハブで処理されます。これにより、自動車メーカーは各カメラ センサーのコストを最小限に抑え、最終的にはシステム全体のコストを最小化できます。したがって、4、5、さらには 6 つのリアルタイム ビデオ入力を同時に処理できるように、中央ユニットの処理プラットフォームには非常に高い性能と広い帯域幅が必要とされます。

## 医療分野における SMARTER VISION

Smarter Vision が劇的な変化をもたらしているもう 1 つの分野として、医用電子工学業界が挙げられます。この業界では、Smarter Vision テクノロジは、内視鏡や画像スキャナー (CT、MRI など) から、Xcell Journal (英文) 77 号 Page 38 (<http://www.xilinx.com/publications/archives/xcell/Xcell77.pdf> を参照) に掲載されている Intuitive Surgical 社の Da Vinci などのロボット手術システムに至るまで、幅広い医学画像システムに利用されています。

Da Vinci の高度な 3D ビジョン システムにより、外科医はロボティック手術機器を極めて高精度に、なめらかかつ触覚的に操作し、多数の精密で入り組んだ外科的処置を行えます。どの世代のシステムでも、外科医はさまざまな手術を数多く実施できる

ため、患者の予後の改善と回復期間の短縮に貢献します。これらの処置を制御し調整するには、極めて高度なテクノロジが必要であり、プロセッサとロジックを組み合わせた処理能力に大きく依存します。新しいテクノロジは、各世代ごとにプロセッサとロジックの統合が進むことからメリットが得られるはずです。

## SMARTER VISION による没入型体験

Smarter Vision は、ネットワークを介したコミュニケーションにも飛躍的な進化をもたらします。最新のオフィスビルで働いている方なら、世界中の人と話せるだけでなく、その場にいるかのように相手を見ることができる、高度なテレプレゼンス会議システムを備えた会議室が会社にあるでしょう。このようなビデオ会議システムは、テーブルまたは会議でどな人が話しているかを検出し、自動的にその人の方を向いてズームインし、高品質の没入型ビデオで表示できる段階まで進化しています。

ザイリンクスのブロードキャスト / コンシューマ マーケティング担当ディレクターである Ben Runyan によれば、テレプレゼンス テクノロジを開発している企業は、ユーザーのために没入型体験を作り出す方法を追求しています。「目標は、ユーザーが地球の裏側にいたとしても、同じ部屋にいるかのように感じさせることです。これを実現するには、最先端のカメラとディスプレイ テクノロジが必要になり、先進的な画像処理が要求されます。これらのテクノロジが高度化し、没入感が高まるにつれて、出張の必要性と費用が削減されるとともに、共同作業が容易になり、生産性が向上していきます。」

## ザイリンクス：SMARTER VISION のための ALL PROGRAMMABLE SOC

Smarter Vision があらゆる分野で急速に進展し、新しい市場を獲得するには、極めて柔軟な処理プラットフォーム、豊富なリソース、Smarter Vision 専用の実用可能なエコシステムが必要です。この 10 年間、ザイリンクスのデバイスは、各企業が Smarter Vision システムを創出する上で重要な役割を果たしてきました。現在ザイリンクスは、5 年の開発期間を経て、Smarter Vision アプリケーションの開発

者を支援し、次世代のイノベーションを加速するための包括的なソリューションを提供しています。

10 年以上の間、エンベデッド ビジョンの設計者は、ザイリンクス FPGA のプログラマビリティ、並列コンピューティング、高速 I/O 機能を多数のエンベデッド ビジョン システムに活用してきました。従来、設計者は、システムの メイン プロセッサの低速化の原因となる機能を FPGA を使用して高速化するか、またはプロセッサでは実行できない

ないレベルの統合です。インテリジェントなメイン プロセッサと FPGA ロジック間が基板速度で情報を送受信する代わりに、ワン チップ上のプロセッサとロジック間で 3,000 個の高性能接続点を通してシリコン速度で情報をやり取りできます。」

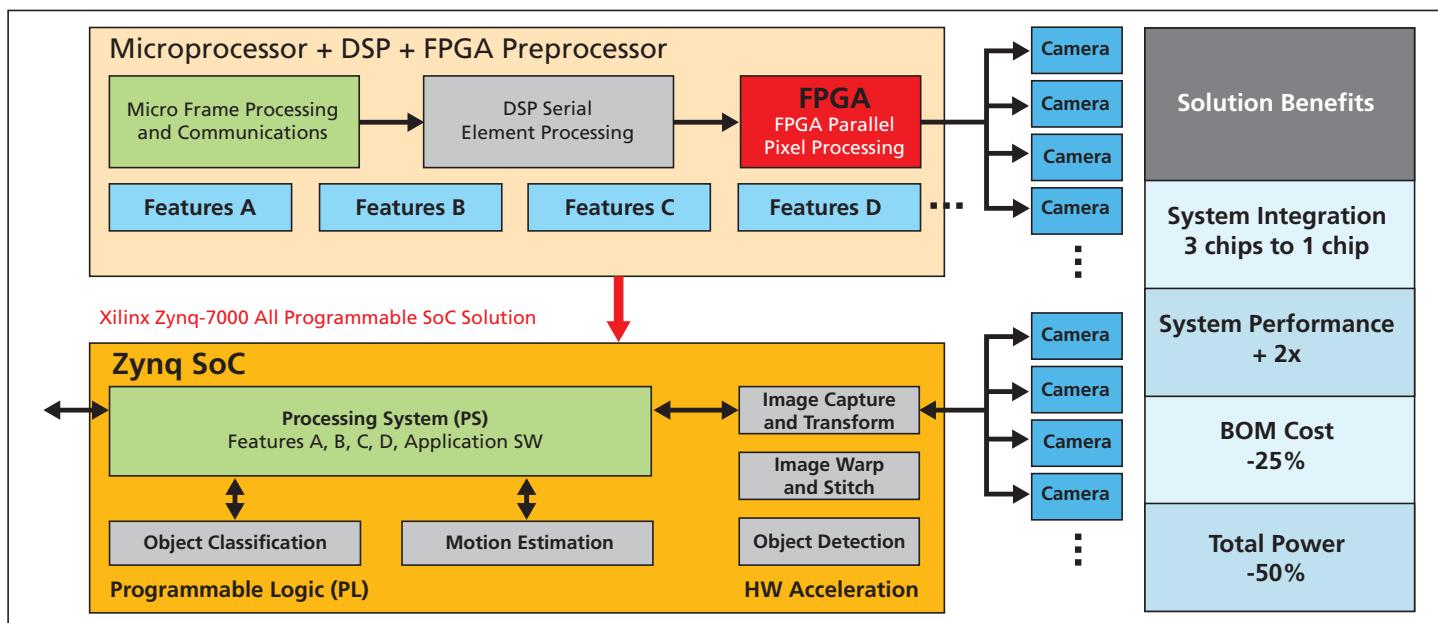

図 1 は、多機能運転支援システムを構築する上での、従来のマルチカメラ、マルチチップ アーキテクチャに対する Zynq-7000 All Programmable SoC のメリットを示しています。1 つの Zynq-7000 All Pro-

か、計算能力が不十分です。多くの場合、これらのデバイスに基づくソリューションには、これらの欠点を補うスタンドアロン FPGA を追加する必要があります。

## プログラマビリティと性能

Zynq-7000 All Programmable SoC のプログラマビリティと性能は、GPU および DSP 中心の SoC に対して大きなメリットがあります。ARM プロセッシング システムはソフトウェアでプログラマブル、

図 1 – 運転支援アプリケーションのマルチカメラ システムにおける Zynq All Programmable SoC とマルチチップの比較

並列コンピューティング タスクを FPGA で実行してきました。現在、Zynq-7000 All Programmable SoC により、エンベデッド ビジョンの開発者は、次世代の Smarter Vision アプリケーションの開発に最適でしかも、完全にプログラマブルなデバイスを手にしたと言えます。

ザイリンクスのビデオ テクノロジ担当エンジニアリング ディレクターである Jose Alvarez は、次のように述べています。

「Smarter Vision は、同じ基板上で互いに通信する個別のプロセッサと FPGA を使用してインプリメントできます。しかし、Zynq-7000 All Programmable SoC が提供するのは、電子機器業界ではこれまで

grammable SoC に接続された 複数のカメラを使用して、ザイリンクスのアーキテクチャ（図の左下）は、死角検出、360 度の周辺表示、車線逸脱警告、および歩行者検出などの機能群を実現できます。それに対して、既存の多機能運転支援システムでは、複数のチップと複数のカメラが必要になるため、統合の複雑化、性能の低下、システムの消費電力の増加、BOM コストの上昇を招きます。

ARM プロセッサと DSP または GPU を組み合わせた ASSP を提供するシリコンベンダーは数社ありますが、これらのデバイスは、現在の多くの Smarter Vision アプリケーションに使用するには柔軟性に乏しい

FPGA ロジックは HDL または C++ でプログラマブルであり、I/O も完全にプログラマブルです。その結果、顧客は特定のアプリケーションに適した極めて高性能な Smarter Vision システムを構築し、競合他社のシステムに対して差別化できます。

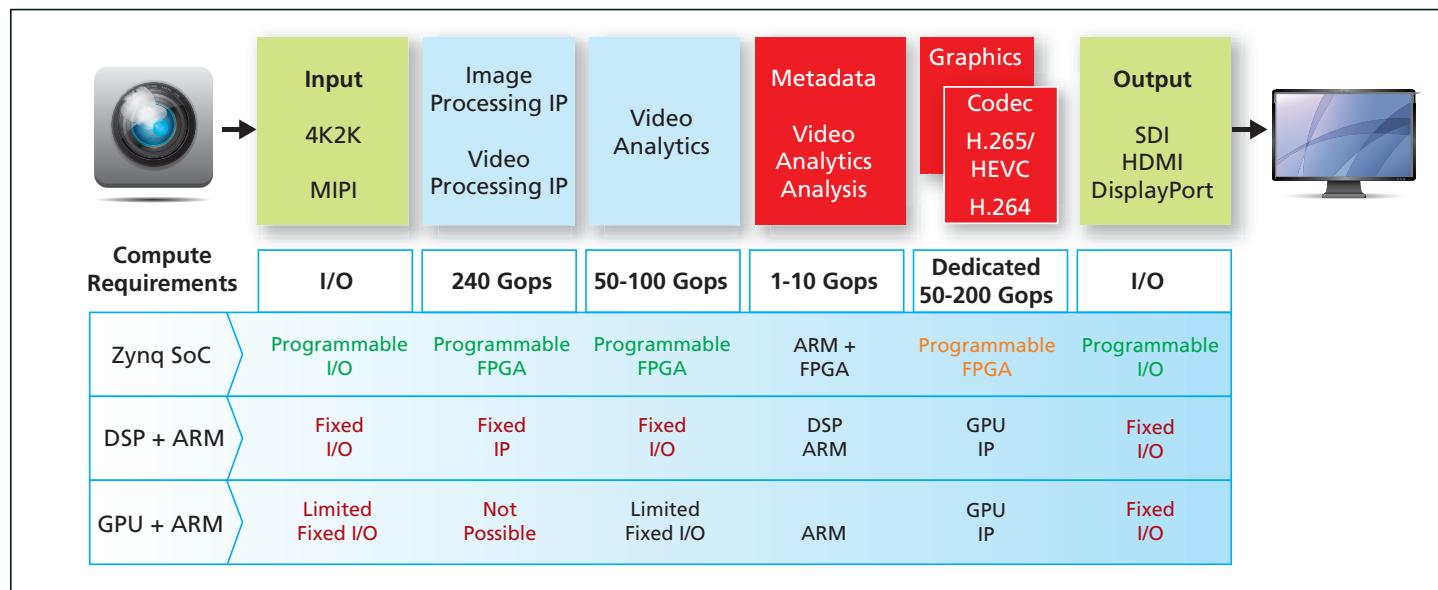

図 2 は、Smarter Vision システムの一一般的な信号フローの詳細と、ARM + DSP および ARM + GPU ベースの ASSP に対する Zynq-7000 All Programmable SoC の優位性を示しています。

フローの最初の信号処理ブロック（図の緑色の部分）は、デバイスをカメラ センサーに接続する入力です。Zynq-7000 All Programmable SoC では、開発者は幅広い

I/O 信号に適応可能で、顧客が要求するあらゆるカメラ接続に対応できます。次の信号処理ブロックは、アプリケーションが画像処理用か表示用かに応じて、ピクセル レベルの処理またはビデオ処理を行います。次のブロックではその画像の分析を行いますが、並列計算を必要とするこの演算量の多い処理は、多くの場合、FPGA ロジックでインプリメントするのが最適です。続く 3 つのブロック（赤い部分）では、プロセッsing システムが分析からメタデータ結果を取り出し、その結果のグラフィック表示を作成し（「Graphics」のステップ）、結果を転送用にエンコードします。

Zynq-7000 All Programmable SoC では、プロセッsing サブシステムと FPGA ロジックが協調して動作します。圧縮が必要な場合は、適切なコーデックを FPGA ロジックに簡単にインプリメントできます。次に、最後の信号処理ブロック（「Output」）では、開発者は、Zynq-7000 All Programmable SoC のプログラマブル I/O を使用して、IP プロトコルが独自規格に基づくものか、市場特有のものか、あるいは業界標準に基づくものかを問わず、多数の通信プロトコルとビデオ転送規格をターゲットにできます。それに対して、DSP 中心および GPU 中心の SoC のいずれにも、ASSP の DSP や GPU セクションでは実現できない性能を必要と

するアルゴリズムを開発できないリスクがあります。多くの場合、その欠点を補うためにスタンドアロン FPGA をシステムに追加する必要があります。

Zynq-7000 All Programmable SoC が Smarter Vision システムにとって最適な選択肢であることは明らかですが、ザイリンクスは、デバイス開発の初期段階から、特にビジョン アルゴリズムを C および C++ ベースで開発することに慣れた設計者のために、プログラミングを効率化する必要性を認識していました。この目的のために、2012 年 6 月、ザイリンクスは、Vivado Design Suite と呼ぶ最新のソフトウェア環境を発表しました。その中でも特長的なのは、2011 年 1 月の AutoESL 社買収によって獲得したクラス最高のハイレベル合成テクノロジです。Vivado HLS は、エンベデッド ビジョン アプリケーションに特に適しています。たとえば、Zynq-7000 All Programmable SoC を使用するビジョン開発者が C または C++ でアルゴリズムを作成したが、速度が不十分であるか、プロセッsing システムに負荷がかかりすぎる場合は、その C アルゴリズムを Vivado HLS に送り、それを Verilog または VHDL に合成して、デバイス上の FPGA ロジックで実行できます。これにより、Zynq-7000 All Programmable SoC 上のプロセッsing サブシステムを解放し、実行に適

したタスクだけを扱えるようにして、全体的なシステム性能を向上させることができます。

## OPENCV ライブラリ

OpenCV（コンピューター ビジョン）ライブラリの発表により、ザイリンクスの Smarter Vision テクノロジ製品のラインアップが完成しました。OpenCV は、エンベデッド ビジョン開発者がビジョンシステムを迅速に開発するときに使用する OpenCV.org からの業界標準のオープンソース ライブラリ アルゴリズムです。このオープンソース ライブラリには、世界中のエンベデッド ビジョン開発者から新しいアルゴリズムが活発に投稿されており、C、C++、Java、Python で作成された 2,500 種類を超えるアルゴリズムがあります（20 ページの OpenCV の記事を参照）。ライブラリに含まれるアルゴリズムの複雑さはさまざまであり、画像フィルターのような単純な機能から、動き検出などの高度な分析機能まで多岐にわたります。

Alvarez は、これらの OpenCV アルゴリズムは、ほぼすべての商用マイクロプロセッサおよび DSP へのインプリメンテーションをターゲットとしていると言っています。Zynq-7000 All Programmable SoC は ARM プロセッsing システムを使用しているため、C++ で作成されたこれらのアルゴ

図 2 - 一般的なビデオおよび画像処理システムのフロー

リズムをデバイスのプロセッサ部分にインプリメントできます。

Alvarezによれば、Vivado HLSを使用することで、ユーザーはCまたはC++で書かれたこれらのアルゴリズムを使用して、関数呼び出しをOpenCVからHLSに変更した後、Vivado HLSを使用してアルゴリズムを合成またはコンパイルし、Zynq-7000 All Programmable SoCのロジック部にインプリメントするに最適なRTLコードに変換できます。Vivado環境でOpenCVを使用するSmarter Vision設計者は、デザイン内のアルゴリズムがZynq-7000 All Programmable SoCのプロセッサ部とFPGAロジック部のどちらで最適に実行されるかを簡単に比較できます。ザイリンクスのオープンソースライブラリのリリースにより、ザイリンクスは、顧客が他社より一步先を行くことを可能にしました。既にザイリンクスは、Vivado HLSを使用して、30種類を超える最もよく使用されるエンベデッドビジョンアルゴリズムをOpenCVライブラリからコンパイルしています。顧客は、プロセッサ対ロジックのトレードオフをシステムレベルで迅速に検討し、Zynq-7000 All Programmable SoCで即座に実行して、各アプリケーションに最適なシステムを作成できます。

ザイリンクスとアライアンスメンバーは、OpenCVライブラリから多くの機能を積極的かつ継続的に移植し、年に4回のペースでザイリンクスのユーザーに公開しています。開発者はほぼすべての商用プロセッサ上でOpenCVライブラリを実行できるため、ビジョン設計者はさまざまなシリコンデバイス上で実行されるアルゴリズムの性能を比較でき、ベンチマークテストも実行できます。

Smarter Visionイニシアチブの一環として、ザイリンクスはSmartCORE IPと呼ばれる知的設計資産(IP)スイートも作成しました。このIPは、Smarter Visionを次世代の製品に組み込もうとする多くの市場分野で求められるSmarter Visionの要件に対応しています。ザイリンクスが新たに発表したIPインテグレーターツールを使用して、SmartCORE IPスイートからコアを、OpenCVライブラリからアルゴリズムを、デザインに簡単にインプリメン

トできます。この新しいツールは、ユーザーが希望に応じて回路図上またはコマンドライン環境で作業できる、最新のプラグアンドプレイIP環境です。

## ターゲット プラットフォーム 対応型のツール

Alvarezによれば、ザイリンクスは、各デバイスの機能をフルに活用できるように、最初からVivado Design Suiteをデバイス対応型のツールとして設計しました。IPインテグレーターにより、Vivado Design Suiteは、デバイス対応型であるだけでなく、すべてのZynq All Programmable SoCと7シリーズFPGAボードおよびキットをサポートするターゲットプラットフォーム対応型のツールになりました。ターゲットプラットフォーム対応型とは、Vivado Design Suiteがボード特有のデザインルールチェックを設定および適用し、作業システムの迅速な立ち上げを可能にするという意味です。

たとえば、ザイリンクスのZynq-7000 SoCビデオ/画像処理キットを選択して、IPインテグレーター内でZynq-7000 All Programmable SoCプロセッシングシステムのインスタンシエーションを行う場合、Vivado Design Suiteは、ボードに対応する適切な周辺機器、ドライバー、メモリマップでプロセッシングシステムを事前設定します。エンベデッド設計チームは、デュアルコアARMプロセッシングシステムと高性能FPGAロジックをターゲットとするソフトウェアIPとハードウェアIPの両方を、すばやく特定、再利用、統合できます。

ユーザーは、プロセッシングシステムとロジック間のインターフェイスを、一連のダイアログボックスで指定します。IPインテグレーターは自動的にRTLを生成し、性能または領域に合わせてコードを最適化します。ユーザーは、独自のロジックを追加するか、またはVivado IPカタログを利用して、デザインを完成します。

ザイリンクスのFPGAを使用して顧客がこれまでに作成したSmarter Visionシステムを見るのはこのうえない喜びです。Zynq-7000 All Programmable SoCとパワフルなSmarter Vision環境の登場は、次の製品がさらに素晴らしいものとなることをお約束します。

## GET ON TARGET

## パートナーの皆様 貴社の製品・サービスを Xcell journal誌上で PRしてみませんか?

Xcell Journalは

プログラマブルデジタルシステム開発者へ

ザイリンクスおよびエコシステム製品の最新情報を

はじめ、システム/アプリケーションの解説、

サービス/サポート情報、サードパーティー各社の

製品情報などを届けています。

現在では日本各地の10,000名を超える幅広い

分野のエンジニアの皆様に愛読いただいており

ザイリンクスのWebサイトから、無償でダウンロード

またはiPad対応デジタル版が購読できます。

貴社製品/ソリューションのプロモーションに

非常に効果的なメディアです。

広告掲載に関するお問い合わせ先

Xcell Journal日本語版への広告出向に関するお問い合わせは

E-mailにてご連絡下さい。

有限会社 エイ・シー・シー

sohyamaj@jcom.home.ne.jp

# Xilinx All Programmable Devices Enable Smarter Wireless Networks

## ザイリンクスの All Programmable デバイスで Smarter Wireless Network を実現

**Chris Dick**

Chief DSP Architect

Xilinx, Inc.

chrisd@xilinx.com

**モバイル IP の急増により、

将来の高性能ヘテロジニアス

ネットワーク アーキテクチャ構築の

柔軟なシリコンとデザイン ツールへの

ニーズが高まっています。**

無線通信事業者の喫緊の課題は、モバイル インターネット利用の爆発的な増加に対応する方法を見つけることです。ただし、単に高速な機器を多数導入するのではなく、よりスマートなネットワークの使用方法が求められています。各企業では自己組織型ネットワークなどの新しいアーキテクチャを積極的に導入して、優れた品質のサービスを顧客に提供し、収益力を最大限に高めようとしています。

ザイリンクスは、28 ナノメートル プロセス技術を採用した All Programmable デバイスと Smarter Wireless Network ソリューションに加えて、SmartCORE™ IP、Vivado™ Design Suite、サービスの専門知識などのサポート インフラストラクチャを用意し、ワイヤレス ネットワーク機器メーカーが他社に先駆けて新しいアーキテクチャの開発と製品化を進められるようにサポートしています。

**モバイル IP の爆発的な増加**

モバイル インターネット プロトコルの利用は、最近 4 年間で爆発的に増加しています。国際電気通信連合 (ITU) の ICT 統計によると、2000 年から 2010 年までの間に携帯電話契約数は 8 倍に増加し、同期間のインターネット ユーザー数の増加をはるかに超えるペースを示しています。このモビリティの優位性は、固定電話回線契約数の長期減少傾向と際立つ対照をなしています。2010 年の時点で、携帯電話契約数は固定電話回線契約数の 4 倍に達していました。スマートフォンとタブレットの登場により、仕事の進め方、余暇の過ごし方、家族や友人との交流の仕方は根本的に変わりました。

スマートフォンとタブレットが実現する機能やビジネス モデルと、インターネットにアクセスする際のアンカー ポイントとなる携帯電話網の間には、相互の成長を促す共生関係が成り立ちます。スマートフォンとタブレットの機能の高度化と共に、ユーザーはそれらの機能の新たな利用方法を考案し、そのためにネットワーク容量にストレスがかかります。そこで市場力学が作用し、ネットワーク事業者はネットワークのグレードアップで対応します。すると今度は、モバイル機器メーカーが新たなキャパシティを消費する新しいデバイスを発表するので、このサイクルはさらに続きます。アナリストの現時点の予測では、2020 年のネットワークは現在の 1,000 倍のキャパシティをサポートする必要がありそうです。

スマートフォンが主流に移行して以来、4 年間で画面のピクセル数は 163PPI (一平方インチ当たりのピクセル数) から 326PPI に倍増しました。同時に、ストレージ容量は 32GB から 64GB に倍増し、リア カメラの性能は 3 メガピクセル写真および VGA ビデオから 30 フレーム / 秒の 1024p HD ビデオをサポートする 8 メガピクセル カメラへと進化しました。モバイル機器メーカーは、現在ではフロント カメラと FaceTime などのアプリケーションを組み合わせて搭載するようになりました。これにより、モバイル ビジネス ビデオ会議が可能となり、モバイル ユーザーは、たとえば海外出張中でも自宅に接続したままいることができます。

2009 年から現在までの間に、驚くべきことに 6 世代にわたるスマートフォンが発売されました。初めて商用として成功したタブレットの発売以来わずか 3 年間で 5 世代のタブレットが発表され、画質は 2 年前の 720p ビデオから現在の標準的なリア カメラの 1024p HD ビデオへと進化しました。世界のスマートフォンの台数は 10 億台を超え、北米地域では人口の 2 分の 1 以上がスマートフォンを所有し、メディアリッチなコンテンツを高画質でダウンロードしたり、モバイル機器から画像とビデオのデータをクラウドにアップロードしたりしています。その結果、ネットワーク容量とレイテンシが問題となっています。世界のスマートフォンの台数が 10 億台に達するには 16 年かかりましたが、今後わずか 3 年で次の 10 億人のスマートフォン ユーザーが参加すると予想されます。キャパシティの問題は急速に深刻化しそうです。

新しいサービスやアプリケーションが次々と考案され、ますます高性能化するスマートフォンとタブレットがそれをサポートするすれば、それに応じてネットワークも進化する必要があります。より大きなキャパシティとカバレッジ、これまでにないレベルの体験の質、レイテンシの短縮を実現し、ビデオ会議やビデオ ストリーミングから、ローカル機器へのメディア コンテンツのダウンロードに至るまで、あらゆるモバイル体験を強化する必要があります。たとえば、長距離便に搭乗する前に、『Xcell Journal』や『IEEE Communications Magazine』の最新号、1 ~ 2 種類の新聞、その他の雑誌、オフィスからの技術レポート、または都合の良いときに後で視聴するためのビデオを何本かダウンロードすることが考えられます。オンライン ゲーム、インタラクティブ ゲームや金融取引の増加も、キャパシティとレイテンシへの需要を生み出しています。

Facebook などの先進の社会技術システムと、ますます高性能化するモバイル機器の組み合わせは、世界中の数十億人のユーザーにとって、日常生活の中心的な部分になりました。ソーシャル メディアのユーザーは、これまでにないほど積極的にモバイル アプリケーションを駆使しています。メディア エージェンシーの Ruder Finn 社による最近の調査では、ソーシャル コンピューティング アプリケーションを利用しているユーザーの

割合は、デスクトップ PC ユーザーで 79% に対して、モバイル回線加入者では 91% に達します。米国内のユーザーは、モバイル機器を 1 日平均 2.7 時間利用しており、45% がコメントを投稿し、43% が友人とつながり、40% が他人とコンテンツを共有し、38% がソーシャル ネットワーキング サイト上で写真を共有しているなど、モバイル機器は社会生活の基盤としてますます好まれています。

モバイル機器の利用の性質が変わったことの帰結として、現在、ワイヤレス ネットワーク上では音声トラフィックよりもはるかに大量のデータ トラフィックが発生しています。一部の業界レポートによれば、世界のモバイル データ量は今後数年間で約 40 倍に増加し、2009 年の毎月 90 ペタバイト (PB) から 2014 年には毎月 3.5 エクサバイト (EB) を超えると予想しています。

世界のスマートフォンの台数が 10 億台に達するには 16 年かかりましたが、今後わずか 3 年で次の 10 億人のスマートフォン ユーザーが参加すると予想されます。キャパシティの問題は急速に深刻化しそうです。

## 帯域幅の需要に応じた キャパシティの拡張

このような需要の増大、そして新しいモバイル アプリケーションとそれに関連するビジネス モデルの考案に対応して、ワイヤレス ネットワークの容量は飛躍的に改善されてきました。過去 30 年にわたり、ワイヤレス ネットワーク業界は、2G GSM システムの出現以来 10 年ごとにスループットを 10 倍に拡張し、1000 倍を超えるビットレートを達成しました。スマートフォンとタブレットの使用者の急増は、明らかに通信トラフィックの大幅な増加を招いており、この増加は 2020 年まで続くと予想されます。

19 世紀末の無線通信の発明以来、人類は、各種のメディアリッチ サービスを使用していくでも、どこでも、誰とでも通信できるテクノロジの開発に取り組んできました。しかし、モバイル ユーザー機器とワイヤレス および有線ネットワークそれ自体は大幅に進化していますが、接続の切断、キャパシティとカバレッジの問題、コンテンツのダウンロードの遅さ、端末のバッテリ持続時間の短さ、メディア体験の品質を低下させるネットワーク レイテンシなどの問題が山積し、

真のテレプレゼンス機能の提供にはまだ程遠い状況です。人対人の IP ネットワーク型の通信以外に、現在ではマシン ツー マシン (M2M) と呼ばれる新しいクラスのサービスが進化しており、ネットワーク性能への要求はさらに高まるでしょう。

## ネットワークの進化

3GPP などの標準規格団体、次世代ネットワーク モビリティ アライアンスなどの業界グループ、産業界と学究界の研究機関は、これらのさまざまな課題に対処するため、LTE (Long-Term Evolution) や EPC (Evolved Packet Core) などのモバイル ブロードバンド 4G テクノロジの定義と推進に取り組んできました。過去 4 年間に、2008 年後半には 3GPP Release 8 仕様 (OFDMA および SC-FDMA マルチキャリア テクノロジを利用した次世代の機能を定義する業界初の 3GPP 規格) が標準化され、2011 年には LTE-Advanced Release 10 仕様が承認されて LTE が初めて大きく進展するなど、大きな成果が上がりました。LTE および LTE-A システムはまだ導入途上ですが、Release 12 ワーク グループは LTE-B の要件とテクノロジの計画を進めています。

無線通信業界が直面している重要な課題の 1 つは、キャパシティの拡張です。通信技術の先駆者である Claude E. Shannon が Bell 研究所時代に発表し、大きな影響を与えた 1948 年の論文「通信の数学的理論」の有名なチャネル容量の公式によると、帯域幅の効率を改善するには、電力効率の低下という代償を払う必要があります。この法則は、キャパシティは帯域幅の 1 次関数であるとともに、S/N 比の対数関数でもあることを示しています。したがって、研究コミュニティは、各種規制要件への対応、周波数帯の割り当て、相互運用性、多重アクセス、信頼性、サービス品質、および帯域の柔軟性などを複雑な制約の範囲内で、ユーザー機器のレベルを考慮しつつ、帯域幅の効果的な利用方法の研究に取り組んできました。

これらの制約への対応は、LTE に採用されたマルチキャリア変調方式および EPC (Evolved Packet Core) の開発の動機付けとなり、現在では LTE-Advanced におけるキャリア アグリゲーション (CA) などの

機能開発の動機付けとなっています。しかし、キャパシティの問題を解決するには、チャネル帯域幅の拡張だけでは不十分です。

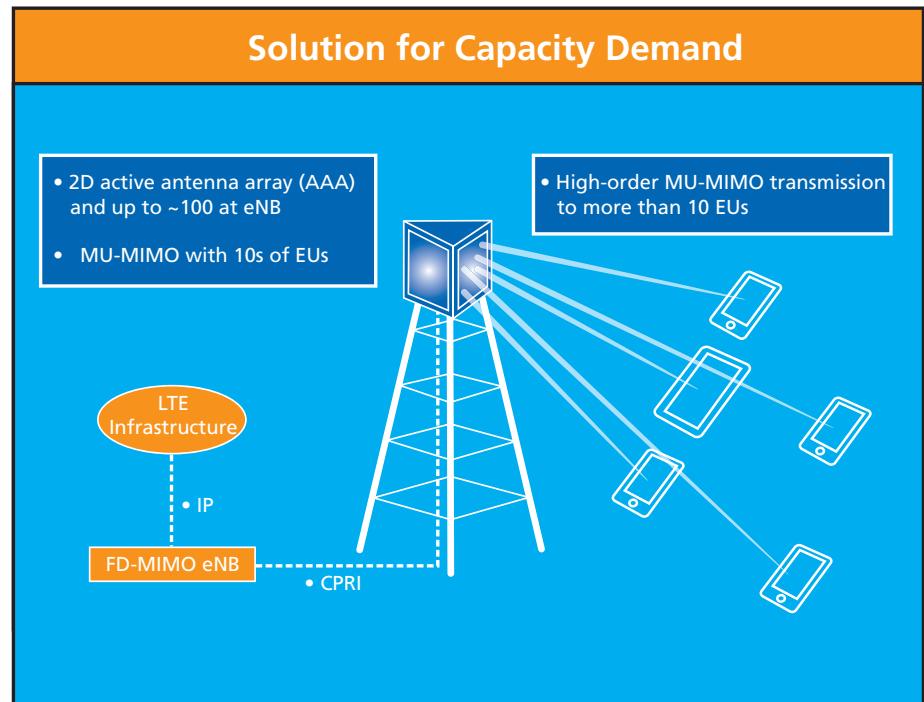

キャパシティのさらなる拡張は、空間分割多重 (SDM) MIMO の利用によって可能になりました。この方式では、対数関数に基づくキャパシティの公式とは対照的に、送信アンテナと受信アンテナの数が同じ場合、理論的にはアンテナ数に比例してキャパシティをリニアに増加させることができます。SDM が単一ユーザーのスループットを向上させるのに対して、空間分割多重アクセス (SDMA) 構成は、複数ユーザー間でシステム スループット全体を共有することで、1 つのセル内でサポートされるユーザー数を最大限に増やすことができます。MIMO トランシーバーと分散型または仮想 MIMO の組み合わせにより、電力効率に優れた「グリーン」ソリューションでキャパシティの問題に対応できます。LTE-B への移行と共に、3D MIMO (全次元 MIMO) は、3GPP 規格の将来のバージョンに採用され、マクロ基地局向け機器の OEM メーカーにも受け入れられるでしょう (図 1)。ネットワーク事業者は、ヘテロジニアス ネットワークとビームフォーミング スモール セル (垂直および水平電子ビーム チルトによってカバレッジ ホールに対処し、セル間干渉を最小限に抑える技術) を組み合わせて導入するでしょう。

しかし、キャリア アグリゲーションを先進のマルチアンテナ技術で増やすだけでは、まだ十分ではありません。空間分割多重方式が理論的に保証しているキャパシティの拡張を実際に実現することは簡単ではありません。実際には、精度の低いチャネル推定などによる実施劣化のために、理論上保証された利得が制限されます。

リレーとスマートセル アンダーレイによって増強されたマクロセルで構成されるヘテロジニアス ネットワークの導入は既に進んでおり、今後もますます速いペースで進むでしょう。ヘテロジニアス ネットワーク導入の目的には、高密度なビルの谷間の環境におけるキャパシティとカバレッジの問題への対応、建物内のカバレッジの向上、各種規制のためにマクロセルを設置できない環境での使用などが挙げられます。しかし、ヘテロジニアス ネットワーク (HetNets とも呼ばれる) とセルの稠密化は、バックホール、セ

図 1 - 産業界と学究界の研究コミュニティと 3GPP PHY ワーキング グループは、マッシブ (3D) MIMO を将来世代のセルラー アクセスに利用する可能性について分析しています。マッシブ MIMO は、数百本のアンテナを使用して、アンテナ システムを現在のシステムの 10 倍程度に拡張する技術です。

ル間干渉、セル間のハンドオーバーやキャリア グレードの WiFi 対応のハンドオーバーの管理など、さらなる課題をネットワーク設計者にもたらします。

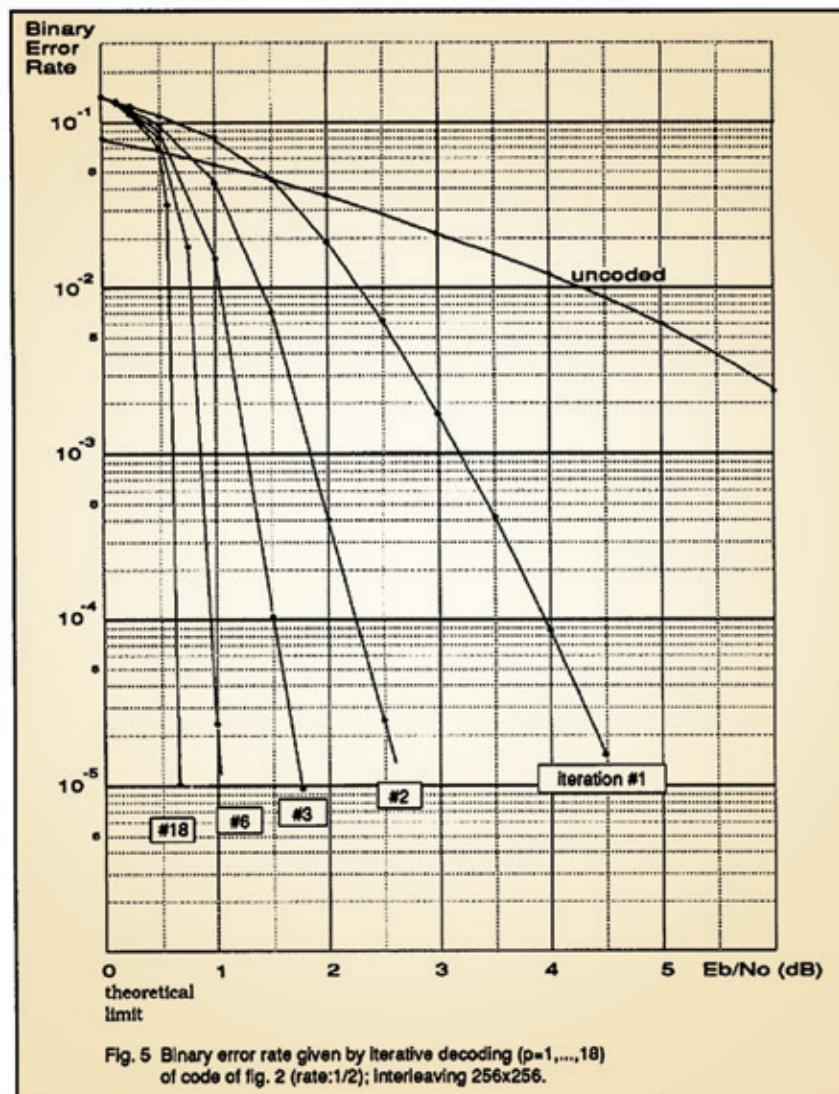

Shannon の先駆的な論文以来 60 年にわたる研究の結果として、先進の符号化方式 (たとえばターボ符号) と、マルチアンテナ技術、変調システム、通信プロトコル、デジタル IF 処理を組み合わせて、チャネル容量に限りなく近い容量で動作するシステムを実現できるようになりました。しかし、より大きなキャパシティ、より安定した通信、エンド ツー エンドのレイテンシ短縮への飽くなき要求に対処するには、まだ長い道のりが必要です。OFDMA (直交周波数分割多重アクセス) およびスマート アンテナ構成による、より柔軟で精緻な (またはスマートな) 周波数帯の利用に加えて、ハンドオーバーとネットワーク接続機器の耐障害性の維持をサポートする、拡張されたセル間干渉除去機能などの概念が生まれています。

自己組織型ネットワーク (SON) に関する豊富な概念は、LTE ロードマップ上で

は必須のテクノロジの 1 つです。SON は、隣接関係の自動推定 (Automatic Neighbor Relation)、負荷分散、トラフィックの増加とキャパシティの管理など、複数の要素で構成されます。自己最適化型自己障害回復 テクノロジの使用により、消費電力の削減、カバレッジの向上、LTE パラメーターの最適化 (たとえば、ランダム アクセス チャネル (RACH) の最適化) が約束されます。

SON のもう 1 つ重要な要素は、OPEX に関するドライブ テストの削減を最終目的としたネットワークのスマート化です。ネットワーク事業者は、自社のネットワークを改善するために、しばしば現場に技術者を配置して無線測定値を収集し、ネットワーク内のカバレッジ ホールなどの問題を発見したり、基地局またはネットワークのパラメーターの調整が必要かどうかを判断したりします。しかし、こうした従来のドライブ テストはコストがかかる上、収集される測定値は、ネットワーク全体の中で一度に 1 箇所の限られた情報しか与えません。次世代 モバイル通信網 (NGMN) および 3GPP

団体のメンバー企業は、この問題への対処について積極的に議論しています。3GPP Release 10仕様ではドライブ テストの最小化の概念が導入されました。この仕様は SON の分野に大きく貢献するもので、ネットワークへのノードの挿入が簡単に行えるようになり、ノードとネットワークの全存続期間にわたるパラメーターの自動調整が可能となります。

ネットワーク デザインにおけるもう 1 つの考慮事項は、運用コストの問題です。OPEX の（また実際には CAPEX の）重要な要因の 1 つは、パワー アンプまたはマルチアンテナ システム用アンプを内蔵した RF プラットフォームです。RF エレクトロニクスの「グリーン」対応は多面的な手法で構成されます。コストの面から見ると非線形パワー アンプの導入が望ましいのですが、LTE RAN ダウンリンクに使用される 非定常包絡線変調方式の一つ OFDMA は、低コストの非線形アンプで処理した場合、スペクトルの再成長という望ましくない結果をもたらします。これは隣接スペクトル帯域に影響を与える非常に好ましくない帯域外スペクトル放射であり、近隣の通信システムへの電磁妨害をもたらし、各種規制要件への違反を招きます。

1 つの解決策は、大きなバックオフを使用し、アンプの伝達関数の線形部分のみを適用することです。しかし、パワー アンプの効率や DC 電力を RF 搬送波に変換するアンプの実効性も重視する必要があります。アンプの効率が最も高まるバイアス ポイント、すなわち小さな出力バックオフでアンプを動作させることをお勧めします。ただし、アンプのバイアス調整によってバックオフを最小限に抑えると、伝達関数の圧縮部分の近くに移動するため、マルチキャリア信号の問題が発生します。LTE OFDMA ダウンリンク波形は、サンプリングされた直交正弦波の加重和として形成されます。この加重和によって形成される信号は、大きなピーク対平均電力比を示します。時系列の実数部と虚数部の振幅は、レイリー分布の包絡線を持つガウス分布になる傾向があります。

レイリー分布包絡線は大きなピーク対平均比を示し、0.00035 の確率でピーク値が平均値の 4 倍を超える。OFDMA 時系列の忠実度を維持し、パワー アンプのクリッピングによって発生する帯域外スペクト

図 2 - 1993 年の有名な論文で Berrou らが初めて発表した、畳み込みターボ符号のウォーターフォール グラフ。ターボ符号は、3G および 4G ワイヤレス システムに使用される符号化体系を刷新しました。

ルを避けるために、平均信号のレベルがフルスケールの 4 分の 1 になるようにアンプを動作させることができます。しかし、4:1 のピーク対平均比の信号をパワー アンプを通過させると、犠牲になる効率が必要以上に大きくなります。ピーク電力レベルは平均電力レベルの 16 倍になります。つまり、5W の平均電力を供給する必要があるアンプは、80W のピーク電力を供給できなければなりません。

パワー アンプがピーク電力レベルのほんのわずか（この場合 1/16）で動作していると、DC 電力から信号電力への変換プロセスが非常に非効率になります。クラス B ア

ンプの場合、おおよその計算では、広範囲にわたる出力電力レベルにわたって、電源から引き出される電力は一定であり、ピーク電力レベルの約 35% です。したがって、この 80W アンプは、DC 電源から 28W を引き出し、その電力のうち 23W をアンプのヒートシンクに捨てながら、外部負荷に 5W を供給することになります。

デジタル信号処理は、これらの難題の解決策を提供します。1,540 個の乗算アキュムレータを搭載し、491.52MHz で動作するザイリンクスの 28nm Kintex™-7 410T などのミッドレンジ All Programmable デバイスは、1 秒当たり 7570 億 MAC の

ピーク演算性能を発揮します。この値は、1980 年代初頭に発表された第 1 世代ハーバード アーキテクチャを採用した統合型 DSP プロセッサの 30 万倍に相当します。各メーカーは、この DSP の処理能力を使用して高度なクレスト ファクター低減機能をインプリメントし、伝送波形のピーク対平均比を制御すると共に、デジタル ブリディストーション処理を適用し、非線形性の高い低成本のドハイティ パワー アンプを線形化しています。この方法により、設計者は、忠実度の高い RF 処理と增幅機能の作成に関連する高コストの一部を、比較的低成本のデジタル信号処理デバイスに負担させることで、機器の全体的コストを管理しています。デジタル信号処理デバイスは、RF デバイスとは異なり、ムーアの法則に基づくプロセス ノード スケーリングの恩恵を受けてきました。

## ザイリンクスと次世代の SMARTER NETWORK

キャパシティ、レイテンシ、カバレッジ、サービス品質、OPEX および CAPEX の問題解決手法は、各モバイル ネットワーク事業者およびセルラー インフラストラクチャ メーカーごとに異なります。各社独自のソリューションは、既存の資産、専門知識、市場化戦略に応じて変化します。単一の SoC を使用した単一のハードウェア プラットフォームでは、各 OEM メーカーは自社の製品を差別化できません。また、スマートセルからマクロセル、さらにクラウド RAN ネットワーク アーキテクチャへとテクノロジを拡張できる、統一的な共通のプラットフォーム手法を手に入れることもできません。

OEM メーカーは多様なアーキテクチャをサポートする必要がありますが、従来の商用シリコン SoC では対応できません。これらのアーキテクチャには、従来の基地局から、レディオ ヘッドにベースバンド部を統合したアーキテクチャ、あるいはクラウドを利用した「ベースバンド ホテル」モデルをサポートするリモート レディオ ヘッド アーキテクチャまであります。特定の OEM メーカー 1 社に限っても、ネットワークを導入する地域によって、市場化とテクノロジの考慮事項は異なります。その上、現在は、製品の Time-to-Market によって企業がどの程度

成功するかが決まる傾向がこれまでにないほど強まっています。したがって、ワイヤレス ネットワークを特徴付ける複雑な特性に適合する、豊富なエンベデッド ソフトウェア、演算性能、接続性の組み合わせを備えた、柔軟性と拡張性に優れたテクノロジを選択することが重要です。シリコン プラットフォームだけにとどまらず、デザイン ツールと知的設計資産 (IP) コア ライブライアリも、生産性の向上に重要な役割を果たします。

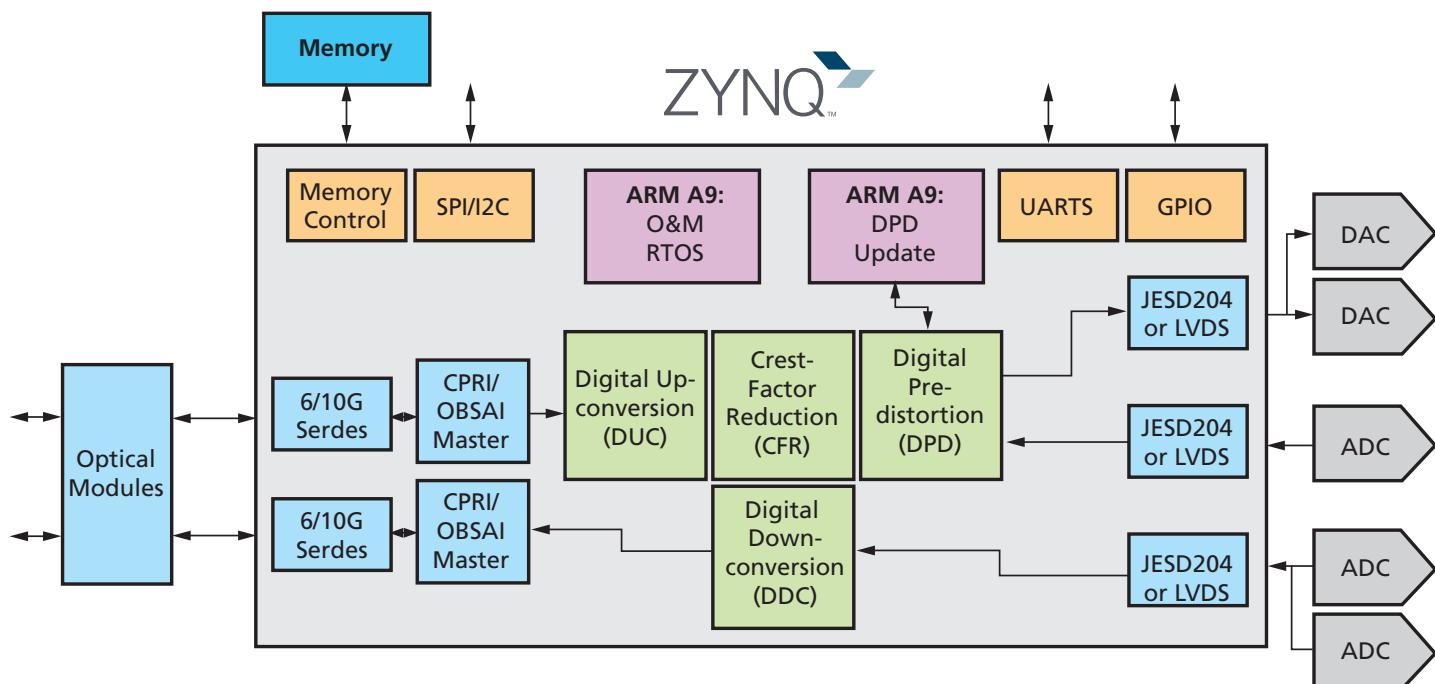

ザイリンクスの 28nm 7 シリーズ テクノロジ、特に All Programmable Zynq SoC は、次世代ネットワークの新基準の中心となる接続性、信号処理、エンベデッド コンピューティング 機能を提供します。FPGA コンピューティング ファブリックとその比類なき信号処理機能を OFDMA および SCFDMA LTE ベースバンド処理に適用すれば、反復的手法を用いてマルチアンテナシステム内のチャネル デコーダー、イコライザー、MIMO ディテクタの間で統計情報をやり取りする、先進のレシーバーの高速数値演算の要件を実現できます。同様に、Zynq All Programmable SoC は、キャパシティの拡張と ITU が IMT-Advanced 規格の一部として定義した最小限の要件を超えるための 1 つの選択肢として 3D MIMO を利用する、将来世代のシステムをサポートします。

FPGA 信号処理のそのほかの応用分野として、コスト削減、CAPEX および OPEX、そしていわゆるネットワークの「グリーン」対応が挙げられます。LTE-A とキャリア アグリゲーションにより、チャネル帯域幅は 100MHz に移行しました。クレスト ファクターの低減 (CFR) とパワー アンプの線形化の手法を進化させて、これらの広帯域チャネルを扱えるようにする必要がありますが、それは信号処理の負担が増すことを意味します。ザイリンクスの通信ビジネスユニットは、数年にわたってこの問題に取り組み、広範囲にわたる無線インターフェイスプロトコルを処理する CFR とデジタル ブリディストーション IP コアを開発しました。

将来を展望すると、ますます多岐にわたるキャリア構成をサポートする必要が増すにつれて、無線処理がさらに複雑化していくことは明らかです。LTE 仕様は、わずか 4 年弱の間に、6 チャネル帯域 (1.4, 3, 5, 10, 15、および 20MHz) の基本セットか

ら、イントラバンド構成およびインターバンド構成に搬送波成分を集約できる Release 10 まで進化しました。LTE 仕様は現在 Release 12 の策定作業に入っています、さらなるスペクトル帯域の柔軟性を実現するためのソリューションの調査に着手したところです。

もちろん、マクロセルであれスマートセルであれ、すべての基地局がすべての可能なシナリオをサポートする必要があるわけではありません。この事実があることから、各 OEM メーカーは、ネットワーク事業者の周波数プランニングの要件を判別して取り込むために、費用対効果の高い一連のソリューションを迅速に構築する必要性のジレンマに直面しています。これらの要件は、周波数帯の割り当て、周波数帯の断片化、単一の RF チェーンから複数の無線アクセス テクノロジをサポートする必要性 (マルチ RAT の問題) などの変数に基づく複雑な方程式です。さらに、マクロ基地局、スマートセル アンダーレイ、WiFi オフロードの組み合わせで構成されるヘテロジニアス ネットワークの導入が、この構図をさらに複雑にしています。これは規模と柔軟性の問題であり、この 2 つの特性はザイリンクスの All Programmable SoC と FPGA の核心にあります。

この問題は、PHY 内での信号処理だけにとどまりません。LTE と将来の LTE-A および LTE-B ネットワークは多くの面でよりスマートになっており、それは特に、自己組織化ネットワーク アプリケーションの実行とドライブ テストの最小化、LTE パラメーターの最適化の実行、リアルタイムのパフォーマンス管理のインプリメント、ネットワークおよび機器のプランニング目的での統計情報の収集などから、プロトコル スタックと O&M (運用管理) ソフトウェアの実行に至るまで、あらゆる面でソフトウェアの重要性が増しているからです。

ザイリンクスは、2012 年の Zynq All Programmable SoC の発表により、デュアル Cortex™ A9 プロセッサと高性能プログラマブル ロジック ファブリックを緊密に結合した業界初のコンピューティング パラダイムをシステム設計者に提供し、信号処理、MAC レイヤーの高速化、イーサネット、CPRI、OBSAI 接続などの用途に使用できるようにしました。これらのデバイス

(および製品ラインに含まれるその他の製品)は、各 OEM メーカーが差別化された製品を開発し、高い費用対効果で迅速に市場に提供するのに必要な、コンピューティング要件、ISA とデータバス、拡張性と柔軟性のさまざまな組み合わせをただちに提供します。

この新たな時代には、バックホールも問題になります。無線アクセス ネットワークの機能が進化するにつれて、ネットワークのバックホールの要件は劇的に高度化します。さまざまなセル構造と導入シナリオは、一

前の問題の正確なニーズに基づいてリンクキャパシティをスケールアップまたはスケールダウンできる柔軟性を備えた、さらに一歩先を行くバックホール テクノロジを提供できるようになりました。たとえば、一部のハイエンドなシナリオでは、電磁波の垂直偏波と水平偏波の両方にデュアルモード伝送を使用して、リンクのキャパシティまたは信頼性向上させることが可能ですが、それ以外の状況では、よりデータレートの低い、簡単な低コストの単一偏波方式で十分でしょう。ソフトモジュム IP コアをチップに統

トコルなど、ネットワーク デザインのすべての要素をワンチップで実現します(図 3)。

先頃ザイリンクスは、先進のシリコンおよび IP コア ソリューションと共に、新世代のデザイン ツールを発表しました。

2012 年の Vivado HLS 高位合成テクノロジの発表は、この分野にエキサイティングな進化をもたらしました。このフローにより、顧客は、C、C++、または SystemC を使用して作成したプログラムをザイリンクスのシリコン向けにコンパイルできます。この機能で高級言語から FPGA をプログラム

図 3 – Zynq All Programmable SoC により、アップコンバージョンとダウンコンバージョン、クレスト ファクターの低減、デジタル プリディストーション、接続機能を統合したデジタル IF 処理チェーンをワンチップで構築できます。

部のスマート セル基地局向けのイーサネットと光ファイバーから、その他の構成でのポイント間マイクロ波リンクと e-band ミリメートル波リンクまで、多様なバックホール テクノロジを利用します。この分野で、ザイリンクスが OEM メーカーを支援する一つの方法に、バックホール用モジュム IP の提供があります。

先頃ザイリンクスは、バックホール分野の専門知識を持つ企業を買収し、現在の ASSP シリコンに匹敵するだけでなく、目

合し、1+1、2+0 など、あらゆる一般的な構成を高い柔軟性で実現できるため、顧客はソリューションの性能とコストを段階的に向上させることができます。

Zynq All Programmable SoC は、ARM Cortex-A9 プロセッサ上で動作するソフトウェア、コンピューティング ファブリックと積和演算エンジンの大量並列処理アレイ内にインプリメントされる RAN 物理層の機能とバックホール モジュム、高速 SERDES を使用して構築される接続プロ

すれば、生産性が向上し、ハードウェア記述言語に不慣れな設計者も All Programmable デバイスを利用できます。新しい Vivado フィジカル インプリメンテーション ツールは、完成品の品質、実行時間、使いやすさを向上させます。

ザイリンクスの製品がどのように顧客の Smarter Network の構築に役立っているかの詳細は、<http://japan.xilinx.com/applications/smarter-networks/index.htm> を参照してください。

All Programmable FPGA および SoC、3D IC の世界的なリーディング プロバイダーの

ザイリンクスが提供するプログラマブル ロジックからプログラマブル システム

インテグレーションのさまざまな機能と活用方法をご紹介します。

コストを抑え、最大のパフォーマンスを実現するための最新情報を手に入れてください。

ニーズに合わせたプログラムを各種取り揃えて好評配信中!!

## New!! 新セミナー登場

システムレベル セキュリティの強化:

All Programmable SoC で OS を超える

### FPGA入門編

FPGA をこれから始める方に FPGA の全体概要を解説した入門編と、ものづくりにチャレンジする経営者、技術管理者の方へなぜ今 FPGA / CPLD なのかをご説明します。

▶ 30分で判る! FPGA入門

▶ 15分で判る! FPGA採用理由

### FPGA活用編

ザイリンクス FPGA を使った最先端デザインの設計手法や、さまざまなアプリケーション設計に求められる

デザイン チャレンジに対するソリューションをご紹介・解説します。

- ▶ システムレベル セキュリティの強化: All Programmable SoC で OS を超える

- ▶ Zynq-7000 All Programmable SoC での C コードからコプロセッシング アクセラレーター

- ▶ ザイリンクス シリアル デザイン ソリューション

### 開発ツール編

プログラマブルデバイスである FPGA の設計には開発ツールがキーになります。ザイリンクスが提供する

ユーザー フレンドリーな開発ツールの特徴や使い方、先端設計メソドロジについて解説します。

- ▶ 次世代FPGA設計手法セミナー PlanAhead デザイン解析ツール

～ 第1部、第2部、第3部、デモ～

- ▶ AMBA AXI4 テクニカルセミナー

- ▶ 製品の差別化を実現する開発ツール: ISE Design Suite

### FPGA/SoC 概要編

FPGA の世界トップシェアを誇るザイリンクスが提案するソリューションや、ザイリンクスの最先端 FPGA の

詳細を解説します。

- ▶ Zynq-7000 EPP アーキテクチャとエコシステム

- ▶ エクステンシブル プロセッシング プラットフォーム Zynq-7000 ファミリのご紹介

- ▶ 28nm ザイリンクス 7 シリーズ FPGA のアジャイル ミックスド シグナル テクノロジ

# Using OpenCV and Vivado HLS to Accelerate Embedded Vision Applications in the Zynq SoC

## OpenCV と Vivado HLS を使用して、 Zynq SoC のエンベデッド ビジョン アプリケーションを高速化

**Fernando Martinez Vallina**

HLS Design Methodology Engineer

Xilinx, Inc.

*Vallina@xilinx.com*

**José Roberto Alvarez**

Engineering Director

for Video Technology

Xilinx, Inc.

*jalvarez@xilinx.com*

## Vivado HLS と OpenCV ライブラリを組み合わせて、Zynq SoC をターゲットとする Smarter Vision システムの迅速なプロトタイピングと開発が可能です。

コンピューター ビジョンは、学究界では以前から確立されている分野であり、現在の多くのビジョン アルゴリズムは数十年にわたる研究に由来するものです。しかし、私たちの生活の多くの場面にコンピューター ビジョンが普及したのはつい最近のことです。現在、自動運転車、ユーザーの動作に反応するゲーム機、身振りに応答する自律型掃除機や携帯電話など、多彩なビジョン 製品が登場しています。

現在の課題は、消費電力と Time-to-Market 短縮の厳しい制約を受けながら、どのように現在および将来のビジョン システムを効率的にインプリメントするかということです。Zynq™ All Programmable SoC は、広く利用されているコンピューター ビジョン ライブラリの OpenCV と、ハードウェア上で重要な機能を高速化する高位合成 (HLS) ツールを組み合わせることで、このようなビジョン 製品の基盤として使用できます。Zynq All Programmable SoC、OpenCV、HLS ツールの組み合わせは、Smarter Vision システムを設計しインプリメントするための強力なプラットフォームを提供します。

エンベデッド システムは、現在では市場で広く利用されています。しかし従来、計算処理能力の制限により、特に大きなサイズの画像や高いフレームレートを処理する必要がある場合、コンピューター / マシン ビジョン 向けの実用的な用途は限られていました。エンベデッド デバイスの目を外の世界に開き、コンピューター ビジョン アルゴリズムを使用して周囲の環境との相互作用

を可能にするには、イメージ センサー テクノロジの進化が不可欠でした。エンベデッド ビジョンは、エンベデッド システムとコンピューター / マシン ビジョンの組み合わせによって構成されます。この分野は、周囲の環境を知覚し理解するマシンの設計基盤へと急速に成長しています。

### エンベデッド ビジョン システムの開発

エンベデッド ビジョンを実現するには、コンピューティング プラットフォーム上でインテリジェント コンピューター ビジョンのアルゴリズムを動作させる必要があります。多くのユーザーにとって、標準的なデスクトップ コンピューターは、便利で利用しやすいターゲット プラットフォームです。しかし、60 フレーム / 秒のリアルタイム HD ビデオ のマルチストリームのように大きな画像データ セットを処理する場合、コンパクトで効率的な省電力型のエンベデッド 製品を開発するには、汎用コンピューティング プラットフォームでは不十分なことがあります。

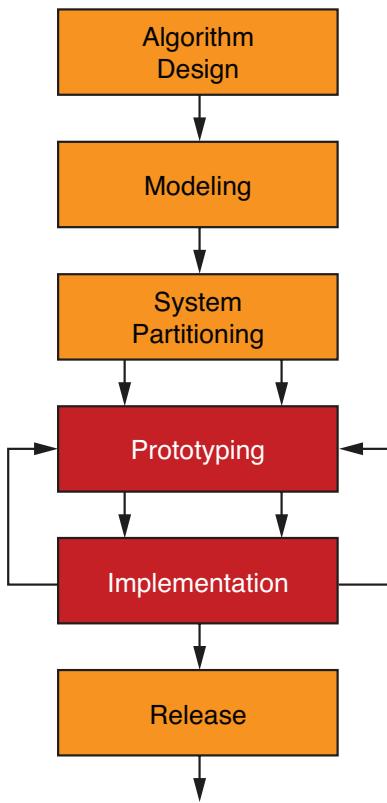

図 1 に、エンベデッド ビジョン アプリケーションを開発する際の一般的な設計フローを示します。特定のコンピューター ビジョン タスクの処理と品質の基準を満たすかどうかはアルゴリズムによって決まるため、このプロセスではアルゴリズムのデザインが最も重要です。最初に、高度な処理オプションを実現するために、MATLAB® などの数値演算コンピューティング 環境内でアルゴリズムの選択肢を検討します。適切なアルゴリズムが決まつたら、アルゴリズムの高速実行

78977348759834759843

87984654546546

7987465465465132132131

6258795836458734657

665387875684653400

図 1 - エンベデッド ビジョン システムの開発プロセス

とビット アキュレートな最終インプリメンテーションを順守するために、通常は高級言語（一般的には C/C++）でアルゴリズムをモデル化します。

システム パーティショニングは、開発プロセスにおける重要な手順です。この手順では、アルゴリズムのパフォーマンス解析を通じて、代表的な入力データ セットのリアルタイム処理の要件に基づいて、アルゴリズムのどの部分をハードウェア内で高速化する必要があるかを判断できます。また、現実的なパフォーマンス期待値の測定を行うために、ターゲット プラットフォーム内でシステム全体をプロトタイピングする手順も重要です。プロトタイピング プロセスにより、デザインがパフォーマンスと品質のすべての目標を満たしていることを確認できたら、実際のターゲット デバイスに最終システムのインプリメンテーションを開始できます。最後の手順は、チップ上で動作するデザインを、すべてのユースケース シナリオ

でテストすることです。すべてのチェックが完了したら、最終製品をリリースできます。

### ZYNQ SOC : エンベデッド ビジョンのための 最もスマートな選択肢

マシン ビジョン アプリケーションの開発では、柔軟性の高いデバイスを選択することが非常に重要です。コンピューティング プラットフォームは、幅広いソフトウェア エコシステムをサポートする強力な汎用処理能力と、大量の演算を必要とするメモリ効率の高いコンピューター ビジョン アルゴリズムをインプリメントするための堅牢なデジタル信号処理機能の装備が必要です。効率的で完全なシステムをインプリメンテーションするには、シリコン レベルでの緊密な統合が必要不可欠です。

ザイリンクス® All Programmable SoC は、ソフトウェア、ハードウェア、および I/O のプログラマビリティをワンチップで提供するプロセッサ中心型デバイスです。Zynq All Programmable SoC は、ARM 社のデュアルコア Cortex™-A9 MPCore™ プロセッシング システムと FPGA ロジックおよび主要なペリフェラルを組み合わせてワンチップで提供します。したがって、このデバイスを使用すれば、極めて効率的にエンベデッド ビジョン システムのインプリメンテーションができます。

Zynq All Programmable SoC は、プロセッシング サブシステム、FPGA ロジック、ペリフェラルの高度な統合により、個別のコンポーネントを使用して設計されたシステムに比べてデータ転送が高速化され、消費電力と BOM (部品) コストもはるかに少なくて済みます。Zynq All Programmable SoC には、数百 GOPS (Giga Operations Per Second) の処理能力による 1080p 60 ビデオ シーケンス (60 フレーム / 秒の 1,920x1,080 RGB 画像) のリアルタイム処理を必要とするシステムをインプリメンテーションすることができます。

Zynq All Programmable SoC の多くの機能をフルに利用できるように、ザイリンクスは Vivado™ Design Suite を提供しています。Vivado Design Suite は、よりスマートなエンベデッド製品のダイナミックな開発に必要とされるインテグレーションとインプリメンテーションの高速サイクルに

よって設計者の開発生産性を向上させる、IP コアおよびシステム中心型のデザイン環境です。Vivado Design Suite のコンポーネントである Vivado HLS を使用して、C/C++ で開発したアルゴリズムを RTL にコンパイルし、FPGA ロジック内で実行できます。

Vivado HLS ツールは、特にエンベデッド ビジョンのデザインに最適です。このフレームでは、まず C/C++ でアルゴリズムを作成し、次に Vivado HLS を使用してこのアルゴリズムまたはその一部を RTL にコンパイルし、FPGA ロジックでの実行に適した関数と ARM プロセッサでの実行に適した関数を決定します。このようにして、Zynq All Programmable SoC 上で動作するビジョン システムの最適なパフォーマンスに到達できます。

ザイリンクスは、エンベデッド ビジョン開発者向けに Smarter Vision システムの作成をさらに支援できるよう、コンピューター ビジョン アルゴリズムの OpenCV ライブライアリのサポートを Vivado に追加しました。またザイリンクスは、これらのデザインをサポートする新しい IP インテグレーター ツールと SmartCORE™ IP を発表しました (4 ページのカバー ストーリーを参照)。

### OPENCV によるコンピューター ビジョン開発の促進

OpenCV は、リアルタイム パフォーマンスを重視したインテリジェント コンピューター ビジョン アルゴリズムの簡単な開発手法を提供します。OpenCV ライブライアリにより、設計者は、アルゴリズムの実験と迅速なプロトタイピングに最適な環境を手に入れられます。

OpenCV のデザイン フレームワークは複数のプラットフォームでサポートされます。しかし多くの場合、エンベデッド製品向けに OpenCV ライブライアリの効率を高めるには、高いリアルタイム パフォーマンスが要求されるルーチンの高速化が可能なエンベデッド プラットフォームにアルゴリズムをインプリメンテーションする必要があります。

OpenCV は演算効率を重視して設計されていますが、本来はマルチコア プロセッシングをサポートする従来のコンピューティング環境で開発されたものです。これらのコンピューティング プラットフォームは、効率、

コスト、消費電力の要件が極めて厳しいエンベデッド アプリケーションに最適であるとは限りません。

## OPENCV の特長

OpenCV は、BSD ライセンスの下でリースされるオープン ソースのコンピューター ビジョン ライブラリです。つまり、OpenCV は学術および商用アプリケーションに無償で使用できます。OpenCV は、本来は汎用マルチプロセッシング システムの演算効率の向上を目的として、リアルタイム アプリケーションに焦点を合わせて設計されたライブラリです。さらに、OpenCV は、C/C++ や Python などの複数のプログラミング インターフェイスへのアクセスを提供しています。

オープン ソース プロジェクトの利点は、ユーザー コミュニティが継続的にアルゴリズムを改善し、広範囲にわたる応用分野で使用できるように拡張を続けていることです。OpenCV には現在、次のような 2,500 種類以上の関数がインプリメントされています。

- マトリックス数値演算

- ユーティリティおよびデータ構造

- 一般的な画像処理関数

- 画像変換

- 画像ピラミッド

- ジオメトリ（幾何学的）記述子関数

- フィーチャ認識、抽出、追跡

- 画像セグメンテーションおよび フィッティング

- カメラ キャリブレーション、ステレオ および 3D 処理

- 機械学習：検出、認識

OpenCV の詳細は、[opencv.org](http://opencv.org) および [opencv.willowgarage.com](http://opencv.willowgarage.com) を参照してください。

## HLS による OPENCV 関数の高速化

エンベデッド ビジョン システムのアーキテクチャを分割し、大量の演算が必要な部分を特定したら、HLS ツールを使用して、C++ で記述された状態のままでこれらの関数を高速化できます。Vivado HLS は、C、C++、または SystemC コードを使用して、

効率的な RTL インプリメンテーションを生成します。

さらに、IP 中心型の Vivado デザイン環境は、イメージ センサー、ネットワークおよびその他の必要な I/O インターフェイスへの接続を簡素化し、これらの OpenCV ライブラリ関数を簡単にインプリメントできるようにする、各種のプロセッシング IP SmartCORE を提供します。OpenCV の最も基本的な I/O 機能までも高速化する必要がある場合、これはほかの代替手段に対する Vivado 環境の大きなメリットになります。

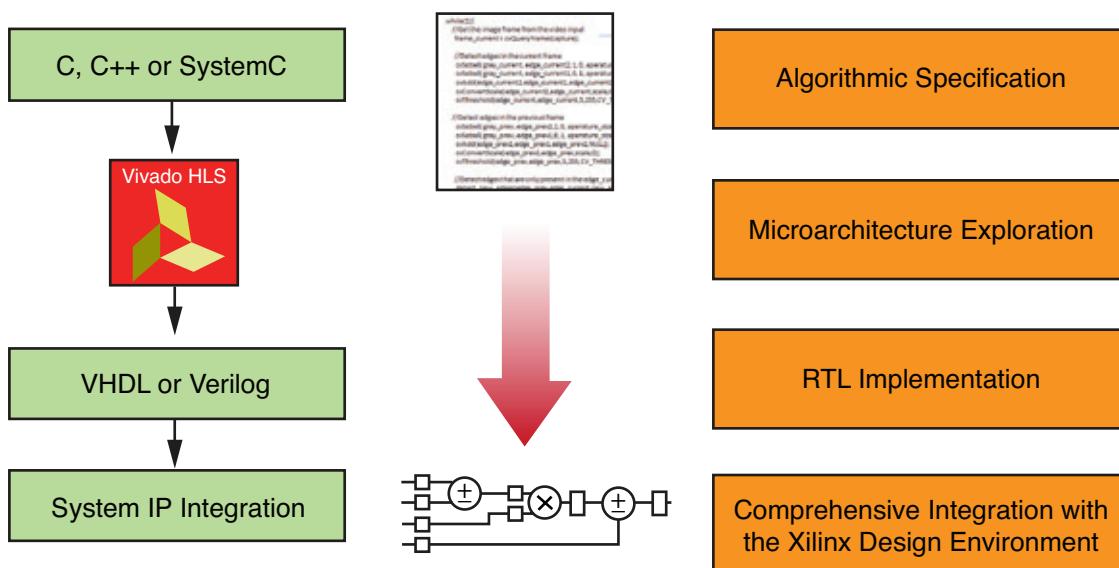

## 高位合成のメリットとは

ザイリンクスの Vivado HLS コンパイラは、C、C++、または SystemC でインプリメントされたアルゴリズムを、ユーザーが定義したクロック周波数とザイリンクスの製品ラインのデバイス向けに最適化された RTL に変換するソフトウェア コンパイラです。Vivado HLS は、C/C++ プログラムの解釈、解析、最適化について、x86 プロセッサ向けコンパイラと同じ基本的なテクノロジ基盤を採用しています。このような類似性により、デスクトップ開発環境から

## Accelerate Algorithmic C-to-IP Integration

図 2 - 高位合成のデザイン フロー

FPGA インプリメンテーションへの迅速な移行が可能です。Vivado HLS は、デフォルトの動作では、ユーザーがターゲット クロック周波数とデバイスを選択した後、何も入力しなくても RTL インプリメンテーションを生成します。さらに、Vivado HLS は、ほかのコンパイラと同様に複数の最適化レベルを備えています。アルゴリズムの最終的な実行ターゲットはオーダーメイドのマイクロアーキテクチャであるため、Vivado HLS では従来のコンパイラよりもきめ細かく最適化レベルを指定できます。プロセッサ向けのソフトウェア デザインで一般的な O1 ~ O3 レベルの最適化の概念は、アーキテクチャ探索指示子で置き換えられます。これらの指示子は、ユーザーの専門知識を利用して、消費電力、エリア、パフォーマンスの観点から特定のアルゴリズムに最適なインプリメンテーションを作成するように Vivado HLS に指示します。

HLS コンパイラのユーザー デザイン フローを図 2 に示します。コンセプト レベルでは、ユーザーは C/C++/SystemC で記述したアルゴリズムを提供し、HLS コンパイラが RTL インプリメンテーションを生成します。プログラム コードを RTL に変換するプロセスは、アルゴリズム仕様、マイクロアーキテクチャ探索、RTL インプリメンテーション、IP パッケージングの 4 つの主な段階に分けられます。

アルゴリズム仕様の段階は、FPGA ファブリックをターゲットとするソフトウェア アプリケーションの開発に対応します。この仕様は、標準的なデスクトップ ソフトウェア開発環境で開発可能であり、ザイリンクスが提供する OpenCV などのソフトウェアライブラリをすべて利用できます。Vivado HLS は、ソフトウェア中心型開発フローの実現に加えて、検証の抽象化を RTL から C/C++ レベルに引き上げます。ユーザーは、元のソフトウェアを使用してアルゴリズムの機能検証を漏れなく実行できます。Vivado HLS による RTL の生成後、生成されたデザインは、従来のソフトウェア コンパイラによって生成されるプロセッサ アセンブリ コードによく似ています。ユーザーはこのアセンブリ コード レベルでデバッグを実行できますが、これは必須ではありません。

Vivado HLS は、ほかのソフトウェア コ

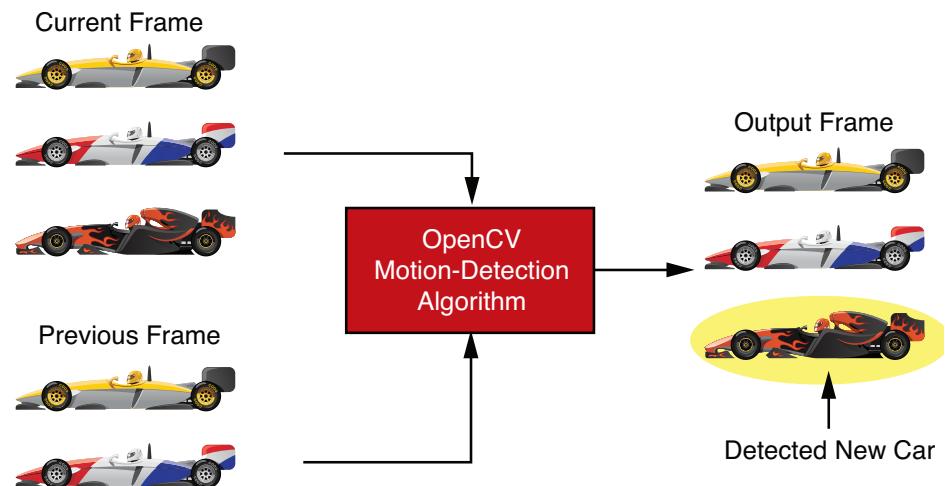

図 3 - OpenCV ライブラリの動き検出アルゴリズムの例

ンパイラをターゲットとするほぼすべての C/C++ コードを処理できますが、コードには 1 つの制限が課されます。すなわち、Vivado HLS を使用して FPGA にコンパイルできるのは、動的なランタイム メモリ割り当てを含まないコードに限られます。プロセッサでは単一のメモリ アーキテクチャによってアルゴリズムが拘束されるのに 対して、FPGA インプリメンテーションはアルゴリズム固有のメモリ アーキテクチャを持ちます。Vivado HLS は、配列と変数の使用パターンを解析して、アルゴリズムのストレージと帯域幅の要件に最適な物理メモリ レイアウトとメモリのタイプを決めることができます。この解析が機能するための条件は、C/C++ コード内でアルゴリズムが参照するすべてのメモリを、配列の形式で明示的に記述することだけです。

C/C++ インプリメンテーションを最適化された FPGA インプリメンテーションに変換するプロセスの第 2 段階は、マイクロアーキテクチャ探索です。この段階では、Vivado HLS コンパイラの最適化機能を適用してさまざまなデザインをテストし、エリアとパフォーマンスの適切な組み合わせが得られるものを探します。ソース コードを変更しなくても、同じ C/C++ コードをさまざまなパフォーマンス ポイントにインプリメントできます。Vivado HLS コンパイラの最適化機能または指示子は、アルゴリ

ズムの異なる部分ごとに、そのパホーマンスがどのようなものであるかを指定するものです。

Vivado HLS コンパイラ フローの最後の段階は、RTL インプリメンテーションと IP パッケージングです。これらは Vivado HLS コンパイラ内部で自動的に実行される手順であり、ユーザーに RTL の知識は必要ありません。このコンパイラには、ザイリンクスの製品ラインの各種デバイス向けに最適化された RTL の作成の詳細が組み込まれています。この段階では、Vivado HLS ツールは、タイミング駆動型で FPGA ファブリック駆動型の RTL を生成するための、徹底的なテストと検証済みのプッシュボタン ユーティリティとして事実上機能します。Vivado HLS コンパイラの出力は、IP-XACT などのほかのザイリンクス ツールに受け入れられるフォーマットで自動的にパッケージされます。したがって、HLS が生成した IP コアを Vivado 内で使用する場合、追加の変換手順は不要です。

ザイリンクスの OpenCV ライブラリは、Vivado HLS を使用したデザインの最適化プロセスにショートカットを提供します。これらのライブラリは、解像度 1080p のピクセルレート処理を実行可能な関数を生成するようにあらかじめ特徴付けられています。これらのライブラリには、Vivado HLS

コンパイラへの指示に必要な最適化の知識が組み込まれています。したがって、デスクトップ環境の OpenCV コンセプト アプリケーションと Zynq All Programmable SoC 上の OpenCV 実行アプリケーション (ARM プロセッサと FPGA ファブリック上の動作が可能) の間での反復 (イタレーション) を制限なしに迅速に行えます。

図 3 に、OpenCV で開発した動き検出アプリケーションの概要を示します。このデザインの目標は、現在のイメージ フレームと直前のイメージ フレームを比較して、ビデオ ストリーム内の動いている対象を検出することです。アルゴリズムの最初の段階では、両方のフレーム内の輪郭を検出します。このデータ リダクション操作により、連続するフレーム間の相対的な変化が簡単に解析できるようになります。輪郭情報の抽出後、両方の輪郭を比較して、現在のイ

メージに現れているが、直前のイメージには現れていない輪郭を検出します。新たに検出されたこれらの輪郭から、動き検出マスク イメージが作成されます。ここで、新しい輪郭の検出結果を現在のイメージ上でハイライトする前に、イメージ センサー ノイズの影響を考慮に入れる必要があります。このノイズはフレーム間で変化することがあり、動き検出マスク イメージ内にランダムな偽りの輪郭を発生させることができます。したがって、このイメージをフィルタリングし、アルゴリズムの品質に対するノイズの影響を軽減する必要があります。

このアプリケーションでは、ノイズ リダクションは動き検出マスク イメージ上の 7x7 の Median フィルターによって実現されます。Median フィルターの中心となる考え方とは、隣接するピクセルの 7x7 の枠内の中間値をとることです。このフィルター

は、この枠の中央のピクセルの最終的な値として、この中央値を戻します。ノイズ リダクションの実行後、動き検出マスク イメージが生の入力イメージと組み合わされ、動いている輪郭が赤でハイライトされます。

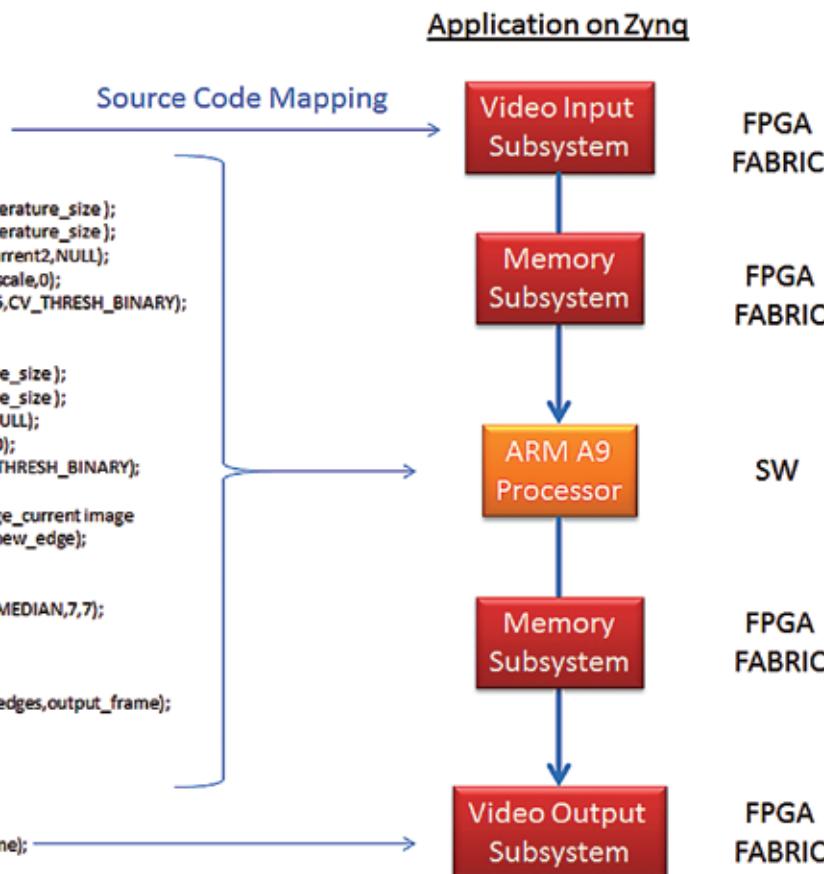

図 4 に示す Zynq All Programmable SoC へのソース コード マッピングを使用して、ARM プロセッシング サブシステム上で動作するアプリケーションを完全にインプリメントできます。このインプリメンテーションのハードウェア要素は、cvgetframe 関数と showimage 関数の要素だけです。これらのビデオ I/O 関数は、FPGA ファブリック内のザイリンクスのビデオ I/O サブシステムを使用してインプリメントされます。cvgetframe 関数が呼び出されると、このビデオ I/O サブシステムの入力側がすべての詳細な処理を扱い、HDMI

### Application Code

```

while(1){

//Get the image frame from the video input

frame_current=cvQueryFrame(capture);

//Detect edges in the current frame

cvSobel(gray_current,edge_current2,1,0,aperture_size);

cvSobel(gray_current,edge_current1,0,1,aperture_size);

cvAdd(edge_current2,edge_current1,edge_current2,NULL);

cvConvertScale(edge_current2,edge_current,scale,0);

cvThreshold(edge_current,edge_current,5,255,CV_THRESH_BINARY);

//Detect edges in the previous frame

cvSobel(gray_prev,edge_prev2,1,0,aperture_size);

cvSobel(gray_prev,edge_prev1,0,1,aperture_size);

cvAdd(edge_prev2,edge_prev1,edge_prev2,NULL);

cvConvertScale(edge_prev2,edge_prev,scale,0);

cvThreshold(edge_prev,edge_prev,5,255,CV_THRESH_BINARY);

//Detect edges that are only present in the edge_current image

detect_new_edges(edge_prev,edge_current,new_edge);

//Remove noise from the new edges

cvSmooth(new_edge,filtered_new_edges,CV_MEDIAN,7,7);

//Combine new edges with current frame

//Highlight new edges in red

highlight_blend(frame_current,filtered_new_edges,output_frame);

//Copy current frame into previous frame

cvCopy(frame_current,frame_prev,NULL);

//Display output frame

cvShowImage("Detector Output",output_frame);

}

```

図 4 – ARM プロセッサを使用した Zynq All Programmable SoC 上の動き検出

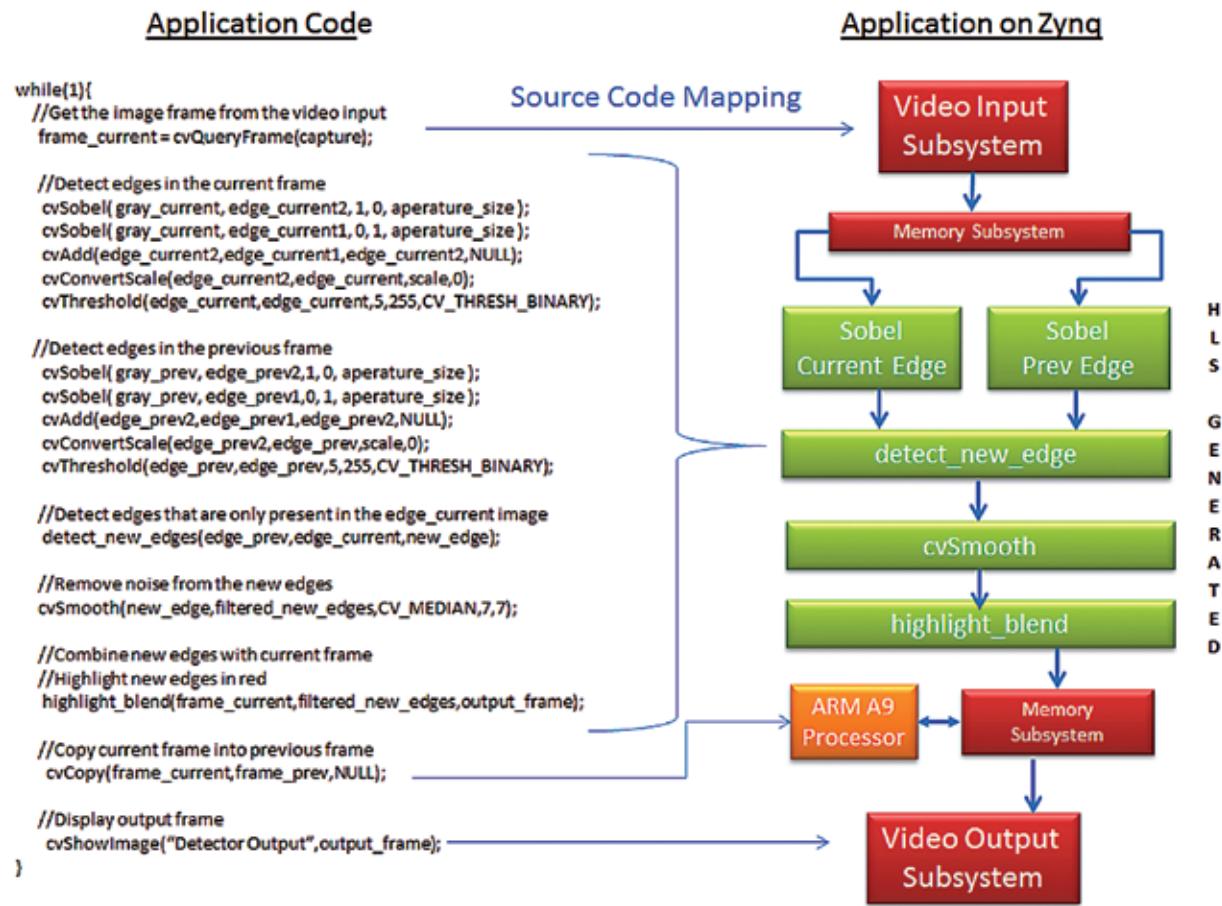

図 5 – プログラマブル ファブリックを使用した Zynq All Programmable SoC 上の動き検出

インターフェイスからビデオ ストリームを取り込んでデコードし、ピクセル データを DDR メモリに格納します。showimage 関数が呼び出されると、このサブシステムは、テレビまたはその他の HDMI 準拠のビデオ ディスプレイ デバイスを駆動するために、DDR メモリからビデオ ディスプレイ コントローラへのピクセル データの転送を処理します。

Vivado HLS に最適化されたハードウェア アクセラレーション用 OpenCV ライブラリを使用して、図 4 のコードを、FPGA ファブリック上のリアルタイム 60 フレーム / 秒のピクセル処理パイプラインに移植できます。これらの OpenCV ライブラリは、ハードウェア アクセラレーションを必要とする OpenCV 内の要素の基本的関数を提供します。ハードウェア アクセラレーションを使用しない場合、すなわち、すべてのコードを

ARM プロセッサのみで実行した場合、このアルゴリズムのスループットは 13 秒当たり 1 フレーム (0.076 フレーム / 秒) に低下します。図 5 に、Vivado HLS のコンパイル後のアプリケーションの新しいマッピングを示します。元のシステムのビデオ I/O マッピングが再利用されていることに注意してください。以前 ARM プロセッサ上で実行されていたアルゴリズムの演算コアは、Vivado HLS によって生成された複数の IP ブロックにコンパイルされます。Vivado IP インテグレーター内でビデオ I/O サブシステムに接続されるこれらのブロックは、解像度 1080p、60 フレーム / 秒のビデオ処理に最適化されています。

Zynq SoC および Vivado Design Suite が提供する All Programmable デバイスの開発環境は、最新の高精細度ビデオ テクノロジが要求する高いデータ処理

レートでのエンベデッド ビジョン システムのデザイン、プロトタイピング、テストに最適です。要求の厳しいコンピューター ビジョン アプリケーションを短い開発期間でインプリメントするための最も良い方法は、OpenCV に含まれる一連のオープン ソース ライブラリを使用することです。OpenCV ライブラリは C++ で作成されているため、Vivado HLS を使用して、Zynq All Programmable SoC の FPGA ファブリック内のハードウェア RTL に効率的に変換できるソース コードを作成します。OpenCV ライブラリは、当初構想されたデザイン環境の柔軟性を損なわずに、便利な処理アクセラレータとして使用できました。

Vivado Design Suite を使用した Smarter Vision デザインの詳細は、<http://japan.xilinx.com/products/design-tools/vivado/index.htm> をご覧ください。

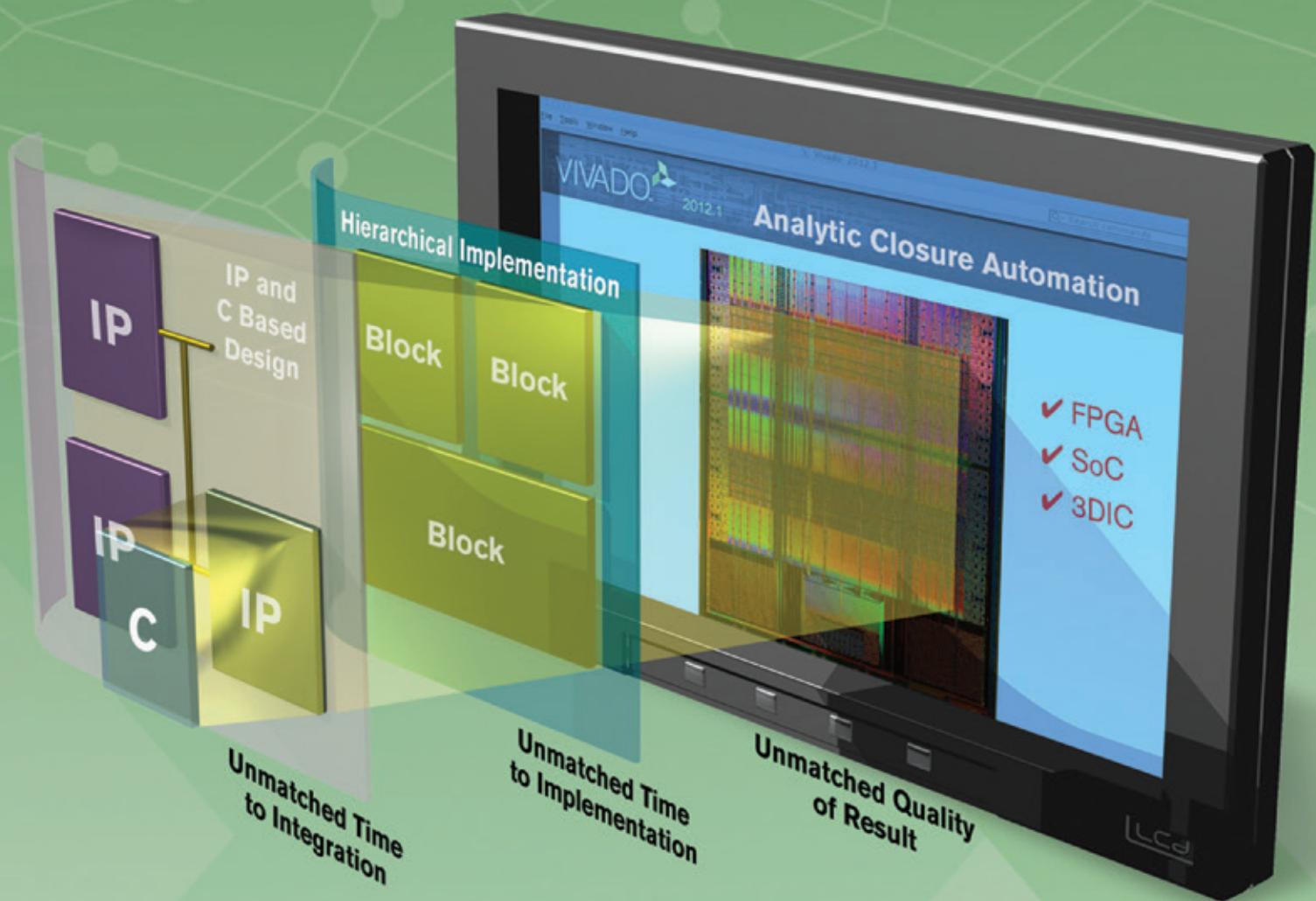

# A Generation Ahead

Vivado™ Design Suite WebPACK™ Edition で比類なき

インテグレーションおよびインプリメンテーション タイムを実現

詳細は[こちら](#)

ザイリンクス株式会社

製品のお問い合わせは下記の販売代理店へどうぞ

■東京エレクトロン デバイス(株) TEL(045)443-4016 x2web@teldevice.co.jp ■アバネット・インターニックス(株) TEL(03)5792-8210 EVAL-KITS-JP@avnet.com

■(株)PALTEK TEL(045)477-2005 nfo\_pal@paltek.co.jp ■新光商事(株) TEL(03)6361-8086 X-Pro@shinko-sj.co.jp

©Copyright 2013 Xilinx, Inc. All rights reserved. ザイリンクスの名称およびロゴは、米国およびその他各国のザイリンクス社の登録商標および商標です。

ARMは、EUおよびその他の国におけるARM Limitedの登録商標です。他のすべての商標はそれぞれの所有者の財産です。

**XILINX**

ALL PROGRAMMABLE

## Xilinx High-Level Synthesis Tool Speeds FPGA Design

# FPGA のデザインを迅速化する ザイリンクスの高位合成ツール

**Sharad Sinha**

PhD Candidate

Nanyang Technological University, Singapore

sharad\_sinha@pmail.ntu.edu.sg

```

#include "matrixmult.h"

using namespace d_stream;

stream<data> d_matrixleft;

stream<data> d_matrixright;

stream<data> d_matrixproduct;

```

```

data elementmat1;

data elementmat2;

data i,j,p,q,k;

for (i=0;i<2;i++)

{

for(j=0;j<2;j++)

{

matrixleft[i][j] = 0;

}

}

```

```

data matrixproduct;

data elementmat1;

data elementmat2;

data i,j,p,q,k;

for (i=0;i<2;i++)

{

for(j=0;j<2;j++)

{

mat...

```

# Vivado HLS と C などの高級言語を組み合わせることで、FPGA にアルゴリズムを迅速にインプリメントできます。

高位合成 (HLS) とは、最初に C、C++、または SystemC で記述したデジタルデザインを自動的に合成する手法です。高位合成は、高い抽象化で作業ができる上に、複数のデザインソリューションを簡単に生成できるため、技術者の注目を集めています。設計者は、HLS を使用してデザインの多くの可能性を検討し、それぞれのエリアとパフォーマンスの特性を比較した後、1つに絞って FPGA チップ上にインプリメントできます。たとえば、メモリをブロック RAM (BRAM) にマッピングした場合と分散 RAM にマッピングした場合の効果を比較したり、ループ展開などのループに関連する最適化手法の効果を検討したりするとき、手作業なしで複数の異なるレジスタトランシスター レベル (RTL) デザインを生成できます。C/C++/SystemC デザイン内で関連する指示子を設定するだけで済みます。

ザイリンクスは、新たにリリースされた Vivado™ ツール スイートに HLS ツールを導入しました。Vivado HLS は、AutoESL ツールを再設計して商標変更した製品であり、C/C++/SystemC コードを最適化して目標性能を達成するための多くの機能を備えています。Vivado HLS のような HLS ツールを使用すると、Verilog や VHDL などのハードウェア記述言語に基づく時間のかかる RTL 設計手法に頼らずに、FPGA にアルゴリズムを迅速にインプリメントできます。

ユーザーの視点から Vivado HLS の機能を理解するために、デザイン例として

行列乗算を取り上げ、デザイン記述 (C/C++/SystemC) から FPGA インプリメンテーションまでに至るエンドツーエンドの合成プロセスを見てみましょう。行列乗算は多くのアプリケーションで一般的な演算であり、画像およびビデオ処理、科学技術計算、デジタル通信に広く使用されています。このプロジェクトのすべての結果は、Vivado HLS 2012.4 と、物理合成および配置配線用ザイリンクス® ISE® ソフトウェアツール (バージョン 14.4) を使用して生成されたものです。またこのフローでは、RTL 協調シミュレーションに ModelSim および GCC-4.2.1-mingw32vc9 を使用します。

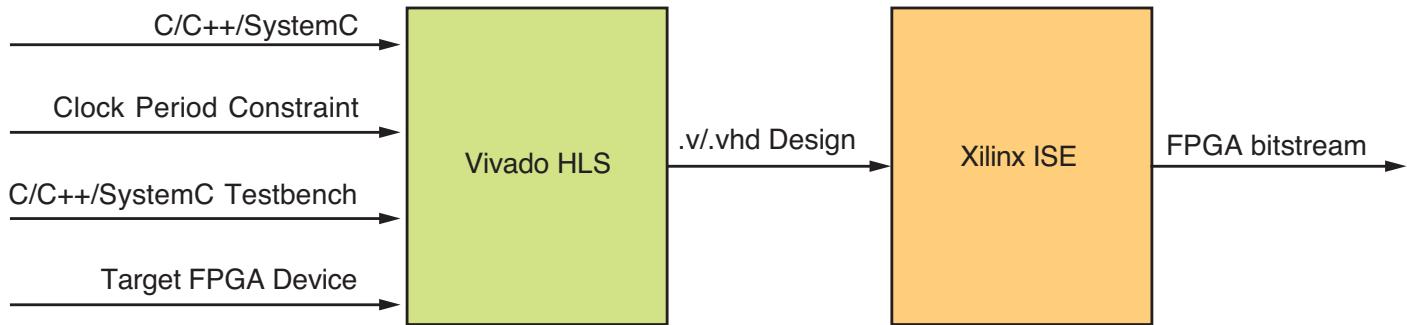

図 1 に、FPGA に合成されるデザインの、C/C++/SystemC の記述から始まる簡単な合成プロセスのフローを示します。C/C++/SystemC テストベンチは、このデザインが正しく機能することを検証するのに必要なテストベンチです。RTL および C 協調シミュレーションにもこのテストベンチが必要です。協調シミュレーションでは、RTL テストベンチや「e」または Vera などの検証用言語で作成されたテストベンチではなく、この C/C++/SystemC テストベンチを使用して、生成済み RTL デザイン (.v または .vhd デザイン) の機能を検証します。クロック周期制約は、デザインが動作すると想定されるターゲットクロック周期を設定します。ターゲット FPGA デバイスは、デザインがマッピングされるザイリンクスの FPGA です。

```

"matrixmultiplystream.h"

space hls;

data> d_mat1;

data> d_mat2;

data> d_prodmat;

multiplystream

>& d_prodmat)

```

図 1 — Vivado HLS を使用した FPGA 合成フロー

## C コードによる行列乗算

筆者らの行列乗算の例から多くを得るために、C による行列乗算のインプリメンテーションのさまざまな修正版を検討し、合成済みのデザインに与える影響を示します。このプロセスは、プロトタイプと実際のデザインに HLS を使用する際に注意しなければならない重要な点を明らかにします。プロジェクトのセットアップの手順は HLS ツールのマニュアルに記載されているので、ここでは説明を省略し、デザインとインプリメンテーションに焦点を合わせます。

標準的な Vivado HLS フローでは、合成される C 関数を含むソース ファイル、ヘッダー ファイル、main() 関数の呼び出しの中でテストベンチを記述するファイルの 3 種類の C/C++ ファイルが必要です。

ヘッダー ファイルには、ソース ファイル内にインプリメントされている関数の宣言に加えて、特定のビット幅を持つユーザー定義のデータ型をサポートする指示子があります。これにより、設計者は、C/C++ で定義されている標準ビット幅とは異なるビット幅を使用できます。たとえば、C では整数データ型 (int) のデータ長は常に 32 ビットです。しかし、Vivado HLS 内では、16 ビットのみを使用するユーザー定義のデータ型「data」を指定できます。

図 2 に、行列乗算用の簡単な C 関数を示します。2 つの行列 mat1 と mat2 を乗算すると、行列 prod が得られます。わかりやすいように、すべての行は 2 行 × 2 列の同じサイズとします。

この HLS フローで実行しなければならな

い手順は次のとおりです。

- ・手順 1：プロジェクトの構築

- ・手順 2：ビルドのテスト

- ・手順 3：合成

- ・手順 4：RTL 協調シミュレーション

- ・手順 5：RTL/RTL インプリメンテーションのエクスポート

手順 1 では、さまざまなデザイン ファイルにプロジェクトをコンパイルし、構文エラーなどがないかチェックします。手順 2 では、(ソース ファイル内にある) インプリメントされる関数の機能の正しさをテストします。この手順では、テストベンチ内で関数の呼び出しを実行し、関数が正しく機能する

ことを検証します。機能検証に合格しなかった場合は、前の手順に戻ってデザイン ファイルを修正します。

手順 3 では合成を実行します。Vivado HLS は、ソース ファイル内で定義されている関数を合成します。この手順の出力には、C 関数を変換した Verilog および VHDL コード (RTL デザイン) と、ターゲット FPGA 上のリソース使用率の推定値、ターゲット クロック周期を基準としたクロック周期の推定値が含まれます。Vivado HLS は、レイテンシの推定値とループに関連する指標も生成します。

手順 4 では、C テストベンチを使用して、生成済み RTL のシミュレーションを行います。Vivado HLS は、C ソース コードの検証に使用したのと同じテストベンチを使用し

```

void matrixmultiply(data matleft[2][2], data matright[2][2], data product[2][2])

{

data i,j,k;

for(i=0;i<2;i++)

{

for(j=0;j<2;j++)

{

for(k=0;k<2;k++)

{

product[i][j] = product[i][j] + matleft[i][k] * matright[k][j];

}

}

}

}

```

図 2 – 2 × 2 の行列乗算用の簡単な C コード

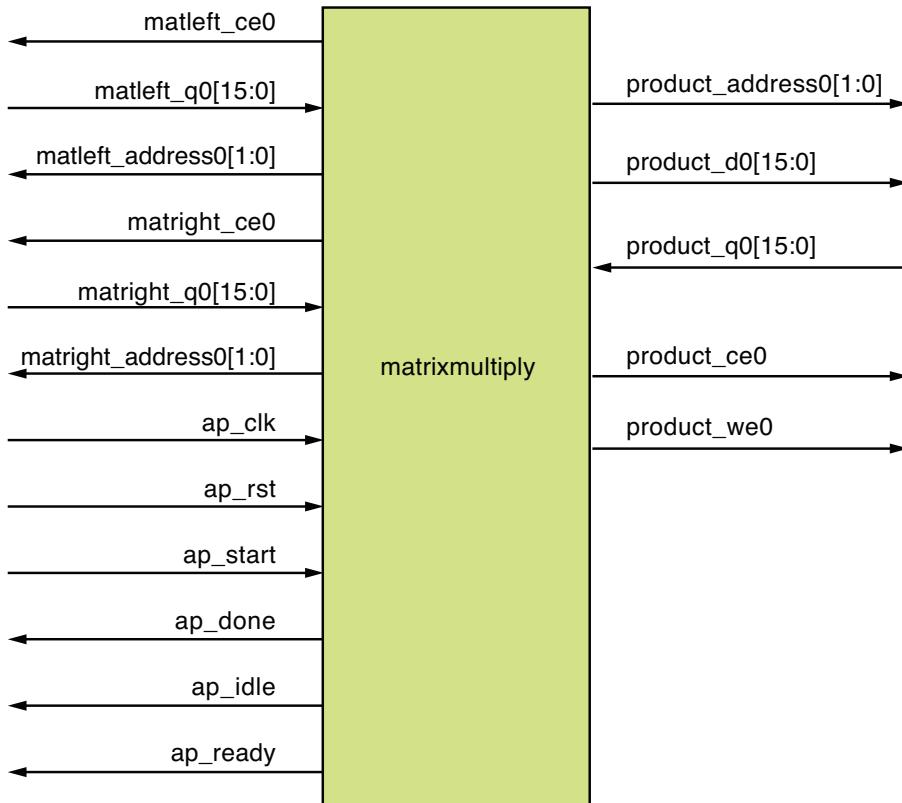

図 3 - 図 2 のコードから得られるデザイン

て、今度は RTL の機能の正しさを検証するため、この手順は RTL 協調シミュレーションと呼ばれます。この手順を成功させるには、使用するシステム (Windows または Linux) 上の PATH 環境変数に ModelSim インストレーションのパスが含まれている必要があります。また、ModelSim インストレーション フォルダーに GCC-4.2.1-mingw32vc9 パッケージが置かれている必要があります。

最後の手順 5 では、RTL を IP ブロックとしてエクスポートし、より大規模なデザインで使用したり、ほかのザイリンクス ツールで処理できるようにしたりします。IP-XACT フォーマットの IP ブロック、System Generator IP ブロック、または pcore フォーマットの IP として RTL をエクスポートし、ザイリンクスのエンベデッド デザイン キットで使用できます。Vivado で生成された RTL をエクスポートしている間に、Vivado ツールの [Evaluate] オプションを選択し、RTL インプリメンテーションで得られる配置配線後

のパフォーマンスを評価できます。この場合、ザイリンクス ISE ツールは Vivado HLS ツールの中から実行されます。これを行うには、Vivado HLS が ISE インストレーション

を探せるように、PATH 環境変数に ISE インストレーションのパスを設定しておく必要があります。

もちろん、Vivado で生成された RTL は、IP ブロックとして上記の 3 種類のフォーマットでエクスポートしなくてもかまいません。エクスポート済みのフォーマット ファイルは、<project\_directory>/<solution\_number>/impl/<pcores>、<project\_directory>/< solution\_number>/impl/<sysgen>、または <project\_directory>/< solution\_number>/impl/<ip> の 3 箇所で利用可能です。Vivado で生成された RTL は、より大規模なデザインの中で使用することも、それ自体のトップレベルのデザインとして使用することもできます。ただし、より大規模なデザインにインスタンシエートする場合は、インターフェイスの要件に注意する必要があります。

図 2 の C 関数が合成されると、図 3 に示す RT レベルのインプリメンテーションが得られます。おわかりのように、このインプリメンテーションでは、行列 1 と行列 2 の要素が関数に読み込まれ、行列の積の要素が書き出されます。このように、このインプリメンテーションは、行列 1、行列 2、行列 prod の要素の格納に「matrixmultiply」エンティティの外部のメモリを利用できることを想定しています。表 1 にデザインの指標、表 2 に信号の説明を示します。

表 2 では、スタート (start) 信号、完了 (done) 信号、アイドル (idle) 信号が、デザイン

| デザイン指標                   | デバイス: XC6VCX75TFF784-2 |

|--------------------------|------------------------|

| DSP48E                   | 1                      |

| ルックアップ テーブル              | 44                     |

| フリップフロップ                 | 61                     |

| 最善のクロック周期 (ns)           | 2.856                  |

| レイテンシ                    | 69                     |

| スループット (イニシエーション インターバル) | 69                     |

表 1 - 図 3 のデザインのデザイン指標

| 信号                    | 説明                                                         |

|-----------------------|------------------------------------------------------------|

| matleft_ce0           | 行列 1 を格納するメモリのチップ イネーブル                                    |

| matleft_q0[15:0]      | 行列 1 の 16 ビット要素                                            |

| matleft_address[1:0]  | 行列 1 を格納するメモリからデータを読み出すアドレス                                |

| matright_ce0          | 行列 2 を格納するメモリのチップ イネーブル                                    |

| matright_q0[15:0]     | 行列 2 の 16 ビット要素                                            |

| matright_address[1:0] | 行列 2 を格納するメモリからデータを読み出すアドレス                                |

| product_ce0           | 行列の積を格納するメモリのチップ イネーブル                                     |

| product_we0           | 行列の積を格納するメモリの書き込みイネーブル                                     |

| product_d0[15:0]      | 行列の積を格納するメモリに書き込まれるデータ                                     |

| product_q0[15:0]      | 行列の積を格納するメモリから読み出されるデータ                                    |

| product_address0[1:0] | 行列の積のデータが読み出される/書き込まれるアドレス                                 |

| ap_clk                | デザインのクロック信号                                                |

| ap_rst                | デザインのアクティブ High 同期リセット信号                                   |

| ap_start              | 演算の開始を示すスタート信号                                             |

| ap_done               | 演算の終了と出力レディを示す完了信号                                         |

| ap_idle               | エンティティ (デザイン) がアイドルであることを示すアイドル信号                          |

| ap_ready              | デザインが新しい入力データを受け入れられることをデータ供給段に指示する信号。ap_idle と組み合わせて使用される |

表 2 - 図 3 のデザインの信号の説明

内のデータパスを制御する有限ステート マシン (FSM) に関連付けられます。おわかりのように、Vivado HLS で生成された Verilog は、スタート (start) 信号で演算が開始され、ap\_done 信号の Low から High への移行で有効な出力データが利用可能になることを前提としています。Vivado HLS で生成された Verilog/VHDL は、少なくとも 3 つの基本信号 ap\_start、ap\_done、ap\_idle と ap\_clk 信号を必ず使用します。つまり、Vivado HLS を使用して

どのようなデザインをインプリメントしたとしても、ストリーミング スループットはデザインのレイテンシによって制約されます。図 2 のデザインのレイテンシは、3ns のターゲット クロック周期で 69 クロック サイクルです。つまり、この例では、行列の積のすべての要素が利用可能になるまでに 69 クロック サイクルかかります。したがって、少なくとも 69 クロック サイクル経過するまでは、新しい入力行列をデザインに供給できません。

図 3 に示したインプリメンテーションは、設計者が FPGA に行列乗算をインプリメントするときに意図しているものとはおそらく異なります。おそらく設計者は、供給される入力行列を内部に格納して演算し、行列の積の要素を読み出すようなインプリメンテーションを意図しているはずです。図 2 のインプリメンテーションが実行する処理は、明らかにこれとは異なります。図 2 のインプリメンテーションは、入力行列と出力行列のデータをインプリメンテーションの外部のメモリ

内で利用できることを想定しています。

## コードの再構築

本来の設計者の目的には図 4 のコードが役立つでしょう。このコードはソース ファイルの一部ですが、このソース ファイルは、前の例のような C ファイルではなく、C++ ファイルに違いありません。関連するヘッダー hls\_stream.h と ap\_int.h をヘッダーファイル matrixmultiply.h 内で指定する必要があります。ソース ファイルが C ファイルであった図 2 の例では、ヘッダー ファイルに ap\_cint.h ヘッダーが含まれていたことに注意してください。ヘッダー ファイル ap\_int.h は C++ ソース ファイル内、ap\_cint.h は C ソース ファイル内で、任意のビット幅を持つユーザー定義のデータ型を定義できるようにします。ヘッダー ファイル hls\_stream.h は、ストリーム インターフェイスを利用するのに必要なファイルであり、ソース ファイルが C++ 言語で記述されている場合にのみ使用できます。

入力行列をストリーム入力し、行列の積をストリーム出力するデザインを生成するには、読み出しストリームと書き込みストリームをコードにインプリメントする必要があります。コード hls::stream<> stream\_name を使用して、読み出しストリームと書き込みストリームを指定します。ここでは d\_mat1 と d\_mat2 が読み出しストリームで、d\_product が書き込みストリームです。ストリーミング インターフェイスは FIFO として動作します。デフォルトでは、FIFO の深さは 1 です。Vivado HLS の [Directive] ビューで定義済みストリームを選択し、深さを設定する必要があります。図 4 のコードでは、各ストリームの深さは 4 データ単位です。C++ コードにはシーケンシャルに実行する性質があるため、(i,j) ループが (p,q) ループよりも前に実行されることに注意してください。したがって、d\_mat2 ストリームは d\_mat1 ストリームよりも後に充填されます。

ストリーム インターフェイスが完成したら、[Directive] ビューから指示子 RESOURCE を適用してコアを選択し、行列が BRAM にマッピングされるように選択します。この操作を行わないと、行列はフリップフロップとルックアップ テーブル (LUT) を使用してインプリメントされます。なお、[Directive] ビューは、[Synthesis] ビューでソース

ファイルをアクティブにしている場合にのみアクティブになります。

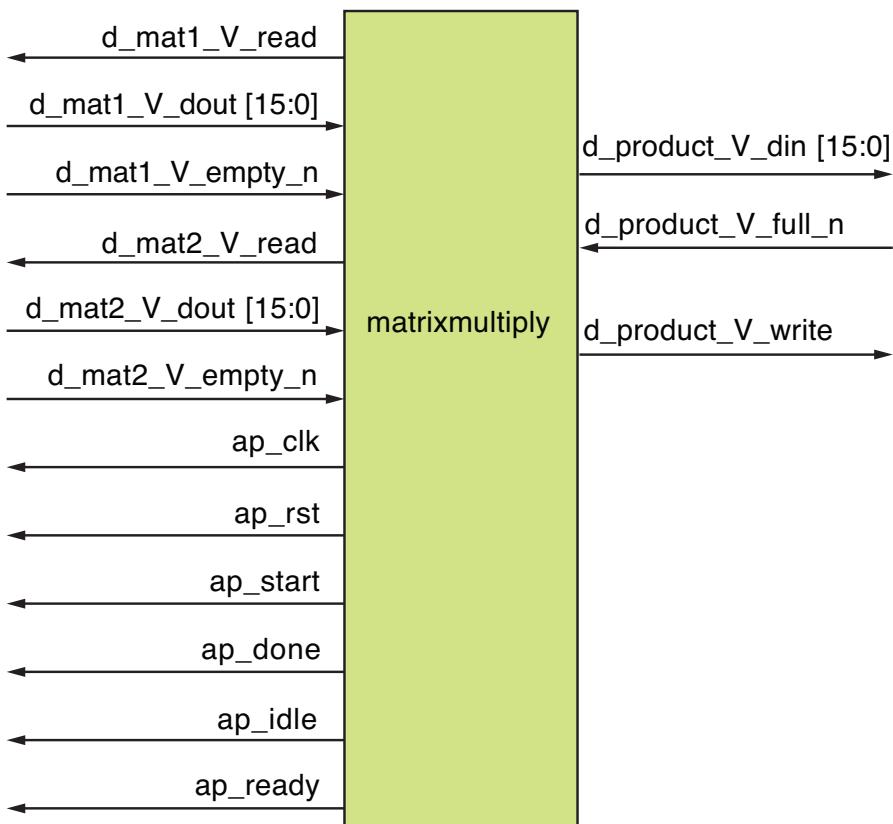

図 4 のコードのインプリメント済みデザインを図 5 に示します。表 3 に、このデザインのインターフェイス上で利用可能な信号の説明を示します。表 3 の d\_product\_V\_full\_n は、行列の積が一杯になったことをコアに知らせるアクティブ Low 信号です。

これは一般的にインプリメンテーションでは不要です。

表 4 に、行列の配列を BRAM または分散 RAM にマッピングした場合とマッピングしない場合について、3ns のクロック周期制約で配置配線を行った後のさまざまなデザイン指標を示します。表 4 から、シングルポートの BRAM に行列をマッピングすると、

```

#include "matrixmultiplystream.h"

using namespace hls;

stream <data> d_mat1;

stream <data> d_mat2;

stream <data> d_product;

void matrixmultiplystream (stream<data>& d_mat1, stream<data>& d_mat2,

stream<data>& d_product)

{

data matrixleft [2] [2] = {{0}};

data matrixright [2] [2] = {{0}};

data matrixproduct [2] [2] = {{0}};

data elementmat1;

data elementmat2;

data i, j, p, q, k;

for (i=0;i<2;i++)

{

for(j=0;j<2;j++)

{

matrixleft [i] [j] = d_mat1.read();

}

}

for (p=0;p<2;p++)

{

for(q=0;q<2;q++)

{

matrixright [p] [q] = d_mat2.read();

}

}

for(i=0;i<2;i++)

{

for(j=0;j<2;j++)

{

for(k=0;k<2;k++)

{

matrixproduct [i] [j] = matrixproduct [i] [j] + matrixleft [i] [k] *

matrixright [k] [j];

}

}

}

for(i=0;i<2;i++)

{

for(j=0;j<2;j++)

{

d_product << matrixproduct [i] [j];

}

}

}

```

図 4 – 再構築された行列乗算用ソース コード

| 信号                     | 説明                                                             |

|------------------------|----------------------------------------------------------------|

| d_mat1_V_read          | デザインが 行列 1(左の行列)への入力を受け入れられることを知らせる信号                          |

| d_mat1_V_dout [15:0]   | 行列 1 の 16 ビットストリーミング要素                                         |

| d_mat1_V_empty         | 行列 1 の要素がもう残っていないことをデザインに知らせる信号                                |

| d_mat2_V_read          | デザインが 行列 2(右の行列)への入力を受け入れられることを知らせる信号                          |

| d_mat2_V_dout [15:0]   | 行列 2 の 16 ビットストリーミング要素                                         |

| d_mat2_V_empty         | 行列 2 の要素がもう残っていないことをデザインに知らせる信号                                |

| d_product_V_din [15:0] | 行列の積の 16 ビット出力要素                                               |

| d_product_V_full_n     | 行列の積を読み出す準備ができていることを知らせる信号                                     |

| d_product_V_write      | データが行列の積に書き込まれていることを知らせる信号                                     |

| ap_clk                 | デザインのクロック信号                                                    |

| ap_rst                 | デザインのアクティブ High 同期リセット信号                                       |

| ap_start               | 演算の開始を示すスタート信号                                                 |

| ap_done                | 演算の終了と信号出力レディを示す完了信号                                           |

| ap_idle                | エンティティ(デザイン)がアイドルであることを示すアイドル信号                                |

| ap_ready               | デザインが新しい入力データを受け入れられることをデータ供給段に指示する信号。<br>ap_idle と組み合わせて使用される |

表 3 - 図 5 のデザインの信号の説明

| デバイス : XC6VCX75TFF784-2 |                             |                         |                                        |

|-------------------------|-----------------------------|-------------------------|----------------------------------------|

| デザイン指標                  | 行列に BRAM も<br>分散 RAM も使用しない | 行列にシングル ポート<br>BRAM を使用 | 行列に(LUT にインプリ<br>メントされた) 分散<br>RAM を使用 |

| DSP48E                  | 1                           | 1                       | 1                                      |

| ロックアップ テーブル             | 185                         | 109                     | 179                                    |

| フリップフロップ                | 331                         | 102                     | 190                                    |

| BRAM                    | 0                           | 3                       | 0                                      |

| 最善のクロック周期(ns)           | 2.886                       | 3.216                   | 2.952                                  |

| レイテンシ                   | 84                          | 116                     | 104                                    |

| スループット(イニシエーションインターバル)  | 84                          | 116                     | 104                                    |

表 4 - 図 5 のデザインのデザイン指標

デザインは 3ns のタイミング制約を満たさないことがわかります。この結果を恣意的に表に含めたのは、この手法を使用して、さまざまなエリアと時間の指標対応する多様なデザインを生成できることを示すためです。また、表 1 から、図 2 のコードで発生する 69 クロック サイクルのレイテンシは図 4 のコードに基づいて再構築されたデザインよりも短いのですが、既に説明したように、図 2 のデザインでは matrixmultiply エンティティの外部のメモリが必要になることが推測されます。

入力行列をストリーム入力し、行列の積をストリーム出力するデザインを生成するには、読み出しへストリームと書き込みストリームをコードにインプリメントする必要があります。ストリーミング インターフェイスは FIFO として動作します。デフォルトでは、FIFO の深さは 1 です。

## インプリメンテーションの精度

ここに示した結果については、筆者はデータ型「data」を 16 ビット幅として定義しました。したがって、すべての行列（左、右、および積）の要素は 16 ビット幅に限られます。その結果、行列の乗算と加算はフル精度では実行されていません。ヘッダー ファイル内でほかのデータ型 data\_t1 を 32 ビット幅として定義することもできます。この場合、行列の積のすべての要素はこの 32 ビット幅のデータ型になります。これは、16 ビット数（左の行列の要素）にほかの 16 ビット数（右の行列の要素）を掛けた結果は最大で 32 ビット幅になるからです。この場合のリソース使用率とタイミング結果は、表 1 と表 4 の値とは一致しません。

再構築されたソース コードは、同じソース ファイルからどのように複数のデザイン ソリューションを生成できるかを示しています。この例では、1 つのデザイン ソリューション

は BRAM を使用し、もう 1 つのソリューションは使用しません。Vivado HLS の各プロジェクト ディレクトリには、Vivado HLS が各ソリューションごとに個別のディレクトリを生成していることが見て取れます。各ソリューション ディレクトリには、「impl」(implementation) というサブディレクトリが作成されます。このサブディレクトリには、RTL インプリメンテーション フェーズで使用したソース コードの種類に応じて、「Verilog」または「VHDL」というディレクトリが作成されます。同じ impl サブディレクトリには、ザイリンクス ISE プロジェクト ファイル（ファイル拡張子 .xise）もあります。Vivado HLS で生成されたデザインがトップレベルのデザインである場合、このファイルをクリックすることで、ザイリンクス ISE 内でソリューションのシミュレーションを開始し、ゲートレベルのタイミングおよび論理シミュレーション用に配置配線後のシミュレーション モデルを生成できます。Vivado HLS 内からこのシミュレーションを実行することはできません。

ISE でソリューションのシミュレーションを開始した後、デザインに I/O ピンを割り当てる必要があります。次に、ISE Project Navigator で [Generate Programming File] を実行し、ビットストリームを生成できます。

この演習では、Vivado HLS の開始から完了までの実際のフローと、FPGA 上のインプリメンテーションを見てきました。Vivado HLS の高度な機能の多くを上手に利用するには、ソース コードを再構築するために、設計者が目的のハードウェア アーキテクチャを理解している必要があります。詳細は、次の資料をご覧ください。

『Vivado Design Suite チュートリアル：高位合成』(UG871 : [http://japan.xilinx.com/support/documentation/sw-manuals\\_j/xilinx2012\\_4/ug871-vivado-high-level-synthesis-tutorial.pdf](http://japan.xilinx.com/support/documentation/sw-manuals_j/xilinx2012_4/ug871-vivado-high-level-synthesis-tutorial.pdf))

『Vivado Design Suite ユーザー ガイド：高位合成』(UG902 : [http://japan.xilinx.com/support/documentation/sw-manuals/xilinx2012\\_2/ug902-vivado-high-level-synthesis.pdf](http://japan.xilinx.com/support/documentation/sw-manuals/xilinx2012_2/ug902-vivado-high-level-synthesis.pdf))

Sharad Sinha 氏のほかの記事をお読みになりたい方は、氏のブログ <http://sharadsinha.wordpress.com> をご覧ください。

図 5 - 図 4 のコードから得られるデザイン

# Using Xilinx's Power Estimator and Power Analyzer Tools

## ザイリンクスのパワー エスティメーター およびパワー アナライザー ツールの使用

# 適切な電源アーキテクチャを確保するには、FPGA デザインの消費電力を正確に予測することが非常に重要です。

**Adam Taylor**

Principal Engineer

EADS Astrium

[aptaylor@theiet.org](mailto:aptaylor@theiet.org)

FPGA は、他の多くのコンポーネントとは異なり、コア電圧、補助電源電圧、I/O 電圧の入手に必要な電力が、デザインのインプリメンテーションによって決まります。このため、アプリケーションにおける FPGA の消費電力の計算は、単にデータシートを読み取るよりも多少複雑になります。したがって、必要な静止電流、ランプレート、シーケンシングに対応するだけでなく、デバイスのジャンクション温度を許容範囲内に保ちながら目的のアプリケーションに十分な電力を供給できる、適切な電源アーキテクチャを確保することはなかなか容易なことではありません。

ザイリンクスが提供するザイリンクス パワー エスティメーター (XPE) とザイリンクス パワー アナライザー (XPA) は、FPGA デザインの正確な消費電力解析を実現するデザイン ツールです。デザインの早期段階ではスプレッドシート ベースの XPE を使用し、インプリメンテーションの完了後に XPA を使用します。XPA はデザインの電力要件の詳細な解析を実行し、消費電力の最適化が必要な場合はそれをサポートします。

## デザイン早期の手順

プロジェクトの開発を始めるとき、完成した FPGA デザインが存在することはまれです（運が良ければ、一部のコードを再利用することにより、消費電力予測のためのより正確な情報が得られることがあります）。したがって、消費電力予測は、ザイリンクス パワー エスティメーターのスプレッドシートから始められます (<http://japan.origin.xilinx.com/>)。

[inx.com/products/design\\_tools/logic\\_design/xpe.htm](http://www.xilinx.com/products/design_tools/logic_design/xpe.htm) を参照）。最初の消費電力予測は、デザインに必要なクロック、ロジック、および追加リソースの数に関するエンジニアリング チームの初期の想定に基づいて行われます。

XPE の使用方法は非常に簡単です。さらに良いことに、このツールは、インプリメンテーションに関する豊富な「what if」条件を使用して、デザインのさまざまな選択肢が消費電力予測に与える影響を判定できます。大量の電力を消費するソリューションの場合、最適なインプリメンテーションを決めるには、この機能が非常に効果的です。

ヒート シンク、エアフロー、プリント回路基板のレイヤー数に基づいてデバイスのジャンクション温度を予測する XPE の機能も、早期の段階では非常に便利です。この機能により、意図したインプリメンテーションに対して、そのデザインがジャンクション温度を下げることができるかどうかがわかります。

XPE を使用するには、最初の手順で [Settings] タブにできるだけ正確に設定値を入力します。デバイスの選択とともに、パッケージ、スピード グレード、温度グレード、また必要に応じてステッピング、プロセス、電力モードを正しく設定するように特に注意してください。これらのパラメーターはすべて全体的な電力要件に大きな影響を与えます。特にプロセスの選択が重要であり、設定値は [Maximum] または [Typical] です。[Typical] に設定すると統計的に予測されるアプリケーションの消費電力が計算され、[Maximum] に設定するとワースト ケースの

消費電力が計算されます。電源ソリューションは [Maximum] の条件にも対応できるのですが、大電流が必要な大規模のデバイスでは、これが問題となる場合があります。

この画面では、周囲温度、ヒートシンク、エアフローなどの動作環境も定義できます。デバイスのジャンクション温度が上昇するにつれて必要な電力は増えるので、この段階で最大周囲温度を定義しておけば、より正確な消費電力予測が得られます。ヒートシンク、エアフロー、またはその両方を使用することになると、消費電力の予測値は小さくなります。

また、この段階では、ザイリンクス ISE® ツールの最適化の設定にも注意する必要があります。エリアの最小化に対するタイミングパフォーマンスなど、適用される最適化方式によってさまざまなインプリメンテーションが生成され、各インプリメンテーションが独自のリソース使用率とファンアウトを持つため、最適化の設定も消費電力予測に大きな影響を与えます。

予測の次の段階では、XPE スプレッドシートの最下部の各タブを順番にクリックし、提案されたソリューションの詳細をできるだけ正確に入力します。できるだけ正確な予測が早期の段階で得られるように、少なくともリソース使用率、クロック周波数、トグルレート、イネーブルレートを定義することが非常に重要です。また、いつでも起こり得る要件の変化に対応できるように、ある程度の余裕を見ておくことをお勧めします。

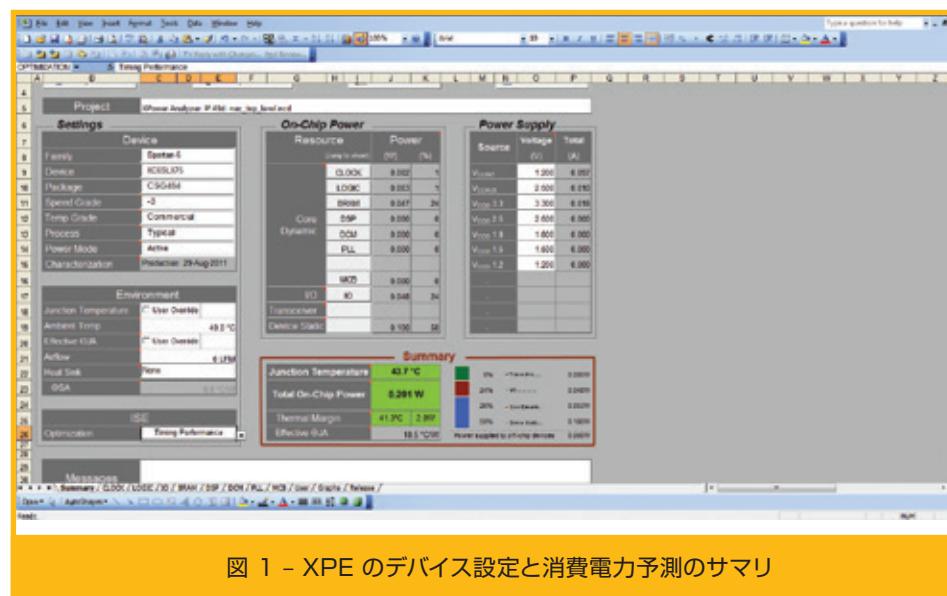

このプロセスにより、図 1 のように、XPE の [Summary] タブに消費電力とジャンクション温度の全体的な予測値が表示されます。

予測が完了したら、後でザイリンクスパワー アナライザー (XPA) で使用できるよう、必要に応じて [Summary] ページの [Export File] オプションを使用して XPE の設定をエクスポートできます。これにより、XPE で最初に予測に使用した設定と、XPA の設定の整合性が確保されます。

RTL の生成、トレイル合成、配置配線へと開発が進むにつれて、より正確な情報が利用可能になるため、予測を最新の状態に保つことが重要です。ハードウェア開発チーム（特に電源エンジニアリング担当グループ）に予測値の変化を伝えることも大事です。電源技術者は、電源レールのワーストケースの最大電圧を、デバイス設計者に伝える必要があります。これによって、予測の精度がさらに向上します。

図 1 - XPE のデバイス設定と消費電力予測のサマリ

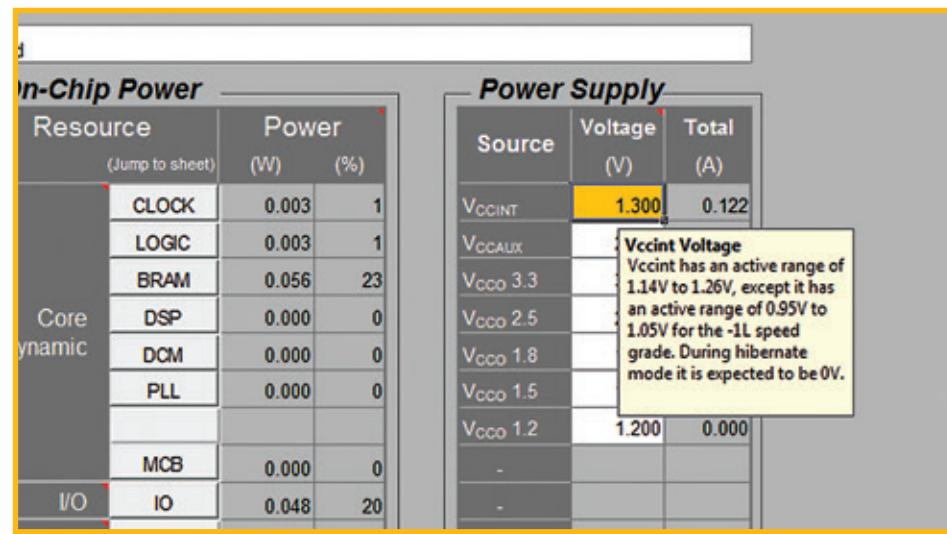

図 2 - 電源電圧が許容範囲から外れたときに表示される警告

上します。ワースト ケースの最大電源電圧が高くなるほど、消費電力は増加します。

XPE はインテリジェントなツールです。ワースト ケースの最大電源電圧がデバイスの許容範囲を超えた場合は、図 2 に示すように、スプレッドシート上の電圧セルをオレンジ色で表示し、警告を発します。

## XPA への移行

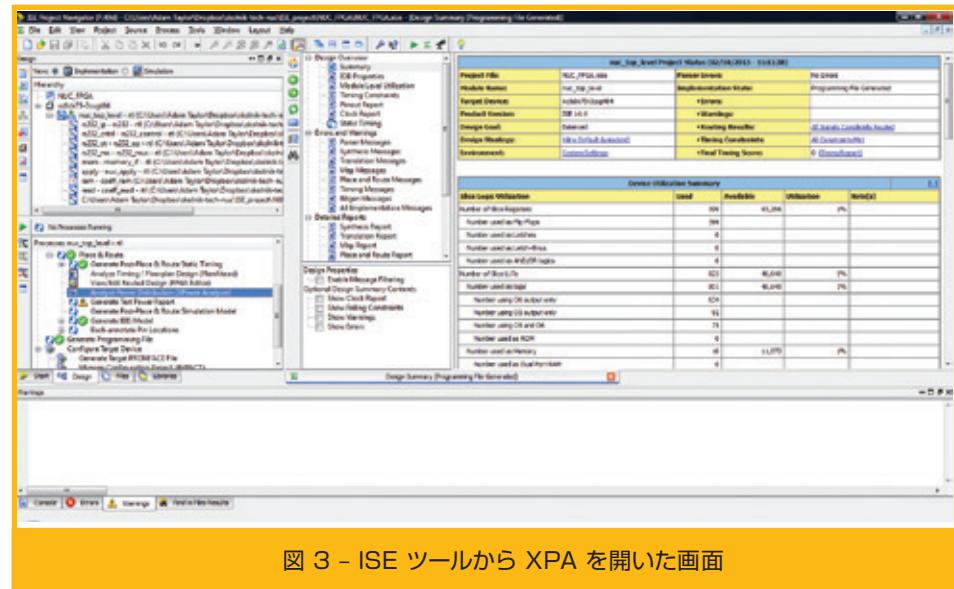

デザインのインプリメントが完了したら、ザイリンクス パワー アナライザーを使用して、非常に正確な消費電力の予測を得ることができます。予測結果の精度は、XPA ツールに入力する設定値によって決まります。XPA を開くには、ISE Design Suite の [Processes]

ウィンドウで [Place & Route] オプションの下の [Analyze Power Distribution] をクリックします（図 3 を参照）。

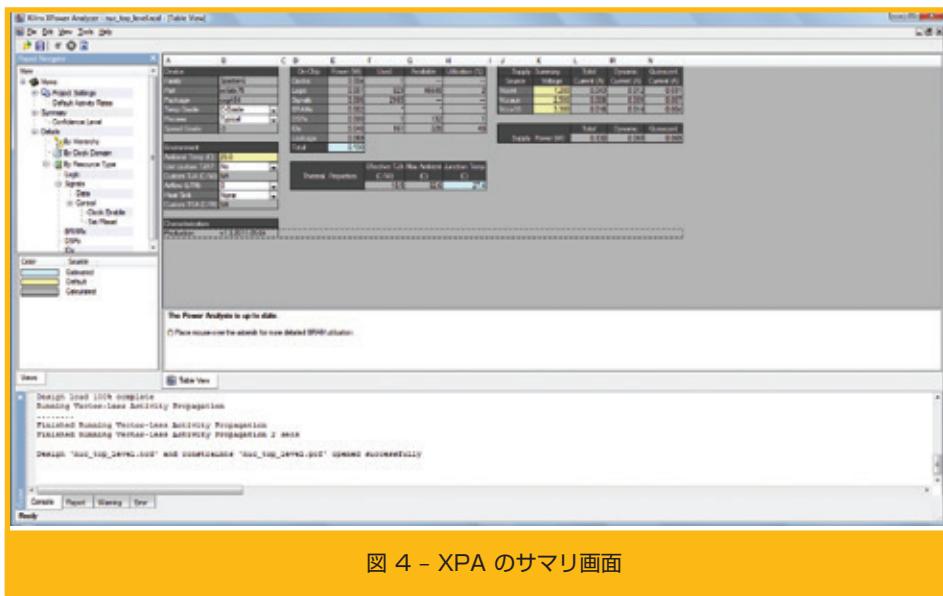

XPA が開くと、XPE のサマリ画面によく似たサマリ画面が表示されます（図 4）。この画面で環境を定義し、追加の設定を作成するか、XPE 解析ツールから設定値をインポートできます。

.xpa ファイルを組み込むか、または新規プロジェクトを開くには、次に挙げるファイルを含むフローに従う必要があります。

- FPGA の物理デザインのインプリメンテーションを定義する NCD (Native Circuit Design) ファイル

- XPE からインポートした設定値を定義する設定ファイル

- クロック情報、マッピング制約、UCF 制約を指定する物理制約ファイル (PCF)

- VCD (Value Change Dump) ファイルまたは SAIF (Switching ActivityInterchange Format) ファイルのいずれかのシミュレーションファイル。

このファイルはご使用のシミュレーションツールで生成できます。XPA は、このファイルからデザインのスイッチング情報を取得します。

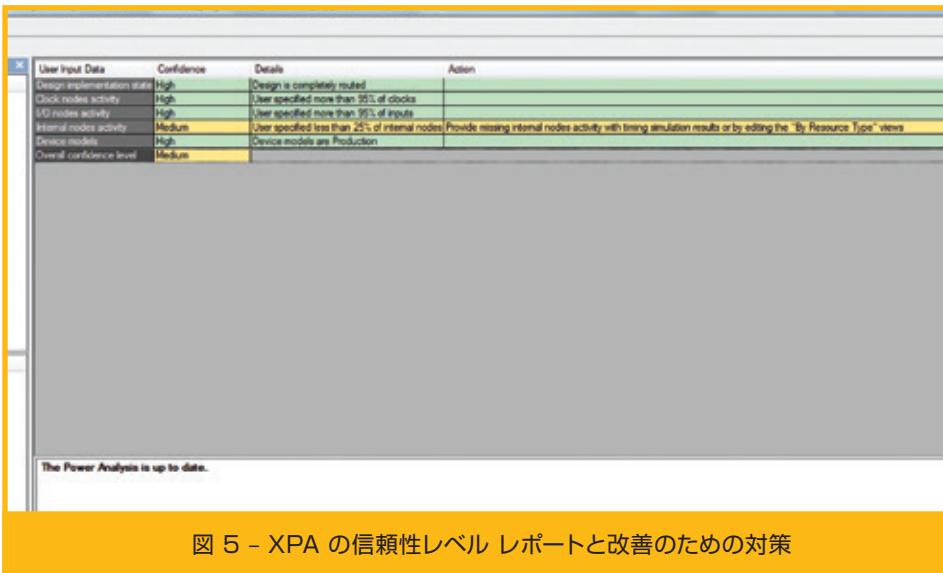

もちろん、最初に指定する情報が多いほど消費電力予測の精度は向上します。XPA は、デザインインプリメンテーションステート、クロックノードのアクティビティ、I/O ノードのアクティビティ、内部ノードのアクティビティ、デバイスモデルの 5 つのカテゴリについて予測の信頼性レベルを低、中、高で示し、設計者をサポートします。

個々の信頼性レベルは、予測の全体的な信頼性レベルに影響を与えます。XPA は、各カテゴリの信頼性レベルを高めることで全体的な信頼性レベルを向上させる対策を表示し、設計者をサポートします（図 5）。

消費電力予測で最高の信頼性レベルを得るには、ゲートレベルのシミュレーションで得られた VCD または SAIF ファイルを組み込む必要があります。これにより、XPA は内部ノードの動作を理解し、より正確な予測を提供します。

シミュレーションから VCD を作成するのは非常に簡単ですが、ご使用のツール (Mentor Graphics 社の ModelSim、ザイリンクスの ISim など) によって、必要なコマンドの形式が多少異なります。ModelSim をご使用の場合は、次の構文で簡単な VCD ファイルを作成できます。

```

vcd file myvcd.vcd

-define the file name and

location if desired

vcd add /memory_if_tb/

uut_apply/*

-the region of the design

that is to be recorded

```

シミュレーションが終了すると、結果は VCD ファイルに保存され、そのファイルを XPA で使用できます。ISim をご使用の場

図 3 - ISE ツールから XPA を開いた画面

## 正確な消費電力予測の 10 の手順

できるだけ正確な消費電力予測をするために、重要な手順のチェックリストを示します。

1. 最初に、ステッピング、スピードグレード、ヒートシンク、エアフロー、周囲温度などの環境設定を正しく行います。

2. プロセスが [Typical] または [Maximum] (ワーストケース) に正しく設定されていることを確認します。

3. 電源電圧をワーストケースの最大電圧に設定します。

4. 正確なトグルレート、ファンアウト、イネーブルレート、I/O プロパティ、クロックレートを指定します。

5. VCD/SAIF シミュレーションファイルを使用して、デザインのパフォーマンスに関する最善の情報を XPA に提供します。最善の結果を得るには、ゲートレベルのシミュレーションから得られたファイルが必要です。

6. ハードウェアデザインと FPGA デザインが進むにつれて、消費電力予測を頻繁に更新し、最新の状態に保ちます。

7. アプリケーションの要件の変化に対応できるように、消費電力予測に余裕を見ておきます。

8. XPA と XPE の両方で、I/O の終端方式と負荷容量を正しく定義します。

9. XPA の報告する信頼性レベルが高いことを確認します。

10. 電源ソリューションがデバイスと信頼性に関するすべての電力要件に適合しており、負荷容量またはそれに近い値で動作していないことを確認します。

今は、コマンドの形式が次のように多少異なります。

```

vcd dumpfile myvcd.vcd

-define the file name and

location if desired

vcd dumpvars -m

/memory_if_tb/uut_apply

```

*-the region of the design

that is to be recorded*

Run Simulation

```

vcd dumpflush

-save results to the vcd

file created

```

図 4 - XPA のサマリ画面

図 5 - XPA の信頼性レベル レポートと改善のための対策

これらのシミュレーションツールは、より高度なコマンドを多数備えているので、それらのコマンドを使用して VCD を生成することも可能です。詳細は、各ツールのマニュアルを参照してください。

VCD シミュレーションファイルを組み込むことで、消費電力予測の信頼性レベルは向上します。シミュレーションの実行に長時間かかる場合など、シミュレーション結果を利用できない場合は、XPA は内部解析エンジンを使用して予測を実行します。この場合、正確な結果を得るには、トグルレートとイネーブルレートを指定することが重要です。

XPE と同じように、XPA でもワーストケースの最大電源電圧を指定することは重

要です。また、XPA デザインをエクスポートして XPE に戻し、エンジニアリングチームがより実験的な変更を試して、消費電力とジャンクション温度の予測値に与える影響を確認することも可能です。

### 予測が要件を満たさない場合の対策

シミュレーション結果を組み込み、その他の情報を指定することで、消費電力とジャンクション温度の予測に高い信頼性レベルが実現されるでしょう。理想を言えば、これによって予測結果はアプリケーションの許容範囲内に収まるはずです。しかし、結果がアプリケーションの許容範囲を超えた場合は、デザインが電力バジェットやジャンクション温

度の要件を確実に満たすために、どのような対策をとれるでしょうか。

希望の結果を得るために、デザインソース、インプリメンテーション、または（ジャンクション温度の場合）物理モジュールのデザインの 3箇所でデザインを改善できます。

デザインソースでは、次の手順を実行できます。

1. 非同期リセットを削除する。

2. 大きな組み合わせ関数の間にパイプライン段を挿入する。

3. 推論またはインスタンシエーションにより、デバイス内で利用可能な専用リソースを使用していることを確認する。

合成と配置配線で利用できる対策には、次のものがあります。

1. 最適化方式をエリアの最小化または電力削減に設定する。

2. デザイン制約を検討し、必要以上にデバイスを制約していないことを確認する。

3. 高ファンアウトのバスのファンアウトを制限する。

4. ステートマシンなどの回路には、できるだけ RAM を使用する。

5. リタイミングが有効になっていることを確認する。

上記の手順により、おそらく消費電力とジャンクション温度の予測値は下がるはずです。上記の手順で不十分な場合は、必要に応じてヒートシンクまたは強制エアフローを使用し、ジャンクション温度を下げるすることができます。ただし、この対策をとると、プロジェクトの機械的デザインに影響を与えます。

### 正確な予測

ザイリンクス パワー エスティメーターとザイリンクス パワー アナライザーを使用して、FPGA デザインの正確な消費電力予測が得られます。2つのツールの間では情報の共有も簡単に行えます。消費電力予測の精度は、シミュレーションから得られるデータと電源の開発担当チームが提供するデータの品質によって決まります。

要件の変化に対応できるように、またソリューションが電源の供給電流と電源電圧のランプレートに依存する電力に対応できるように、十分な余裕を見ておくことをお勧めします。●

## ザイリンクス販売代理店 オリジナル トレーニング

販売代理店各社のオリジナルトレーニングの内容およびスケジュールは、各社のWebサイトをご覧ください。

アヴネット・インターニックス

[avnetinternix.co.jp/training.aspx](http://avnetinternix.co.jp/training.aspx)

新光商事

[xilinx.shinko-sj.co.jp/training/index.html](http://xilinx.shinko-sj.co.jp/training/index.html)

東京エレクトロンデバイス

[ppg.teldevice.co.jp/](http://ppg.teldevice.co.jp/)

パルテック

[www.paltek.co.jp/seminar/index.htm](http://www.paltek.co.jp/seminar/index.htm)

詳細とご登録はこちらから

[Japan.xilinx.com/training/](http://Japan.xilinx.com/training/)

## Latest and Greatest from the Xilinx Alliance Program Partners

# ザイリンクス アライアンス プログラム パートナーが 最新の優れたテクノロジを提供。

## ザイリンクス アライアンス プログラム パートナーのエコシステムが 提供する最新テクノロジのハイライトをご紹介します。

ザイリンクス アライアンス プログラムは、ザイリンクスと協力して All Programmable テクノロジの開発を促進している認定企業で構成される世界的なエコシステムです。ザイリンクスは、オープン プラットフォームと標準規格に基づいてこのエコシステムを構築し、顧客のニーズへの対応と長期的な成功のサポートを取り組んでいます。IP プロバイダー、EDA ベンダー、エンベデッド ソフトウェア プロバイダー、システム インテグレーター、ハードウェア メーカーで構成されるアライアンス メンバーは、皆様の設計の生産性向上の加速とリスクの軽減をサポートしています。ここではメンバー企業 5 社のレポートを紹介します（この情報は2013年3月現在の、各社の情報をベースに書かれています）。

### MATHWORKS 社のカスタム ビジョン アルゴリズム

MATLAB® ツールと Simulink® ツールのプロバイダーである MathWorks 社（マサチューセッツ州ナティック）は、エンベデッド ビジョン向けにザイリンクスのハードウェアと組み合わせて使用できる各種のアドオン製品を提供しています。同社の Computer Vision System Toolbox は、コンピューター ビジョン システムおよびビデオ処理システムのデザインとシミュレーション用のアルゴリズムとツールを提供します。HDL Coder は、MATLAB 関数、Simulink モデル、Stateflow チャートから、移植可能で合成可能な Verilog および VHDL コードを生成します。HDL Verifier は、FPGA インザ ループ (FIL) テストにより、ザイリンクス FPGA ボード上の HDL コードの検証を自動化します。また、MathWorks 社は、先頃、

ザイリンクス Zynq™ - 7000 All Programmable SoC と連携して動作するハードウェア サポート パッケージをリリースしました。

「Smarter Vision アプリケーションは着実に進化しており、解析、認識、追跡などの新機能が追加されています」と、MathWorks 社のシニア ストラテジストである Ken Karnofsky 氏は述べています。「これらの機能を実現するには、システム パフォーマンスの向上と、ハードウェアおよびソフトウェア インプリメンテーションにおけるデザインの柔軟性向上が必要です。この数年間、MathWorks 社とザイリンクスは、ハード

**Ken Karnofsky 氏**

MathWorks 社