- テクノロジ

- PCI Express

概要

PCI Express® (PCIe®) は、通信、データセンター、エンベデッド、テスト/測定、防衛など、さまざまな市場の幅広いアプリケーションに対応できる汎用シリアル インターコネクトです。また、ペリフェラル デバイス インターコネクト、チップ間インターフェイス、およびその他さまざまなプロトコル規格へのブリッジとしても利用できます。

AMD は、多くのデバイスで、ハード化したサブシステムとして高性能で低消費電力な PCI Express 用統合ブロックを提供しています。

また、PCI Express 用統合ブロックを活用する PCIe DMA および PCIe ブリッジのハード/ソフト IP ブロック、PCI Express コネクタ付きボード、コネクティビティ キット、リファレンス デザイン、ドライバー、および PCIe ベース デザインの実装を容易にするツールも提供しています。

デバイス ファミリを選択して、各ファミリの AMD PCIe ソリューション ポートフォリオをご覧ください。

Versal ソリューション

データセンター、通信、エンベデッド アプリケーションでは、PCI Express® 仕様に対応できるシステムが求められています。Versal™ アーキテクチャでは複数の接続オプションを利用できるため、開発者は最先端規格に準拠したインターフェイスを活用しながら、競合を凌ぐ高性能製品の開発に注力できます。Versal アーキテクチャに統合された PCI Express ブロックは、完全なソフト IP ソリューションよりも使いやすく効率的で、はるかに優れた性能を提供します。Versal アーキテクチャには、PCIe デザイン向けに 5 つのタイプの統合ブロックがあります。

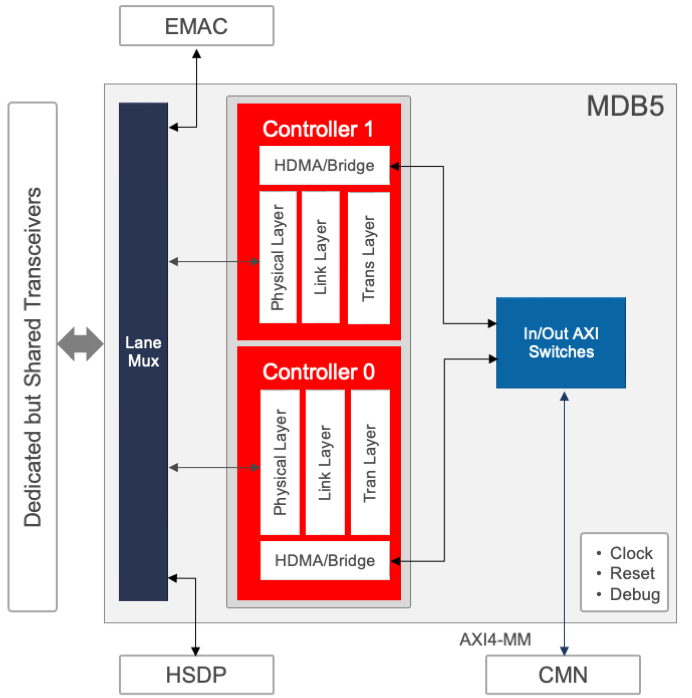

- MDB5: DMA/ブリッジを備えた PCI Express Rev. 5.0 用の統合ブロック

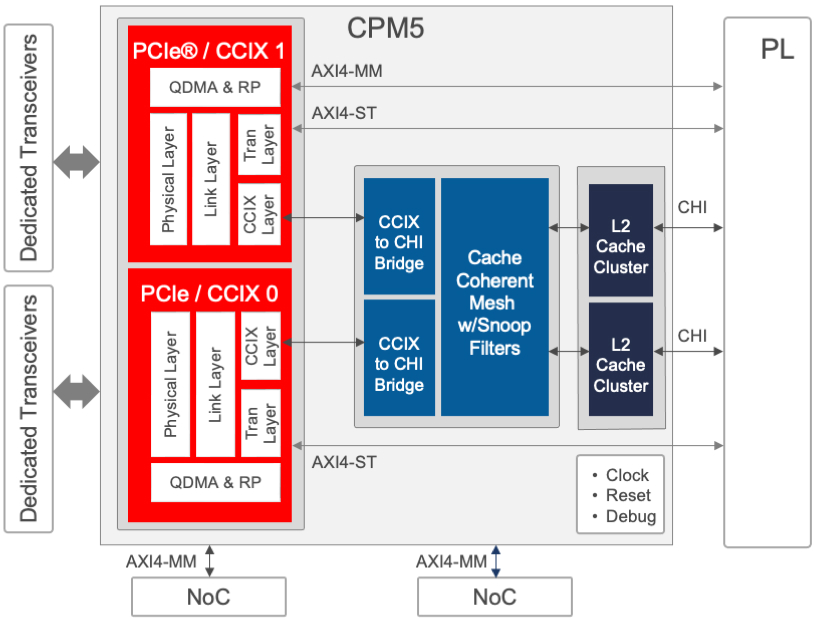

- CPM5: DMA/ブリッジを備えた PCI Express Rev. 5.0 用の統合ブロック

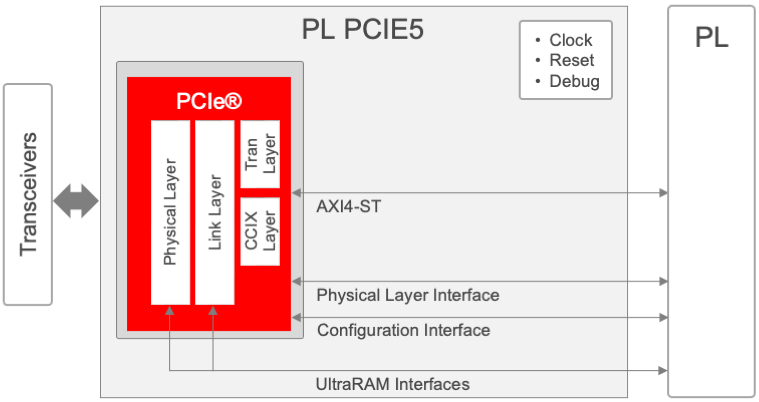

- PL PCIE5: PCI Express Rev. 5.0 用統合ブロック

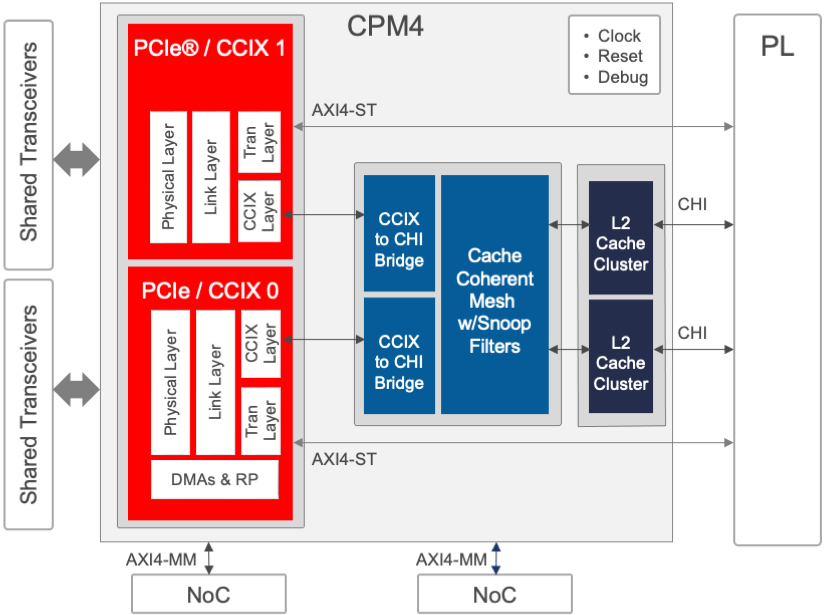

- CPM4: DMA/ブリッジを備えた PCI Express Rev. 4.0 用の統合ブロック

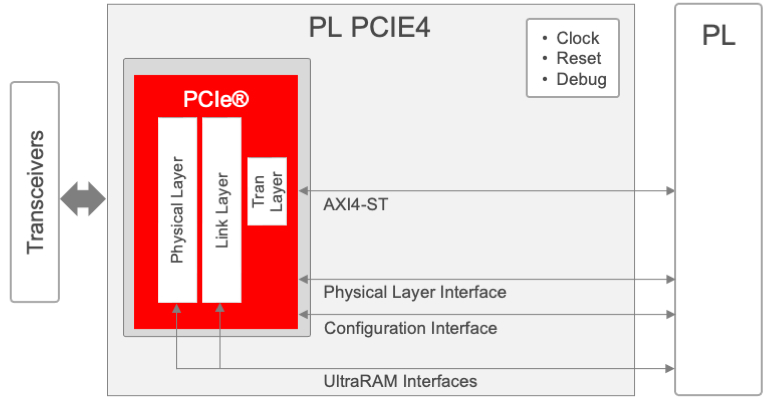

- PL PCIE4: PCI Express Rev. 4.0 用の統合ブロック

MDB5、CPM5、PL PCIE5、CPM4、および PL PCIE4 は、GTYP や GTY トランシーバーと組み合わせて使用することで、仕様どおりのデータ レートでインターフェイスを動作させることができます。1 レーン (Gen1x 1) 構成から規定された最大構成まで 1 レーンあたり 2.5 GT/s からの動作範囲をサポートします。たとえば、8 レーン (Gen5x 8) の場合は 1 レーンあたり 32 GT/s、16 レーン (Gen4x16) の場合は 1 レーンあたり 16 GT/s で動作可能です。

次の表では、Versal アーキテクチャで使用できる PCI Express 用統合ブロックの特徴をまとめています。現在利用できるデバイス、パッケージ、スピード グレードの組み合わせで有効なリソースおよび機能については、『Versal アーキテクチャおよび製品データシート: 概要』 (DS950) を参照してください。

Versal アーキテクチャに統合された PCI Express 用ブロック |

|||||

|---|---|---|---|---|---|

MDB5 |

CPM5 |

PL PCIE5 |

CPM4 |

PL PCIE4 |

|

| 関連 仕様 |

PCIe Rev. 5.0 | PCIe Rev. 5.0 | PCIe Rev. 5.0 |

PCIe Rev. 4.0 |

PCIe Rev. 4.0 |

| 最大 PCIe リンク構成 |

Gen5x4 2 x Gen5x2 Gen5x2 |

2 x Gen5x8 Gen4x16 2 x Gen4x 8 |

Gen5x4 Gen4x8 Gen 3x16 |

Gen4x16 2 x Gen4x8 |

Gen4x8 Gen 3x16 |

| PCIe ポート サポート タイプ |

EP、RP | EP、RP、 スイッチ |

EP、RP、 スイッチ |

EP、RP、 スイッチ |

EP、RP、 スイッチ |

| 主な PCIe の 機能 |

SR-IOV 8PF/64VF |

SR-IOV 16PF/4KVF |

SR-IOV 8PF/4KVF |

SR-IOV 4PF/252VF |

SR-IOV 4PF/252VF |

| 統合 DMA/ブリッジ | 2 ブリッジ (1 つまたは 2 つを選択)、HDMA (オプション) | 1 つまたは 2 つを選択: HDMA (オプション) | - | いずれか 1 つを選択 QDMA/ブリッジ (オプション) XDMA/ブリッジ (オプション) |

- |

これらのブロック (MDB5、CPM5、PL PCIE5、CPM4、PL PCIE4) は、少ないリンク構成で使用できるため、コスト重視の製品デザイン、小規模フォームファクターへの対応、ボードの複雑性緩和、消費電力削減が可能になります。また、リンク構成が削減されることで、プログラマブル ロジックのリソース使用率を削減できる場合もあります (これは、統合ブロックの適用拡大に使用するソフト IP の性質に依存します)。CPM5、PL PCIE5、CPM4、および PL PCIE4 は、エンドポイント (EP)、ルート ポート (Rp)、およびスイッチ ポート タイプとして構成できます。詳細は、『Versal Adaptive SoC Integrated Block for PCI Express LogiCORE IP 製品ガイド』 (PG343) および『Versal Adaptive SoC CPM Mode for PCI Express 製品ガイド』 (PG346) を参照してください。MDB5 は、エンドポイント (EP) およびルート ポート (RP) タイプとして構成可能であり、統合 DMA/ブリッジ ソリューションを使用する必要があります。

AMD は、Versal アーキテクチャに統合した PCI Express 用ブロックと検証済みの高性能な DMA/ブリッジ サブシステムを提供しているため、開発者は付加価値の設計に多くの時間を費やすことができます。DMA/ブリッジ サブシステムのオプションは次のとおりです。

- MDB5 は、PCI Express 用のコントローラーを 2 つ統合し、HDMA/ブリッジ サブシステムのインスタンスを 2 つ統合しています。統合された DMA の使用は任意であり、各インスタンスは個別にカスタマイズ可能です。HDMA サブシステムは、統合されたプロセッサや AXI インターコネクトの密結合を提供します。このサブシステムは AXI ブリッジの機能も提供します。データ移動には、プログラマブル NoC を使用するメモリマップド方式を採用できます。

- CPM5 は、PCI Express 用のコントローラーを 2 つ統合し、また QDMA/ブリッジ サブシステムのインスタンスを 2 つ統合しています。統合された DMA の使用は任意であり、各インスタンスは個別にカスタマイズ可能です。QDMA サブシステムは、大量のデータを低レイテンシで移動させるための拡張性に優れたキューベースの DMA を提供する上、エンタープライズ クラスの製品で必要とされる物理/仮想機能をいくつかサポートします。データ移動には、プログラマブル NoC を使用するメモリマップド方式、またはストリーミング方式を採用して、Versal アダプティブ SoC のプログラマブル ロジックへ送られます。また、このサブシステムには、AXI インターコネクトへのブリッジ機能も含まれています。

- CPM4 は、PCI Express 用のコントローラーを 2 つ統合し、また QDMA/XDMA とブリッジ サブシステムのインスタンスを 1 つ統合しています。統合された DMA の使用は任意であり、使用する場合は CPM5 の場合のように QDMA サブシステムとして、または XDMA サブシステムとして構成可能です。データ移動には、プログラマブル NoC を使用するメモリ マップド方式、またはストリーミング方式を採用して、Versal アダプティブ SoC のプログラマブル ロジックへ送られます。また、このサブシステムには、AXI インターコネクトへのブリッジ機能も含まれています。

- PL PCIE5 および PL PCIE4 は、PCI Express 用の個別コントローラーであり、ソフト IP として実装する DMA/ブリッジ サブシステムと組み合わせて使用します。これらは Vivado™ Design Suite の IP カタログから無料で利用できます。

ほとんどの開発者にとって、手軽に利用できるこの高性能 DMA/ブリッジ サブシステムは、高速データ通信をすばやく構築するためのインフラとして有効です。詳細は、『Versal Adaptive SoC DMA and Bridge Subsystem for PCI Express 製品ガイド』 (PG344) および『Versal Adaptive SoC CPM DMA and Bridge Mode for PCI Express 製品ガイド』 (PG347) を参照してください。また、ドライバーやアプリケーション ソフトウェアへの投資を最小限に抑えて、DMA/ブリッジ サブシステムを独自構築する場合や、エンド アプリケーションの詳細知識を活かして機能をカスタマイズまたは最適化する場合には、CPM5 および CPM4 に含まれる DMA/ブリッジをバイパスすることも可能です。完全なカスタム ソリューションを実装するため最大限の柔軟性を重視する方には、Vivado Design Suite IP カタログで PCI Express 用のソフト IP コア PHY を提供しています。これらを使用することで、PCI Express 用のコントローラーを独自開発して、GTYP および GTY トランシーバーへ接続することが可能になります。

サポート製品およびテクノロジ

PCI Express 用高速シリアル トランシーバー

UltraScale+ ソリューション

AMD の 16 nm UltraScale+™ デバイスには、今日のデータセンター、通信、およびエンベデッド アプリケーションで必要とされる多くの PCI Express® 機能が統合されています。UltraScale+ デバイスは、3 つの統合ブロック (PCIE4、PCIE4C、PCIE4CE) を使用します。

PCIE4 ブロックは、PCI Express Base Specification v3.1 に準拠しており、最大で Gen3x16 まで対応しています。また、より狭いリンク幅やより低速向けに設定することも可能です。PCIE4 ブロックは、Gen4 動作をサポートしていません。

PCIE4C ブロックは、最大 8.0 GT/s (Gen3) に対応する PCI Express Base Specification v3.1、および最大 16.0 GT/s (Gen4) に対応する PCI Express Base Specification v4.0 に準拠しています。また、最大 16.0 GT/s のスピードをサポートする CCIX Base Specification v1.0 Version 0.9 とも互換性があります。このブロックは、Gen3 で最大 16 レーン、Gen4 で最大 8 レーンをサポートしますが、リソースおよび消費電力の削減を目的としてより低いレーン幅用にも構成できます。

PCIE4CE ブロックは、PCI Express Base Specification v4.0 に準拠しており、最大で 16.0 GT/s (Gen4) まで対応しています。この PCIE4CE ブロックは、Gen3 で最大 16 レーン、Gen4 で最大 8 レーンをサポートしますが、リソースおよび消費電力の削減を目的としてより低いレーン幅用にも構成できます。一部のデバイスには統合ブロックのリビジョンが 1 つしか含まれていませんが、複数のリビジョンが存在するデバイスもあります。

UltraScale™ アーキテクチャが備える PCIe® 統合ブロックはすべて、エンドポイントまたはルート ポートとして構成可能です。ルート ポートは、ルート コンプレックスのベースを構築するために使用でき、PCI Express プロトコルを用いたチップ間のカスタム通信を可能にするだけでなく、イーサネット コントローラーやファイバー チャネル HBA、NVMe SSD などの ASSP エンドポイント デバイスを FPGA、MPSoC、または RFSoC に接続します。

Integrated Block for PCI Express IP は、ハードウェア化されており、次をサポートします。

- 統合ブロックのすべてのリビジョンは最大 Gen3x16 の機能に対応しており、PCIE4C ブロックを備えるデバイスでは Gen4x8 との互換性があり、PCIE4CE ブロックを備えるデバイスでは Gen4x8 に準拠しています。サポートされている特定のリンク幅およびスピードの詳細は、該当する IP の製品ガイド (PG213、PG195、または PG302) を参照してください。Gen4x8 との PCIE4C ブロックの互換性の詳細は、『UltraScale+ Devices Integrated Block for PCI Express 製品ガイド』 (PG213) を参照してください。利用可能なリンク幅は、利用可能なトランシーバー数とパッケージのピン配置によって異なります。

- SR-IOV (Single Root I/O Virtualization) で IO リソースを共有するために必要な 4 つの物理機能と 252 の仮想機能をサポート

- より多くの PCIe 要求に対応するための追加タグで、システム全体の性能が向上

- MSI-X テーブルの統合

その他、AMD ではソフト IP として高性能 DMA およびブリッジ ソリューションを提供しています。

- AMD の QDMA IP サブシステムは、PCIe 対応の主な DMA ソリューションです。QDMA は、スケーラブルなキューで複数の物理/仮想機能へのアクセスを可能にする SR-IOV をサポートします。XDMA は AXI ブリッジの機能も提供します。詳細は、『QDMA Subsystem for PCI Express 製品ガイド』 (PG302) を参照してください。

- AMD の XDMA IP サブシステムは、PCIe 向けの既存 DMA ソリューションで、幅広く使用されています。XDMA は AXI PCIe ブリッジの機能も提供します。詳細は、『DMA/Bridge Subsystem for PCI Express 製品ガイド』 (PG195) を参照してください。

完全なカスタム ソリューションを実装するため最大限の柔軟性を重視する方には、PCI Express 用のソフト IP コア PHY を提供しています。これらを使用することで、PCI Express 用のコントローラーを独自開発して、トランシーバーへ接続することが可能になります。

サポート製品およびテクノロジ

PCI Express 用高速シリアル トランシーバー

PCI Express 用評価キット (AMD)

UltraScale ソリューション

AMD の 20 nm UltraScale™ デバイスには、今日のデータセンター、通信、およびエンベデッド アプリケーションで必要とされる多くの PCI Express® 機能が統合されています。

Integrated Block for PCI Express IP は、ハードウェア化されており、次をサポートします。

- ネイティブの Gen3x8* 統合 PCIe® ブロック

- PCIe 要求に対応する 64 のタグ

- 複数ベクター MSI (最大 32 ベクター) および MSI-X

- 詳細は、『UltraScale Devices Gen3 Integrated Block for PCI Express 製品ガイド』 (PG156) を参照してください。

その他、AMD ではソフト IP として高性能 DMA およびブリッジ ソリューションを提供しています。

- AMD の XDMA IP サブシステムは、量産向けの PCIe DMA ソリューションで、幅広く使用されています。詳細は、『DMA/Bridge Subsystem for PCI Express 製品ガイド』 (PG195) を参照してください。

- AMD は、量産向けの AXI Memory Mapped to PCI Express Bridge IP を提供しています。詳細は、『AXI Bridge for PCI Express Gen3 Subsystem 製品ガイド』 (PG055) をご覧ください。

*サポートされている特定のリンク幅およびスピードの詳細は、該当する製品ガイド (PG156、PG195、または PG194) を参照してください。

サポート製品およびテクノロジ

7 シリーズ ソリューション

AMD の 28 nm 7 シリーズ デバイスには、今日のデータセンター、通信、およびエンベデッド アプリケーションで必要とされる多くの PCI Express® 機能が統合されています。

Integrated Block for PCI Express IP は、ハードウェア化されており、次をサポートします。

- ネイティブの Gen3x8* 統合 PCIe® ブロック

- 64 ビットおよび 128 ビット データ幅

- 詳細は、『7 Series FPGAs Integrated Block for PCI Express 製品ガイド』 (PG054) を参照してください。

その他、AMD ではソフト IP として高性能 DMA およびブリッジ ソリューションを提供しています。

- AMD の XDMA IP サブシステムは、量産向けの PCIe DMA ソリューションで、幅広く使用されています。詳細は、『DMA/Bridge Subsystem for PCI Express 製品ガイド』 (PG195) を参照してください。

- AMD は、量産向けの AXI Memory Mapped to PCI Express Gen2 IP を提供しています。詳細は、『AXI Memory Mapped to PCI Express (PCIe) Gen2 v2.9 LogiCORE IP 製品ガイド』 (PG055) を参照してください。

*サポートされている特定のリンク幅およびスピードの詳細は、該当する製品ガイド (PG054、PG055、または PG195) を参照してください。