# Zynq RFSoC DFE (デジタル フロントエンド) 製品発表

# ザイリンクス、5G NR 大規模運用に対応する Zynq RFSoC DFE を発表 ハード化された IP の画期的な統合

第 2 次 5G NR 要件を満たし、

2 倍の単位ワットあたり性能を達成\*

柔軟性とコストのバランスが取れた

5G NR 無線ソリューション

5G の進化に遅れを取らない

適応型ハードウェア

ソフト ロジックより多数のハード IP を統合した、新しいクラスのデバイス

\* 消費電力および性能を Zynq RFSoC Gen3 と比較

# 現在、そして将来的市場ニーズに対応するポートフォリオ

性能

4GHz の

アナログ帯域幅

5GHz の

アナログ帯域幅

6GHz の

アナログ帯域幅

7.125GHz の

アナログ帯域幅

ハード化された DFE サブシステム

現在だけではなく、将来的

5G NR 要件に対応

- ✓ チャネルあたり処理能力の向上

- ✓ 瞬時帯域幅の拡大

- ✓ より多くの機能を統合

- ✓ 所定のユース ケースで DC 電力を半減

- ✓ 大規模量産時の高コスト効果

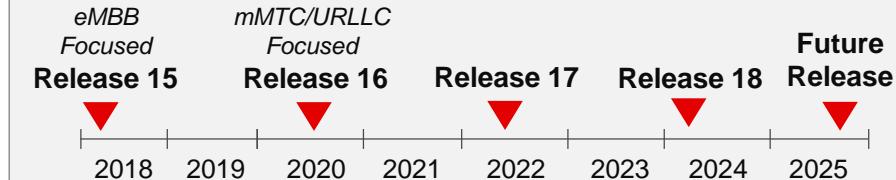

5G NR 初期量産の大半が Zynq MPSoC/RFSoC を採用

2018

2019

2020

2021

# さまざまなユースケースと新しい要件により、4G よりも複雑化する 5G

## 多数同時接続、mMTC (Massive Machine Type Communication)

- ▶ 低消費電力伝送

- ▶ 100 倍の接続デバイス数

## 高速大容量、eMBB (Enhanced Mobile Broadband)

- ▶ スペクトル効率

- ▶ 新しいスペクトル帯域

## EVOLVING STANDARDS

## 超高信頼低遅延、URLLC (Ultra-Reliable & Low Latency Communication)

- ▶ 確定的なレイテンシ

- ▶ 低いエラー率

多様なユースケースの進化に対応できる適応型プラットフォームが必要

# 5G 市場の混乱により新たな通信事業者とプロバイダーが登場

## 4G

### 柔軟性のない市場

- ▶ 4G 市場唯一のユースケース: モバイル データ

- ▶ 通信事業者が消費者にデータを販売

- ▶ 通信事業者が従来のハードウェア OEM でネットワークを構築

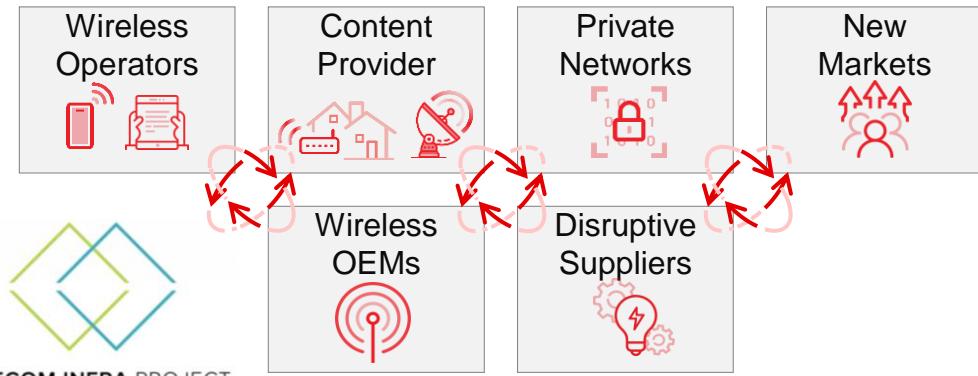

## 5G が可能にする

### 新たなビジネス モデルと競争

- ▶ O-RAN と TIP による既成ビジネス モデルの破壊とより小規模で多様なサプライヤー ベースを可能に

- ▶ 新規参入通信事業者、MVNO、ケーブルおよび衛星通信がスペクトルを獲得してモバイル通信事業者に

- ▶ プライベート ネットワークでは 5G の利点を活かしてエンタープライズ顧客向けに独自ソリューションを構築

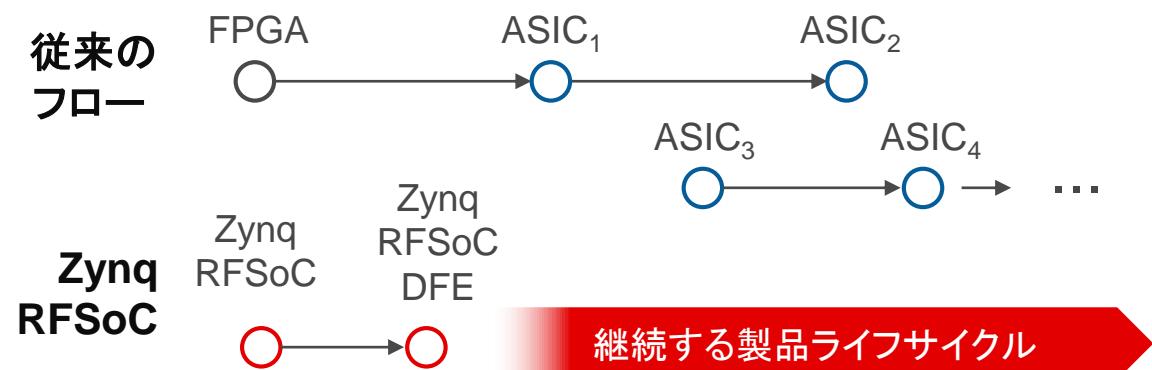

Zynq RFSoC DFE は、従来型 OEM と新規プロバイダーの両者にとって ASIC に代わるソリューション

# 5G の多様な要件とさらなる複雑化

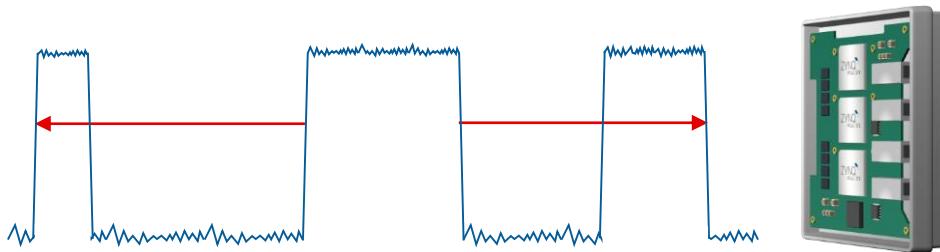

## 帯域幅要件と 1 ワットあたり性能要件の拡大

Zynq RFSoC DFE は無線コアをハード化して

ASIC に匹敵する性能と消費電力を実現

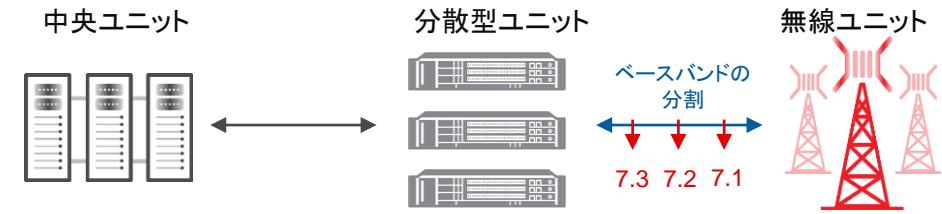

## O-RAN によるディスアグリゲーション RAN

Zynq RFSoC DFE の柔軟性により、無線ユニットと

分散型ユニットでベースバンド処理の分割が可能に

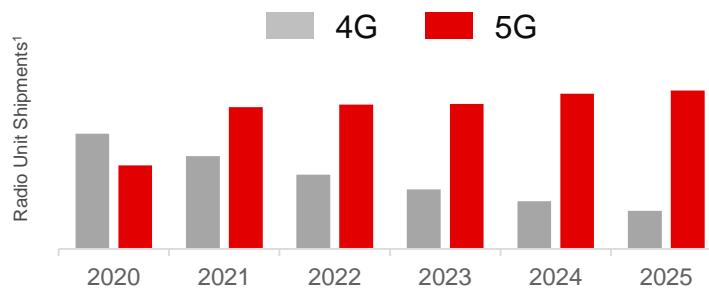

## 4G と 5G の両方に対応する必要

Zynq RFSoC DFE は LTE および 5G に対応

RAN は両方をサポート

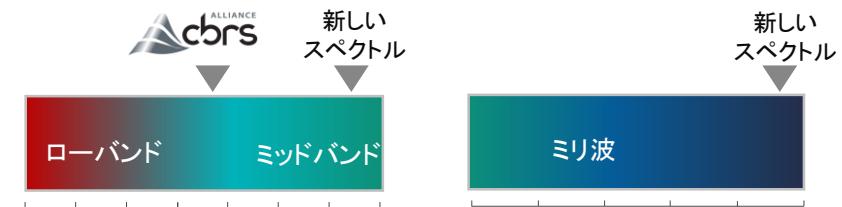

## 変動するスペクトル

Zynq RFSoC DFE は、FR1 でのダイレクト RF マルチバンド

(トライバンド) と最適化されたミリ波インターフェイスを提供

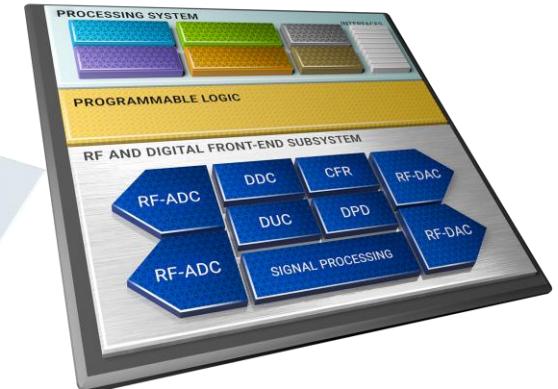

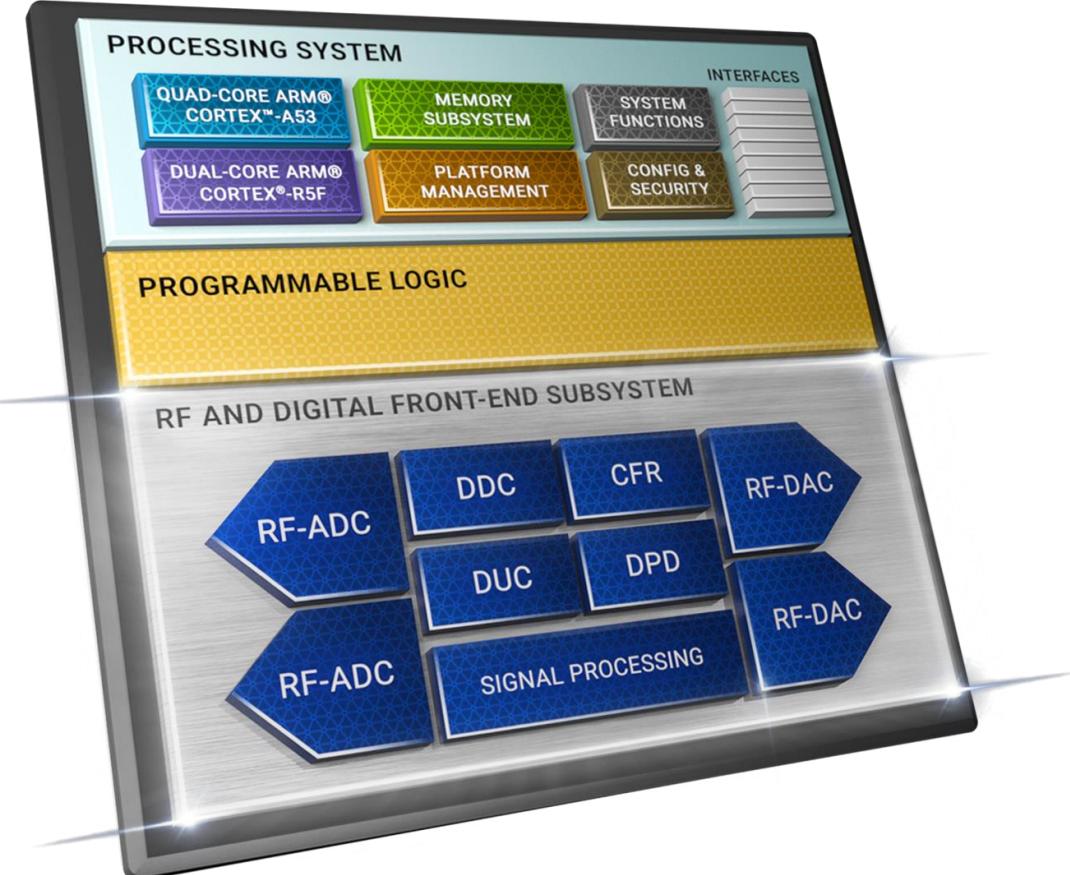

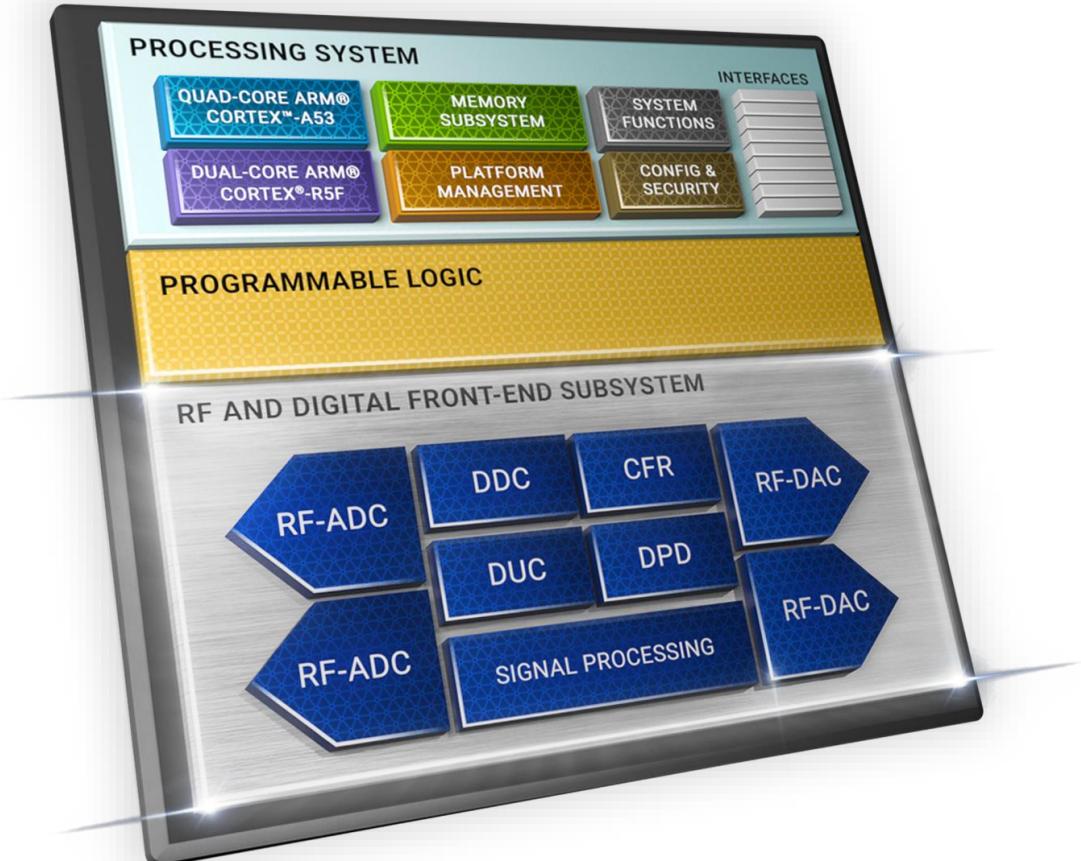

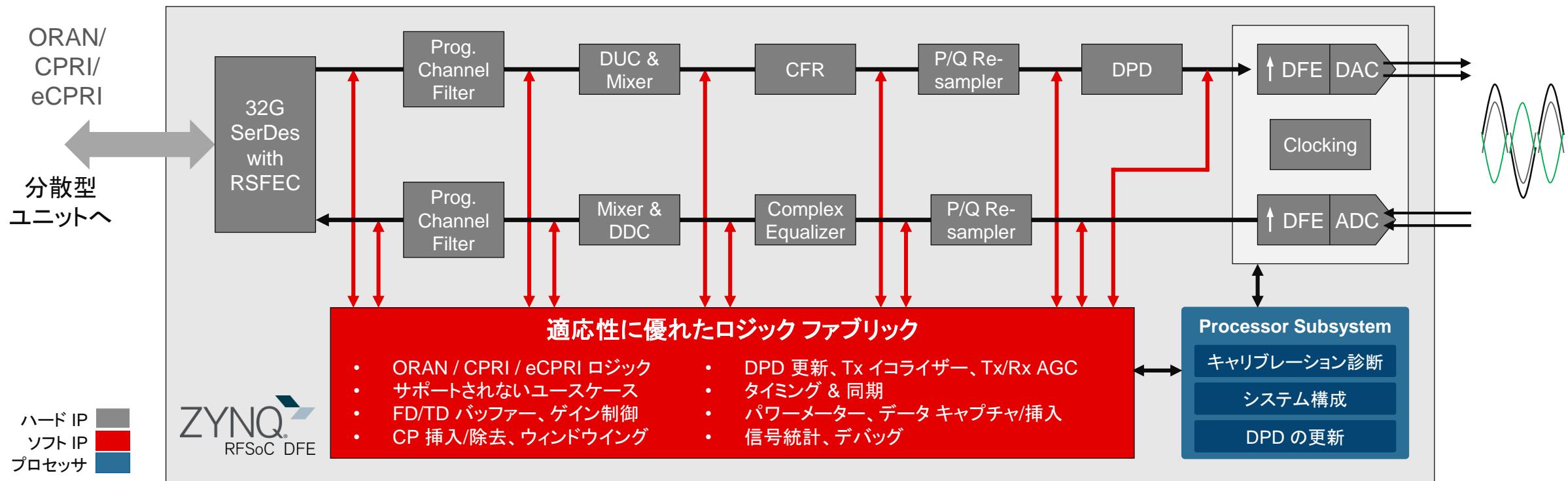

# Zynq RFSoC DFE: 無線サブシステムがハード化された適応型 SoC

適応型 SoC

Arm プロセッシング システム • UltraScale+ プログラマブル ロジック • 32G SerDes

無線サブシステムのハード化

3GPP 規格に準拠した検証済みの

ハード無線コア

運用実績のある

ザイリンクスのソフト IP がベース

4G LTE、5G NR、および

カスタム要件に合わせて構成可能

# Zynq RFSoC DFE: 無線サブシステムがハード化された適応型 SoC

無線サブシステムのハード化

シングル チップ 8T8R FDD/TDD

7.125GHz ダイレクト RF 帯域幅

ダイレクト RF DAC/ADC

従来型/新型 (400MHz) GaN PA のサポート

デジタル プレディストーション (DPD)

最大 400MHz の瞬時帯域幅

クレストファクターの低減 (CFR)

マルチキャリア、マルチバンドのサポート

DUC/DDC<sup>1</sup>

リサンプリング、イコライザー

信号処理 IP

Arm プロセッシング システム • UltraScale+ プログラマブル ロジック • 32G SerDes

1: デジタル アップ コンバージョン/デジタル ダウン コンバージョン

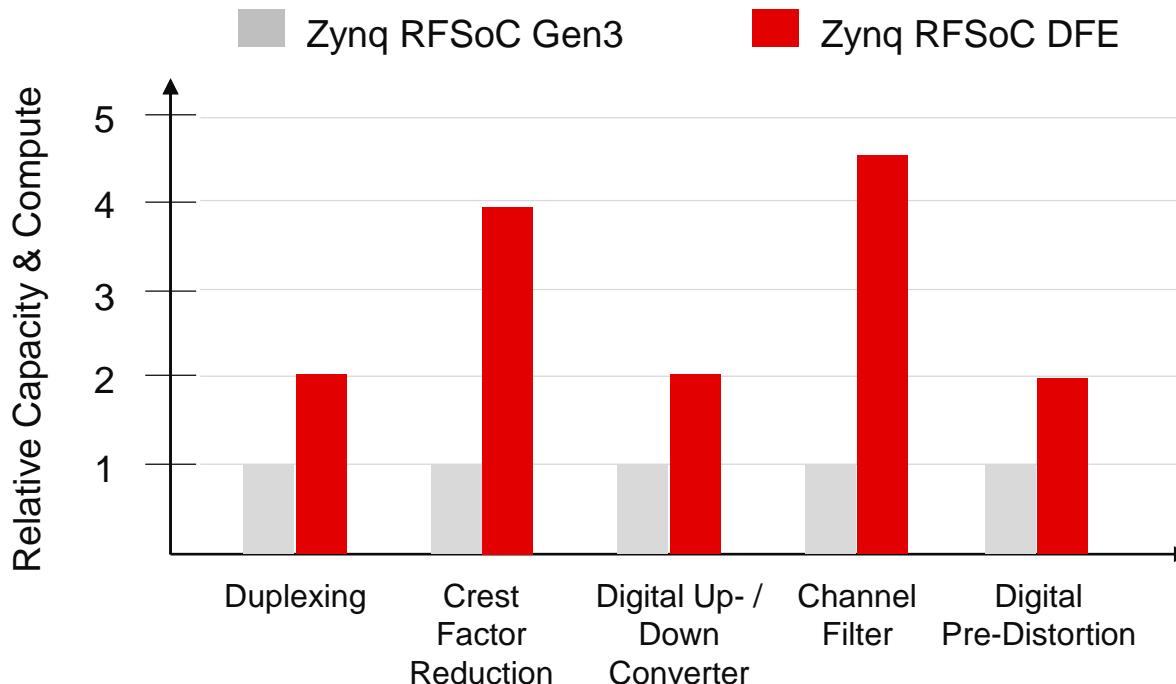

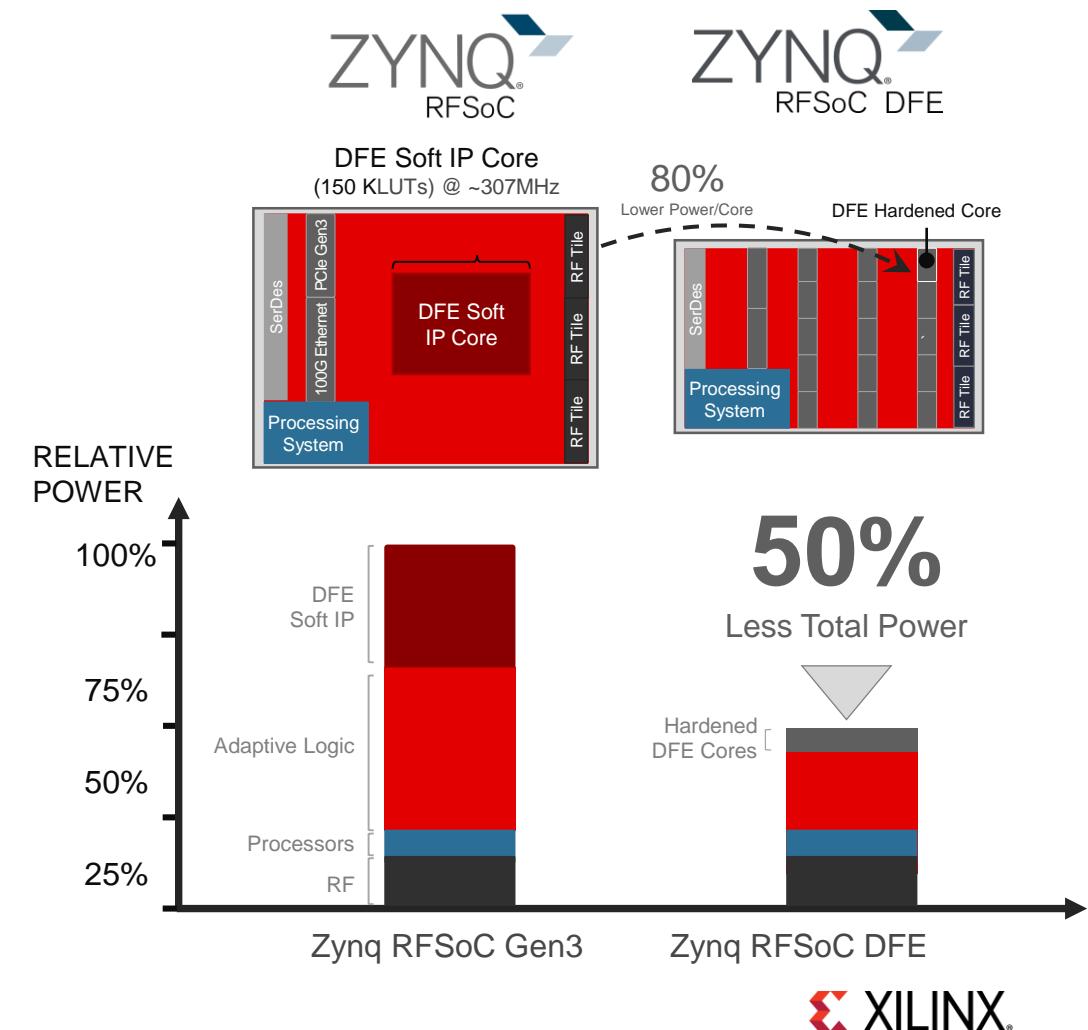

# 高い演算性能と低消費電力

## 2倍の演算性能

- ▶ チャンネルあたりの処理能力の向上

- ▶ 第2次5G NR要件に対応

または

## 50% 低い総消費電力

# ハード IP と適応型プログラマブル ロジックがもたらす効率性

シングル チップの適応型

無線プラットフォーム

- ▶ 演算負荷および消費電力の高い一般的なブロックをハード化 ( $>500\text{MHz } F_{\text{MAX}}$ )

- ▶ 各ハード ブロックは、最大限の柔軟性とカスタマイズを実現するためにバイパスまたは追加が可能

- ▶ プログラマブル ロジックが、将来的な市場の 5G 要件に向けた差別化と適応性を提供

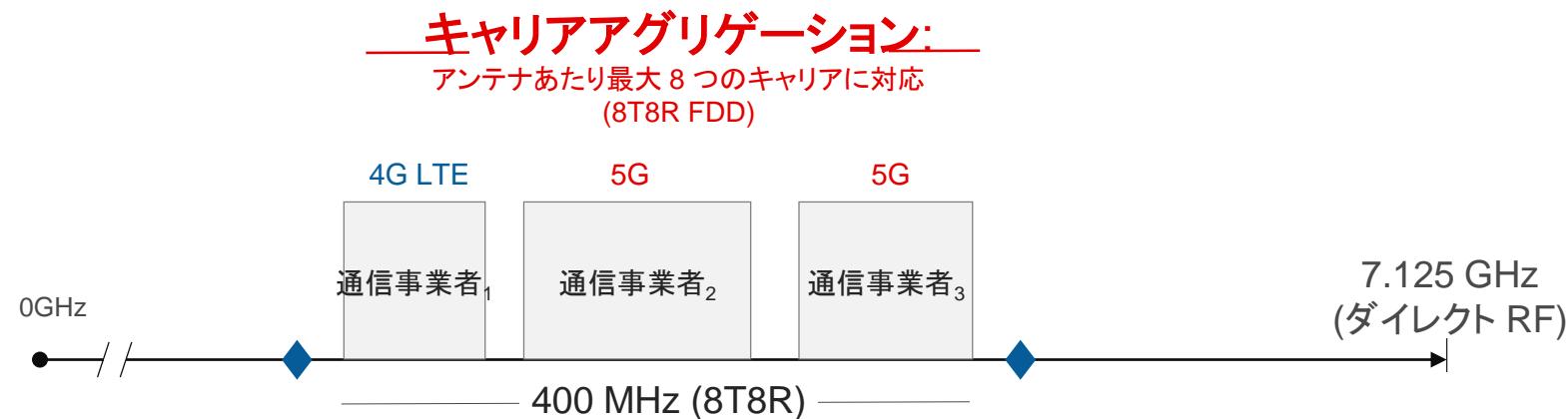

# 多様なキャリア ニーズに対応するシステム性能

業界唯一となる 400MHz の瞬時帯域幅 (iBW) 無線プラットフォーム (業界平均の 2 倍)

- ▶ 400MHz (8T8R)、最大 7.125GHz のダイレクト RF (FR1) をサポート

- ▶ 最大 1600MHz iBW のミリ波 IF トランシーバー (FR2)

- ▶ アンテナあたりの演算性能または無線あたりのアンテナ数を向上

- ▶ 無線あたり帯域幅の増加 → ユニット数の削減 → パワー・アンプの削減 → システム コストの低減

アンテナあたり最大 8 つのキャリアに対応するキャリア アグリゲーション付きマルチバンド

- ▶ 同一無線で 4G LTE と 5G をサポート (マルチバンド、マルチモード)

- ▶ 同一無線を介したデータ パイプ数の増加で、システム コストを削減

- ▶ RAN 共有の実現 (複数事業者が同一無線ユニットを共有)

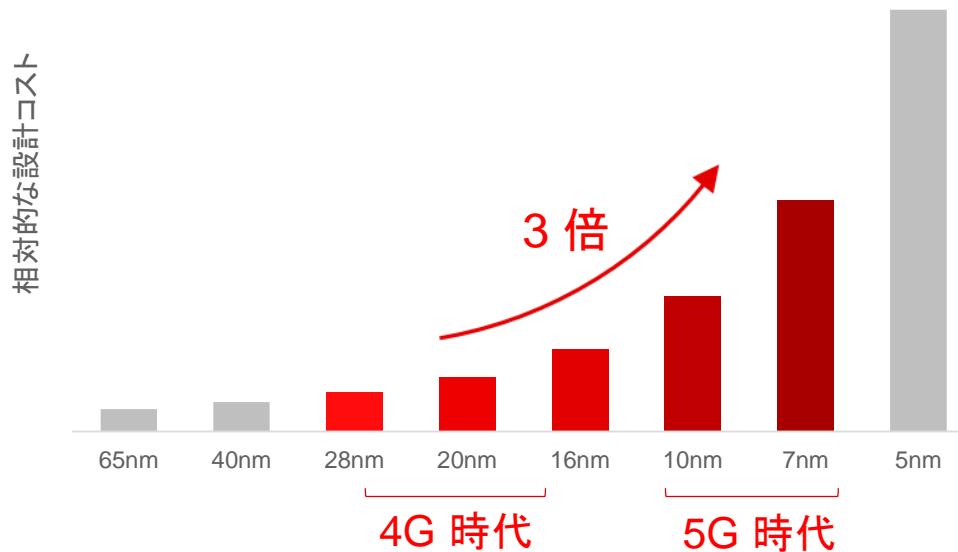

# 5G の進化と多様なユースケースによってかすむ ASIC の戦略

## 必ずしも有望ではない ASIC の経済性

- ▶ 5G 時代の ASIC NRE コストは 4G 時代の 3 倍

- ▶ ニッチな市場とユースケースの場合、ASIC ではコストに合わない

- ▶ ASIC のサイクル時間 (2 年以上) は長すぎる

## 5G では 10 年に及ぶアップグレードを想定

- ▶ 5G NR 要件がどう変わるか明確ではない

- ▶ ASIC は複数の無線方式を並行して着手

- ▶ 大規模運用には ASIC の代わりに Zynq RFSoC DFE が対応

# 大規模 MIMO マクロセルからスモール セルまでの拡張性

大規模 MIMO

マクロセル

サブ 7GHz 帯までの

ダイレクト RF

マルチモード

マクロセル

5G、4G LTE

固定無線

アクセス

IF デジタル トランシーバー

ミリ波スペクトル

スモール セル

ノード

電力効率とコスト効率の高い

シングル チップ無線

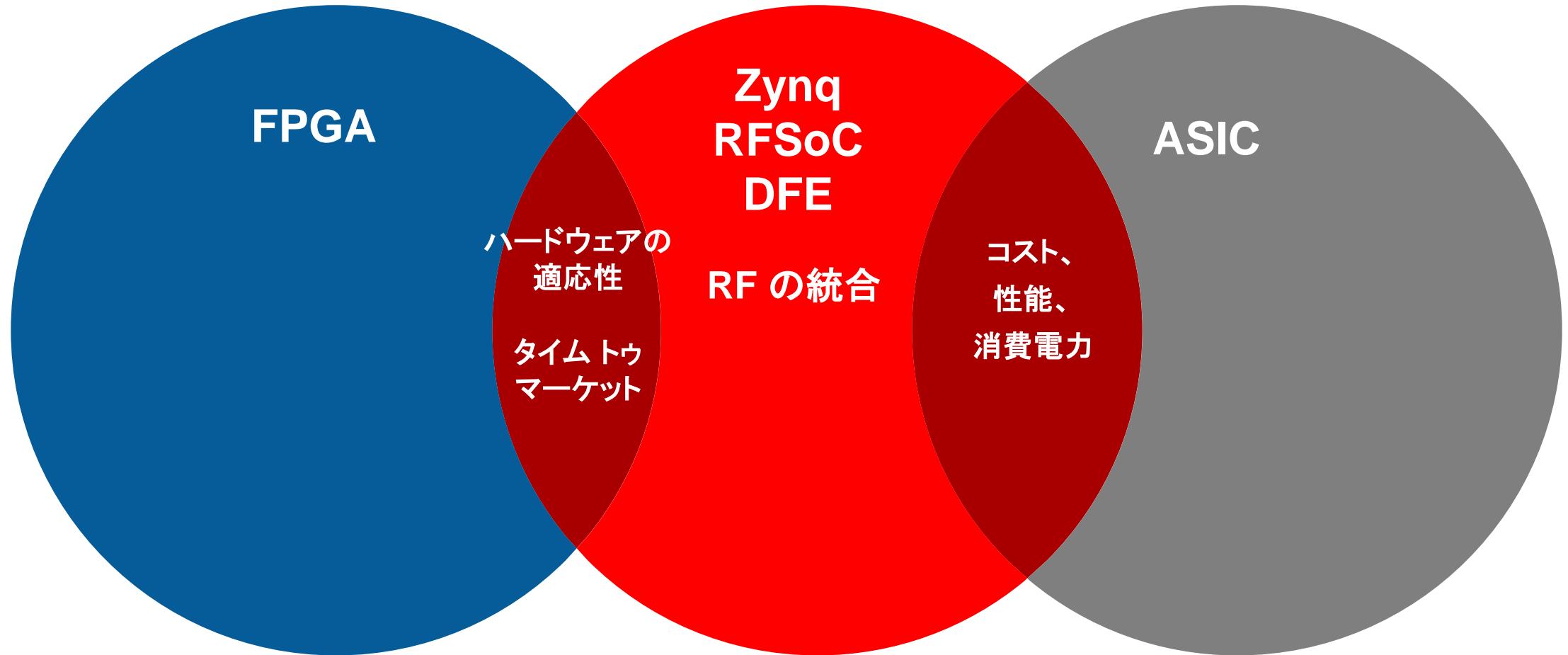

# Zynq RFSoC DFE: FPGA と ASIC 両方の利点を兼ね備える

重要なアプリケーション特性を満足するよう最適化

# 5G NR 大規模運用に対応する Zynq RFSoC DFE ハード化された IP の画期的な統合

第 2 次 5G NR 要件を満たし、

2 倍の単位ワットあたり性能を達成\*

柔軟性とコストのバランスが取れた

5G NR 無線ソリューション

5G の進化に遅れを取らない

適応型ハードウェア

ソフトロジックより多数のハード IP を統合した、新しいクラスのデバイス

\* 消費電力および性能を Zynq RFSoC Gen3 と比較

シリコン出荷は

2021 年上期を予定

---

Thank You