# 未来の最も複雑なテクノロジの創造がここから始まる

Hanneke Krekels – Sr. Director Test、Measurement & Emulation Markets Mike Thompson – Sr. Product Line Manager、Virtex® UltraScale+™ Portfolio

## エミュレーションおよびプロトタイピングの動向

#### ASIC および SoC の採用数の増加

- > AI/ML、5G、オートモーティブ、ビジョン、ハイパースケーラー向け ASIC および SoC に 牽引される

- > 進化するアーキテクチャ、ソフトウェア コンテンツ、複雑性の増大による影響を受ける

#### エミュレーション/プロトタイピングの新たな製品カテゴリ

- > ソフトウェア コンテンツの増加により、プロトタイピングはエミュレーションよりも速いペースで 成長すると見込まれる

- > エンタープライズ プロトタイピング 拡張機能により、ラックベースのプロトタイピングが可能

#### クラウドでのエミュレーション

- > エミュレーション/プロトタイピングの最大容量を一時的にオンプレミスからクラウドにオフロード することが目的

- > スタートアップ企業は初期のエミュレーション/プロトタイピングの投資を削減し、演算リソースを拡大できる

- > CapEx から OpEx へのリソースの移動が可能

## エミュレーション/プロトタイピング業界におけるザイリンクスの歩み

- ▶ エミュレーション/プロトタイピング業界を牽引するザイリンクス

- > No.1 の業界シェア

- > 複数世代にわたって業界をリードするテクノロジ

- ➤ より大規模な FPGA に対する需要が続く

- > 複数の分野において、より大規模な FPGA が 必要とされている

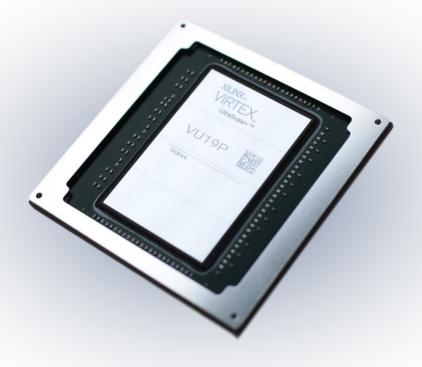

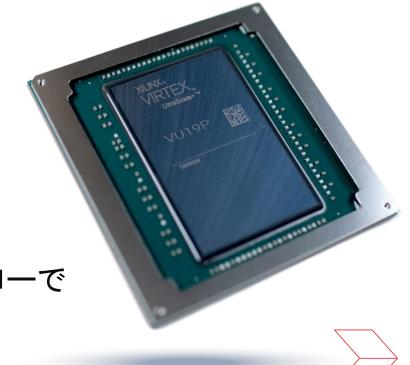

世界最大の FPGA が登場

Virtex® UltraScale+™ VU19P FPGA

## Virtex® UltraScale+™ VU19P FPGA

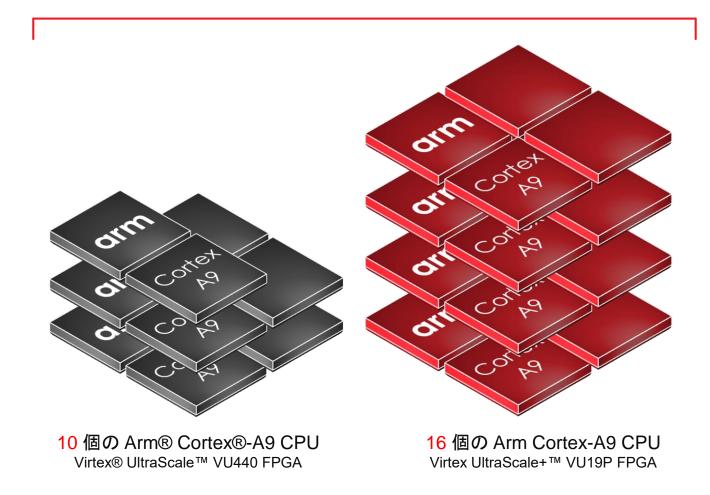

### ▶ 900 万個のシステム ロジック セル

- > より大規模で、より複雑な ASIC/SoC テクノロジを実装

- > 高度にカスタマイズされたアルゴリズムとアプリケーションを実現

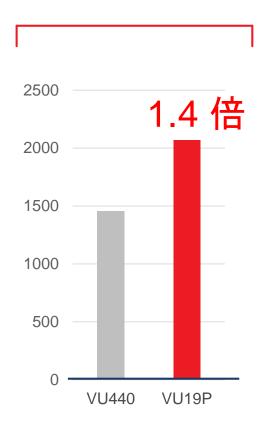

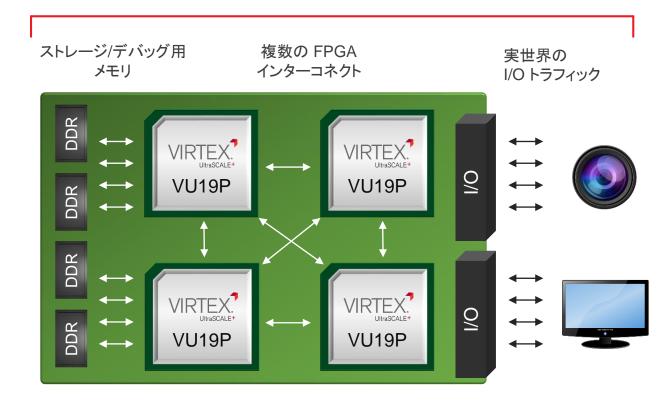

### ▶ 2,072 個のユーザー I/O

- > 複数の FPGA を使用したデザイン プラットフォームがシンプルに

- > スケーラビリティ、デバッグ、および実世界の検証が可能

#### ▶ 80 個の 28G トランシーバー

- > 高ポート密度のテスト装置に対応

- > 新しいインターフェイス規格を使用するシステム デザインの検証が可能

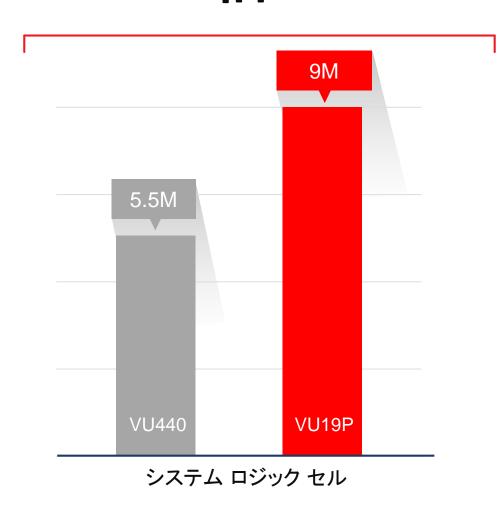

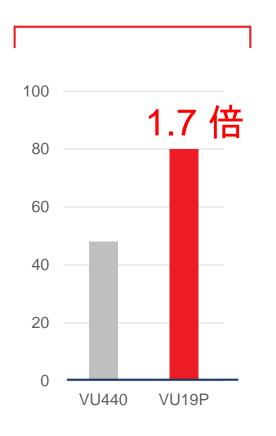

## 最高のロジック容量

## 1.6 倍 ロジック容量

## 大規模な ASIC/SoC のエミュレーションと プロトタイピングが可能

## 最高の I/O 帯域幅

2,072

I/O 数

1.5Tb/s

I/O 帯域幅

## スケーラビリティ、デバッグ、および 実世界の検証が可能

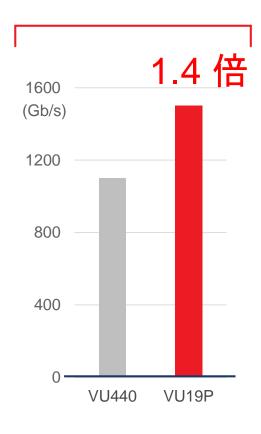

## 最高のトランシーバー帯域幅

80

4.5Tb/s

28G トランシーバー トランシーバー帯域幅

## 最新のインターフェイス規格で 高ポート密度のテスト装置を実現

(バス プロトコル アナライザーなど)

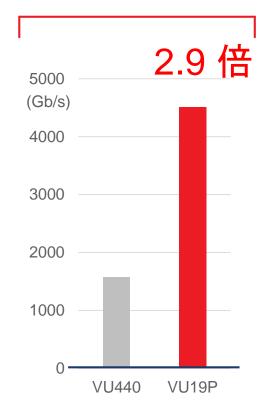

## 第3世代の最先端開発プラットフォーム

ゼロからの設計でエミュレーションクラスのデザインに対応

#### ツールおよび IP

- > 自動デザイン クロージャ支援

- > インタラクティブな提案およびデザイン調整

## コンパイル時間および QoR (結果の品質) Ultra FAST

- > 複数世代にわたってコンパイル時間を短縮

- > 分散、並列コンパイルで反復を削減

#### 堅牢なデバッグ サポート

- > 再コンパイルなしの高速プローブ

- > リモート、マルチ ユーザー デバッグ

Vivado® Design Suite と UltraFast™ メソドロジを組み合わせて使用することで、統合/実装に要する時間がこれまで以上に高速化

## ザイリンクスは最大容量 FPGA で常に業界をけん引

5.5M システム ロジック セル 第 2 世代の SSI 技術

#### **VU19P**

9M システム ロジック セル 第 3 世代の SSI 技術

2M システム ロジック セル 第 1 世代の SSI 技術

2011

2019

## まとめ

3世代にわたる世界最大の FPGA

最も複雑な SoC/ASIC 向けの 最高のロジック容量と I/O 帯域幅

業界をリードするツール、IP、およびデザインフローで低リスクかつ短期間での市場展開が可能

Building the Adaptable, Intelligent World