# Alveo U55C データセンター アクセラレータの紹介

データセンター グループ

HPC プロダクト マネージャー

Nathan Chang

# HPC エクサスケールの課題

- HPC がエクサスケールの限界点に迫る中で、次に立ち塞がるのは消費電力

- 標準的な HPC アーキテクチャでは、許容可能なワットあたり性能を実現するのは困難になる

- CPU と GPU のノイマン型アーキテクチャの限界

- データ移動の課題によりパフォーマンスが低下

- パフォーマンスを最大限に高めるには、ファンクション間の転送中にデータを準備する必要がある

- 柔軟性に欠けるメモリ階層は非効率化をもたらす

- 最終的な結果として、クロックサイクルの無駄遣い、動作量の減少、消費電力の増大をもたらす

サイバー セキュリティ

データ移動

大規模物理宇宙

AI

ゲノム解析

金融

気象

XILINX

# 革新的な HPC アーキテクチャ 本日の発表内容

- ▶ 業界最高性能の Alveo HPC アクセラレータ カード

- ▶ ユーザーの既存インフラストラクチャ およびネットワーク全体で大規模スケールアウトを実現する、画期的な HPC クラスタリング ソリューション

- ▶ アプリケーションとクラスター両方の 完全な高水準プログラマビリティ

# ザイリンクスのスケールアウトシステム アーキテクチャ

既存のデータセンター サーバー インフラストラクチャで RoCE v2 および DCBx のスケールアウト アーキテクチャ

- 低コスト、独自ハードウェア不要、1000 ノード超のスケール

- 高性能、ロスレス、広帯域、低レイテンシのネットワーク コネクティビティ

複数のカード間のワークロード共有およびメモリ共有

- 大きなデータ、大きなワークロード

MPI はノード間でザイリンクス アダプティブ コンピューティングをハイパー並列化

- 現代の HPC 開発者に広く使用されているフレームワーク

# Vitis 統合ソフトウェア プラットフォーム

ドメイン特化型

開発環境

Vitis アクセラレ

ーションライブラリと

API

Vitis コア

開発キット

ユーザーが作成したアプリケーション

ビジョン

ライブラリ

グラフ

分析

ライブラリ

FinTech

ライブラリ

ストレージ

ライブラリ

ネットワー

クライブラリと

ミドルウェア

コンパイラ

Arm、HLS、AI エンジン、P4

アナライザー

デバッガー

Vitis ランタイム (XRT)

Alveo

ビデオ

ストリーミング

SDK

FFmpeg

gstreamer

ビデオ トランス

コーディング

Vitis AI

TensorFlow

Caffe

PyTorch

AI/ML

# Vitis 統合ソフトウェア プラットフォーム

ドメイン特化型

開発環境

Vitis アクセラレ

ーションライブラリと

API

Vitis コア

開発キット

グラフ分析

FEM

AI

HPC

クラスタリング

コサイン

類似度

Louvain

モジュラリティ

FinTech

ライブラリ

MIS

JPCG

API

ICCG

API

MLP

API

ERNIC

XNIK

コンパイラ

Arm、HLS、AI エンジン、P4

アナライザー

デバッガー

Vitis ランタイム (XRT)

Alveo

# Vitis 統合ソフトウェア プラットフォーム

ドメイン特化型

開発環境

Vitis アクセラレー

ションライブラリと

API

グラフ分析

FEM

AI

HPC

クラスタリング

コサイン

類似度

Louvain

モジュラリティ

FinTech

ライブラリ

MIS

JPCG

API

ICCG

API

MLP

API

ERNIC

XNIK

データ サイエンティストが

レコメンデーションエンジンをロータッチ/

ノータッチ コーディングで作成可能

コンバージド イーサネットでの

スケールアウトを実現

FEM 開発者がカスタム データ移動を

・活用するための API - 階層メモリ

・ロックインなし、キャッシュ ミスなし

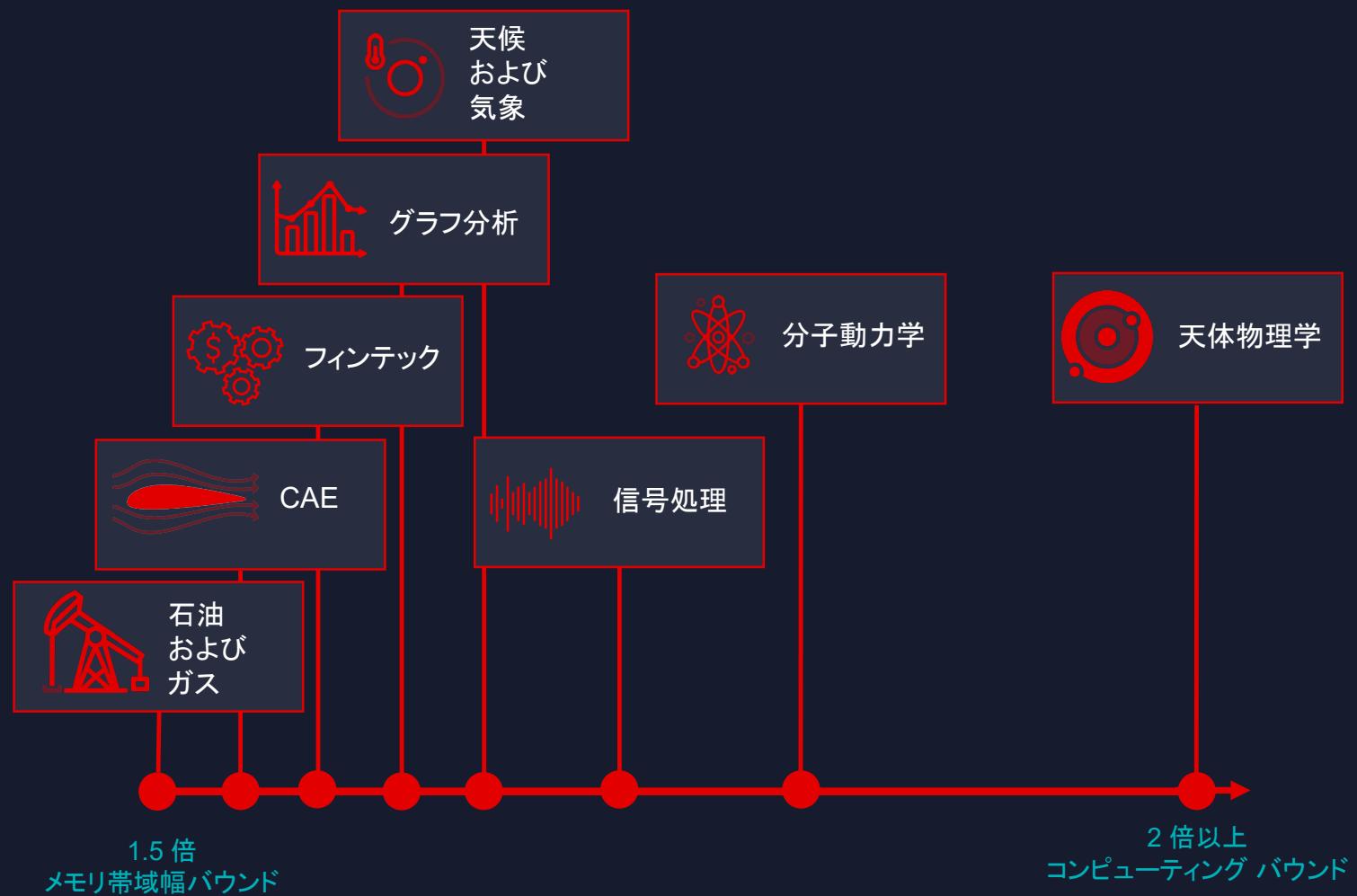

# Alveo U55C: HPC およびビッグデータ ワークロードに特化した設計

- ▶多くの HPC ワークロードは、コンピューティング バウンドまたはメモリ帯域幅バウンドである…

- ▶I/O 要件は時間の経過と共に指数関数的に増加していく…

- ▶消費電力はデータセンターで大きな問題になっている

- ▶HPC には膨大な計算能力と広帯域幅メモリの双方が要求される

- ▶これに対応して、ザイリンクス史上最もパワフルなアクセラレータを開発し、容易に拡張可能にした

# Alveo U55C: HPC およびビッグデータ ワークロードに特化した設計

- ▶ データパイプラインのさらなる並列化

- ▶ 優れたメモリ管理

- ▶ パイプライン全体で最適化されたデータ移動

- ▶ 最高のワットあたり性能

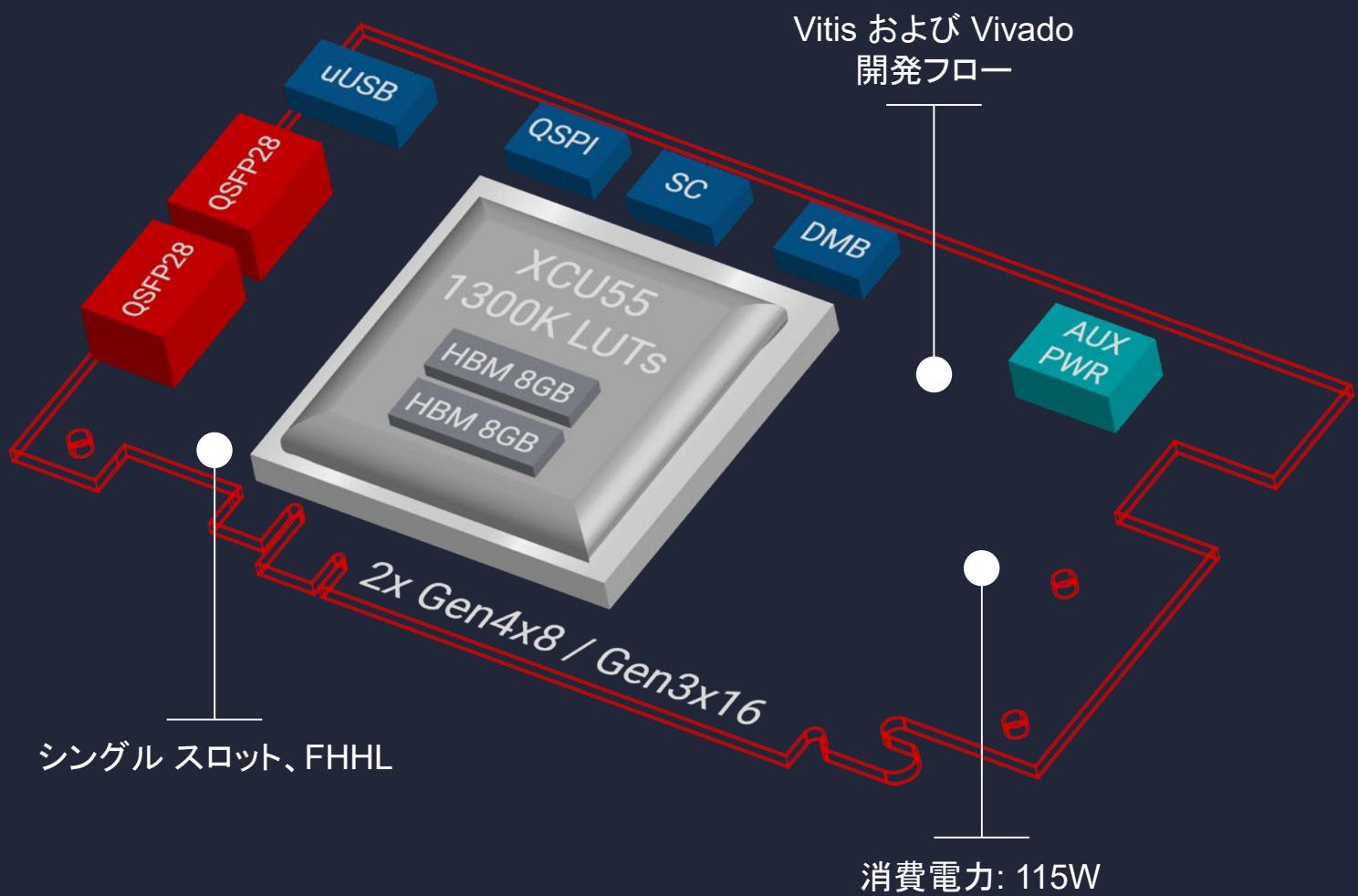

# ザイリンクス史上最高性能のアクセラレータ

|          |                                     | Alveo U280                      | Alveo U55C          |

|----------|-------------------------------------|---------------------------------|---------------------|

| 寸法       | 幅                                   | デュアル スロット                       | シングル スロット           |

|          | フォーム ファクター、パッシブ<br>フォーム ファクター、アクティブ | フルハイ、¾ レンジス<br>フル ハイ、<br>フルレンジス | フル ハイ、<br>ハーフレンジス   |

| ロジック     | ロックアップ テーブル                         | 1,304K                          | 1,304K              |

|          | レジスタ                                | 2,607K                          | 2,607K              |

|          | DSP スライス                            | 9,024                           | 9,024               |

| DRAM メモリ | DDR フォーマット                          | 2x 16GB 72b DIMM<br>DDR4        | —                   |

|          | DDR 総容量                             | 32GB                            | —                   |

|          | DDR 最大データ レート                       | 2400MT/s                        | —                   |

|          | DDR 総帯域幅                            | 38GB/s                          | —                   |

| 内部 SRAM  | HBM2 総容量                            | 8GB                             | 16GB                |

|          | HBM2 総帯域幅                           | 460GB/s                         | 460GB/s             |

| インターフェイス | 総容量                                 | 43MB                            | 43MB                |

|          | 総帯域幅                                | 35TB/s                          | 35TB/s              |

|          | PCI Express®                        | Gen3 x16                        | Gen3 x16、2x Gen4 x8 |

|          | ネットワーク インターフェイス                     | 2x QSFP28                       | 2x QSFP28           |

| 電源/熱管理   | 冷却                                  | パッシブ、アクティブ                      | パッシブ                |

|          | 標準電力                                | 100W                            | 115W                |

|          | 最大電力                                | 225W                            | 150W                |

# HPC のためのザイリンクス アダプティブ コンピューティング

大規模なクラスタリング

ソフトウェア開発者向けに設計

```

if operation == "MIRROR_X":

mirror_mod.use_x = True

mirror_mod.use_y = False

mirror_mod.use_z = False

elif operation == "MIRROR_Y":

mirror_mod.use_x = False

mirror_mod.use_y = True

mirror_mod.use_z = False

elif operation == "MIRROR_Z":

mirror_mod.use_x = False

mirror_mod.use_y = False

mirror_mod.use_z = True

# ...

# ...

# ...

```

パワフルなアクセラレータ

# HPC: 信号処理 CSIRO

- ▶ 世界最大の電波天文用アンテナ アレイ

- ▶ 宇宙の起源に関する情報を収めるために設計

- ▶ テラビット/秒のセンサーデータをリアルタイムで処理する必要

- ▶ ソリューション: 数百のザイリンクス Alveo アクセラレータでリアルタイム分散処理

- ▶ CSIRO は、その他の組織が同様の成功を実現できるよう、現在リファレンス デザインを作成中

## 重要な要素

- 大規模: 21 ノード、420 カード

- パワフル: 15 テラビット/秒の処理

- 消費電力効率が良い: ソーラー電源、カードあたり 90W のみ

- 高信頼性: FPGA ファブリックと HBM の 50% のみ使用

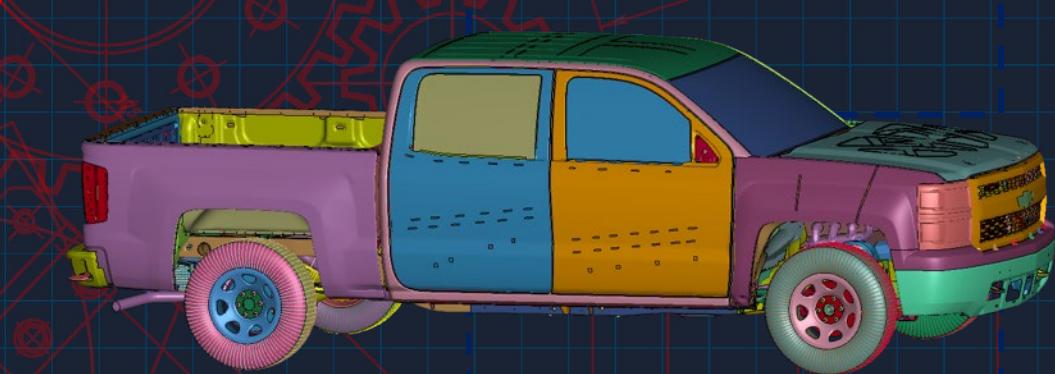

# HPC: コンピューター支援エンジニアリング (CAE) Ansys LS-DYNA

## ▶ LS-DYNA: 有限要素プログラム (FEM)

- FEM を使用して現実世界の製品性能をシミュレーション

- LS-DYNA は、設計者とエンジニアが無限の複雑性をもつシミュレーションを作成できるようにする

## ▶ 大規模シミュレーションを 1 つの CPU で実行すると数週間かかる

- x86 アーキテクチャは、要求される高い I/O および帯域幅を提供するには不足

- CPU メモリ階層は柔軟性に欠け、不要なオーバーヘッドが生じる

- x86 アーキテクチャは本質的にデータ移動の処理が非効率

- National Crash Analysis Center による Silverado モデル

- 700k の要素 (大部分はシェル + ソリッドとビーム)

- 膨大な負荷

# LS-DYNA 向け U55C ハイパー並列データパイプライン処理

- ▶ データはパイプライン処理され、ファンクション間を簡単にストリーミングされる

- ▶ 最高のスループットを実現するため、データは転送中に準備される

- ▶ 高度に構成可能なメモリ階層

- 16GB HBM2 メモリ、32 HBM チャネル @ 460GB/秒

複数の Alveo U55C カード間で分割されたワークロード

結果: CPU の 5 倍のパフォーマンス

5x

240 秒

8 x Alveo U55C

1,200 秒

CPU

行列の大きさ -> 12M

nnzs: 非ゼロ要素の数 -900M

時間(秒): JPCG ソルバーの実行時間

CPU モデル: インテル Xeon Platinum 8260L @2.4GHz,

1.5TB メモリ

XILINX

# ビッグ データ: グラフ分析

- ▶ 表形式および非構造化データベースは、リレーションに焦点を置いていない

- ▶ 挙動を理解し、予測を可能にするには、データの相関関係が鍵

- ▶ 切り離されたデータ環境でデータサイエンティストが回答を探すのは高コスト

- ▶ グラフはデータ間の関係に焦点を当てることで、これまで取得が困難、または高いコストがかかっていたインサイトをすばやく提供

- ▶ グラフの次の新たな領域は、解をリアルタイムで見つけること

# U55C リアルタイムのグラフ インサイト

- ▶ リアルタイムで結果を得るには、ザイリンクスのアクセラレーションが必要

- ▶ 重要なリアルタイム グラフ ユースケースに合わせて調整されたアルゴリズム

- ▶ 患者への推奨ケアパス

- コサイン類似度アルゴリズム

- CPU の 96 倍

- 全体パフォーマンスは U50 の 2 倍に向上

- ▶ 不正検出

- Louvain モジュラリティ アルゴリズム

- CPU の 45 倍

- DDR4 の使用が 66% 低下

- 品質スコアが 35% 向上

# 試用および購入方法

## U55C 提供中

japan.xilinx.com およびザイリンクス販売代理店で提供中

## クラウドおよび DC で容易に評価

### クラウド FPGAaaS

- ▶ ザイリンクス アプリストアへのアクセス

- ▶ 固定されたサーバー構成

- ▶ Vitis デザインフロー

- ▶ マネージド インフラストラクチャ

### コロケーション

- ▶ パートナーおよびユーザーの評価用に提供中

- ▶ 特定のサーバー構成

- ▶ Vivado デザインフロー

- ▶ マネージド インフラストラクチャ

## まとめ

- ▶ ザイリンクスの新しい HPC クラスタリング ソリューションは、ユーザーの既存インフラストラクチャおよびネットワーク全体で大規模なスケールアウトを実現

- ▶ ザイリンクス Alveo U55C アクセラレータ カード (現在提供中) は、HPC およびデータベース ワークロードに優れたワットあたり性能をもたらし、ザイリンクス クラスタリングで容易にスケールアウト可能

- ▶ ソフトウェア開発者およびデータ サイエンティストは、アプリケーションとクラスター双方の高水準プログラマビリティにより、ザイリンクス アダプティブ コンピューティングの利点を最大限に活用できる

---

Thank You