PowerPC® 32-bit RISC プロセッサ

高集積エンべデッド メモリ用 550MHz ブロック RAM

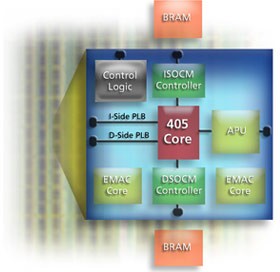

Virtex-4 FX Platform FPGA は、単一デバイスに最高 2 基の PowerPC® 405、32 ビット RISC プロセッサ コアを搭載します。これらの業界標準のプロセッサによって、高性能と広範なサードパーティ サポートが実現します。最新の Auxiliary Processor Unit (APU) コントローラーは、ハードウェア アクセラレーターとコプロセッサの統合を簡易化します。

エンベデッド PowerPC 405 (PPC405) コア

- エンベデッド 450MHz、700DMIPS RISC コア (32 ビット Harvard アーキテクチャ)

- 5 段階のデータ パス パイプライン

- ハードウェアの乗算と除算

- 32 x 32 ビットの汎用レジスタ

- 16KB 双方向セット アソシエイティブ命令およびデータ キャッシュ

- RTOS インプリメンテーションを実現するメモリ管理ユニット (MMU)

- 64 エントリの統一変換ルックアサイド バッファー (TLB)

- 多様なページ サイズ (1KB ~ 16KB)

- 拡張インストラクションおよびデータ オンチップ メモリ (OCM) コントローラーがエンベデッド ブロック RAM に直接インターフェイス

- IBM CoreConnect バス アーキテクチャのサポート

- デバッグとトレースのサポート

最新の APU (Auxiliary Processor Unit) コントローラー が CPU パイプラインを直接 FPGA ファブリックにインターフェイス

- ハードウェア アクセラレータが使用可能

- ユーザー定義の命令をサポート

- 1 つの命令で最高 4 つまでの 32 ビット ワード データ転送をサポート

- 浮動小数点およびコプロセッサのサポート

- パイプライン ストールのない自律型命令をサポート

- 32 ビット命令および 64 ビット データ

- 4 サイクルのキャッシュ ライン転送

トライモード イーサネット MAC コンフィギュレーション レジスタへの直接インターフェイスを提供

図 1: 405 プロセッサ コア