# Xcell journal

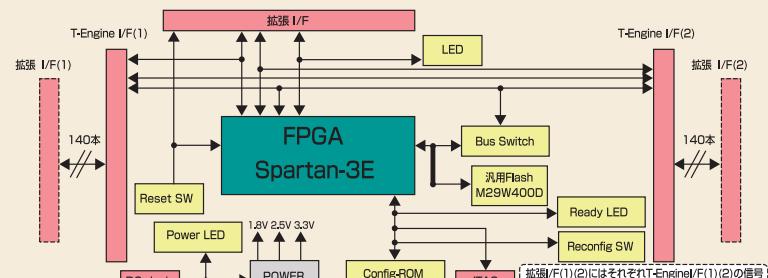

THE AUTHORITATIVE JOURNAL FOR PROGRAMMABLE LOGIC USERS

量産向けの

民生機器市場に

適用範囲を拡大

**HIGH VOLUME**

Spartan-3E: 新時代

オートモーティブ向けマルチメディア

DSP アルゴリズム

**DESIGN TOOL**

最新の ISE 7.1i ソフトウェア

デザイン制御

**SERIAL I/O**

シリアル リンクの高性能化

XILINX®

## INDUSTRY EXPERT

高速シリアルリンクの高性能化 ..... 1

## BUSINESS VIEWPOINTS

低成本FPGAにより変貌を遂げるシステム ランドスケープ ..... 6

## HIGH-VOLUME SOLUTIONS

量産プログラマブル革命をリード ..... 8

低成本 プログラマブル ロジックの新時代を拓くSpartan-3E FPGA ..... 9

Spartan-3Eファミリに追加されたコンフィギュレーション用

新オプション ..... 11

リコンフィギュアブルFPGAによる高解像度Ogg/Theoraビデオエンコード ..... 14

Spartan-3 FPGAを利用したデジタル信号処理アルゴリズムの実装 ..... 17

Spartan-3 FPGAのDDRメモリインターフェイス設計 ..... 21

新機能を搭載したCoolRunner-II CPLD ..... 23

ザイリンクスのロジック コンソリデータで部材 (BOM) ..... 26

コスト低減 ..... 26

CoolRunner-IIのシリコン機能を利用したコスト削減 ..... 28

Spartan-3/3Eの機能を利用したデザインのエリア最適化 ..... 31

ASSPメーカーに展望を与える低成本EasyPath FPGA ..... 34

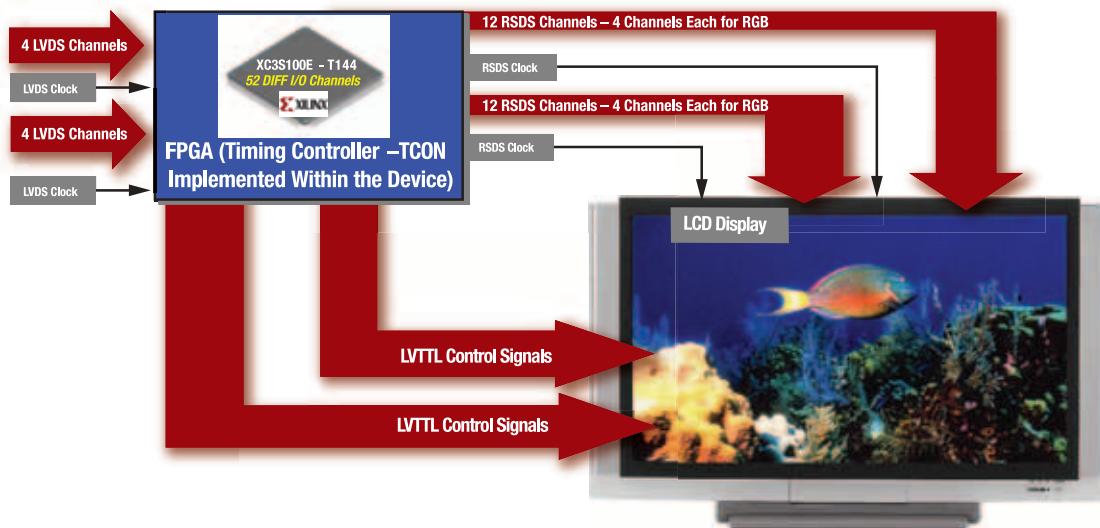

Spartanファミリをフラットパネル ディスプレイに採用 ..... 38

信号品質の制御 ..... 41

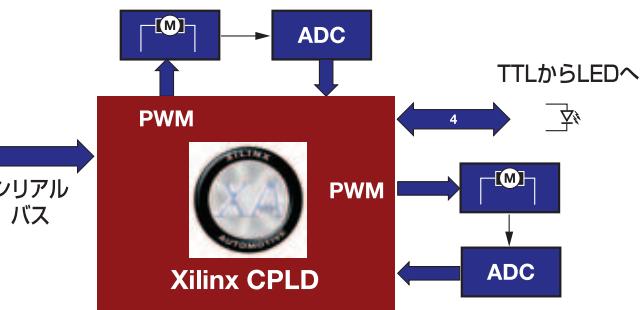

変遷するオートモーティブ向けECU設計の現状 ..... 44

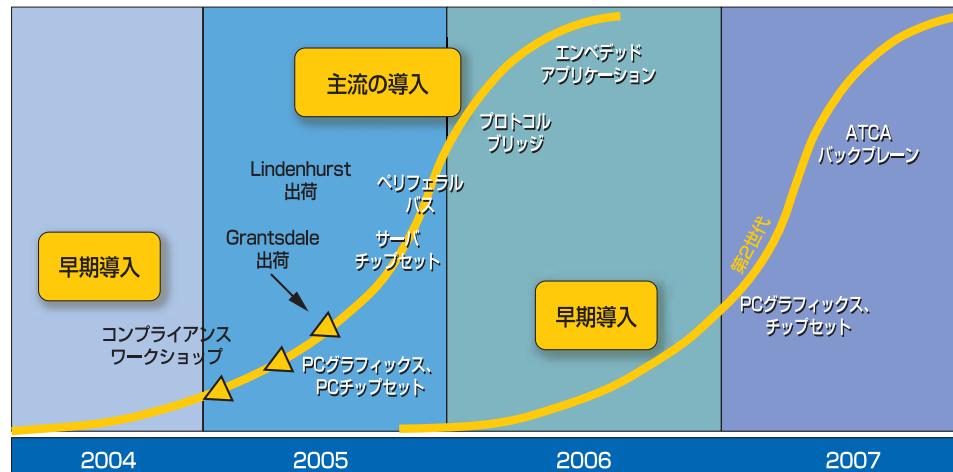

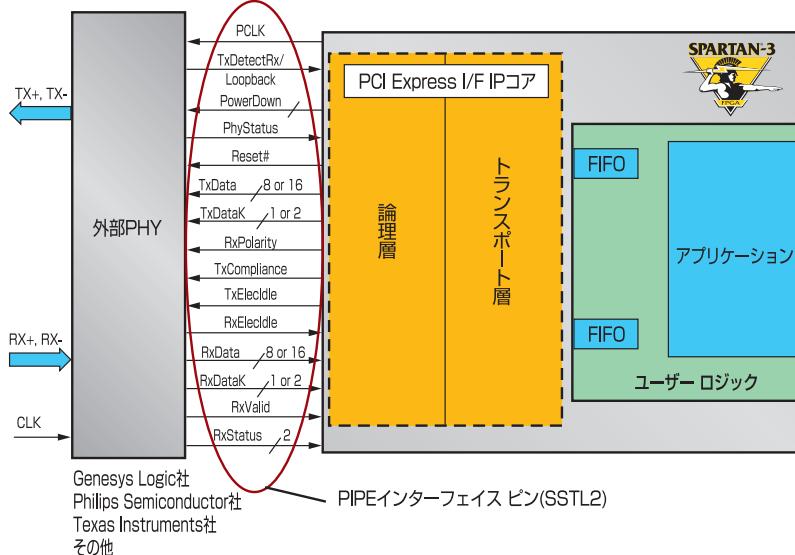

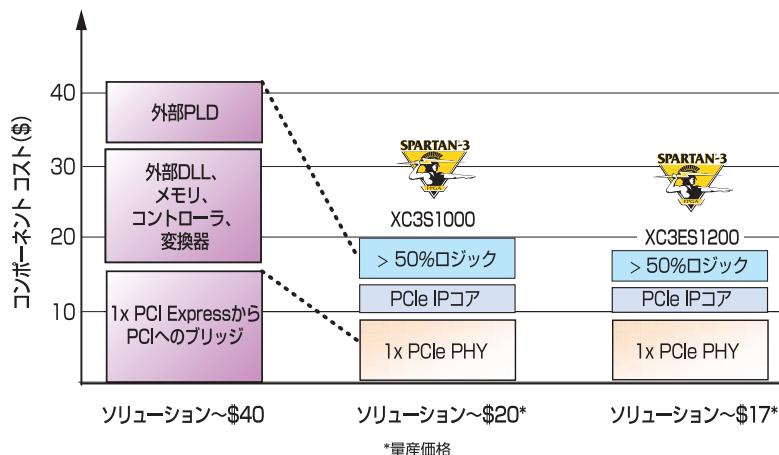

低成本のPCI Expressソリューション ..... 47

## DESIGN TOOLS

ザイリンクスのデザインリーダーシップ ..... 49

ISE7.1iソフトウェアによる設計パフォーマンスの飛躍的向上 ..... 50

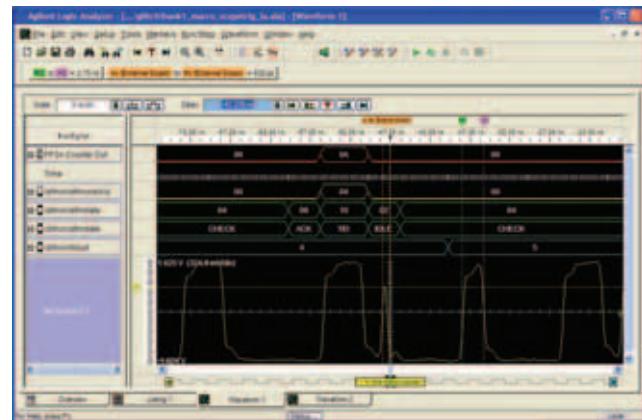

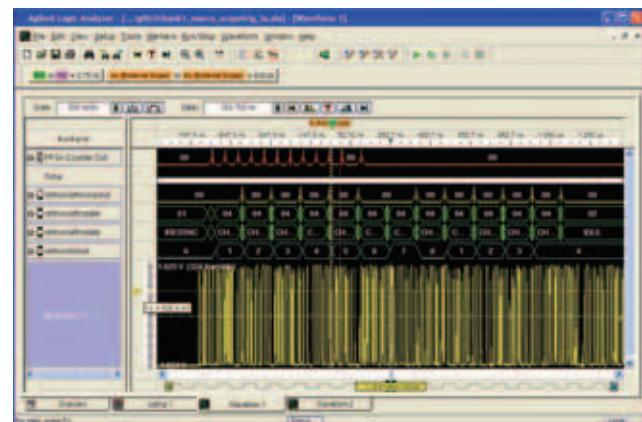

オシロスコープとロジックアナライザを組み合わせたデバッグ手法 ..... 53

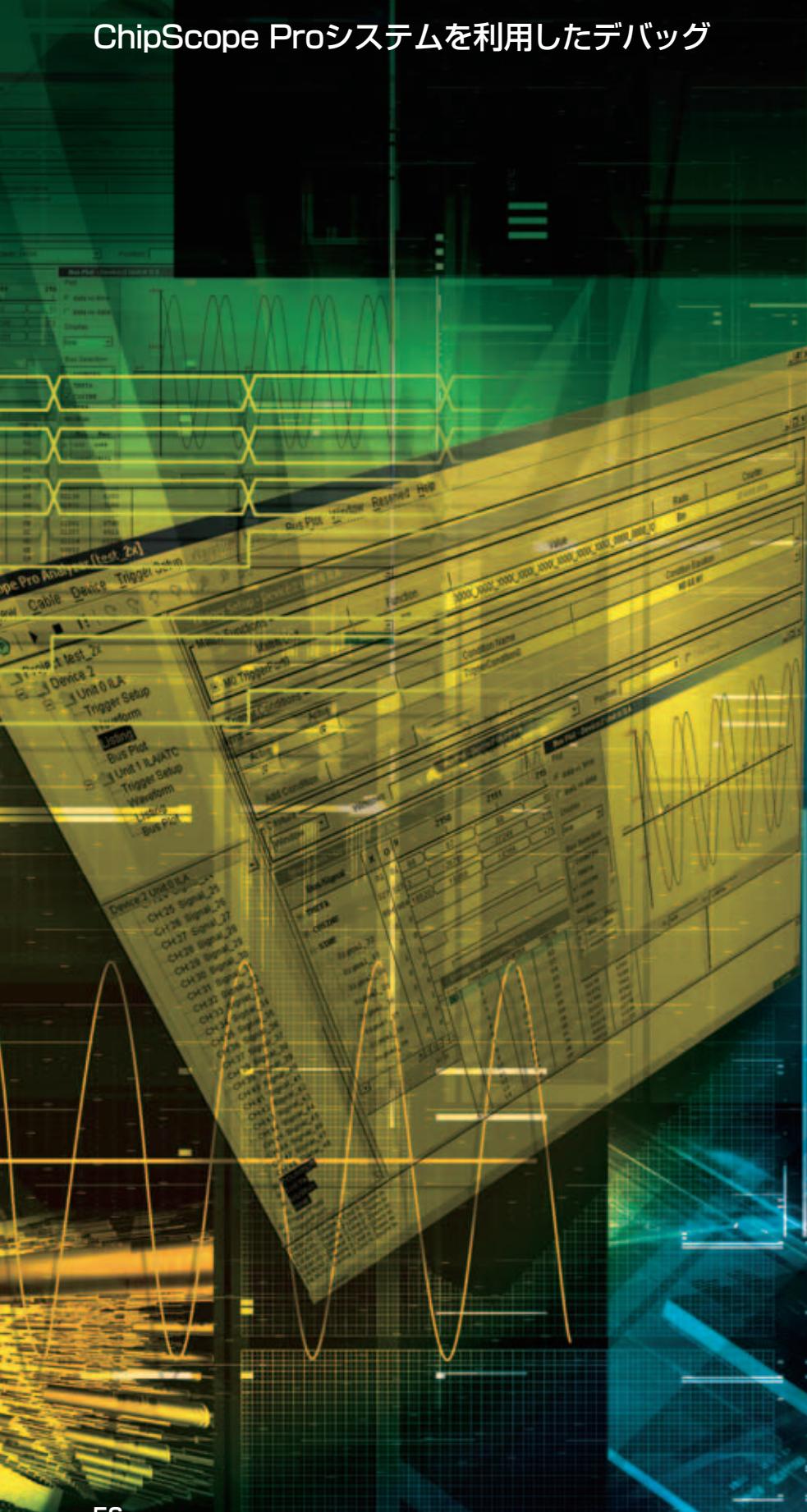

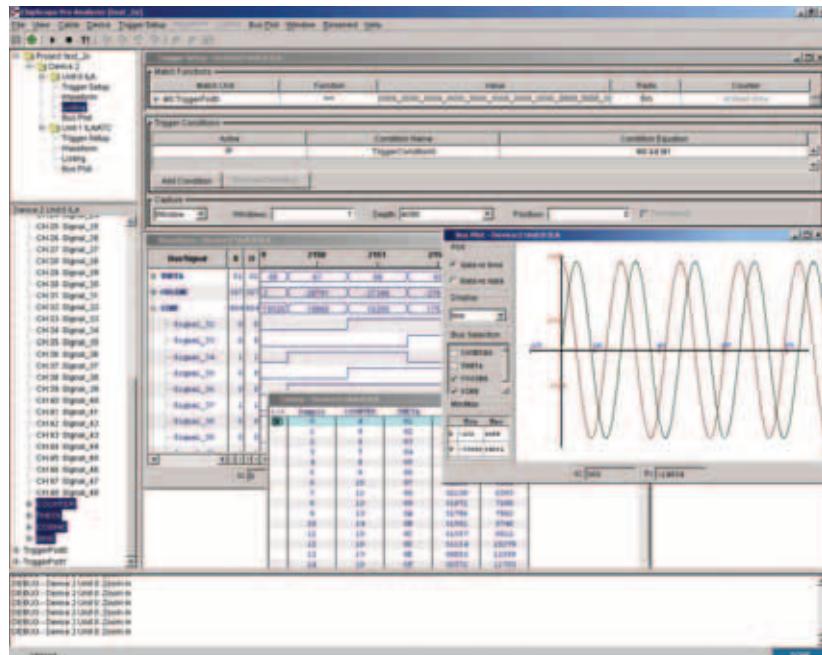

優位なリアルタイム デバッグ ..... 56

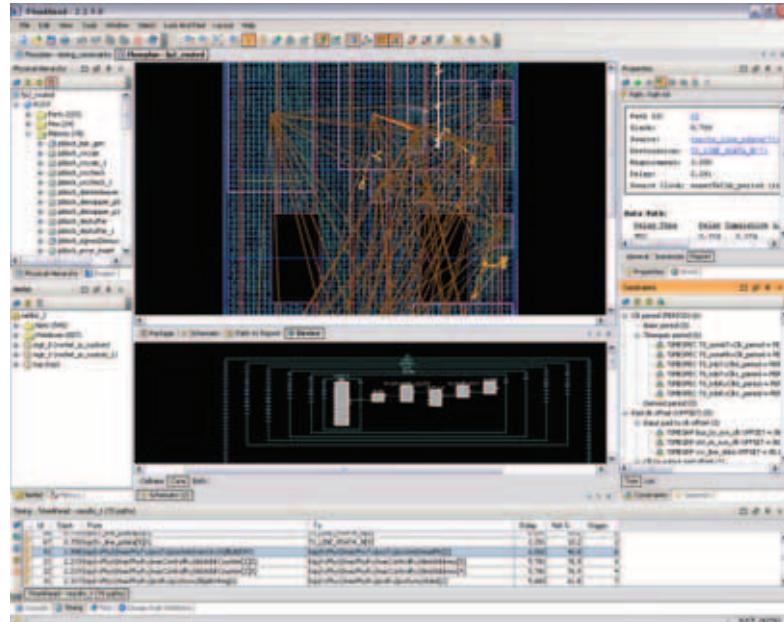

PlanAhead階層設計・解析ツールでデザインを制御 ..... 59

## GENERAL

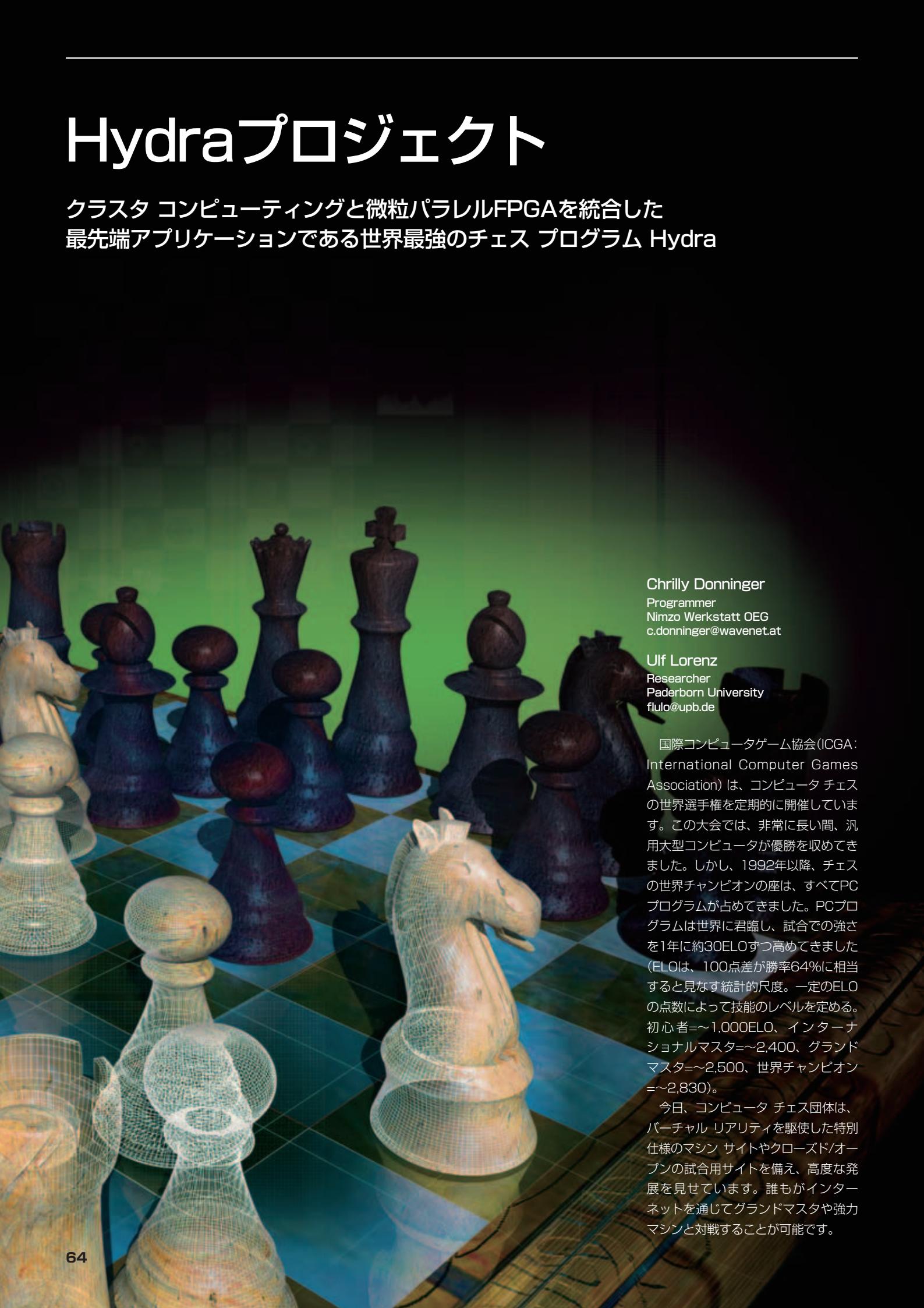

Hydraプロジェクト ..... 64

## SUCCESS STORY FROM JAPAN

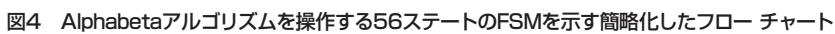

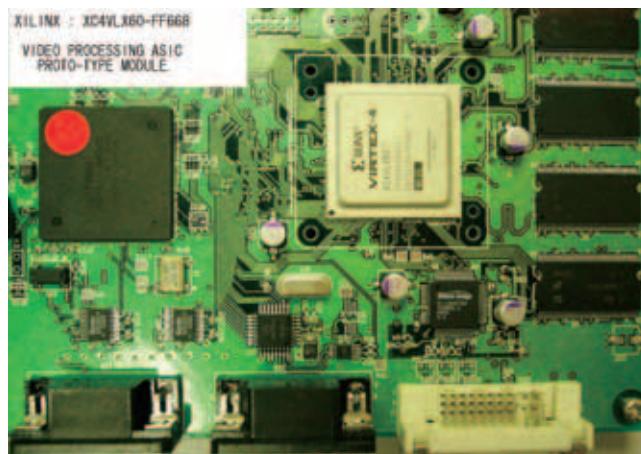

Virtex-4を採用したビデオプロセッサ開発ユニットの開発秘話 ..... 68

ザイリンクスイベントカレンダー ..... 71

BOARD ROOM ..... 72

## LETTER FROM THE EDITOR

低成本で高性能と柔軟性を実現し、幅広いアプリケーションで採用いただけます ..... 76

## 広告索引

株式会社 コンピューテックス ..... 5

株式会社 ソリトンシステムズ ..... 63

有限会社 ヒューマンデータ ..... 75

送付先住所等の変更は：

[www.xilinx.co.jp/xcell/henko/](http://www.xilinx.co.jp/xcell/henko/)

新規定期講読のお申込みは：

[www.xilinx.co.jp/xcell/toroku/](http://www.xilinx.co.jp/xcell/toroku/)

## TABLE OF CONTENTS 2005, ISSUE 53

### INDUSTRY EXPERT

高速シリアルリンクの

高性能化

柔軟性の高いイコライゼーション回路を搭載し、高速シリアルリンクの帯域と性能を大幅に向上したVirtex-4 FPGAファミリ内蔵のRocketIOトランシーバ

1

### BUSINESS VIEWPOINTS

低成本FPGAにより変貌を遂げる

システム ランドスケープ

低成本FPGAの登場が

新時代の幕開けを予告

6

### HIGH-VOLUME SOLUTIONS

量産プログラマブル

革命をリード

PDLを他社に先駆け低成本システム

向けにリードするザイリンクス

8

### DESIGN TOOLS

ザイリンクスのデザイン

リーダーシップ

ザイリンクスの設計ツールISE™7.1iに

より、プロジェクト終了までを最短で実現

49

# 高速シリアルリンクの高性能化

柔軟性の高いイコライゼーション回路を搭載し、高速シリアルリンクの帯域と性能を大幅に向上したVirtex-4 FPGAファミリ内蔵のRocketIOトランシーバ

Howard Johnson, Ph.D.

President

Signal Consulting, Inc.

howie03@sigcon.com

Mike Degerstrom

Senior Staff Signal Integrity Design Engineer

Xilinx, Inc.

mike.degerstrom@xilinx.com

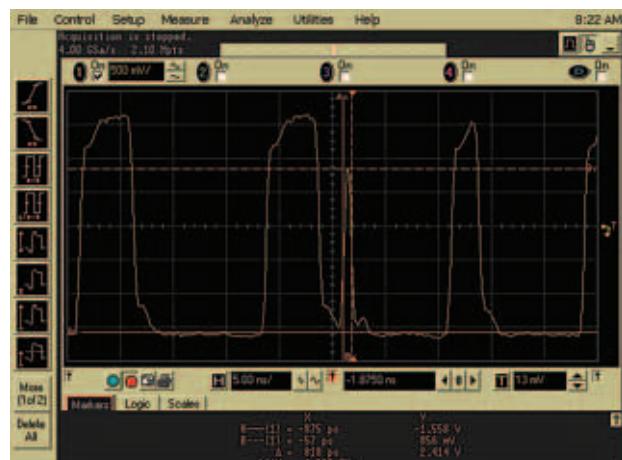

マルチギガギットのバックプレーンや、配線、ケーブルを通る信号には歪みが発生します。この歪みの影響が軽度なものか甚大なものかは、導体の形状、素材、配線長、使用するコネクタのタイプに依存します。

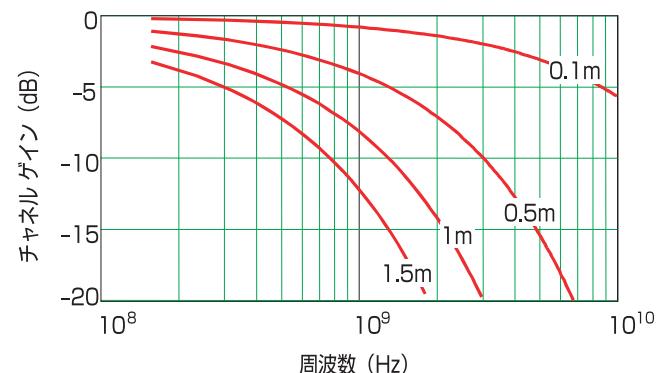

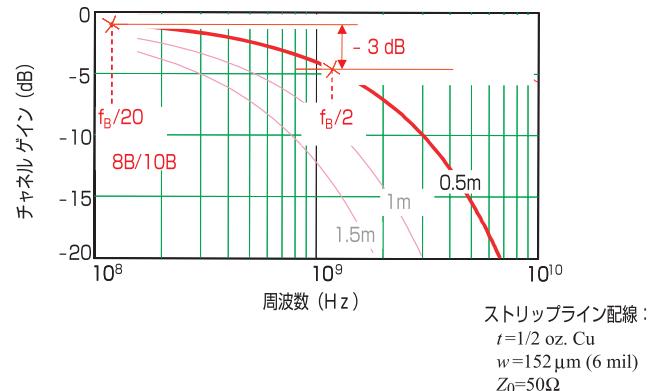

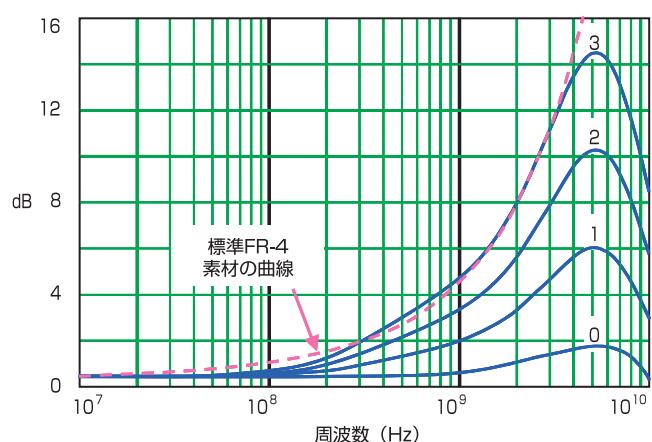

通信エンジニアは、常に正弦波を扱っているため、この歪みを周波数ドメインで説明する必要があります。図1は、完全に終端処理された標準の50オームストリップライン(または100オーム差動ストリップライン)のチャネルゲイン(周波数応答ともいう)を示したものです。このストリップラインはローパスフィルタに似た働きをするので、低周波よりも高周波の正弦波を減衰させます。

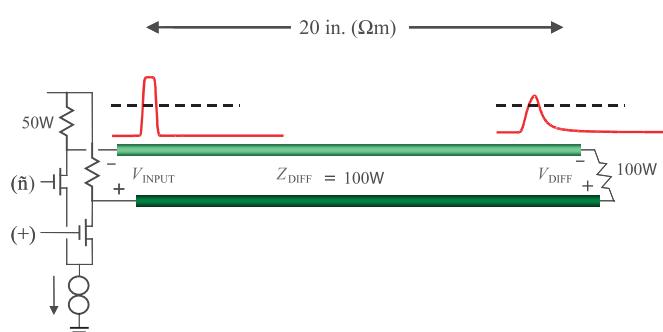

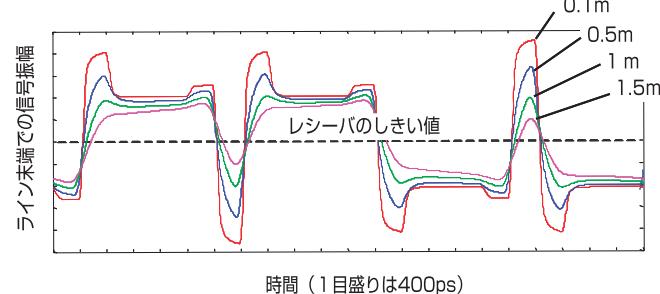

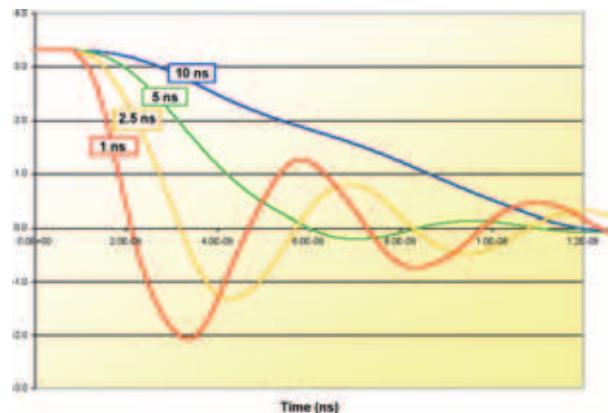

図2は、20インチ(0.5m)のFR-4ストリップラインを通るデジタル信号に特有の劣化を示したものです。配線内での誘電損失と表皮効果損失により、入力パルスの振幅が減少し、立ち上がりと立ち下りエッジが遅くなります。標準的なパルスよりもはるかに小さな受信パルスを、「ラントパルス」と呼びます。バイナリ通信システムでは、レシーバのしきい値を十分なマージンを持って超えることができないラントパルスは、ビットエラーの原因になります。

ここでは、高速シリアルリンクでラントパルスの振幅を低下させるものとして、配線やケーブルでの損失、コネクタや他の信号接続部による反射、そしてドライバとレシーバの制限帯域の3つを取り上げます。

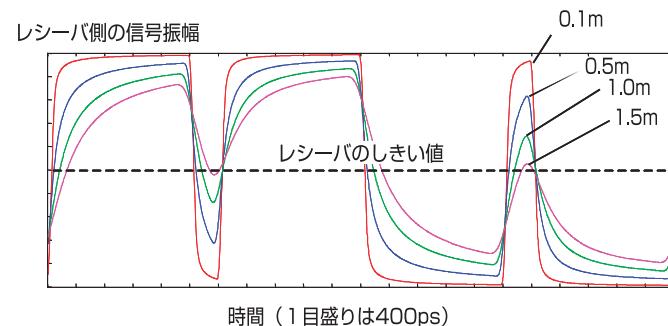

図3は、古典的な劣化のテストを示したものです。この独特の波形（テスト信号の長い平坦な部分がワースト ケースになるように設定してあり、この部分はデータ コードで使われる1または0の最大長にあたる）は、ラント パルスの振幅を表しています。レシーバ側で測定されたこの単一波形は、反射やクロストーク、その他ノイズがない場合におけるチャネル劣化のワースト ケースのテスト波形です。配線が長くなると、さらに劣化が進み、この例では最終的に1.5mでレシーバにエラーが生じます。

レシーバにおける信号品質の基準の1つは、電圧マージンです。この数値は、サンプリングを行った時点の信号の振幅とレシーバのしきい値との差の最小値（単位はボルト）に相当します。反射やクロストーク、その他のノイズのないシステムでは、理論上、極めて小さな電圧マージンで動作が可能で、システムを完全に動作させることも可能となります。

しかし、実際のシステムでは、システムで発生する反射やクロストーク、他のノイズの振幅がすべて最大になっても吸収できるだけの十分なノイズマージンを確保する必要があります。また、限られた帯域とレシーバ固有のノイズを相殺して、受信信号がしきい値を十分に超えるように維持する必要があります。

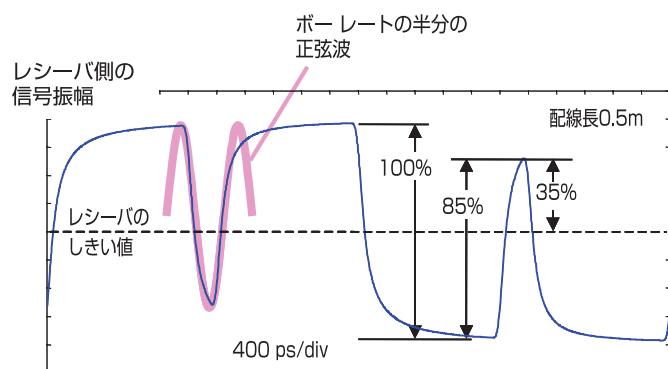

図4の例では、ラント パルスの振幅は、低周波信号の振幅の公称値の85%に相当し、レシーバのしきい値は公称値の50%ではなく、35%のみ超過しています。ラント パルスがさらに小さくなり正常値の75%の値になると、電圧マージンが半分に減少してノイズの発生量が多くなり、大きな痛手にはなりますが、それでもなお動作は可能です。イコライゼーション機能を使用しない一般的なバイナリ通信では、到達するラント パルスの振幅は低周波のパルス振幅の70%以上であることが望されます。

## ラント パルスの劣化

図4の左側に、2ボーの周期の正弦波があります。ラント パルスのパターン (101) がこの正弦波に似かよっているため、ラント パルスの振幅をチャネル減衰の周波数ドメイン曲線から推測することができます。では試してみましょう。

図4のデータ波形のボー レートは2.5 Gbpsです。この周波数の半分(等価の正弦波の周波数) は1.25 GHzに相当します。図5により、配線長0.5mの曲線から、4.5dB減衰する周波数が1.25 GHzであることが分かります。同じ曲線から、1.5dB減衰する周波数がこの周波数の1/10であることも分かります。これは、8B10Bコード データ伝送システムの対象となる最低周波数にほぼ相当します。これら2つの値の差(-3dB)は、レシーバにおけるラント パルスの振幅と低周波信号の振幅との比率にほぼ等しくなります。-3dBだけの劣化であれば、システムはソリッド リンク性能の周波数ドメインでの評価基準である70%を満たしており、配線長0.5mにおける時間ドメインでの波形が良好である理由がよく分かります。

図4をよく見ると、時間ドメインでのラント パルスの実際の振幅は85%であり、周波数ドメインから推測した-3dBほど悪い値ではありません。この矛盾の原因の一部は、矩形波に含まれる高調波にあります。これは基本波の振幅が基本波を取り出した矩形波信号の振幅を超えるためです。また、時間ドメインと周波数ドメインとのおおざっぱな変換をする際に当然生じるあいまいさが原因でもあります。簡単な周波数ドメインでの評価基準では、これらの要因を控えめに推定することになります。

図1 長いIPC基板配線の実効チャネル ゲインは、配線幅、誘電素材、配線長、コネクタのタイプに依存

図2 配線が長いと、入力パルスの振幅が減少し立ち上がりと立ち下りエッジが劣化

図3 ワーストケースのラント パルス波形の振幅を示すテスト波形

図4 ラント パルスの振幅は低周波信号の振幅の85%に相当し、しきい値を超える電圧マージンが公称値の50%ではなく35%に減少

図5 2.5 Gbpsシステムの高周波チャネルと低周波チャネルのゲインの差は3dB

データコードが8B10Bコードよりも0や1の列が長くできる場合は、「対象最低周波数」としてそれに相当するより低い周波数を使用する必要があります。時間ドメインでは、受信信号がラントパルス発生前に振幅の最大範囲の底（または天井）に近接してクリープする（這いつくばう）現象が見られます。これは、ワーストケースのラントパルスがしきい値を超えるのをさらに困難にしています。

経験的に、最大動作周波数（101010のパターン）で動作する場合と、最低動作周波数（コーディングしたデータのランレンジスで決まる）で動作する場合のチャネル減衰の違いから、レシーバでのラントパルスの振幅劣化の度合いが即座に推測できます。この方法では、リンク性能をおおざっぱにしか推測できません。時間ドメインでの厳密なシミュレーションにはなりませんが、リンクの動作の理解にはおおいに役に立ちます。

ラントパルスの劣化が1dB未満のチャネルでは、通常のCMOSロジックの場合いずれも良好に動作します。ただし、低スキーのクロックを分配するか、あるいはレシーバ側にクロックリカバリユニットを使用することで、クロックスキーの問題が解消されていることが前提になります。チャネルの劣化が3dB程度の場合、レシーバのしきい値を厳密に設定し適切に制御できる差動アーキテクチャ以外は必要ありません。チャネルの劣化が6dBになると、イコライゼーション機能が必要になります。

### 伝送プリエンファシス

ザイリンクスのVirtex™-4 RocketI/O™トランシーバには3種類のイコライゼーション機能が使用されており、より深刻なチャネル劣化への対応が可能です。1つ目の機能は、伝送プリエンファシスです。

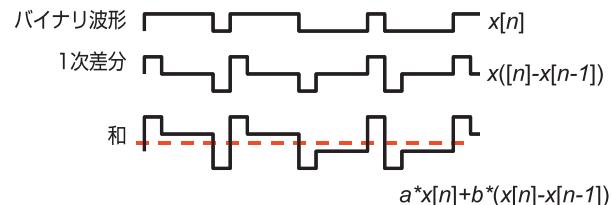

図6は、単純なバイナリ波形 $x[n]$ と、その1次差分波形 $x[n]-x[n-1]$ を示したもので、微積分に詳しい読者であれば、この1次差分波形が一種の導関数演算であることがお分かりいただけます。すべてのエッジの部分で、差分波形は大きくキックします。伝送プリエンファシス回路では、主信号と1次差分波形を特定の比率で足し合わせて、すべての変化点の先頭に大きなキックを重ね合わせます。レシーバで観測されるように、各キックによって信号の低周波の部分の振幅が増大することなくラントパルスの振幅が増大します。低周波の部分はすでに十分な振幅があります。

この1次差分の考えは、プリエンファシスの動作の理解に役立ちますが、構成内容はこれとは異なります。実際の回路では、2つの信号ではなく、プリカーサー、カーサー、ポストカーサーという3つの遅延した項目の足し算になります。このアーキテクチャを用いることで、この3つの項目に関連した係数を調整することにより、1次差分と2次差分の両方を求めることが可能になります。プログラマブル5ビット乗算型DACでこれら3つの係数を制御します。1番目と3番

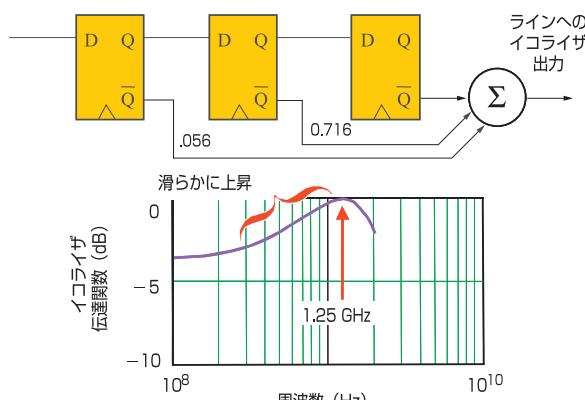

目の振幅は2番目のものに対して常に反転していますが、この方法は1番目と3番目のフリップフロップのNOT-Q出力を使用することにより実行されます。例として、図7に特定の係数のセット（-0.056、0.716、-0.228）に相当する周波数応答をプロットします。

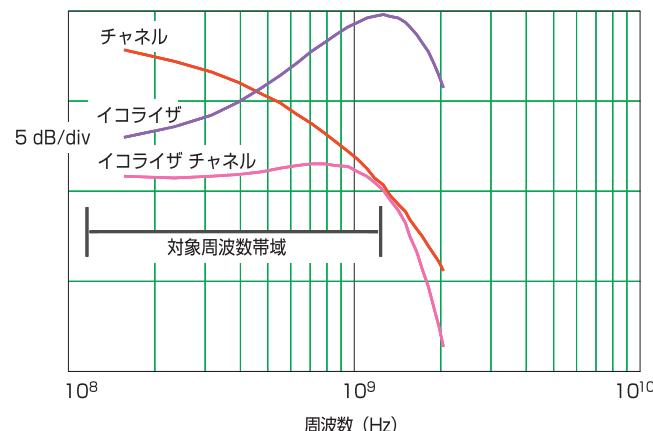

DCから1.25 GHzまでのクリティカルな範囲では、プリエンファシスの応答曲線は図5に示す下降する曲線とは正反対に、滑らかに上昇しています。応答曲線のピークは1.25 GHzにあります。このプリエンファシス回路を高いデータレートのクロックで使用する場合、このピークはデータレートに対応した高い周波数に移行し、常に、必要なデータレートの半分に相当する周波数になります。

図8は、配線長1mでのチャネル応答曲線にプリエンファシスの応答曲線を重ね合わせて合成した結果（イコライズされたチャネル）を示しており、いずれの曲線よりもはるかにフラットな形をしています。単純に考えると、よりフラットな合成チャネル応答曲線が得られれば時間ドメインでの信号の形状が良くなります。

図9ではプリエンファシスの時間ドメインでの効果を示します。配線長が短い場合にはイコライズ過多の信号形状になります。バイナリのシステムでは、信号の振幅が最大になったときにレシーバが飽和しないだけの十分な高さの余裕があれば、各変化点にオーバーシュートがあっても問題はありません。配線長1mでは、信号の形状はかなり良好で、ラントパルス劣化はほとんど見られず、ジッタもほとんどありません。配線長1.5mでの波形は、ラントパルスの評価基準である70%と一致しています。単純な差動アーキテクチャに比べ、プリエンファシス回路は正常に動作するチャネルの配線長を少なくとも2倍にします。

### リニア レシーバ イコライザ

プリエンファシス回路のほか、RocketI/Oトランシーバには高機能な6-ZERO 9-POLE レシーバベースのリニアイコライザも搭載されています。この回路はデータスライサの前にあります。これは、アクティブアナログイコライザが3段接続された構造になっており、各イコライザは個々にイネーブルすることができ、すべてをオフにするか、1つ、2つ、または3つすべてを続けてオンにすることができます。

図6 伝送プリエンファシス回路はすべての変化点の先頭に大きなキックを生成

図7 DCから1.25 GHzまでのクリティカルな範囲では、プリエンファシスの応答曲線は滑らかに上昇

図10は、このレシーバ イコライゼーション アーキテクチャにより得られる4つの周波数応答曲線を示しています。イコライザの各セクションは、チャネル応答が2.5 GHzで約3dB減衰する標準的なPC基板チャネルの特性に調整してあります。すべてのステージをオンにすると、2.5 GHzでほぼ9dB増強できます。応答曲線は5 GHzまで上昇しているため、このイコライザは10 Gbpsを超えるデータ レートまで使用できます。

イコライザの設定を行う場合、最初に全体のチャネル応答が最適になるようにRXリニア イコライザのセクション数を選択します。次に、伝送プリエンファシス回路の5ビット プログラマブル係数を使用して全体のパルス応答を微調整し、ISI(符号間干渉)やジッタまたはその両方を最小にします。回路の完成後は、レシーバ内部のクロック

図8 全体の応答がどちらの曲線のみの場合よりもよりフラットなチャネルを備えるプリエンファシス回路の構成

図9 プリエンファシス回路は正常に動作するチャネルの配線長を少なくとも2倍にする

図10 レシーバのリニア イコライザは、各種長さのFR-4 PC基板配線の応答に合わせてプログラムされた、4種類の応答曲線から選択可能

位相調整機能を使って、ビット誤り率 (BER) のバスタブ曲線を描き出せば、イコライザの設定が正しいことが確認できます。

これら2種類のイコライゼーション機能には柔軟性があるため、非常に多くのシリアルリンク標準に対応し、伝送される信号の仕様に適合させることができます。その上、レシーバ ベースのイコライゼーション機能を追加することで、最高性能のシステム動作が維持できます。

### デシジョンフィードバック イコライザ

予測できない劣悪なチャネル性能に対処する最後の手段として、RocketIOトランシーバには手動で調整できる6タップのデシジョンフィードバック イコライザ (DFE) が搭載されています。DFEはレシーバのスライサ回路に組み込まれています。このDFEは、もともと高いシリアル データ レートの処理用に設計されていない低品質の旧型チャネルに特に有効です。DFEには、クロストークを悪化させることなく入力信号を強調するという優れた特性があります。

信号処理に詳しい読者であれば、DFEがイコライゼーション ネットワークにPOLEを挿入し、TXプリエンファシス回路がZEROを作り出していることがお分かりになると思います。(DFE回路などのデジタル イコライゼーションに関する非常に分かりやすい解説書として、「The Theory and Practice of Modem Design」(John A.C. Bingham著)をご参考ください。)

DFEや、TXプリエンファシス、RXリニア イコライザは一体となって、きわめて豊富な調整機能を提供します。

### 結 論

ラント パルス劣化が6dB程度のチャネルであれば、簡単なプリエンファシス調整により、リンクが動作する配線長を容易に2倍にすることができます。

6dBを超えるラント パルス劣化が予想される場合は、最終的なイコライザ調整をする前にシステムを詳細にシミュレートすること強く推奨します。チャネルのモデリングに必要なRocketIOモデルや関連デザイン キットに関しては、ザイリンクス販売代理店にお問い合わせいただくな、ザイリンクスのWebサイトをご覧ください。モデリング作業を是非にお試しいただき、イコライゼーションにより回路の性能の大幅な向上が実現することを体感ください。

「High-Speed Digital Design and High-Speed Signal Propagation」の著者、Howard Johnson博士は、オックスフォード大学をはじめ、世界各地でデジタル設計者向けテクニカルワーキショップを開催しています。詳細は、www.sigcon.comをご覧いただき、howie03@sigcon.comまでお問い合わせください。

図1、3、4、9はJohnson氏およびGraham氏の承諾を得て「High-Speed Signal Propagation: Advanced Black Magic」 Prentice-Hall, 2003年より掲載したものです。

PowerPC405

CPUデバッグ

1人3役の、スーパードクター。

FPGA

ロジックデバッグCPUとロジックの

協調デバッグ

ソフト／ハードのデバッグ、実機での連動により、真の協調デバッグをこれ1台で。Virtex-4FXとVirtex-II Pro (PowerPC405)専用エミュレータ。

## F-Sightの特長

- Virtex-4FXとVirtex-II Pro内蔵PowerPC405のCPUデバッグに対応

- HDLソース・ウィンドウから、アナライザ観測信号の登録・自動配線が可能 (プロービング機能)

- HDLソース・ウィンドウ上でFPGA内部回路の任意信号値を表示 (クイック・インスペクト機能)

- リードデバッグ機能により、HDLソース上で信号の確認、ブロックRAMの参照が可能

- CPU (ソフト)とFPGA (ハード)の協調デバッグが可能

- アナライザ機能 (標準8ch 拡張オプション32ch)

- FPGAのコンフィギュレーションも超高速

- CPU外部フラッシュメモリ対応

- 手のひらサイズ・軽量・コンパクト設計

- 操作性抜群のデバッガソフト「CSIDE」を標準装備。

F-Sight 2VP-PPCは、ザイリンクス社製Virtex-4FXとVirtex-II Pro専用のデバッグ・ツールです。これ一台で、コンフィギュレーションからFPGAハードウェアとPowerPCソフトウェアの協調デバッグをサポート。コンピューテックスだから実現できたFPGAのハードとCPUのソフトウェア協調デバッグ環境。自在でスムースなデベッキングを体感してください。

## ソフト／ハードの同時デバッグ機能

PowerPC405

CPUデバッグ

- 高級言語レベルデバッグ

- CPUブレーク機能

FPGA

ロジックデバッグ

- HDL対応

- プロービング機能

CPUとロジックの

協調デバッグ

- CPUトレース機能

- アナライザ機能

## 株式会社コンピューテックス

〒605-0846 京都市東山区五条橋東四丁目432-13 尾山町ビル

お問い合わせ先 → 営業部・TEL: 03-3253-2901 FAX: 03-3253-2902

URL <http://www.computex.co.jp/>

上記URLより製品情報、最新情報、リリース予定、サポート情報、各種ダウンロードなどのホットな情報を御覧いただけます。

# 低コストFPGAにより変貌を遂げるシステム ランドスケープ

低コストFPGAの登場が新時代の幕開けを予告

Richard Wawrzyniak

Sr. Market Analyst: ASIC and SoC

Semico Research Corp.

richw@semico.com

今日我々は、魅力に満ちたまったく新しい民生機器アプリケーションが突然どこからともなく出現するような、非常に刺激的な時代に生活しています。プログラマブル ロジックが成長を続けその概念が市場全体に広く浸透するにつれて、FPGAがこのような時代のエネルギーを活かすことが可能となります。

FPGA業界は、ムーアの法則に従って進展を遂げてきました。このムーアの法則によると、半導体デバイスで使用できるトランジスタの数は1年半から2年ごとに倍増すると予測されています。設計者が使用できるトランジスタ数が増加し、プロセス技術の微細化がかつてないレベルへと進行すれば、それは直ちにデバイスの性能向上につながり、チップ面積も低減します。

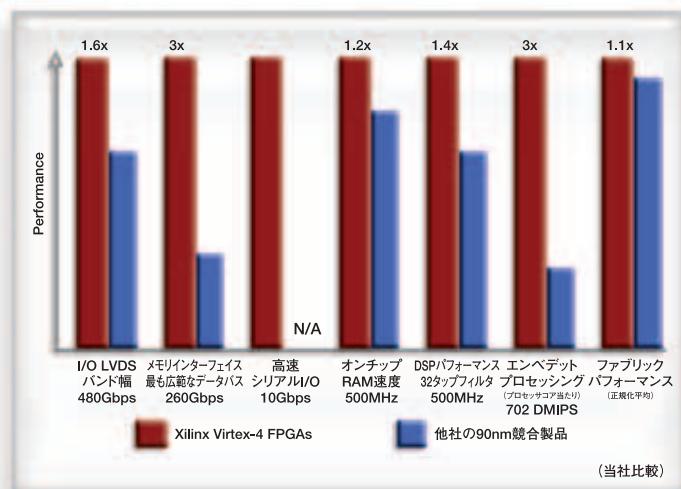

その良い例が、最近導入された90 nmプロセス技術を採用したFPGAです。微細化に伴い、FPGAはこれまで以上のロジック素子とエンベデッド メモリの組み込みが可能となり、同時にソリューションに必要なチップ面積が低減されました。130 nmプロセス技術で製造したデバイスを90 nmプロセスで実現することにより、高性能化に加えチップサイズの縮小化が可能です。チップサイズと歩留まりはデバイスの価格に大きな影響を与えるため、この最新技術を導入した90 nmデバイスは、より低価格で提供できるようになります。

では、これによってシステムのランドスケープはどのように変化するのでしょうか。ある性能レベルをより低い価格で提供できれば、システム設計者は、最終製品の性能を向上させBOMを低減することができます。その結果、システム機器のメーに高収益をもたらし、システム機器全体のコスト削減を実現します。

デバイス コストの削減がシステム コストの削減につながるというのは非常に単純に聞こえるかもしれません。しかし、真の答えはコスト削減よりもはるかに深いところにあります。より正確な視点で理解するために、FPGA市場とASIC業界全体を促して、その背景にあるものを見てみましょう。

## 厳しいデザイン環境

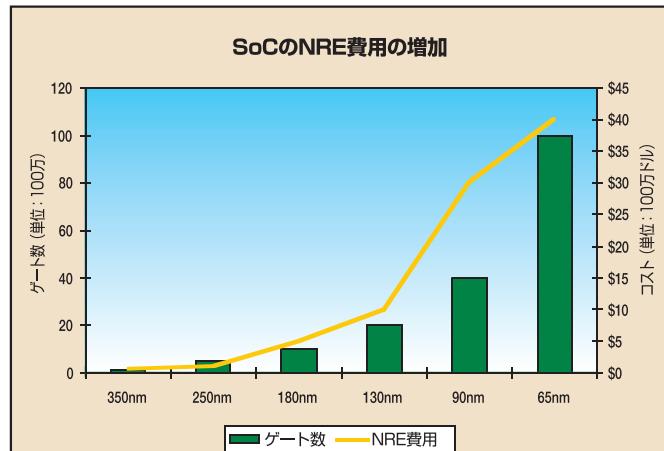

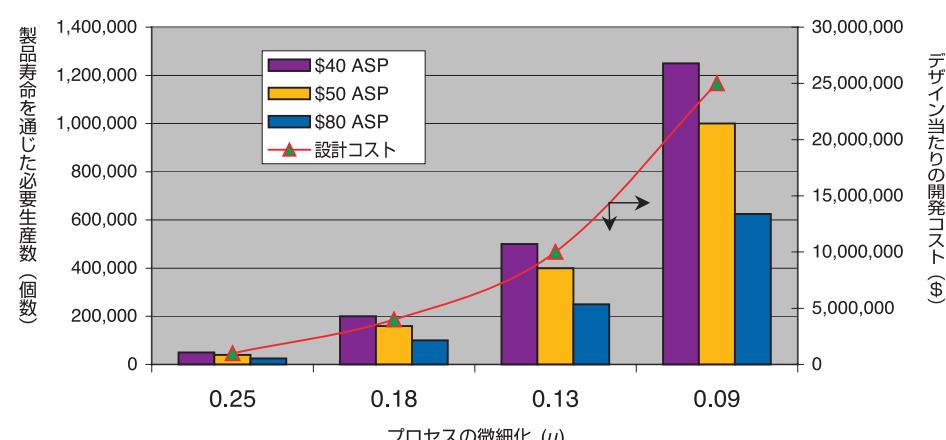

今日の市場環境には、ASIC設計に悪影響を及ぼす一連の傾向が見られます。中でもよく論議されるのが、ASICの開発コストの1つであるNRE（初期開発費）の上昇です。このNRE費用がプロセスの微細化によってどのように増加してきたかを図1に示します。

NRE費用は、主にデバイスの複雑化に伴い増加します。使用可能なゲート数がプロセス ノードごとに増加するにつれて、それらのゲートを市場ニーズに対応するようにデザインに組み込む作業も増大します。

設計者は、マーケット ウィンドウに対応するために最短期間でのデザイン設計が必要であることを認識しているにもかかわらず、新規にSoCデザインを行うためのエンジニアリング リソースや十分な開発費用を持たない場合、NRE費用がゼロないしはそれに近いプログラマブル ロジックは非常に有効な手法となります。

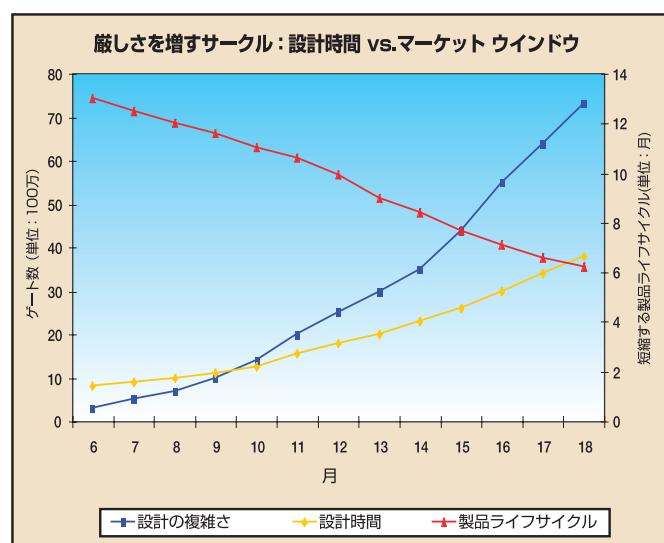

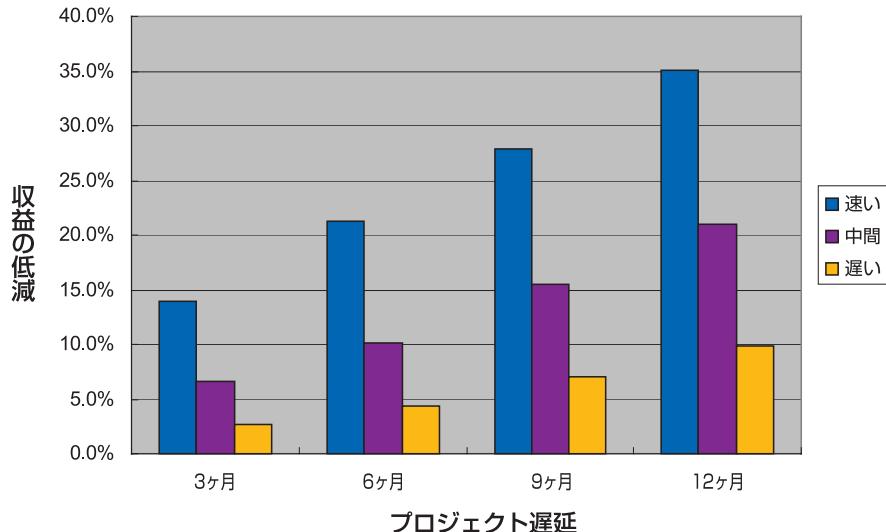

図2は、設計サイクル時間やゲート数、製品のライフサイクルの関係を示しています。設計者は、縮小するマーケット ウィンドウに対応しなければならないというプレッシャに直面しながら、ますます複雑化するデザインと格闘しなければなりません。同様に、短命化の傾向にある製品のライフサイクルに対応することは非常に困難なことです。

このような状況は、最終的にASIC設計者にとってより厳しいデザイン環境をもたらします。デザインの完成前にもかかわらずターゲットとしていた市場が変化してしまう可能性があり、その結果、デザインの変更を余儀なくされます。

さらに、複雑なASICソリューションの開発コストの増加に伴い、そのソリューションがターゲットにする市場規模も拡大する必要があります。仮に、ある複雑なASICの開発コストが3,000億ドル規模だとすると、そのシリコンの初期開発費用を回収するには、ターゲット市場が開発コストの何倍もの規模である必要があります。今日、その初期費用を確実に回収できるほど大きなユニットの生産量を見込めるアプリケーションは、そう多くはありません。

ASICを採用したデザインの減少を招いているこの他の要因として、開発コストの増加、製品ライフサイクルの短命化、マーケット ウィンドウの縮小があります。

## 等式を変える低コストFPGA

ここまで、今日のASICの市場動向について検討してきましたが、次に、低コストFPGAがこの市場にどのように変化をもたらすかを見てみましょう。

設計者は、プログラマブル ロジックの伝統的な強味である低い市場参入コスト、標準部品としての入手の容易さ、短い設計サイクル、デバイス自体のリプログラマビリティ、実用的なアーキテクチャといった特長を、システム ソリューションに活かせるようになります。その上、FPGAはテストデバイスとして使用することが容易

で、さまざまな半導体知的資産（SIP: Semiconductor Intellectual Property）の調査や実証が可能になります。これは、スタンダードセルやSoCの市場では不可能です。ASIC設計者がFPGAを採用すると、従来のスタンダードセルやSoCを使用して1種類のSIPを検査する時間で、何種類ものSIPをテストすることができます。これは、ASIC設計者が最良のシリコンソリューションにたどり着くための大きな助けとなります。

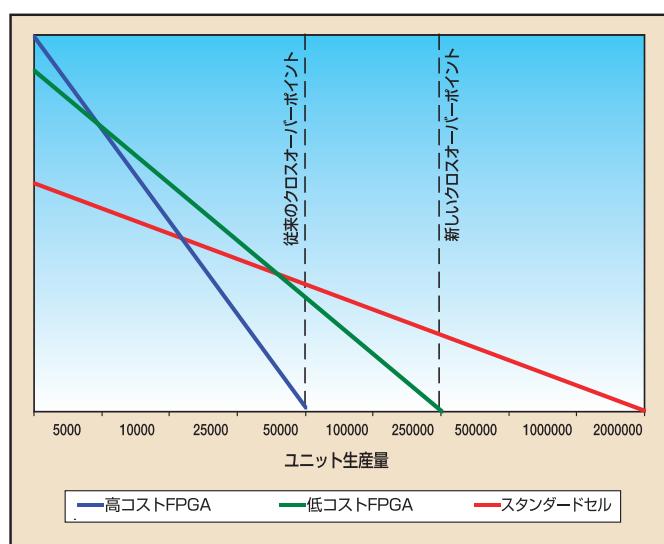

これだけではありません。FPGAはさらなるメリットをASIC設計者に提供します。かつてFPGAデバイスが今よりも高価であった頃、ASIC設計者は、FPGAを使ってプロトタイピングを行い、生産台数が限られた分野にFPGAソリューションを導入してきました。しかし、約3万～10万台単位の生産数（最終アプリケーションの価格依存度による）になると、ASICソリューションへ移行するケースがほとんどでした。この時点で、プログラマブルロジックの採用によって得た多くの資産を放棄したことになります。設計者は、前述のような問題や欠陥があるにも関わらず、これまで伝統的に使用してきたASICのパスへ戻るわけです。

図3に示すように、FPGAの低コスト化により、スタンダードセルやSoCソリューションへの移行の生産ポイントがさらに広がりました。この図では、NREやマスクセットのコスト等の費用を含めたASICソリューションの開発コストと、プログラマブルロジックを使用したシリコンソリューションの開発総コストを比較しています。マーケットウインドウに適合するシリコンソリューションを妥当なプライスポイントで使用できることは低コストFPGAの大きなメリットです。

## 結論

より進んだ微細加工の実用化に伴い、FPGAベンダは微細化プロセス技術の採用を引き続き促進することにより、ASIC業界でのFPGAは、必要なプライスポイントでの堅固なソリューション提供を実現し、従来ASICが占めた市場へとその用途を一層拡大していくます。

設計サイクルが極めて長いために生産まで漕ぎ着けなかったデザインやエンジンシステムソリューションは、FPGAにより、以前に増して多くの成功のチャンスを手にします。これまで、重要性の高いマーケットウインドウに対応できなかったという理由でキャンセルになった機会を捉えることができるのです。

低コストでしかもフル機能搭載のFPGAの導入により、システムのランドスケープは良い方向へ変化しました。今日、ASIC設計者やシステムアーキテクトは、以前よりもはるかに容易にFPGAを生産工程に組み入れ可能になったことを十分認識した上で、プログラマブルロジックソリューションを利用することができます。

図1 プロセス技術の進歩に伴うNRE費用

出典: Semico Research Corp.

図2 デザインと市場動向の比較

出典: Semico Research Corp.

図3 生産数から見たFPGA別の採用可能度

出典: Semico Research Corp.

# 量産プログラマブル革命をリード

PLDを他社に先駆け低成本 システム向けにリードするザイリンクス

Sandeep Vij

Vice President, Worldwide Marketing

Xilinx, Inc.

sandeep.vij@xilinx.com

ザイリンクスは、低成本/量産アプリケーションの分野にFPGAのマーケット ポテンシャルを見いだした最初のFPGAメーカーです。ザイリンクスは、1998年、この市場向けに設計した最初のFPGA、Spartan™デバイス ファミリを発表しました。今日、SpartanシリーズFPGAは量産向け民生用アプリケーションに広く採用されており、出荷数は1億個を超え、10億ドル以上の累積売上を記録しています。

ザイリンクスは最新製品のSpartan-3Eファミリにより、Spartanデバイスの発表以来、そのデバイスコストを30分の1までに低減すると同時に、プラットフォーム機能の拡充を実現しよりハイレベルのインテグレーションを可能にしました。

ザイリンクスはまた、量産向けPLDには、不揮発性のCPLDソリューションが重要であることも認識しています。ザイリンクスのCPLD製品は、最小コストのXC9500/XLデバイスから超低消費電力のCoolRunner™-IIデバイス ファミリまで、業界で最も包括的なソリューションを提供します。これにより、ザイリンクスはCPLDの市場シェアを16四半期連続で伸ばし、現在では同市場で2位の座に就くことができました。

ザイリンクスは、量産向けプログラマブル ロジック デバイスの市場を開拓し、製品を開発してきました。本号では、この市場向け製品やアプリケーションに関する記事を中心に掲載するとともに、実際にこれら製品を使用しているユーザーからの多数の記事を紹介します。•

## Table of Contents

|                                          |    |

|------------------------------------------|----|

| 低成本 プログラマブル ロジックの新時代を拓くSpartan-3E FPGA…  | 9  |

| Spartan-3Eファミリに追加されたコンフィギュレーション用新オプション…  | 11 |

| リコンフィギュラブルFPGAによる高解像度Ogg/Theoraビデオエンコード… | 14 |

| Spartan-3 FPGAを利用したデジタル信号処理アルゴリズムの実装…    | 17 |

| Spartan-3 FPGAのDDRメモリインターフェイス設計…         | 21 |

| 新機能を搭載したCoolRunner-II CPLD…              | 23 |

| ザイリンクスのロジック コンソリデータで部材 (BOM) コスト低減…      | 26 |

| CoolRunner-IIのシリコン機能を利用したコスト削減…          | 28 |

| Spartan-3/3Eの機能を利用したデザインのエリア最適化…         | 31 |

| ASSPメーカーに展望を与える低成本EasyPath FPGA…         | 34 |

| Spartanファミリをフラットパネル ディスプレイに採用…           | 38 |

| 信号品質の制御…                                 | 41 |

| 変遷するオートモーティブ向けECU設計の現状…                  | 44 |

| 低成本のPCI Expressソリューション…                  | 47 |

# 低コスト プログラマブル ロジックの 新時代を拓くSpartan-3E FPGA

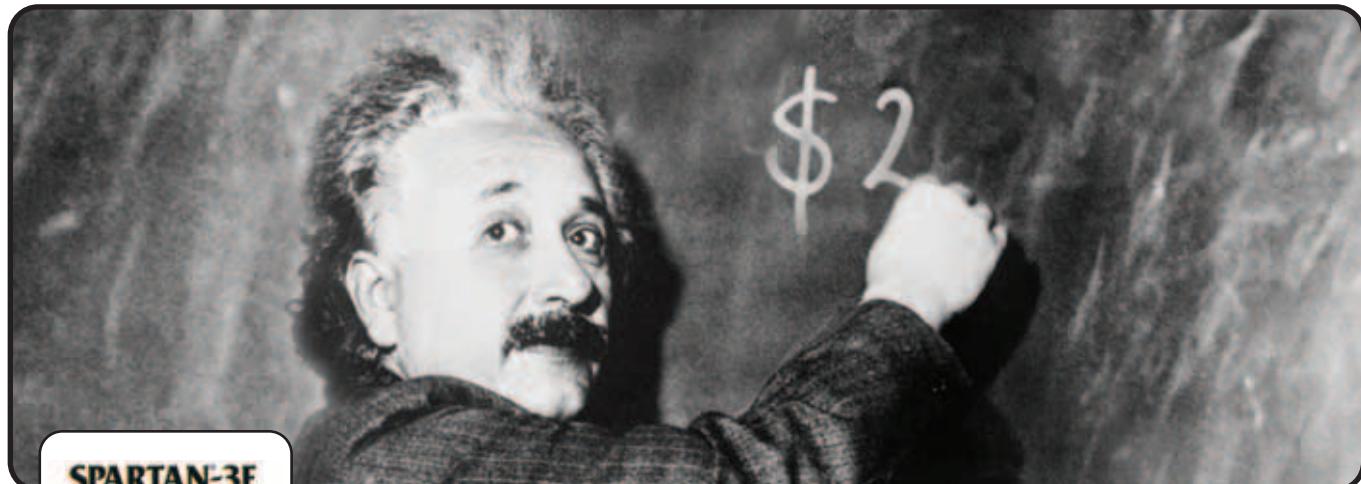

業界初2ドル以下で入手可能な10万システムゲートFPGA

Spartan-3E XC3S100Eデバイス

Richard Terrill

Senior Manager, High-Volume Products Marketing

Xilinx, Inc.

richard.terrill@xilinx.com

1998年に発表されたSpartan™は、低コストなアプリケーションに最適なプログラマブルソリューションとして設計された世界初のFPGAシリーズです。ザイリンクスは最新製品Spartan-3Eを発表し、Spartan FPGAファミリとしては7品種となり、その出荷数量はこれまでに1億個を超えていました。Spartan FPGAは、世界で最も低コストであると評価の高いFPGAアーキテクチャで、何千人の技術者に使用されています。

ザイリンクスは、ムーアの法則により、かつてない低価格のFPGAであるSpartanを実現しました。このSpartan-3Eファミリは、先端の90 nmプロセス技術を採用したSpartanファミリとして、第三世代目のファミリで、これまで最も低い製造コストを実現しました。この低コスト化により、プログラマブル ロジックは、以前はASICやゲートアレイ テクノロジが採用されていた量産向け低コストのプロダクション アプリケーションにも応用が可能となりました。

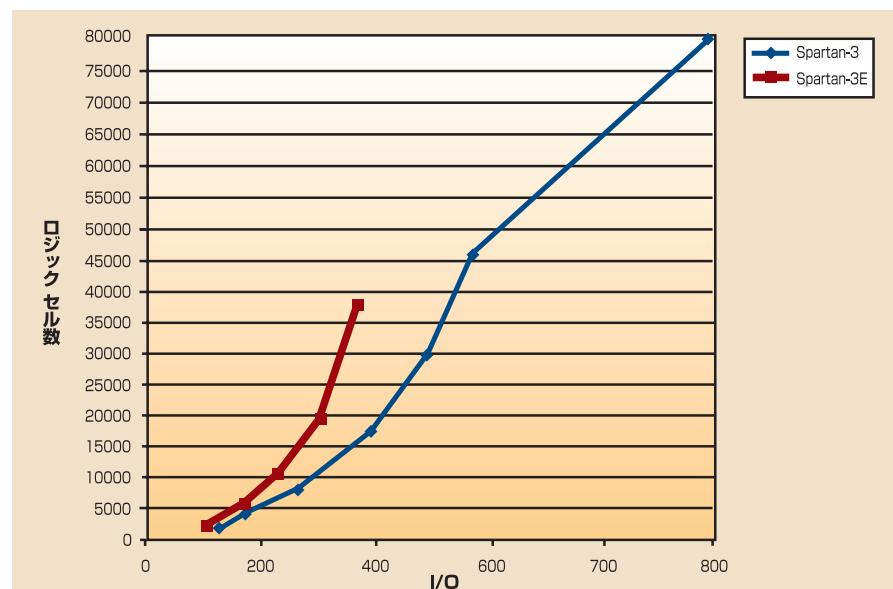

2003年に発表されたSpartan-3ファミリは、I/O重視型のデザインに最適化されており、多くのI/Oを必要とするデザインに最適です。一方、Spartan-3Eファミリは、ロジック重視型のデザインに最適化されており、I/Oと比較してゲート数の高いデザインに適しています。また、旧製品のSpartan-II/IIIEおよびSpartan-XLファミリは、レガシー デザインや5Vや3.3Vなどの高い電圧を使用するシステムに最適です。

Spartan-3ファミリは、これまでASICやゲートアレイが採用されてきたシステム機器の生産面において目覚しい成功を収めてきました。たとえば、フラットパネル ディスプレイ システムにおいては、ディスプレイ ドライバの管理や機能の制御を目的にSpartan-3デバ

イスが数多く採用されています。レイアウト後のデザイン変更やマーケットの変化に応じたシステム変更が容易なFPGAは、非常に魅力的なデバイスであると評価される所以です。

Spartan-3Eファミリは、プログラマブル ロジックの低いNRE(初期開発費)と高い柔軟性を保持しつつ、大幅なデバイスコストの削減により、FPGAの適用範囲を量産分野にまで拡張してきました。Spartan-3Eは、ASICとのコストのクロスポイントが25万個に設定されています。これは、総コストだけを考えた場合、25万個以下の量産は、Spartan-3EはASICのソリューションより値段のメリットがあるということです。

## Spartan-3Eファミリ

ザイリンクス最新の低コストFPGAファミリであるSpartan-3Eファミリは、プライス ポイントをかつてないレベルまで大きく引き下げました。ザイリンクスは、90 nmプロセス技術と300 mmウェハを採用し、アプリケーション主導のアーキテクチャを選択することにより、従来はマスクプログラム型ASICを採用していた量産分野やアプリケーションにまでFPGAの採用の範囲を拡張しました。Spartan-3Eは、FPGAの中で最も低いロジック当たり単価(CPL: Costs-Per-Logic)を提供します。

Spartan-3Eは、コスト優先のデジタルコンスマーアプリケーション向けに設計された製品で、多くの量産/低コスト アプリケーションがこの先進の機能と性能によるメリットを享受することができます。

Spartan-3Eファミリは、10万ゲートのXC3S100Eから最大160万ゲートのXC3S1600Eまでの5品種を用意し、64/66 PCIやMini LVDS、低コスト信号処理に最適な高速エンベデッド乗算器などの機能を追加しながら、いずれも低コスト アプリケーションに対応しています。表1は、Spartan-3Eファミリの主な機能を示しています。

表1 Spartan-3Eファミリの主要機能マトリクス

| Spartan-3E FPGAファミリ |          |          |          |           |           |

|---------------------|----------|----------|----------|-----------|-----------|

|                     | XC3S100E | XC3S250E | XC3S500E | XC3S1200E | XC3S1600E |

| システム ゲート数           | 100K     | 250K     | 500K     | 1,200K    | 1,600K    |

| ロジック セル数            | 2,160    | 5,508    | 10,476   | 19,512    | 33,192    |

| ブロックRAMビット数         | 72K      | 216K     | 360K     | 504K      | 648K      |

| 分散型RAMビット数          | 15K      | 38K      | 73K      | 136K      | 231K      |

| DCM数                | 2        | 4        | 4        | 8         | 8         |

| 乗算器数                | 4        | 12       | 20       | 28        | 36        |

| I/O規格数              | 18       | 18       | 18       | 18        | 18        |

| 最大シングルエンドI/O数       | 108      | 172      | 232      | 304       | 376       |

| 最大差動I/Oペア数          | 40       | 68       | 92       | 124       | 156       |

| 提供パッケージとI/O数        |          |          |          |           |           |

|                     | XC3S100E | XC3S250E | XC3S500E | XC3S1200E | XC3S1600E |

| VQ100 14 x 14 mm    | 66       | 66       |          |           |           |

| CP132 8 x 8 mm      |          | 92       | 92       |           |           |

| TQ144 20 x 20 mm    | 108      | 108      |          |           |           |

| PQ208 28 x 28 mm    |          | 158      | 158      |           |           |

| FT256 17 x 17 mm    |          | 172      | 190      | 190       |           |

| FG320 19 x 19 mm    |          |          | 232      | 250       | 250       |

| FG400 21 x 21 mm    |          |          |          | 304       | 304       |

| FG484 23 x 23 mm    |          |          |          |           | 376       |

図1 Spartan-3のスタッガ型I/OとSpartan-3EのインラインI/Oとの比較

### ロジック重視型FPGA

Spartan-3Eファミリの特長は、無条件の最小コストを実現できるよう最適化されたインラインI/Oリングにあります。図1は、Spartan-3EのインラインI/OリングとSpartan-3が採用しているスタッガ型I/Oパッド手法の比較を示しています。インラインI/Oは集積度が低いほど有効で、図2に示すように一定のI/O数に対してより多くのロジック数を追加することができます。

ザイリンクスは、チップサイズをさらに縮小できるようI/Oのレイアウトを改良し、また、利用度の低いI/O規格を除外して出力バッファのサイズを変更しました。各I/Oの面積をわざわざ縮小しただけで、I/Oパッドを複数個とることが可能で、この面積の縮小が繰り返されることにより、結果としてかなり大きなエリアの低減を実現します。Spartan-3Eのこのようなアーキテクチャの変更は、多岐にわたる顧客からのフィードバックを反映した結果です。

Spartan-3Eは、Spartan-3デバイスに比べCPLが低いため、ロジック重視型デザインでは最小コストのFPGAです。これに対して、Spartan-3は、I/O重視型のFPGAデザインに適しています。このように、Spartan-3とSpartan-3Eにより、低コストシステムデザインにおける顧客のニーズに幅広く対応しています。

### Spartan-3Eの新機能

Spartan-3Eは、より低コスト化を目的に最適化したインラインI/Oリング以外に、以下の多数の新機能を備えています。

- 低コストの汎用フラッシュメモリ (SPI/BPI) を使用したコンフィギュレーションのサポート

- PCI 64/66およびPCI-Xのサポート

- DDR 333メモリ インターフェイス

- Mini-LVDS、RSDS

- DCMクロック周波数の入力レンジを最低5 MHz (ビデオに最適)まで拡大

- 325 MHz乗算器を使用することにより低コスト信号処理機能を実現

Spartan-3Eの最も重要な新機能の1つとして、低コストの汎用フラッシュメモリをサポートしています。Spartan-3Eにより、ユーザーは複数のベンダから入手可能な低コストの汎用シリアルEPROMやバイト幅のフラッシュデバイスを利用して、FPGAをコンフィギュレーションすることができます。そのコンフィギュレーションメモリを他のシステム機能に利用したり、Spartan-3Eの制御下で再プログラムしたりすることもでき、システム設計者にきわめて高い柔軟性を提供します。

### 結論

Spartan-3E FPGAファミリの登場により、プログラマブルロジックの採用を低コストシステムの製造にまで範囲を拡大しました。Spartan-3Eは、2ドル以下という低価格での提供が可能で、また、大幅なコストダウンを実現したコンフィギュレーションソリューションであることにより、ますます増大する低コストの量産向け民生機器アプリケーションの最適なソリューションとなるでしょう。

図2 Spartan-3とSpartan-3EデバイスのI/O対ロジック曲線

# Spartan-3Eファミリに追加された コンフィギュレーション用 新オプション

汎用的なシリアル パラレル インターフェイス(SPI)フラッシュメモリからの

コンフィギュレーションを、Spartan-3Eで新しくサポート

**Steve Knapp**

Sr. Applications Engineering Manager

Xilinx, Inc.

[steve.knapp@xilinx.com](mailto:steve.knapp@xilinx.com)

**Ward Williams**

Sr. Strategic Marketing Manager

Xilinx, Inc.

[ward.williams@xilinx.com](mailto:ward.williams@xilinx.com)

**Kirk Owyang**

Sr. Solutions Marketing Manager

Xilinx, Inc.

[kirk.owyang@xilinx.com](mailto:kirk.owyang@xilinx.com)

ザイリンクスの新しいSpartan™-3E FPGAファミリは、システム コストを大幅に削減する特長を追加しています。その一つに、低コストな汎用メモリからのコンフィギュレーションを新しくサポートしました。これにより、ユーザーはアプリケーション要求に最も適したコンフィギュレーション用メモリソリューションを選択することができます。コンフィギュレーション用メモリとして、業界標準の汎用的シリアル ペリフェラル インターフェイス(SPI)PROMや、パラレルNORフラッシュPROM、価格を抑えたザイリンクスのPlatform Flash、その他マイクロコントローラを備えた低コスト メモリを選択することができます。

Spartan-3Eのコンフィギュレーションピンは、コンフィギュレーション終了後はすべてユーザーI/Oとして使用できます。この結果、コンフィギュレーションメモリ内の残ったスペースを、エンベデッドプロセッサMicroBlaze™用コード、あるいはシリアルナンバやイーサネットMAC IDなどのアプリケーションデータとして活用することができます。SPI PROMやパラレルフラッシュPROMは、ランダムアクセス可能でバイトアドレス指定可能な読み出し/書き込みメモリとしても機能します。アプリケーションが追加されメモリスペースを必要とする場合は、より高集積のPROMにアップグレードが可能です。ほとんどのSPI PROMおよびパラレルフラッシュPROMは、集積度が異なっても共通のフットプリントで提供されています。

ザイリンクスのPlatform Flashは、メガビット当たりのコストが低減できるように極めて低価格に設定されており、2個のチップ(FPGA+専用のコンフィギュレーションPROM)で構成されるスタンダードのプログラマブルロジックソリューション向けに理想的な

ソリューションを提供します。このPlatform FlashはJTAGインシステムプログラマビリティや特許取得の圧縮技術を採用し、性能面でも優れています。

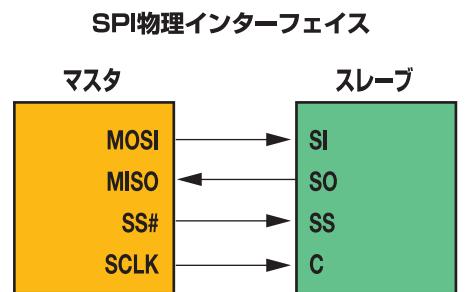

図1 SPIの物理インターフェイス

- SPIは4線式の同期シリアルインターフェイス

- SPIマスタデバイスは1個あるいは複数のスレーブと通信

- SPIマスタはすべてのタイミングをSCLKクロック信号により制御

- SPIマスタはアクティブLowのセレクト信号(SS#)によりスレーブを選択

- 接続されているSPIデバイスはすべて共通のシリアルデータ入力、出力、クロック信号を共有

表1 Spartan-3E FPGAがサポートするSPIフラッシュメモリ ファミリ

| SPIシリアルフラッシュの供給メーカー                             | テスト済みのSPIフラッシュファミリ                        |

|-------------------------------------------------|-------------------------------------------|

| Atmel                                           | AT45DBxxx                                 |

| NexFlash                                        | NX25Pxx                                   |

| Programmable Microelectronics Corporation (PMC) | Pm25LVxxx                                 |

| Silicon Storage Technology (SST)                | SST25LFxxxA<br>SST25VFxxxA<br>SST25VFxx * |

| ST Microelectronics                             | M25Pxx                                    |

表2 必要なSPIデバイスサイズと見積り容量

| Spartan-3Eデバイス | コンフィギュレーションビット | 最小SPIデバイス容量 | コンフィギュレーション後の未使用メモリ |

|----------------|----------------|-------------|---------------------|

| XC3S100E       | 581K           | 1 Mb        | 443K                |

| XC3S250E       | 1,352K         | 2 Mb        | 696K                |

| XC3S500E       | 2,267K         | 4 Mb        | 1,829K              |

| XC3S1200E      | 3,832K         | 4 Mb        | 264K                |

| XC3S1600E      | 5,958K         | 8 Mb        | 2,234K              |

SPIフラッシュPROMは、量産向け民生用電子機器に広く使用されています。このようなアプリケーションでは、エンベデッドプロセッサ用のシステムパラメータやコードをPROMに格納します。また、SPIフラッシュPROMを使用することにより、Spartan-3E FPGA向けに低コストで、しかもより少ないピン数の構成が可能になります。SPIフラッシュメモリのメーカーは複数あり、同じパッケージフットプリントで種々の集積レンジのデバイスが提供されています。

パラレルNORフラッシュは、MicroBlazeソフトコアプロセッサのようなエンベデッドプロセッサを搭載したFPGAアプリケーションに最適なソリューションです。電源を投入すると、FPGAはパラレルフラッシュの一方の端からコンフィギュレーションを開始します。コンフィギュレーションが終了すると、MicroBlazeプロセッサはメモリのもう一方の端から直接実行を開始するか、あるいは外部SDRAMのシャドウ空間にコードを移動します。

### SPIとは？

シリアルペリフェラルインターフェイス(SPI)は、4線式の同期インターフェイスです(図1)。SPIは、もともとCPU、MCU、ペリフェラルなど、SPIプロトコルをサポートするデバイス間のシリアル通信用インターフェイスとして考案されたものですが、今日ではエンベデッドプロセッシングや民生電子機器の市場で広く使用されています。今日、多くのマイクロコントローラが、サードパーティ各社の種々のペリフェラルとともにSPIを採用しています。

### SPIフラッシュのメーカー

SPIは標準の4線式インターフェイスですが、市販されている各SPIフラッシュPROMは、異なるコマンドプロトコルを使用しています。現在、表1に示す5社のメーカー(Atmel、NexFlash、Programmable Microelectronics Corporation [PMC]、Silicon Storage Technology [SST]、ST Microelectronics)のSPIフラッシュPROMがテスト済みでサポートされています。この他メーカーのSPIも現在テスト中で、近い将来サポートする予定です。

### メモリ要件

1個のSpartan-3Eのコンフィギュレーションには、約600Kから6Mビットのメモリが必要になります。これは、今日の大容量のSPIにとってわずかなメモリ容量にすぎません。表2は、Spartan-3Eデバイスの品種ごとに必要なコンフィギュレーションメモリ容量と最小限必要なSPIデバイスのサイズ、ならびに他の目的に使用できる残りのメモリ容量を示します。なお、FPGAごとに専用のコンフィギュレーションメモリを用意する必要はありません。

デイジーチェーンのコンフィギュレーション構成にすると、1個のSPIフラッシュPROMを複数のFPGAで共有することができます。

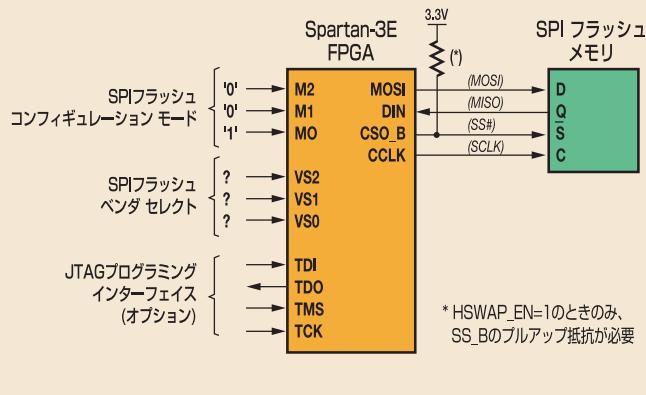

### SPIへのインターフェイス

図2は、Spartan-3EとSPIフラッシュメモリ間の標準的な接続を、コンフィギュレーションの手順を制御するために使用されるFPGAのI/Oピンとともに示します。FPGAがSPIフラッシュのコンフィギュレーションモードのとき、VS[2:0]の3つのデュアル目的ピンは、接続されているSPIフラッシュのタイプを定義し、以下のように動作します。

- SPIのコンフィギュレーションモード時(M[2:0] = "001")のみ、この3つのVSピンがアクティブになります。

- NIT\_BがHighになると、これらのVSピンがサンプリングされます。

図2 Spartan-3E FPGAとSPIフラッシュメモリ間のインターフェイス

Spartan-3E SPIフラッシュインターフェイス

図3 SPIフラッシュメモリを複数デバイスに接続

例：SPIインターフェイスを再利用

- FPGAのコンフィギュレーションが完了すると(DONEがHighになる)、VSピンがユーザーI/Oとして再使用可能になります。

この後、FPGAは選択したSPIフラッシュに対応するコマンドシーケンスを発行します。

#### コンフィギュレーション後

コンフィギュレーションが完了すると、SPIフラッシュPROMに接続されているすべてのピンがユーザーI/Oとして使用可能になります。コンフィギュレーションの後、SPIフラッシュPROMを使用しない場合は、FPGAのCSO\_BピンをHighにするとPROMがディスエーブルされ、FPGAのMOSI、DIN、CCLKピンが解放されユーザーI/Oとして使用できるようになります。

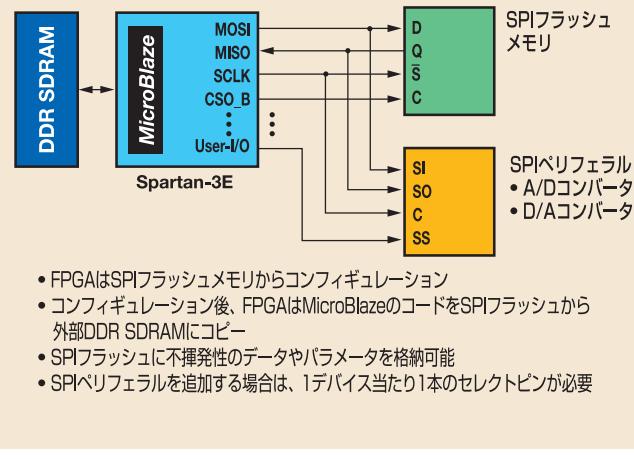

SPIフラッシュPROMに充分な容量があれば、MicroBlazeプロセッサコードや、シリアルナンバーやイーサネットMAC IDなどの不揮発性のアプリケーションデータを保存することができます。図3に、SPIフラッシュメモリを複数目的に使用する例を示します。

#### サードパーティ製ペリフェラル

フラッシュメモリの他に、多くのペリフェラルが同一のSPIを利用しています。このようなペリフェラルには以下があります。

- メモリ(EEPROM、EPROM)

- A/Dコンバータ(ADC)

- D/Aコンバータ(DAC)

- 熱管理

- ディスプレイ ドライバ

- マイクロプロセッサ、マイクロコントローラ(MCU)、デジタル信号処理(DSP)

- 多くの特定用途向け標準部品(ASSP)

コンフィギュレーション後、FPGAのユーザー アプリケーションは、SPIバスマスターとして残し、接続されているSPIフラッシュPROMやSPIペリフェラルと通信することができます。接続されているすべてのSPIペリフェラルは、共通のシリアル入力、シリアル出力、クロック信号を使用します。SPIペリフェラルは、それぞれ個々にセレクト入力があります。コンフィギュレーションに使用するSPIフラッシュPROMは、FPGAのCSO\_Bピンにより選択されます。追加された各SPIペリフェラルは、個々のユーザーI/Oピンにより選択されます。

#### パラレルNORフラッシュ

Spartan-3Eはまた、パラレル コンフィギュレーションインターフェイスを提供します。このインターフェイスは、業界標準のパラレルNORフラッシュからFPGAをコンフィギュレーションするために考案されたものです。Spartan-3Eの非同期メモリインターフェイスは柔軟性に優れ、EEPROM、OTP EPROM、マスクROM、NVRAM、非同期SRAMなど種々のメモリデバイスに接続できます。

パラレルNORフラッシュメモリの要件は非常にシンプルです。コンフィギュレーションの間、FPGAは最大24本のアドレスラインを提供し、バイト幅データを受信します。また、Spartan-3Eは、メモリのchip-select、output-enable、write-enable、x8/x16モード制御(Byte#)を有する高集積のフラッシュPROM用のbyte-enable(オプション)をドライブする4本の制御ラインをもっています。メモリは3.3V、2.5V、1.8Vのいずれかで、200ns以下のリードアクセスタイムを必要とします。

#### 結論

低コストを誇る新しいSpartan-3E FPGAファミリは、デバイスの低価格に加えて、低価格のSPIとパラレルフラッシュメモリからのコンフィギュレーションを新たにサポートすることで、システムの総コストをさらに削減します。現在Spartan-3Eでサポートしているフラッシュメモリは数種類ですが、数ヶ月後には、さらに多くのメモリベンダがSpartan-3Eのサポートを発表するでしょう。現在サポートされているSPIフラッシュメモリについては、ザイリンクスWebサイトのSpartan-3Eのページ[www.xilinx.co.jp/spartan3e/](http://www.xilinx.co.jp/spartan3e/)をご覧ください。

# リコンフィギュラブルFPGAによる 高解像度Ogg/Theoraビデオ エンコード

カスタムASICのアプリケーション領域であった

高性能ビデオエンコーディングを最新FPGAで実現

Andrey Filippov

President

Elphel, Inc.

[andrey@elphel.com](mailto:andrey@elphel.com)

Spartan™-II EベースのElphel Model 313カメラについて私が記事（“How to Use Free Software in FPGA Embedded Designs”）を寄稿したXcellジャーナル2003年春号（46号英語版）は、ザイリンクスのSpartan-3 FPGAに関する記事が多く掲載されたものでした。この後すぐに、Spartan-3をElphel社の新世代ネットワークカメラに採用しようと考えましたが、最終的に利用できると判断したのは昨年になってからでした。

Elphel社がこの新しいテクノロジを採用するのが遅れた要因の1つに、当初はこのデバイスを処理する適当なソフトウェアがなかったことがあります。当社の顧客にとっては、高額なソフトウェア開発ツールなしで当社の製品を変更できることが重要だからです。2004年夏、ザイリンクスのWebサイトにアクセスしたところ、無償ダウンロードが可能なWebPACK™ソフトウェアの最新バージョンが、XC3S1000（小型のFT256パッケージ封止の最高集積デバイス）をサポートしていることを知り、これは、Spartan-3へ切り換える絶好のタイミングであると考えました。

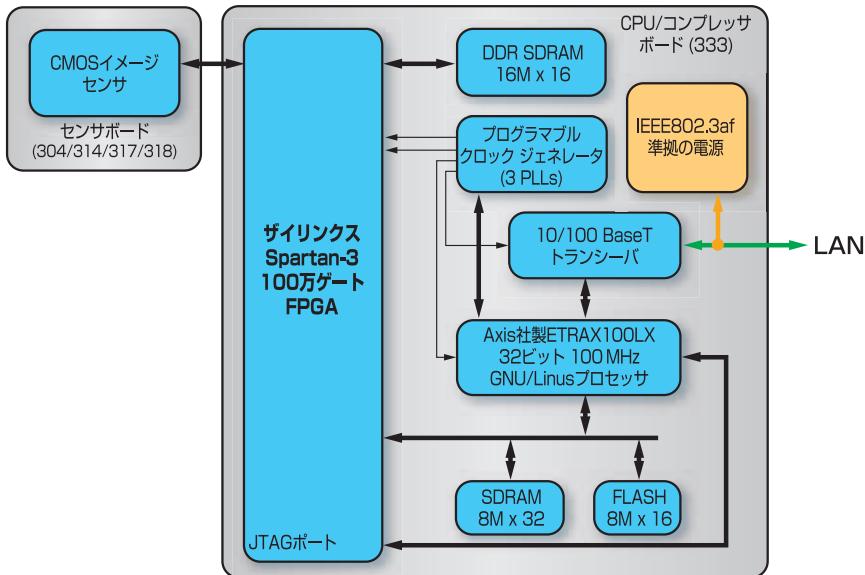

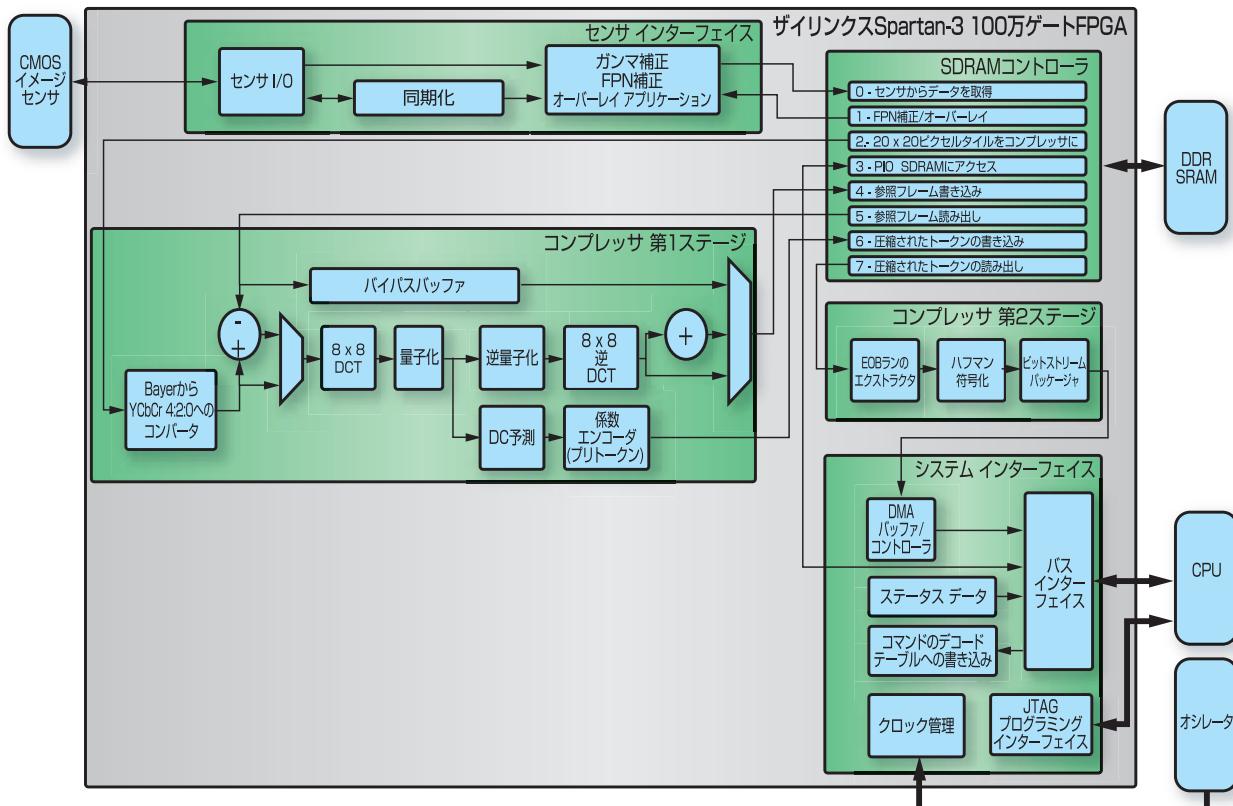

図1 カメラシステムのブロック図

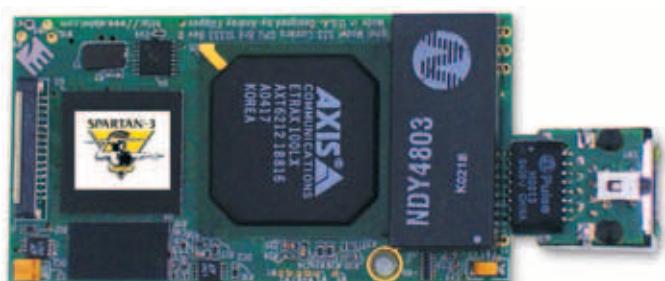

### カメラのハードウェア

当社の新製品Model 333カメラ（図1）は、旧型のModel 313と同じくLinuxに最適化したCPU（Axis Communications社のETRAX100LX）を採用していますが、システムメモリは、SDRAMは32MBに、フラッシュメモリは16MBに拡張されています。また、次に大きな改良点として、FPGAと連動して機能する専用フレームバッファに32MBのDDR SDRAMを採用し、大容量化とI/O帯域幅の向上を図って処理能力を高めています。

Spartan-3 DDRのI/O機能により、ボードサイズを拡大せずにメモリバンド幅を向上することが可能になった結果、旧型同様、全システムが1.5×3.5インチの4層ボード上に収まっています（図2参照）。新型のボードは、戸外での使用向けに密閉型のRJ45コネクタが収まるようにデザインされているため、実際のボード面積はさらに小さくなっています。

我々は、小型サイズで高いコンピュータ演算性能を実現し（これによりPC基板上での高速シグナルインテグリティを容易に保持）、リコンフィギュアブルFPGAの柔軟性をシステム全体に提供することを目標に、カメラの回路設計を行いました。リコンフィギュアブルFPGAの柔軟性を提供するために、カメラの回路を、1つはメインボード、もう1つはセンサと最小限の関連コンポーネントのみを含むボードの2つに分割することにしました。メインボード上では、FPGAのI/Oピンをボード内コネクタに直接つなぐため、ピン機能（極性を含む）を特定のセンサボードに適合するように変更できます。旧型のModel 313カメラでは、同様の方法によりさまざまなタイプのセンサがサポート可能になりました（ほとんどのセンサは、ボード設計後に使用可能となりました）。また、11メガピクセルModel 323カメラについても、この方法によりPC基板の変更なしに目標の達成を実現しました。

### ビデオエンコーディング方式の選択

プロトタイプカメラの準備が整った後わずか2週間で、Spartan-II Eベースのカメラ向けに開発したコードを修正し、モーションJPEG圧縮をインプリメントするという作業が完了しました。作業の半分は、生成されるビットストリームによって新しいFPGAをどのようにコンフィギュレーションするかを考えることに費やされました。カメラ内では、デバイスのJTAGピンが直接プロセッサのI/Oピンに接続さ

れるため、ザイリンクスのコンフィギュレーションハードウェアに付属のソフトウェアを使用することができず、また、JTAGの命令レジスタは、熟知しているSpartan-IIでは5ビット幅でしたが、今回は6ビット幅であるという相違点が存在しました。試行錯誤の後、同じコードが125MHz（旧モデルでは90MHz）で動作可能であること、また利用可能なスライスのうちわずか36%（以前は98%）のみを使用し、より多くの課題に対応する余地が十分にあることがわかりました。

もちろん、転送または保存するデータが大量なため、モーションJPEGは高解像度/高速フレームレートのカメラにとって必ずしも望ましい選択肢とはいえず、いくつかの困難に直面していました。視点固定型カメラでは、ほとんどの場合、連続するフレームの差がごくわずかなため、このようなビデオストリームを記録すると、ネットワーク帯域幅やハードディスクス

ペースが無駄になってしまいます。しかし、MPEG-2のような規格の場合、このような無駄は発生しない可能性があります。私がカメラに実装しようと考えていたのは、まさにこのMPEG-2規格でした。

しかし、MPEG-2に関する書物を何冊か入手し細かく調べ始めてすぐに、MPEGが連続するフレーム間の共通点を利用できるというだけではなく、MPEGとJPEG間にもう1つ基本的な違いがあることに気づきました。JPEGと異なり、MPEG-2はこの規格をベースとしたエンコーダを使用するためのライセンス料を支払う必要があります。その料金は、ハードウェアのコストと比較してわずかなものでしたが、やはりわずらわしく、自由なインプリメンテーションの妨げになります。

MPEG-2に代わる完璧な規格Theoraを見つけるまでに長い時間はかかりませんでした。これは、On2 Technologies社（[www.on2.com](http://www.on2.com)）の開発したVP3コーデックをベースとし、無償で使用・修正することができるオープンソースソフトウェアとしてリリースされています（[www.theora.org/svn.html](http://www.theora.org/svn.html)を参照）。

Theoraは、MPEG-4など低ビットレートのビデオ圧縮方式と競合する先進のビデオコーデックです。現在Theoraは、ビデオコンテンツの配信に共に使用されるトランスポートレイヤ、Oggと同様に、Xiph.org Foundation（ザイフォ財団）によりサポートされています。このビットストリームフォーマットは、安定性が高く種々のオペレーティングシステム上で動作するマルチプレーヤによってサポートされています。Theoraは、JPEGやMPEGと同様、二次元の8×8DCTを使用します。

図2 カメラシステムのボード

## FPGAのインプリメンテーション

Elphel Model 333カメラのFPGA用コードは、Verilog HDLで記述されています(図3)。このFPGA用コードはSpartan-3 DDRの機能を使用する8チャネルのSDRAMコントローラの周囲にデザインされています。メモリアクセスの構造とデータマッピングの特別な構成は、いずれも、メモリ帯域幅が最適化されるように考慮されています。この最適化がうまく行われないと、システムのボトルネックとなります。

現在、一般的FPGAのリソース(スライス)の3分の2と、24ブロック中20ブロックのRAMモジュールを使用しているコードの残りには、ビデオ圧縮モジュールや、センサ、システムインターフェイスが含まれます。

カメラコードの詳細ならびにソースコードについては、Sourceforge (<https://sourceforge.net/projects/elphel>) を参照してください。

## 結論

高性能なリコンフィギュラブルFPGAにより、1280×1024ピクセルの解像度で30fps(2048×1536の解像度で12fps)を達成可能

な、高速高解像度の低ビットレートネットワークカメラを構築することが可能となりました。Spartan-3が提供するDSP機能向けのエンベデッド乗算器や、先進のデジタルクロックマネージャ、DDRのI/O機能、DDR SDRAMコントローラ用に数多く追加されたグローバルクロックネットワーク、カメラ内の各種テーブルおよびバッファ用の大型ブロックRAMモジュールなどの新機能は、カメラ設計にきわめて有用であることがわかりました。

無償のビデオエンコーダ(Theora)と、オープンなインプリメンテーション(GNU General Public Licenseより全ソフトウェアとVerilogコードが提供される)により、Elphel社製品にとって2番目に重要な機能が実現可能となります。ユーザーは、開発したカメラを最終製品としてだけでなく、汎用的な開発プラットフォームとしても利用することができます。これは、Spartan-3ファミリの優れた性能と柔軟性の高さを実証するものです。ユーザー自身のコードを追加し、ツールの再実行(FPGAコードとC言語のカメラ用ソフトウェアの両方について)が可能となることで、先進の画像処理をインプリメントした新型カメラを即座に試してみることができます。

詳細については、[www.elphel.com](http://www.elphel.com)、<https://sourceforge.net/projects/elphel/>、[www.theora.org](http://www.theora.org)をご覧ください。

図3 FPGAコードのブロック図

# Spartan-3 FPGAを利用したデジタル信号処理アルゴリズムの実装

特徴抽出とデジタル画像ワーピングに使用される画像処理アルゴリズムとしてFPGAを実装した2つの研究事例を紹介

## Paolo Giaccon

Graduate Student

Universit di Verona, Italy

paolo.giaccon@students.univr.it

## Saul Saggin

Undergraduate Student

Universit di Verona, Italy

saul.saggin@students.univr.it

## Giovanni Tommasi

Undergraduate Student

Universit di Verona, Italy

giovanni.tommasi@students.univr.it

## Matteo Busti

Graduate Student

Universit di Verona, Italy

matteo.busti@students.univr.it

コンピュータ ビジョンは、人の視覚に特有の機能をコンピュータに持たせることに焦点をあてた人工知能の1分野です。この分野には、動作構造化、画像位置合わせ、カメラ動作検索などのさまざまなアプリケーションがありますが、これらのプリプロセッシングタスクとして最も重要なものの1つが、特徴のトラッキングです。中でも特徴抽出のフェーズは、計算機能が集約されるため、非常に重要です。

デジタル画像ワーピングは、幾何学的空間変換技術を扱う画像処理の1分野です。画像ワーピングは、リアルタイム システムにおける視覚情報の合成、画像モザイク処理、映像安定化など、コンピュータ ビジョンの一般的なアプリケーションだけでなく、多くの画像分析アプリケーションにおいても重要な役割を担っています。

ここでは、これらのアルゴリズムをFPGAに実装した例について紹介します。

## 特徴抽出の理論

コンピュータ ビジョンのさまざまなタスクにおいて、我々は、重要な特徴点、すなわち「端点」を見つけることに、関心をもっています。カメラで写る一連の画像内の特徴間の変位を測定すると、その周囲の構造と撮影側の動きの両方の情報を復元することができるため、これら特徴点を見つけることは非常に重要です。

図1は、カメラ撮影した画像から抽出された一連の特徴点です。端点は、通常2方向(xとy)での勾配の大きな変化を示します。この点は、一連の画像を通して一意的に一致し、追跡することができます。これに対して、点がエッジ上にある場合、2枚目の画像では、そのエッジ上に存在する多くの他の点に一致する可能性があります。

## 特徴抽出のアルゴリズム

適切な特徴を選ぶために採用したアルゴリズムは、Tomasi-Kanadeの因子分解法にヒントを得たもので、Benedetti-Peronaの近似式を用いて、この画像の勾配共分散行列の固有値  $\alpha$  と  $\beta$  について考えるものです。勾配共分散行列は、次式で表されます。

$$H = \begin{bmatrix} I_x^2 & I_x I_y \\ I_x I_y & I_y^2 \end{bmatrix}$$

ここで  $I_x$  と  $I_y$  は、x方向とy方向の画像の勾配（グラディエント）を示します。

したがって、固有値  $H$  に着目すると、各ピクセルの周辺構造を次のように分類できます。

構造がない場合 :  $\alpha \approx \beta \approx 0$

エッジの場合 :  $\alpha \approx 0, \beta \gg 0$

コーナーの場合 :  $\alpha \gg 0, \beta \gg 0$

図1 カメラ撮影した画像から抽出された特徴点

Benedetti-Peronaの近似式を用いると、固有値をコンピュータで計算することなく、端点を選び出すことができます。

我々は、元の方法を参考にして、浮動小数点演算をまったく必要としないアルゴリズムを考え出しました。このアルゴリズムは、ハードウェアでもソフトウェアでも実現できますが、FPGAテクノロジに実装することで、リアルタイム性を達成できます。

入力：

- 既定サイズの8ビット グレーレベル画像

(最大512 × 512 ピクセルまで)

- 特徴点の予測数(wf)

出力：

- 選択された特徴のリスト(FL) - 出力形式は以下3 × Nの行列

- 最初の行にこのリストに含まれる各特徴の信頼度を示す

- 2行目は、特徴点のX座標を示す

- 3行目は、特徴点のY座標を示す

### 本アルゴリズムの解釈

ピクセル(i, j)が、特徴点(端点)であるかどうかを判断するために、我々はTomasi-Kanadeの因子分解法をたどりました。

まず、この画像のグラディエント(変化度)を算出します。これにより、 $2 \times 2$ の対称行列  $G = [a \ b; \ b \ c]$  が算出されます。この場合の入力データは、ピクセル(i, j)の周辺領域の勾配より得られます。

固有値Gの最小値が閾値よりも大きければ、ピクセル(i, j)は端点です。最小固有値は、コストのかかるハードウェアでの平方根演算を避け、近似法を使用して算出します。

端点検出アルゴリズムを要約すると、次のようにになります。

画像の勾配は、事前に定義されたマスクと入力画像との畳み込みという方法で算出されます。このマスクのサイズと値は、画像の解像度により異なります。マスクの標準的サイズは $7 \times 7$ です。

- 各ピクセル(i, j)に対し、次のループ処理を行う

$$a_{i,j} = \sum_k^N (I_x^k)^2$$

$$b_{i,j} = \sum_k^N I_x^k I_y^k$$

$$c_{i,j} = \sum_k^N (I_y^k)^2$$

Nはこの領域内のピクセル数で、 $I_x^k$  と  $I_y^k$  はこの領域の内側にあるピクセルkの勾配成分を示す

- $P_{i,j} = (a - t)(c - t) - b^2$

tは整数の固定パラメータ

- $(P_{i,j} > 0)$ かつ  $(a_{i,j} > t)$ の場合、ピクセル(i, j)を保持する

- $P_{i,j}$  が局所的に極大でないピクセルはすべて破棄する

ループ処理終了

信頼値の度合に基づいて特徴リストFLを降順に並び替え、その最初のwf項目だけを採用する

### インプリメンテーション

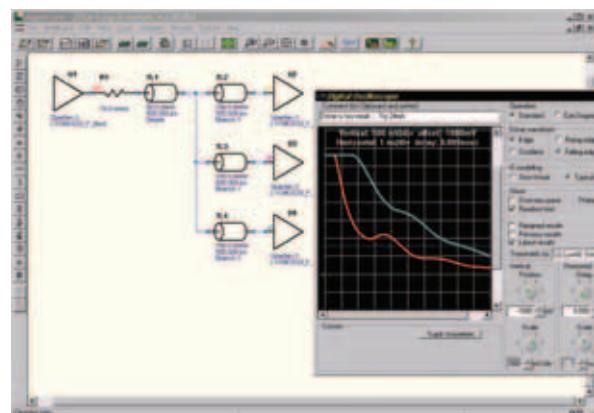

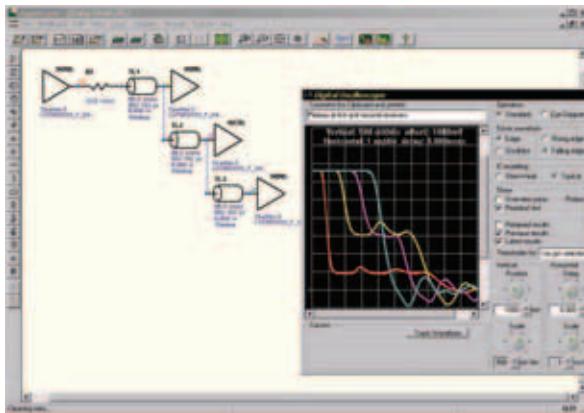

高速エンベデッド乗算器を搭載したザイリンクスのSpartan™-3のアーキテクチャは、このアルゴリズムを利用する多くのコンピュータビジョンシステムで要求される優れたコスト対性能を満たすことができます。

インプリメンテーションは、4つの基本タスクに分けて次のように行われます。

- データの獲得 - x軸とy軸に沿って2つの勾配をとり、特性多項式で使用される3つの係数を各ピクセルごとに算出します。この勾配の保存や読み出しには、バッファを利用してインプリメントします(Spartan-3 ブロックRAMを使用してインプリメント)。

- 特性多項式の値の算出 - この値は、特定のピクセルに関する特徴を分類するために重要です。特性多項式微積分法で使われる乗算を、Spartan-3に搭載のエンベデッド乗算器を用いてインプリメントしました。

- 特徴のソーティング - 算出した特徴値をブロックRAMに保存し、逐次比較方式でそれらを順を追ってソーティングします。

- 最小距離を確保 - 特徴の間に最小距離を保つために行います。最小距離を確保しないと、最も重要な特徴の周囲に多くの特徴が集中してしまいます。最小距離の確保は、ブロックRAMを使用して実現され、最も重要な特徴の周辺に非検出領域を設け、その領域では他の特徴が選択されないようにします。

### Spartan-3の理論上の性能

このアルゴリズムは、1秒間に100フレームで最大512 × 512までの種々の解像度でのグレーレベル画像を対象に開発されています。

ザイリンクスのSystem Generatorにより見積られる必要なリソースは次のとおりです。

- 1,576 スライス

- 15個のブロックRAM

- 224個の LUT

- 11個の エンベデッド乗算器

Spartan-3に搭載されているエンベデッド乗算器と豊富なメモリリソースにより、ロジックを効率よくインプリメントすることができます。

### 特徴抽出のアプリケーション

特徴抽出は、自動ナビゲーションや視覚に基づいた判断や制御を行うシステムなど、制御に関連する実質的な問題を解決するあらゆるシステムのフロントエンドで採用されています。典型的なアプリケーションには、動作ビデオの監視、ロボットアーム動作、点や距離の測定、自動誘導車などがあります。

## 画像ワーピング理論

デジタル画像のワーピングでは、幾何学的空间変換の技術を扱います。1枚の画像に含まれるピクセルは2つの直交座標 (x, y) により空間的に表されます。幾何学的空间変換をこの画像に当てはめるために同次座標への切り替えを行うと、ただ1つの行列演算によりこの変換を表すことができます。これは通常、第3座標値として、1を加えることで処理されます (x, y, 1)。

一般的には、このような変換は特異点のない  $3 \times 3$  の行列  $H$  により表され、行列ベクトルの乗算によりそのピクセルの同次座標に次の式で当てはめられます。

$$\begin{bmatrix} H_{1,1} & H_{1,2} & H_{1,3} \\ H_{2,1} & H_{2,2} & H_{2,3} \\ H_{3,1} & H_{3,2} & H_{3,3} \end{bmatrix} \bullet \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \begin{bmatrix} H_{1,1}x + H_{1,2}y + H_{1,3} \\ H_{2,1}x + H_{2,2}y + H_{2,3} \\ H_{3,1}x + H_{3,2}y + H_{3,3} \end{bmatrix} = \begin{bmatrix} x' \\ y' \\ w' \end{bmatrix} = \begin{bmatrix} x' \\ y' \\ w' \end{bmatrix} \Rightarrow (x'/w', y'/w') \quad (1)$$

行列  $H$  は、ホモグラフィまたは共線変換と呼ばれ、スケールファクタ (8自由度を持つ) により定義されます。この変換は、射影座標 (または同次座標) では線形ですが、直交座標では非線形です。

この公式は、ピクセルの変換結果の直交座標を得る際に、FPGA の性能と領域を消費する非常にやっかいな除算演算を行う必要があることを示唆します。このため、我々は、ホモグラフィを特殊化した「アフィン変換」と呼ばれる空間変換の1種を採用することを検討しました。この変換方式により、除算をしなくても、次のような良好な測定結果を得ることができます。

$$\begin{bmatrix} A_{1,1} & A_{1,2} & A_{1,3} \\ A_{2,1} & A_{2,2} & A_{2,3} \\ 0 & 0 & 1 \end{bmatrix} \bullet \begin{bmatrix} x \\ y \\ 1 \end{bmatrix} = \begin{bmatrix} A_{1,1}x + A_{1,2}y + A_{1,3} \\ A_{2,1}x + A_{2,2}y + A_{2,3} \\ 1 \end{bmatrix} = \begin{bmatrix} x' \\ y' \\ 1 \end{bmatrix} \Rightarrow (x', y') \quad (2)$$

アフィン変換には、回転、変換、拡大縮小、そしてこれらすべての可能な組み合わせを含む、平面変換のさまざまな種類があります。このアフィン変換を、並列処理が可能な個々の単純な平面変換に置き換えられます。1つのアフィン変換を定義するには、6つのパラメータが必要です。

## 画像ワーピング アルゴリズム

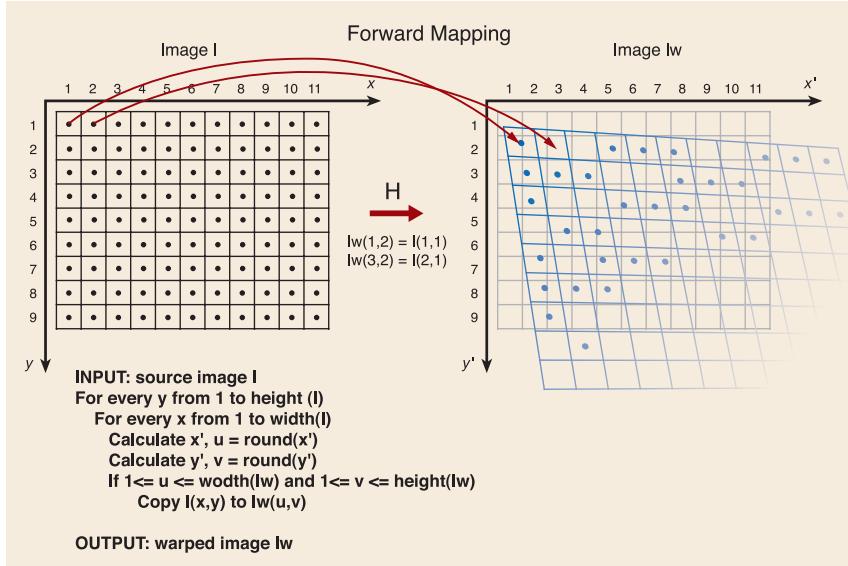

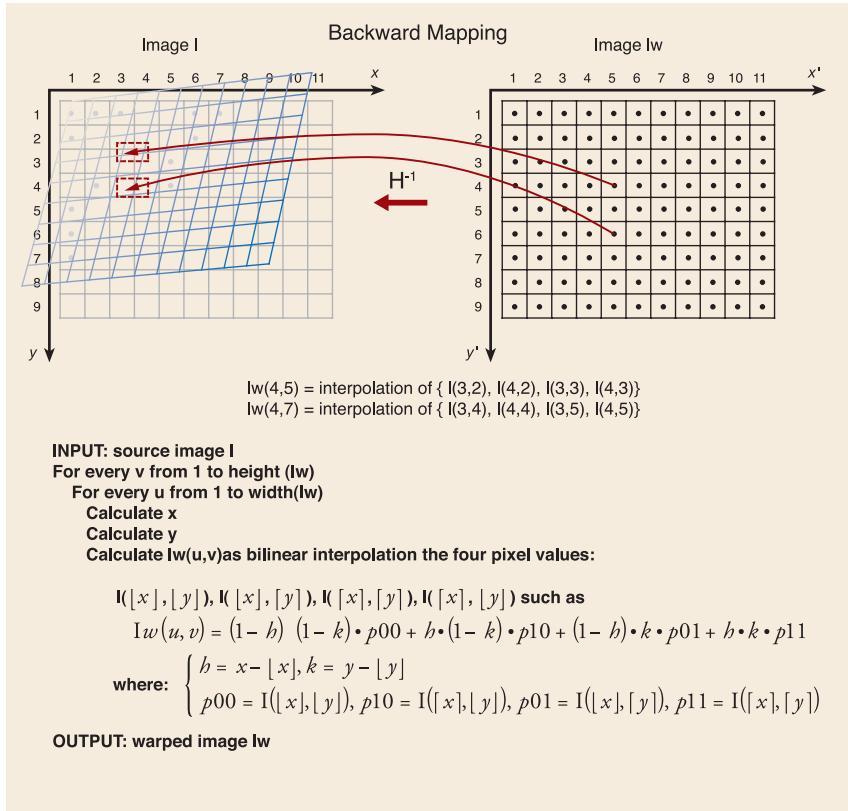

画像のワープ処理には、2つの一般的な方法があります。

- 前方マッピング

- 後方マッピング

前方マッピングを用いると、元の画像が直線ごとにスキャンされ、結果の画像にピクセルがコピーされますが、コピーされる位置は方程式 (2) で示される線形システムの結果で決まります。このテクニックにはいくつかの問題点がありますが、その最たるものは、画像に大幅な変換 (回転や、1より大きな係数での拡大など) を加えると最終画像に穴ができることがあります (図2)。

後方マッピングの手法では、より良い結果が得られます。逆変換  $A^{-1}$  を使用して、最終画像をピクセルごとにスキャンし座標を変換します。この結果、元の画像には2つの非整数座標ができます。元の画像に存在する4つのピクセル値の双1次補間を行って、最終画像のピクセル値を割り出すことが可能です (図3参照)。

このテクニックを用いることにより、最終画像にホールができるという問題を回避できるため、これをハードウェア実装手段として採用しました。

## インプリメンテーション

ソフトウェアにこのアルゴリズムを実装することは良く知られています。パーソナル コンピュータやワークステーションが必要とされるアプリケーションに広く使われています。しかし、ハードウェアに実装するには、FPGA に与える効率的な制約を指定するためのさらなる作業が必要になります。

基本的にこの処理は、変換と補間の2つの部分に分けられます。我々は、4つの乗算器と4つの加算器を使い、最初の変換部分を行列ベクトル乗算 (2) として実装しました。2つ目は、補間の実際の結果の概算です。変換結果の4つのピクセル値を、2進小数点以下2ビットで近似して重み付けしました。我々は、補間によって得られるであろう結果を1組の離散値に分けたため、公式の計算を行う代わりに、LUT を使用して、ピクセルの最終値を算出しました。

## Spartan-3の理論上の性能

我々は、Spartan-3デバイスをターゲットに、System Generator for DSP を使用してアルゴリズムをデザインしました。HDLコードを生成し、それを ISE™ デザイン ソフトウェアで合成して、次のようなリソース使用率を得ました。

- 744スライス (1,107個のLUT)

- 164個の SRL16

- 4個のエンベデッド乗算器

このデザインにより、 $512 \times 512$  の画像を最大46 fps (フレーム/秒) まで処理することができます。理論的に、Spartan-3を使用したシステムの限界は360+ fps です。

## 画像ワーピングのアプリケーション

画像ワーピングは、視覚情報の合成、映像安定化、画像モザイク処理といったさまざまなコンピュータ ビジョン アプリケーションで一般的に使われています。

画像モザイク処理は、共通のリファレンス フレームに対してそのすべての画像を個別に並べ替えた後の連続した (一群の) 画像合成を扱います。これらの幾何学的変換は、座標システム間の単純な関係で表せます。

ワーピング処理を通して適切な変換を行い、ワープした画像の重なり合う領域を統合することで、そのシーンの可視領域全体をカバーする1つのパノラマ画像を構成することができます。画像モザイク処理は、実際のイメージに基づいたバーチャルリアリティアのきめ細かな立体モデルや景色を作る強力な手段を提供します。画像モザイク処理は、ライト シミュレータ、双方向マルチプレイヤ ゲーム、医療画像システムなどに採用され、実際のパノラマ風景や限定されたバーチャル環境を築きます。

図2 1より大きな係数で拡大する前方マッピング

## 結論

効率性や有効性、信頼性の面で優れたビジョンモジュールを、可能な限り高い信頼性でデザインするのは至難の業です。

ザイリンクスのXPERTSパートナーであるUltimodule社とVerona大学VIPS研究室は、Ultimodule社のシステム オン モジュール ファミリを使用して、コンピュータ ビジョンのための基礎プラットフォームを定義しました。このプラットフォームは、3次元データのリアルタイム抽出用ステレオビジョン システムや、視覚に依存した判断や制御を行うアプリケーションで必要なアルゴリズムを実装するリアルタイム画像処理エンジンを提供します。

このプラットフォームは、質と（リアルタイム）算出論理の両面において、高性能で強力なビジョン解析が必要なアプリケーションをサポートします。これらのアプリケーションには、動作ビデオの監視、ロボット アーム動作と制御、自動誘導車、検査と測定、ハザード検出などがあります。このプラットフォームは、システム制御ロジックやメモリ、プロセッsing ハードウェアなど、必要なモジュールをすべて備えたアプリケーション ソフトウェアとともに提供されます。相互接続モジュールにより、複雑なアーキテクチャを短期間で開発することが可能になります。

このプラットフォームは、ザイリンクスのSpartan-3を利用していますが、このSpartan-3は、その柔軟性、優れた性能、信号処理を対象としたアーキテクチャにより、画像処理IPコアのターゲットとして最適です。また、このSpartan-3ファミリは、ASICにとって代わるプログラム可能な有効なデバイスです。こうした特徴がその低コスト構造と相まって、Time-to-Marketが鍵を握る場合に、大きな価値を付与します。

特徴抽出の詳細については、

[paolo.giacon@students.univr.it](mailto:paolo.giacon@students.univr.it)

または [saul.saggin@students.univr.it](mailto:saul.saggin@students.univr.it)まで

Eメールにてお問い合わせください。

画像ワーピングの詳細については、

[matteo.busti@students.univr.it](mailto:matteo.busti@students.univr.it) または

[giovanni.tommasi@students.univr.it](mailto:giovanni.tommasi@students.univr.it)まで

お問い合わせください。 ●

ご助言をいただいたいた、Verona大学情報学部、VIPS（ビジョン、画像処理、音響）研究室のMurino教授、ならびに貢献いただいたMarco Monguzzi氏、Roberto Marzotto氏、Alessandro Negrente氏に感謝いたします。

図3 1より大きな係数で拡大する後方マッピング

# Spartan-3 FPGAの DDRメモリインターフェイス設計

ザイリンクスは、カスタマイズされたDDRメモリ インターフェイスを

インプリメントする多くのツールを提供

## Rufino Olay

Marketing Manager, Spartan Solutions

Xilinx, Inc.

rufino.olay@xilinx.com

## Karthikeyan Palanisamy

Staff Engineer, Memory Applications Group

Xilinx, Inc.

karthi.palanisamy@xilinx.com

メモリ速度はシステム性能の鍵を握るもので。現在、最も一般的に使用されているメモリの形式は、同期型ダイナミック ランダム アクセス メモリ(SDRAM)です。

1990年代後半、システムのさらなる高性能化と記憶データの大容量化が求められることにより、SDRAMのメモリ速度とテクノロジは飛躍的に進歩しました。2002年までには、このような要求がますます増大するとともに、DDR266(初期)、DDR333、そして最新のDDR400という動作速度を備えたダブル データ レート(DDR) SDRAMが標準となりました。

DDR SDRAMは、シングル データ レートであるSDRAMを発展的に拡張したもので、高速化、低消費電力化、コンポーネントの高集積化というメリットを提供します。データは、クロックの立上がり/立下がりエッジの両方でデバイスにクロック入出力されます。ただし、コントロール信号はこれまで同様、立上がりクロックのエッジでのみ変更します。

DDRメモリは、さまざまなシステムやプラットフォームで幅広く

使用されているコンピュータ メモリです。カスタムDDRメモリ コントローラをユーザー ボードにインプリメントするために、ザイリンクスのSpartan™-3デバイスを使用することができます。

## Spartan-3とDDR SDRAMとのインターフェイス

Spartan-3は、最新世代のDDRメモリへのインターフェイスに必要なシステムレベルのビルディング ブロックを提供し、低コスト システムに最適なコネクティビティ ソリューションです。

Spartan-3のすべての入出力ブロック (IOB: Input/Output Block) には、三対のストレージ エレメントが含まれています。出力バス上あるいは3ステート パス上のいずれかにある一対のストレージ エレメントは、特別なマルチブレクサと共にDDR伝送を実行するために使用されます。この伝送を行うには、クロック信号の立上がりエッジに同期されたデータを取り込み、そのデータを立上がり/立下がりの両方のエッジで同期をとったビットに変換します。マルチブレクサと2つのレジスタとの組み合わせは、ダブル データ レートDタイプ フリップフロップ(FDDR)と呼びます。

## メモリ コントローラの設計が迅速かつ容易に実現

ザイリンクスは、Spartanデバイス用のメモリ コントローラの構築やテストのプロセスを迅速化できるよう、多くのツールを提供しています。これらのツールには、リファレンス デザインとアプリケーションノート、メモリ インターフェイス ジェネレータ(MIG)、そして最近新たに加わったハードウェア テスト プラットフォームがあります。

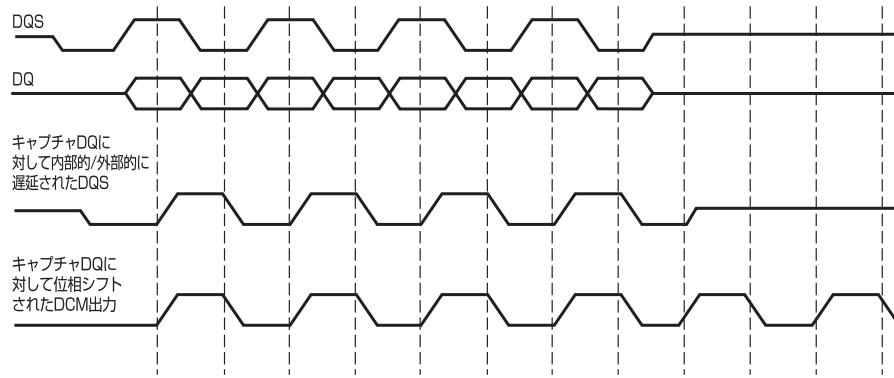

図1 読み出し動作のタイミング図

ザイリンクスのアプリケーションノート XAPP454、「DDR2 SDRAM Memory Interface for Spartan-3 FPGA」では、Spartan-3 FPGAをメモリ コントローラとして使用する方法を、特にMicron社のMT46V32M16TG-6T DDR SDRAMとのインターフェイスに焦点を当てて説明しています。また、この他アプリケーションノートでは、動作理論、主な課題、Spartan-3 FPGAベースのメモリ コントローラのインプリメンテーションについて解説しています。

DDRメモリは、非自由走行ストローブとエッジアライン読み出しデータを使用します（図1）。データ速度が333 Mbpsの場合、マージンを向上させるようにメモリストローブを使用する必要があります。ローカル クロックギング リソースを使用することにより、遅延ストローブをデータ ウィンドウの中心に合わせることでデータを取り込むことができます。

FPGA内のリソースを最大限に活用できるよう、グローバルクロック バッファ (BUFG) とデジタルクロックマネージャ (DCM) の使用を最小限に抑える一方で、データの取り込みにLUTをRAMとして使用するなどのデザイン手法を検討することができます（詳細は、ザイリンクスのアプリケーションノートを参照）。FPGAの左右あるいは上下のいずれかへのインプリメンテーションに関しても、最大限のデータ幅が結果として得られます。このようなインプリメンテーションは、新しいメモリインターフェイス ジェネレータによって軽減されます。

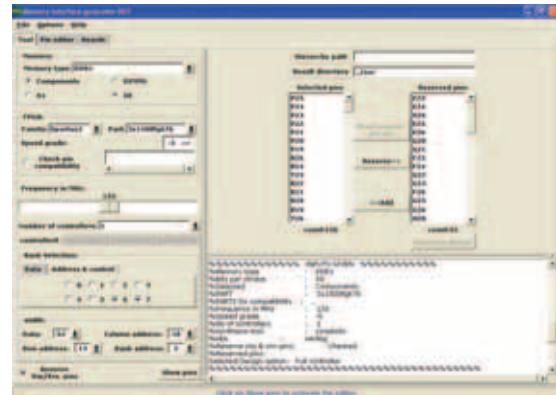

図2 MIG 007を使用したDDRメモリコントローラの自動構築

表1 XC3S1500 FPGAにおけるDDR 64ビットインターフェイスのデバイス使用度

| 機能                      | 使用数                 | 使用率(%) |

|-------------------------|---------------------|--------|

| Number of Slices        | 2,277 out of 13,312 | 17%    |

| Number of DCMs          | 1 out of 4          | 25%    |

| Number of External IOBs | 147 out of 487      | 30%    |

ザイリンクスは、ユーザー独自のコントローラ設計を推奨で行う部分をなくすため、メモリインターフェイス ジェネレータ (MIG 007) を開発しました。このツールを使用すると、インターフェイスを構築するために、FPGAデバイス、周波数、データ幅、使用するバンクなどのデータの入力を行います。対話型GUI（図2）により、RTLや、EDIF、SDC、UCF、その他関連するドキュメントファイルが生成されます。

一例として、MIGを使用してSpartan XC3S1500-5FG676向けのDDR 64ビットインターフェイスを構築しました。表1は、インプリメンテーションによって使用されたスライスは全体の17%で、デバイスの80%を超える部分がデータ処理機能に使用できる空き領域であることを示しています。

### ユーザー デザインの試行

設計の最終ステップは、実際のハードウェアを使った検証とデバッグです。MIG 007を使用してカスタマイズされたメモリコントローラを構築した後は、図3に示すように、Spartan-3のメモリ開発キット HW-S3-SL361上にユーザー デザインをインプリメントすることができます。この開発キットは995米ドルで、これは、150万ゲートのSpartan-3 (XC3S1500) をベースとして、以下の機能が新たに追加されています。

- Micron社製64 MBのDDR SDRAM、MT5VDDT1672HG-335、および将来の拡張用に128MBのDDR SDRAM DIMM

- 2ラインLCD

- 166 MHzオシレータ

- ロータリスイッチ

- ユニバーサル電源85V-240V、50-60 MHz

図3 Spartan-3メモリ開発ボード(HW-S3-SL361)

### 結論

システムデザインにDDRメモリが幅広く採用されるようになると、Spartan-3をメモリコントローラとして使用するのはごく当然のこととなりますし、コントローラのインプリメンテーションは決して難しいことではありません。

アプリケーションノート、GUI、開発ボードの詳細については、[www.xilinx.co.jp/products/design\\_resources/mem\\_corner/index.htm](http://www.xilinx.co.jp/products/design_resources/mem_corner/index.htm)をご覧ください。

# 新機能を搭載した CoolRunner-II CPLD

マクロセル数32および64の

CoolRunner-II CPLDがアップグレードして登場

Steve Prokosch,

High-Volume Product Solutions

Marketing Manager,

Xilinx, Inc.

steve.prokosch@xilinx.com

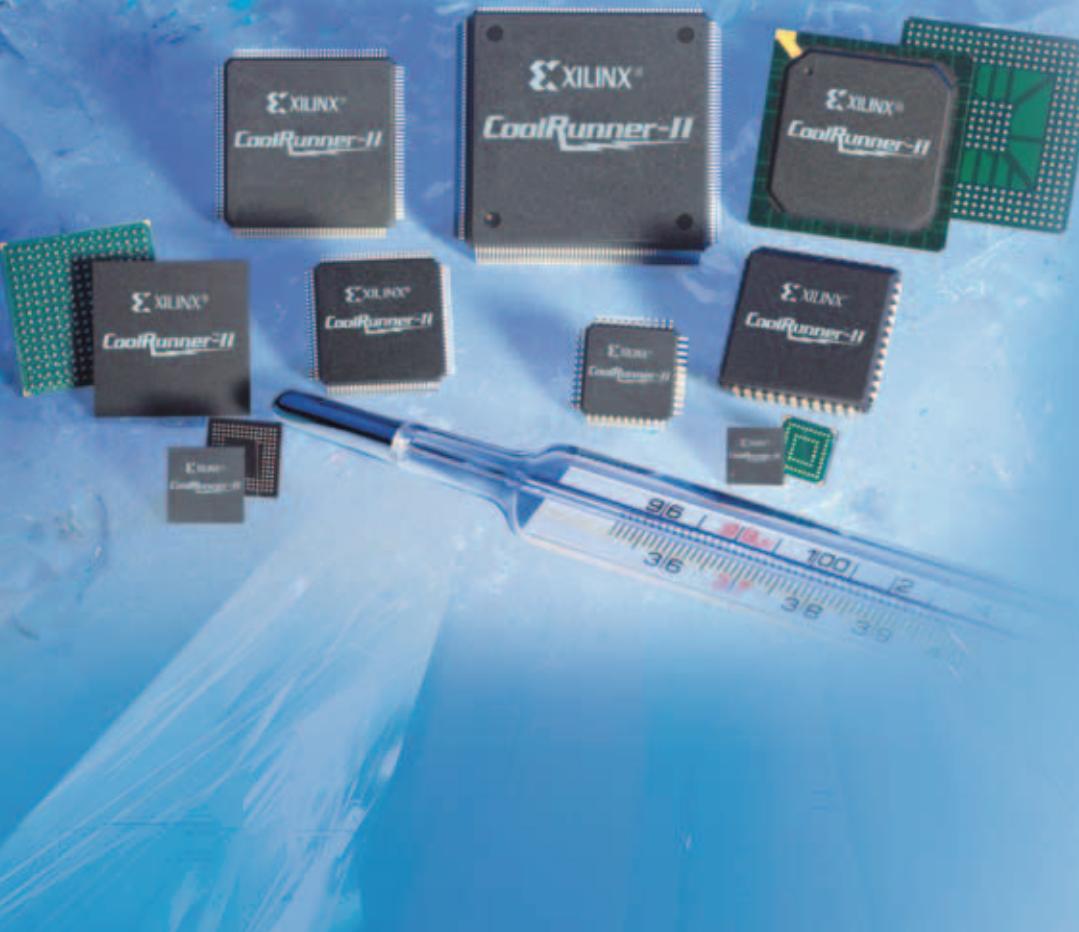

ザイリンクスは、1992年にCPLD市場に参入以来、業界の新規参入者からCPLD市場第2位のサプライヤとしての地位を確立するとともに、現在では、出荷数、売上額ともに市場1位のサプライヤとの差を狭めつつあります。このような成長を達成できた要因には、顧客の要望を的確に把握し、ニーズを満足する先進のアイデアを創出してきたことにあります。

ザイリンクスは、常に改善を重ねることに取り組んできた結果、従来高集積デバイスでのみ使用可能であった機能を、マクロセル数が32および64個のCPLDデバイスにも採用しました。これにより、設計課題に容易に対処できるとともに、総システムのコスト削減が可能になります。機能追加に加え、新しい小型のフットプリント パッケージも提供し、I/O当たりの単価の低減を実現しています。この新パッケージは、ザイリンクスが低コストのバッテリ駆動デバイス市場への引き続きの浸透を図る上で非常に有効なものです。

ザイリンクスのCPLDは、従来 CPLDが採用されてきたコンピューティング、データ処理、ネットワーキング、テレコムなどの分野はもとより、CPLDにとって新市場である民生機器(セットトップ ボックス、プラズマや液晶など大画面テレビ)、重要な携帯機器(PDA、ハンドセット、バッテリ駆動機器)などの分野においても、市場シェアを拡大しています。このように、新市場で成功を収め、また従来市場でもシェアの拡大を続けることにより、CPLDはシステムロジック ソリューションとしてさらなる成長が見込まれています。

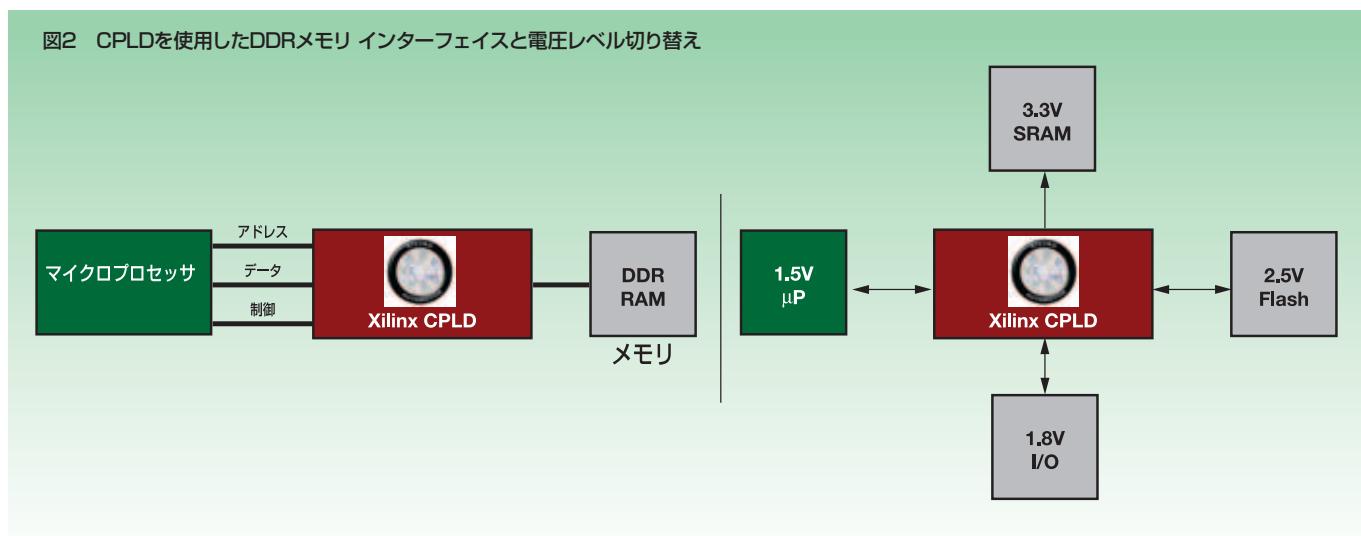

## CoolRunner-II CPLD用の新しいバンキング

ザイリンクスは、マクロセル数が32および64のCoolRunner-II™に、I/Oバンキングという新機能を搭載しました。このI/Oバンキングは、同一のPC基板上で複数の異なる電源電圧レベルを使用するシステムにおいて効果的な機能です。通常、システム プロセッサとその通信対象のデバイス間では、電圧レベルが必ずしも一致しません。このような通信には、シリアルからパラレル変換のようにシンプルなものから、プロセッサがディスプレイとインターフェイスする際のように必須のものがあります。

もう1つの例は、プロセッサをコンパクト フラッシュ (CF) やSD (secure digital) などの外部メモリカードに接続する場合です。プロセッサなどの多機能デバイスには、他社との競合や価格に対する絶え間ないプレッシャから、常に先進のプロセス技術を採用する必要があります。このようなプロセス技術では、ウェハジオメトリの物理的特性上、電圧振幅がますます小さくなっています。

また、メモリカードや無線通信、バス アーキテクチャといった市場向け標準化団体による仕様策定は、こういった技術の進歩に比べてゆっくりと進行します。今日のアーキテクチャでは、このギャップを埋めるために、電圧レベルとI/Oの変換が必要になります。入力と出力電圧のスイッチング スレッショルドを電圧規格に適合させる際、注意が必要となります。

設計者は、種々のデバイスタイプごとに制定されたロジックレベルの規格を同じ環境で使うという課題に直面します。これら目的を達成し、設計変更やアップグレードに対応できる、最適なデバイスを使用する必要があります。ディスクリート デバイスは、通常このような問題に対応できますが、コスト増になり、また消費電力やPC基板層、デザインのエリアを拡張させる

可能性がでできます。また、ディスクリート デバイスは機能が限定されるため、問題を完全に解消するには追加デバイスが必要になる場合があります。部品点数が増えれば、製造中止の可能性のある部品を選択する確率も高くなり、より多くの発注書の作成や、在庫管理が必要になります。さらに、部品点数が増えれば、ボードのアセンブリコストも増大します。しかし、ANDゲートのみが必要な場合は、ディスクリートのロジックデバイスの使用は正しい選択であるといえるでしょう。

しかし、単純なゲート以外に多くのデバイスを必要とする場合はどうでしょう。CPLDの価格は継続して下がり続け、今やディスクリートデバイス並みになってきています。複数のディスクリートを採用している場合には、CPLDの利点はさらに強調されます。

このようにCPLDは、低価格でしかも新たなレベルの高集積化への道を開拓してきました。CPLDは、機能を追加や低コスト化を図ってきた結果、史上初のディスクリート ソリューションと競合し得るデバイスとなりました。たとえば、標準的な

電圧変換デバイスの価格は、個数、パッケージ タイプ、使用するI/O数、そのデバイスのプロセス技術に依存しますが、通常、\$0.5から\$3.5です。CPLDデバイスは、最も低集積で低コスト パッケージを使用した場合、\$1以下で購入が可能、かつ、1個のCPLDで他のディスクリート ファンクション ロジックデバイスより、はるかに多くのメリットを手に入れることができます。

マクロセル32および64のCoolRunner-II CPLDにI/Oバンクを追加することで、他のデバイスと比較し非常に低コストのCPLDデバイスにて、電圧変換や各標準間のI/O変換が可能になりました。また、CoolRunner-II CPLDを使用することにより、以下に示すような利点も提供されます。

- セキュリティ

- 入力ヒステリシス

- オプションの出力制御

- 低消費電力動作

- 異なるI/O数で複数のパッケージを選択可能

- IEEE1149.1バンダリ スキャン テスト

- 1.5Vから3.3V範囲で調整可能

これら機能により、CPLDでは、電圧変換の他にさらに多くのことが可能となります。ディスクリートのレベル シフタは特定のタスクを実行するだけなので、特定のI/Oしか選択できずに問題となる場合があります。ザイリンクスのCPLDは、I/O選択が可能で、かつそのCPLDを他の目的にも使うことができます。このようにCPLDは、電圧変換が柔軟で、追加のロジックやI/Oを必要とし、他のシステム機能を集積化したい場合に、より適したデバイスといえます。CoolRunner-II CPLDの機能とパッケージ タイプは表1のとおりです。

表1 CoolRunner-IIファミリ概要

| CoolRunner-II CPLDファミリ             |         |         |         |         |         |         |

|------------------------------------|---------|---------|---------|---------|---------|---------|

| 機能                                 | XC2C32A | XC2C64A | XC2C128 | XC2C256 | XC2C384 | XC2C512 |

| マクロセル数                             | 32      | 64      | 128     | 256     | 384     | 512     |

| $F_{\text{Toggle}}$ (MHz)          | 500     | 500     | 450     | 450     | 450     | 450     |

| $F_{\text{SYSTEM}}$ (MHz)          | 323     | 263     | 263     | 256     | 217     | 217     |

| 最大 I/O数                            | 33      | 64      | 100     | 184     | 240     | 270     |

| I/Oバンク数                            | 2       | 2       | 2       | 2       | 4       | 4       |

| LVCMOS, LVTTL (1.5, 1.8, 2.5, 3.3) | ○       | ○       | ○       | ○       | ○       | ○       |

| HSTL, SSTL                         | —       | —       | ○       | ○       | ○       | ○       |

| DualEDGE                           | ○       | ○       | ○       | ○       | ○       | ○       |

| DataGATE, CoolCLOCK                | —       | —       | ○       | ○       | ○       | ○       |

| 静止消費電力 ( $\mu\text{W}$ )           | 28.8    | 30.6    | 34.2    | 37.8    | 41.4    | 45.0    |

| 先進のセキュリティ機能                        | ○       | ○       | ○       | ○       | ○       | ○       |

| パッケージ(サイズ)                         |         |         |         |         |         |         |

| VQ44 (10 x 10 mm)                  | 33      | 33      |         |         |         |         |

| PC44 (16.5 x 16.5 mm)              | 33      | 33      |         |         |         |         |

| CP56 (6 x 6 mm)                    | 33      | 45      |         |         |         |         |

| QFG32 (5 x 5 mm)                   | 21      |         |         |         |         |         |

| QFG48 (7 x 7 mm)                   |         | 37      |         |         |         |         |

| VQ100 (14 x 14 mm)                 |         | 64      | 80      | 80      |         |         |

| CP132 (8 x 8 mm)                   |         |         | 100     | 106     |         |         |

| TQ144 (20 x 20 mm)                 |         |         | 100     | 118     | 118     |         |

| PQ208 (28 x 28 mm)                 |         |         |         | 173     | 173     | 173     |

| FT256 (17 x 17 mm)                 |         |         |         | 184     | 212     | 212     |

| FG324 (23 x 23 mm)                 |         |         |         |         | 240     | 270     |

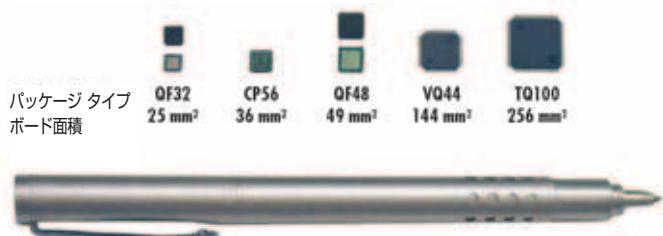

## 図1 MLFパッケージの比較

## 最小コストの小実装面積のパッケージ

## 低コストパッケージの導入

CPLD製品は、新市場へ展開を図るに伴い、パッケージ形状とコストが重要になってきています。ザイリンクスのCPLD担当グループは、顧客ニーズを的確に把握し、より優れた小型パッケージを導入しました。これまで使用されていた高価なチップスケールBGAパッケージに代わる低コストのパッケージで、ほぼ同数のI/Oを備えています。また、図1に示すMLF（マイクロ リード フレーム）パッケージは、小型で多くのI/Oを持っています。

ザイリンクスはCoolRunner-IIファミリCPLD用に新たに2種類のMLFパッケージを導入しました。1つは32マクロセル デバイス用の32ピンQFG（クワッド フラット、鉛フリー対応）パッケージで、21本のI/Oを備えています。もう1つは64マクロセル デバイス用の48ピンQFGパッケージで、37本のI/Oを備えています。これにより、高価なチップスケールBGAパッケージと低コストの薄型クワッド フラット パッケージの中間を埋めるパッケージが提供されたことになります。

また、QFN（クワッド フラット）として知られるMLFパッケージは、小型で多くのI/Oを提供しながら、BGAチップスケールと異なり、

組み立てやプローブが容易です。MLFパッケージは、通常の0.5mmピッチの薄型クワッド フラット パッケージ(TQFP)と同様の組み立てが可能です。このため、BGAパッケージと比べてピン配置や半田リフローが非常に容易に行えます。

MLFパッケージは、デバッグ用に外部ピンを持つためTQFPパッケージと同様にプローブが容易になります。これらの特長により、CoolRunner-II CPLDは民生機器向けに最適なソリューションになっています。

MLFパッケージはまた、電気的特性にも優れ、小型化されているため、パルク容量とイングクタンスはTQFPパッケージよりも小さくなっています。

## 結論

電圧レベルの変換を考慮してデバイスを選択する場合、多くの選択肢がありますが、CPLDはさまざまな理由で最も優れたデバイスであるといえます。CPLDを使用することにより、ロジック機能の追加が可能で、豊富なパッケージ、低消費電力、コスト不要のJTAGテスト、I/Oオプション、先進のセキュリティ、コスト低減など多くの利点が提供されます。ユーザーは、現在使用しているピン配置のまま新しいI/Oバンキング機能の利点を得ることができます。

CPLDの使用方法に関する詳細は[www.xilinx.co.jp/cpld/](http://www.xilinx.co.jp/cpld/)をご覧ください。

設計には、使い易いソフトウェアを無償でご利用いただくことが可能です。その最新のISE™ WebPACK™ソフトウェアは[www.xilinx.com/products/design\\_resources/design\\_tool/index.htm](http://www.xilinx.com/products/design_resources/design_tool/index.htm)からダウンロードが可能です。このような設計ツールとワールドクラスのサポートを提供するザイリンクスCPLDは、ディスクリートのロジックデバイスに代わるロジック ソリューション向けの最適なデバイスといえます。

選ばれるCPLD。

それはRealDigital™ CPLD。

最新の技術革新を遂げたCPLDをお使いでないとしたら、それは CPLDを最大限に活用しているとは言い難いでしょう。ザイリンクスの1.8V CoolRunner-II RealDigital CPLDは、完全デジタルコアにより、高性能と低消費電力、そしてユーザの求める数々の機能をコストアップすることなく実現します。

## 業界最高クラスのシステム パフォーマンス

CoolRunner-II RealDigital CPLDは、マクロセル当たり最大のI/O数を備え、HSTL, SSTLなどの先進のI/Oインターフェイスをサポートしています。消費電力は動作時、静止時ともに、一般的な1.8Vデバイスの20分の1に抑え、400MHzを超えるシステムパフォーマンスを可能にします。独自のクロック分周器により、チップ外部クロックの分周は不要です。RealDigital CPLDは最小パッケージで最高レベルのデザイン セキュリティを保証します。

## CoolRunner-IIの概要

|                  |                                                     |

|------------------|-----------------------------------------------------|

| コア電圧             | 1.8V                                                |

| I/O標準のサポート       | LVTTL, LVCMOS, HSTL*, SSTL*                         |

| I/Oインターフェイス電圧    | 3.3V, 2.5V, 1.8V, 1.5V                              |

| 最大I/O数           | 32~270                                              |

| 性能               | 最大333MHz                                            |

| 消費電力(静止時)        | 100µA未満                                             |

| 集積度(マクロセル数)      | 32~512                                              |

| 使用可能ゲート数         | 750~12,000                                          |

| $t_{PD}^{(max)}$ | 3.5~6.0ns                                           |

| クロックデータ          | あり                                                  |

| クロック分周器          | あり*                                                 |

| ClockCLOCK       | あり*                                                 |

| データゲート           | あり*                                                 |

| パッケージ            | CP56, CP132, VQ44, PC44, TQ144, PQ208, FT256, FG324 |

\*マクロセル数:128以上

## CoolRunner-IIデザインキット

CoolRunner-IIデザインキットを使用いただくとすぐにCoolRunner-IIでデザインを開始できます。機能搭載ボード、プログラミングケーブル、デザインガイド、ソフトウェアリソースCDなどすべてをご提供いたします。キットのお申し込みは、最寄りのザイリンクス販売代理店にお問い合わせください。詳しくは、[www.xilinx.co.jp/cr2/](http://www.xilinx.co.jp/cr2/)にアクセスしてください。また、CoolRunner-II RealDigital CPLDの高機能デザインツールとして、ISE WebPACK™をご利用いただることもお忘れなく。ISE WebPACKは、今すぐインターネットから無償でダウンロード可能です。

# ザイリンクスのロジック コンソリデータで 部材(BOM)コスト低減

ボード上のディスクリート ロジックのトータルコストの削減やザイリンクスCPLDの使用により見込まれるコスト低減の解析を支援するロジック コンソリデータ

Monita Chan

Product Marketing Manager, High Volume

Xilinx Hong Kong

monita.chan@xilinx.com

Ajay Panicker

Field Applications Engineer

CG-Coreel, India

ajay@cg-coreel.com

既存のシステム デザインをアップグレードする際、システムを改良しコスト削減を図ることは重要なトレンドとなってきています。すなわち、企業は競争力を高揚させるため、既存製品の機能セットに改良を加えトータル コストの削減を図り、より多くのシステムをより低価格で提供する必要があります。

従来のシステムでは、デザインに必要なグローロジックや制御ロジックをインプリメントするために、常にディスクリート ロジック デバイスが使用されてきました。ディスクリート ロジックが選択された主な理由は、低価格で入手が可能なことにありました。しかし、ディスクリート ロジックは、ボード面積や消費電力、プログラマビリティの点から最適な選択ではありませんでした。

プログラマブル ロジック デバイスの導入により、プログラマビリティや柔軟性、ならびにより高レベルの統合化がもたらされました。しかし、同時にディスクリート デバイスを上回るコスト増も招きました。

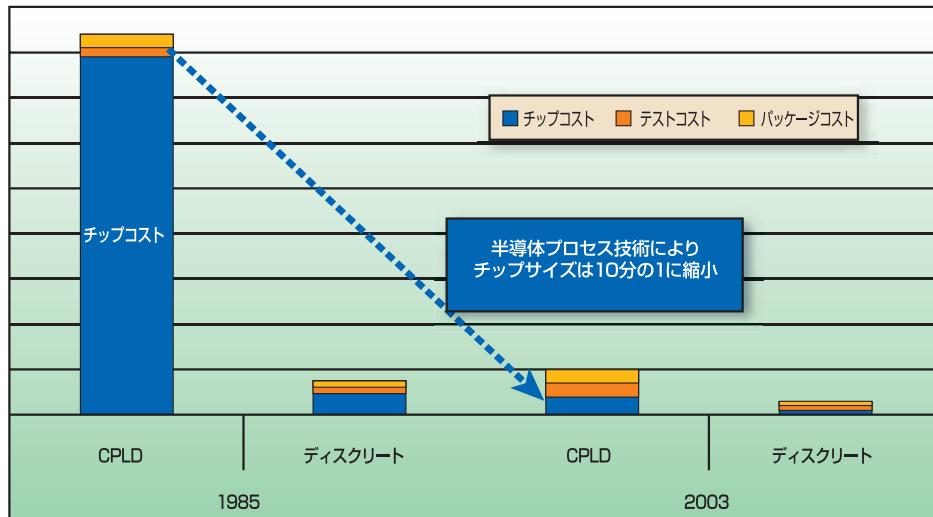

プログラマブル ロジック デバイスのコストは、過去10年間の製造プロセスとパッケージング技術の進歩により大幅に低減されました。今日では、CPLDの単価はディスクリート ロジック デバイスと置き換える可能なレベルまで下がり、かつ、高性能、デザインの柔軟性、リプログラマビリティ、信頼性といった利点を保持しています(図1)。

## ロジック コンソリデータ

ザイリンクスはロジック コンソリデータ (Logic Consolidator) という解析ツールを提供しています。このツールは、複数のディスクリート デバイスの代わりに1個のCPLDを使用することでコストとボード面積をどれだけ低減できるかを即座に正確に見積もることができます。またこのツールは、Microsoft社のExcelがベースになっており、1個のCPLDに集積できるディスクリート ロジック デバイスの数を見積もることができます。ザイリンクスのXC9500XLとCoolRunner™-IIの1万個の金額は、使った7400系ディスクリート ロジック デバイスで構成した最も低コストのプラスチック パッケージを1万個の平均金額と比較されます。また、より正確に比較するため、見積書に基づいて独自の価格を指定することもできます。

ロジック コンソリデータは、設計者だけでなく管理者にもメリットをもたらします。購買部門の管理者は、このツールを使用して、陳腐化したディスクリート ロジック デバイスのうち、ザイリンクス CPLDとの置き換えが望ましいデバイスの数を示し、アップグレードを妥当とするコスト削減効果を確認することができます。設計者は、種々のディスクリート ロジック デバイスを、どのPLDに置き換えるかを判断するために費やす貴重な設計時間を節約することができます。

本稿では、実際にロジック コンソリデータを使用して解析を行った結果、ザイリンクスCPLDによりディスクリート ロジック デバイスを上回るコストメリットが得られ、何千ドルものコスト削減を実現した例を紹介します。

## ケーススタディ

ボード上のディスクリート ロジックの全部を1個のザイリンクス CPLDに統合するという提案に、当初懐疑的であったあるユーザーは、ロジック コンソリデータによる解析結果により、納得することができました。

図1 チップサイズの縮小によりコストを劇的に低下するCPLD

インド最大手のハードウェア設計会社で、ザイリンクスXPERTSパートナーでもあるWipro Technologies社は、既存のテレコム製品をアップグレードするプロジェクトに取り組んでいました。そのプロジェクトでは、製造コストの削減と複数の拡張機能の追加がプロジェクトの主な目標でした。ザイリンクスの販売代理店であるCG-CoreE社のセールスチームは、Wipro社に、初期段階からロジックコンソリデータを導入し、ボード上の複数のディスクリートデバイスと置き換える最適なCPLDを特定する作業を支援しました。

ロジックコンソリデータは、非常にシンプルで、すべてのディスクリートロジックについてどのCPLDに置き換えるかを最短時間で判断します。図2に、Wipro社が使用したロジックコンソリデータツールの画面を示します。

このケースでは、1個のザイリンクスCPLDに統合可能な73個のディスクリートロジックデバイスを特定することができました。

Wipro社は、XC9500XLデバイスあるいはCoolRunner-IIデバイスのいずれかを使用可能な電源電圧に対応して選択することができました。どちらを選択しても、直ちにBOM (Bill of Material) コストが低減でき (XC95288XLデバイスでは0.74ドル、XC2C256デバイスでは1.81ドル)、同時にCPLDの約40%を超える領域に、機能強化用ロジックを追加するスペースができました。

Wipro社のエンジニアは、このデザインを実際にインプリメントする段階で、ザイリンクスのソフトウェアツールISE™で最適化した結果、144のマクロセルを持つ次に小さいザイリンクスデバイスXC95144XL-10TQ144Cに、デザインがぴったり収まりました。XC95144XLデバイスの定価は6.45ドルなので、さらにコストを削減することができました。PC基板に関しては、ボード面積を約70%以上、ボード配線は60%以上が低減され、ボード設計時間を50%短縮でき

る可能性があります。

これに、プログラマビリティ、ボード設計の複雑さの軽減、消費電力とEMI (電磁波干渉) の低減による信頼性の向上といった利点を加えた結果、Wipro社は、ザイリンクスCPLDが正しい選択であることを確信しました。

Wipro社は、ロジックコンソリデータの優れた効率と有用性を実感し、このプロジェクトの後も、同社のテレコム製品のアップグレードプロジェクトに含まれるすべてのカードにこの解析ツールを使用することを決めた上、将来のプロジェクトにも利用する計画です。

## 結論

ロジックコンソリデータは、ユーザーがさまざまな選択肢のコストを自分で解析できるように支援する強力なツールです。このツールはMicrosoft社のExcelベースで構築されており、使用方法はいたって簡単です。ロジックコンソリデータは [www.xilinx.co.jp/products/cpldsolutions/logic\\_tool.htm](http://www.xilinx.co.jp/products/cpldsolutions/logic_tool.htm)よりダウンロードが可能です。また、詳細につきましては、ザイリンクス販売代理店までお問い合わせください。現在、新バージョンでは、より多くのロジックデバイスの選択が可能です。✿

図2 ロジックコンソリデータにより、Wipro Technologies社は複数のディスクリートロジックデバイスの代わりに1個のCPLDを使用するコストメリットを認識

**7400 Conversion Calculator**

Please Select Category, Device & Total

| Category                                                                              | Device | Description                                                          | Total | Discrete                                                                                                        |              | MacroCell Utilization |                |

|---------------------------------------------------------------------------------------|--------|----------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------|--------------|-----------------------|----------------|

|                                                                                       |        |                                                                      |       | Cost \$                                                                                                         | CoolRunner   | \$500                 | MacroCell      |

| SSI Gates                                                                             | 7400   | Quad 2 Input NAND                                                    | 7     | 0.67                                                                                                            | 5            | 5                     |                |

| SSI Gates                                                                             | 7402   | Quad 2 Input NOR                                                     | 5     | 0.50                                                                                                            | 13           | 13                    |                |

| SSI Gates                                                                             | 7404   | Hex INVERTERS                                                        | 4     | 0.42                                                                                                            | 16           | 16                    |                |

| SSI Gates                                                                             | 7410   | Triple 3 Input NAND                                                  | 2     | 0.38                                                                                                            | 4            | 4                     |                |

| SSI Gates                                                                             | 7427   | Triple 3-Input Positive-NOR Gates                                    | 2     | 0.20                                                                                                            | 4            | 4                     |                |

| Registers                                                                             | 7474   | Dual D-Type Positive-Edge-Triggered Flip-Flops With Preset And Clear | 10    | 0.85                                                                                                            | 13           | 13                    |                |

| All Devices                                                                           | 74163  | Sync 4-Bit Binary Counter w/Sync CLR                                 | 10    | 1.50                                                                                                            | 33           | 33                    |                |

| All Devices                                                                           | 74164  | 8 Bit Parallel Out Serial Shift Register                             | 3     | 0.42                                                                                                            | 16           | 16                    |                |

| All Devices                                                                           | 74165  | Parallel Load, 8 Bit Shift Register w/Comp Outputs                   | 3     | 0.27                                                                                                            | 18           | 18                    |                |

| All Devices                                                                           | 74175  | Quad D-Type FlipFlop w/CLR                                           | 1     | 0.14                                                                                                            | 5            | 5                     |                |

| All Devices                                                                           | 74257  | Quad 2 to 1 Data Selector/Mux                                        | 3     | 0.45                                                                                                            | 8            | 8                     |                |

| All Devices                                                                           | 7485   | 4-Bit Magnitude Comparator                                           | 1     | 0.28                                                                                                            | 4            | 4                     |                |

| All Devices                                                                           | 7474   | Dual D-Type Positive-Edge-Triggered Flip-Flops With Preset And Clear | 10    | 0.17                                                                                                            | 3            | 3                     |                |

| All Devices                                                                           | 74253  | Dual 4 to 1 Data Selector/Mux w/ 3-State Outputs                     | 4     | 2.40                                                                                                            | 5            | 5                     |                |

| All Devices                                                                           | 74257  | Quad 2 to 1 Data Selector/Mux                                        | 1     | 0.15                                                                                                            | 3            | 3                     |                |

| All Devices                                                                           | 74240  | Octal Buffer/Driver w/ 3-State Outputs                               | 1     | 0.12                                                                                                            | 5            | 5                     |                |

| All Devices                                                                           | 7420   | Dual 4 Input NAND                                                    | 1     | 0.13                                                                                                            | 1            | 1                     |                |

| All Devices                                                                           | 7451   | Two 2-Wide 2-Input AND-OR-INVERT Gates                               | 1     | 0.60                                                                                                            | 1            | 1                     |                |

| All Devices                                                                           | 74258  | Quad 2 to 1 Data Selector/Mux                                        | 1     | 0.21                                                                                                            | 3            | 3                     |                |

| All Devices                                                                           | 74241  | Octal Buffer/Driver w/ 3-State Outputs                               | 1     | 0.18                                                                                                            | 5            | 5                     |                |

| All Devices                                                                           | 74112  | Dual JK FlipFlops w/Neg Edge, CLR & PRE                              | 5     | 0.90                                                                                                            | 7            | 7                     |                |

| All Devices                                                                           | 7432   | Quadruple 2-Input Positive-OR Gates                                  | 5     | 0.43                                                                                                            | 13           | 13                    |                |

| User Input (Additional MacroCell Est.)                                                |        |                                                                      |       | 0                                                                                                               | 0.00         | 0                     | 0              |

|                                                                                       |        |                                                                      |       | (Per Board)                                                                                                     | (Dimensions) | Est. MacroCell        | Est. MacroCell |

| Totals                                                                                |        |                                                                      |       | Discrete Device Count                                                                                           | 73           | \$ 11.25              | 187            |

| <b>Conversion Analysis</b>                                                            |        |                                                                      |       |                                                                                                                 |              |                       |                |

| Cost Summary                                                                          |        |                                                                      |       | * Est. Macrocell assumes 32% reduction plus 10% logic integration                                               |              |                       |                |

| Target CPLD<br>Xilinx CPLD Cost<br>Discrete TTL Cost<br>Total Cost Savings /per board |        |                                                                      |       | CoolRunner<br>XC2C256      XC95288XL<br>\$ 9.44      \$ 10.51<br>\$ 11.25      \$ 11.25<br>\$ 1.81      \$ 0.74 |              |                       |                |

| Area Summary                                                                          |        |                                                                      |       | Total MC per device                                                                                             |              |                       |                |

|                                                                                       |        |                                                                      |       | 256      288<br>73.0%      64.8%<br>27.0%      35.2%                                                            |              |                       |                |

# CoolRunner-IIのシリコン機能を利用したコスト削減

CoolRunner-II CPLDの機能により、コンポーネント数の削減、ボード面積の縮小、製造コストの削減を通じPC基板上のトータルコストを低減

Steve Prokosch

Product Solutions Marketing Manager

Xilinx, Inc.

sprokosch@xilinx.com

ザイリンクスは、2001年にCoolRunner™-II CPLDファミリを発表して以来、常にプロセス技術に改良を加え低消費電力化を図ってきました。テクノロジ主導型のメーカーは、常にこの低消費電力化を求められています。このCoolRunner-II CPLDファミリには、これまでのリプログラマブル ロジック デバイスに見られない特長があります。それは、さらなる低消費電力化や高速化を可能にするとともに、最も重要な点としてシステムコストを低減する集積化された機能の提供にあります。

CoolRunner-IIの設計チームは、今日のCPLD市場で求められている低コスト性を維持しながら機能を追加する方法を模索しました。この目標を達成するために、機能あたりのコストの観点から、クロック ダブル、クロック ディバイダ、入力ヒステリシス、I/Oバンキングが考案されました。これにより、最小限のシリコン面積にこれらの機能を組み込むという極めて創造的な手法に到達しました。ある機能をデバイスに追加しようとする際、それにより削減されるシステムコストがチップ サイズの増大に見合うほど大きいものでなければ、その機能のデバイスへの追加は見送られることになりました。このように、機能とコストとのバランスをとることにより、CoolRunner-II CPLDは類のない利点を提供します。

## コスト削減をもたらす機能

通常のプロセス技術の微細化により、シリコンコンポーネントのサイズの縮小化を図ることができます。今回、CoolRunner-II CPLDに搭載された特殊な機能は、この縮小レベルをはるかに超えてデザイン上の総部品点数を削減するものです。このような部品点数の削減は、設計者の創造力次第でとても簡単に実現しますが、複雑な作業にもなり得ます。削減の範囲は、クロッキング機能から、電圧やI/Oレベルの違いに対する単純なロジック機能の集積化にまでおよびます。CoolRunner-II CPLDの特殊機能の背後にあるアイデアは、機能の集積化により設計作業を簡素化することです。まず、最も基本となるのはクロック生成です。

多くのデザインでは、デザインに必要な複数の周波数は1つのクロックソースですべて生成できるとは限りません。また、PC基板がハンドヘルド機器よりも大きい場合、クロックスキーが関わる可能性があります。CoolRunner-IIは、このようなクロッキングデザイン上の問題を考慮して開発されました。

### クロックダブルとディバイダ

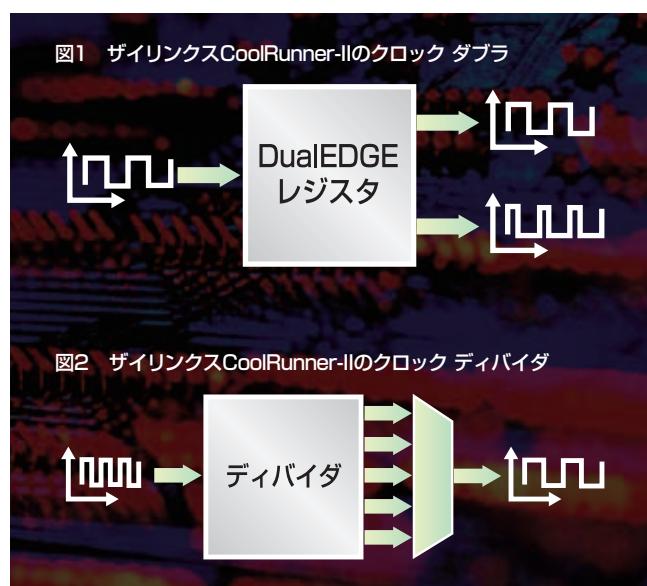

CoolRunner-IIには、DualEDGEとクロックディバイダ（マクロセル数128以上のデバイスに搭載）の2つの機能が搭載されています。DualEDGEフリップフロップが、シーケンシャル動作の性能を向上させるのに対し、クロックディバイダは消費電力の低減を可能にします。

これらメリットは氷山の一角にすぎません。まず、入力クロックの2倍の周波数を生成できる簡単なクロックダーリング方式から紹介しましょう。この方式は、1つのクロック入力から2つのクロックソースを生成します。これにより、シリアルデータフローを改善する目的でクロックの高速化が必要となった場合、DualEDGEフリップフロップが最適です。また、パルス幅変調機能の改良やタイマ/カウンタの分解能の向上にも威力を発揮します。このように、デザインの高速動作が求められる部分に対し、別のクロックソースを使用する必要がありません。

もう1つ重要な点は、クロック入力ピンを節約できることです。つまり、DualEDGEフリップフロップを使用すると、CPLD上の入力ピンを使用することなく自由なクロックが得られます。図1は、DualEDGEフリップフロップを簡略化して示したものです。

クロックディバイダ機能（図2）は、同様に、有用なI/Oピンを節約した状態で、余分なクロックソースを除去します。CoolRunner-IIのクロックディバイダ回路の優れた点は、実際にデューティサイクルが改善されることです。たとえば、入力クロックソースのデューティサイクルが60/40である場合、内部のディバイダ回路が実際にデューティサイクルを補正します。そのためCPLD内部では、50/50のデューティサイクルが得られます。この機能は、クロックスキーの問題を回避し、さらに複数のオシレータ入力を除去するのに効果的です。

クロックディバイダは単に2分周するだけではありません。設定によって8種類の分周が可能です（図2参照）。したがって、クロックディバイダをDualEDGEフリップフロップと一緒に使用すると、複数の組み合わせのクロック周波数を生成することができます。クロック周波数奇数になるという面倒な問題に関しては、クロックの選択肢をさらに増やして奇数の周波数比が得られるように整数分周（6、10、14など）を使用するだけで解決できます。

### 入力ピン機能

設計チームは、CoolRunner-II CPLDが低消費電力であるという性質から、ノイズの多い環境に置かれるポータブルアプリケーションが存在するかもしれませんと考えました。そこから、入力ピンにヒステリシス機能を搭載するというアイデアが生まれました。この機能は、すべてのCoolRunner-II CPLDで使用が可能で、機能追加によるシリコン面積への影響がほとんどなく、多くの利点を提供できます。入力ヒステリシスにより、ノイズ環境の問題は回避され、副次的なメリットとして消費電力が低減します。この電力削減は他のCPLDにはない利点です。

では、コストはどのように低減されるのでしょうか。ヒステリシスは、ピンごとにプログラム可能なため、外部のシムミットトリガーデバイスは不要です。このコンポーネントは、安価かもしれません、最初のボード製造後に追加された場合のコストが結果的に高くつく可能性があります。信頼性を考慮して安全性を見ておくのが賢明です。

一般に見落とされるもう1つのコストとして、PC基板の配線コストと回路基板材料の多層化に伴うコストがあります。基板の層数が少ないほど、常にコストは低くなります。

### I/Oバンキング - 電圧とI/O規格の変換

今日、コンポーネントの選択には、広範な選択肢が提供されていることから、入力電圧レベルが同じ部品だけを選ぶ必要はほとんどありません。今日の設計者に求められているTime-to-Marketの要求について考えてみましょう。以前のデザインを一部分でも再利用できない場合、新しい製品のリリースサイクルに遅延が発生する可能性がでできます。たとえば、古いASSPデバイスを使用するデザインは、ユーザーが指定した新しいプロセッサの電圧やI/O構成とは適合しない可能性があります。

この電圧の問題は、1個のCPLDを追加するだけで解決します。それだけでなく、次世代製品向けに市場が要求しているすべての新機能を実現する追加ロジックも手に入ります。さらに、さまざまI/O規格への対応を考慮する必要がありますが、CoolRunner-II CPLDは、これもユーザーに代わって処理することができます。

これらCoolRunner-IIの機能はコスト削減にどのように関わっているかを見てみましょう。ディスクリートデバイスと低コストのザイリンクスCPLDをコスト面で比較すると、同じ機能をより少ないメモリで実現できる上、はるかに多くのものが得られます。ザイリンクスは、ユーザーがどれだけのコストを節約できるかを示すロジック

コンソリデータ (Logic Consolidator) という無償でダウンロード可能なツールを用意しています (最新版ではさらに多くのデバイスの比較が可能)。この解析ツールは [www.xilinx.co.jp/products/cpldsolutions/logic\\_tool.htm](http://www.xilinx.co.jp/products/cpldsolutions/logic_tool.htm) よりダウンロードが可能です。さらに、比較方法を説明したドキュメントも提供しています。

コスト削減の観点ではこれで完璧とはいえない。シリコン以外にコストがかかる要素が多数あるためです。実際、ディスクリートデバイスとそれに関連する在庫、出荷、組み立て、配線の各コストについて調べてみると、ほとんどの場合、1個に集積されたデバイスのほうが低コストです。CoolRunner-II CPLDによる信頼性の向上や多機能性、低消費電力にも注目してみましょう。

#### その他のコスト削減案

CoolRunner-II CPLDには、この他にもコスト削減を可能にする優れた機能があります。OTF (on-the-fly) リプログラミングは、余分なコストをかけずにCPLDデザインに2倍の仕事をさせる機能です。OTFを利用した適切な例を紹介しましょう。ボードへの電源投入時に、1個のCPLDを使用してボード上のザイリンクスFPGAデバイスをコンフィギュレーションします。コンフィギュレーション完了後、電源管理、ディスクリートロジック機能の統合、あるいは標準品の修正箇所のインプリメンテーションを必要とする何らかのシステム機能を実行するように、CPLDの再プログラムが可能です。OTFの詳細については、<http://www.xilinx.co.jp/bvdocs/appnotes/xapp388.pdf> を参照してください。

ザイリンクスCoolRunner-II CPLD用の新しいパッケージオプションは、小型フォームファクタのデバイスのデザインに最適なソリューションです。このパッケージは、一般にマイクロリードフレームまたはクワッドフラットリードなしとよばれ、非常に小型ですが、価格は標準の薄型クワッドフラットパッケージデバイスと同等です。このパッケージは最小限のボードスペースしか使用せず、CoolRunner-II CPLDの優れた低電力動作を発揮させる魅力的な手段です。

#### 結論

本稿で紹介したコスト削減案を是非次回のデザインで活用ください。詳細については、ザイリンクスCPLDのWebサイト [www.xilinx.co.jp/cpld/index.htm](http://www.xilinx.co.jp/cpld/index.htm) をご覧ください。

また、紹介した機能に関する具体的な情報については、アプリケーションノート <http://www.xilinx.co.jp/bvdocs/appnotes/xapp378.pdf> をご覧ください。

CoolRunner-II CPLDの画期的な機能とユーザーの想像力により、デザイン上の問題がより対処しやすいものになることでしょう。皆様のデザインが成功を収めることを願っています。

#### ザイリンクストレーニング

## シグナル インテグリティと基板設計の基礎

コースを好評開催中！

デジタル信号の高速化に伴い、シグナル インテグリティが重要視されています。ザイリンクストレーニングサービスでは、FPGAとの高速インターフェースにおけるシグナル インテグリティの基礎を紹介する2日間のトレーニングコースを開催しています。

2005年6月より好評開催中

Mentor Graphics:HyperLynxによるシミュレーションや、Agilent Technology:TDR測定器を使用した実際の測定など、実践的な演習が豊富なコースです。経験豊富な講師がシグナル インテグリティの基礎から丁寧にご説明いたします。

コース開催日、お申し込み（オンライン登録）は下記URLをご覧ください。

定員数に限りがございますのでお申し込みはお早めにどうぞ。

<http://www.xilinx.co.jp/education>

※本コースは、アジレント・テクノロジー(株)とザイリンクスにより共同開発されました。

ザイリンクス認定トレーニング プロバイダ：

# Spartan-3/3Eの機能を利用した デザインのエリア最適化

従来ハイエンドFPGAのみに搭載されていた分散メモリ、エンベデッド乗算器などの機能を追加し、より効果的な最適化を可能にするSpartan-3/3Eデバイス

## Suhel Dhanani

Senior Marketing Manager, Spartan Products

Xilinx, Inc.

suhel.dhanani@xilinx.com

## Ken Chapman

Staff Engineer, General Products Division

Xilinx, Inc.

ken.chapman@xilinx.com

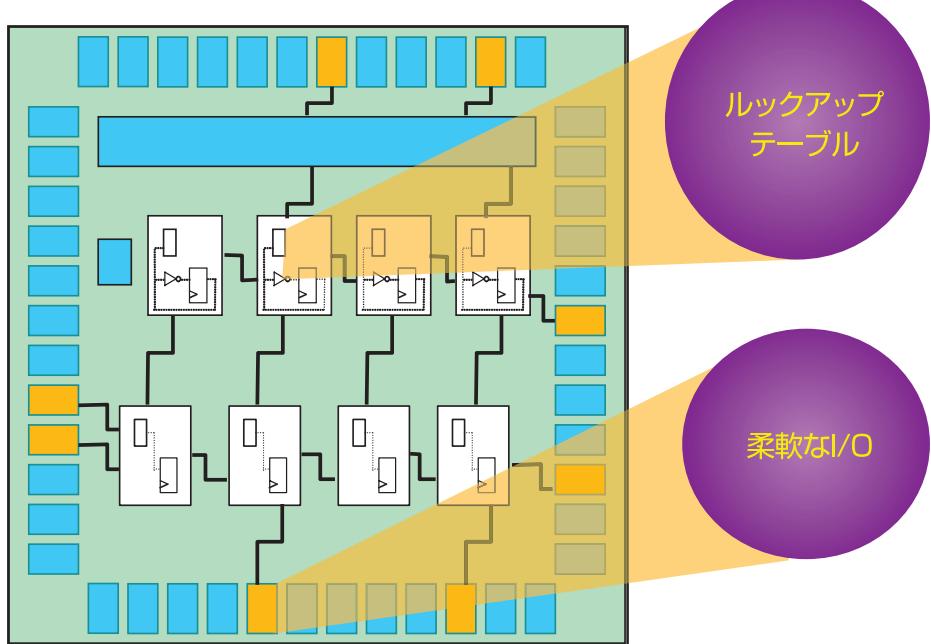

ザイリンクスSpartan™ -3シリーズは、豊富な機能を搭載した低コストFPGAで、高速のエンベデッド乗算器、シフト レジスタとして最適にコンフィギュレーション可能なルックアップ テーブル、分散メモリ、大容量のエンベデッド ブロックRAMを提供します。

これらの機能により、可能な限り最小エリアでのデザインが可能となり、ユーザー デザインにおけるFPGAのサイズ(集積度)が縮小され、その結果FPGAのコストも低減することができます。

Spartanデバイスは、出荷個数が1億個を超え、世界で最高レベルの低コストFPGAアーキテクチャとして短期間で評価を得、何千人の設計者によって利用されています。ザイリンクスは、Spartanの各ジェネレーションで、より多くのロジックとI/Oを追加し、低コスト化を追及してきました。Spartan-3シリーズ時も、今回、新たにエンベデッド機能を追加改善を加えましたが、使い慣れたSpartanデバイスにより多くの機能を統合しました。表1に、これら機能の利点を示します。

## エリア最適化機能

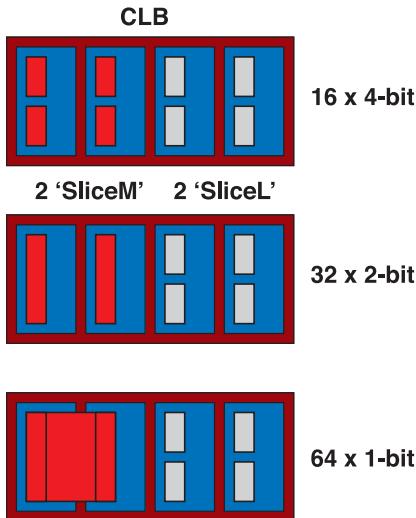

Spartan-3/3Eのアーキテクチャは、メモリ集約型です。このアーキテクチャは、18Kビットのエンベデッド ブロックRAMを搭載しているだけでなく、ルックアップ テーブル (LUT) の半分をメモリとしてコンフィギュレーション可能です(図1)。

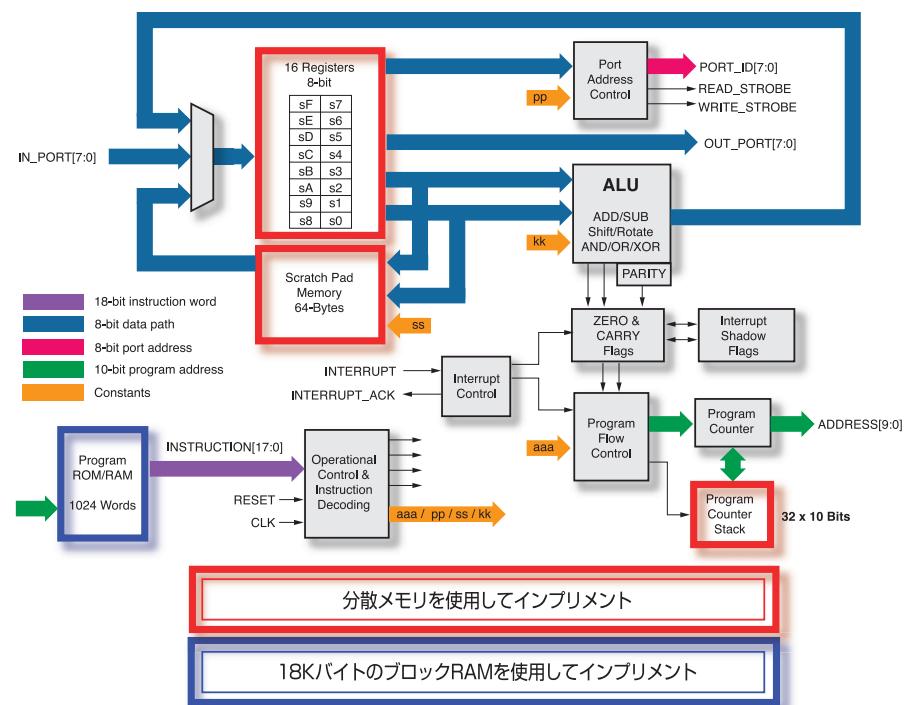

分散メモリを搭載する利点として、小型サイズのメモリ構造を多数必要とするデザインを、レジスタやブロックRAMを使い切ることなく非常に効率良くインプリメントして、比類のないデータ帯域幅を実現できる事があります。良い例として、8ビットのPicoBlaze™マイクロコントローラは、Spartan-3/3Eのアーキテクチャ内でわずか192のロジック セル (LC) を必要とします。図2に示すように、これは、レジスタ スタック、スクラッチパッド メモリ、プログラム カウンタ スタック、プログラムROMが、FPGAのメモリ リソースを使用し構成されているために可能になります。

表1 Spartan-3/3Eファミリに搭載された機能

| エリア使用率を低減するSpartan-3/3Eの機能                 |                                                      |

|--------------------------------------------|------------------------------------------------------|

| エンベデッド乗算器                                  | 各種DSP機能を高いエリア効率でインプリメント                              |

| 最大8個のデジタル クロック マネージャ (DCM)                 | クロック乗算/除算、位相アライメントなどのクロック管理機能をFPGAに集積可能              |

| 分散RAM                                      | 小型FIFO、LIFOバッファ、スクラッチパッド メモリ、レジスタ バンク                |

| 18KビットブロックRAM                              | 大型FIFO、バッファ、キャッシュ メモリ、プロセッサ用 プログラム ストレージ             |

| 16ビット シフト レジスタ(SRL16E)としてコンフィギュレーションされたLUT | FIFO、ディレイ ライン、ステート マシン、ロジック レジスタ、正規集約型デザインにおけるトレードオフ |

| 差動シグナリングのサポート (LVDS、RSDS)                  | ピン数の削減、低消費電力化、EMIの低減、高ノイズ耐性                          |

図1 CLBの2枚のスライス内のLUTは、16×4、32×2、64×1のいずれかのメモリとしてコンフィギュレーションが可能

図2 8ビットのPicoBlazeマイクロコントローラは、Spartan-3/3Eのメモリリソースを効率よく使用することで、192のロジックセルのみで構成可能

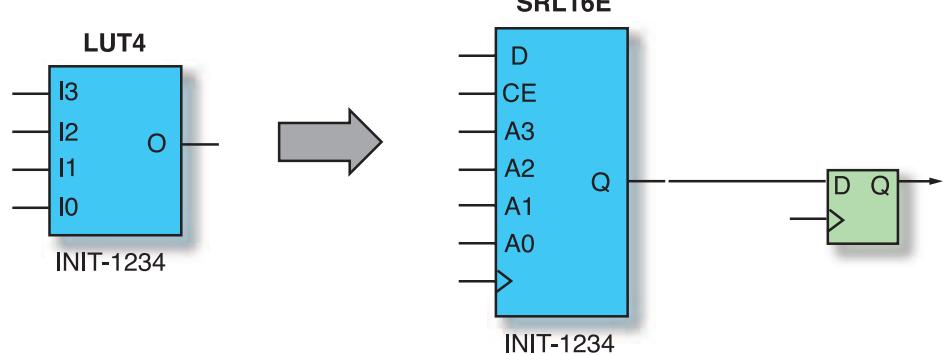

SliceM内の4入力LUTは、SRL16Eモードでコンフィギュレーションが可能です。図3に示すように、このLUTは、専用フリップフロップのほかにクロック イネーブル付きの16ビット シフト レジスタを提供します。

このシフト レジスタへ書き込む場合、新しいデータは常にロケーション “0” に配置され、他のデータはすべて1ロケーション移動します。ただし、データはアドレス入力A[3:0]を使用してどのロケーションからも読み出しが可能です。

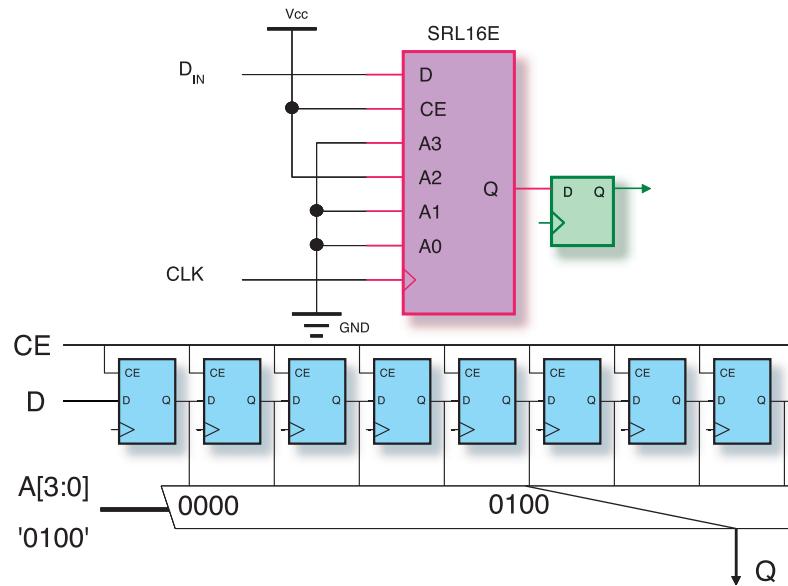

SRL16Eは、ディレイ ラインをインプリメントする上で極めて費用対効果の高い方法を提供します。たとえば図4は、1つのLUTを使用してデータに対し5サイクルの遅延をどのように生成するかを示しています。単に、データをSRL16Eのデータ入力に入れ、アドレスピンを “0100” にハードコード化して、そのアドレスからデータを読み出すだけです。また、合成ツールにより、この手法を自動的にインプリメントすることができ、各LUTで最大16サイクルの遅延まで設定することができます。

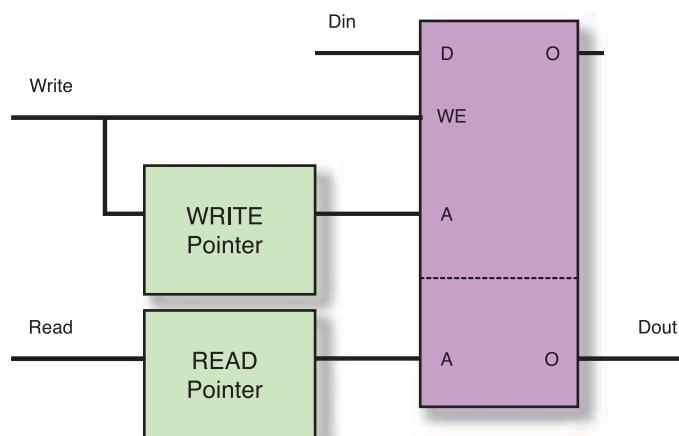

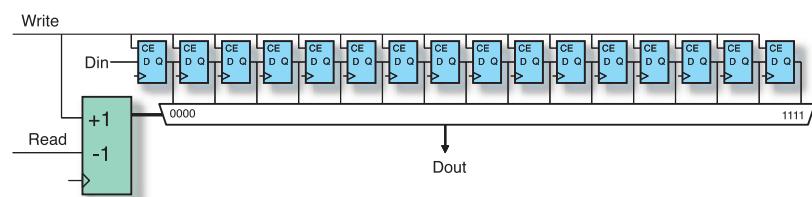

FIFOは、多数のシステム デザインに共通するコンポーネントです。 FIFOを構成するための標準的な方法は、メモリの使用によるものです（図5）。読み出しと書き込みを同時にを行うために、デュアルポート メモリが必要になります。書き込みアドレスと読み出しアドレスを指定する2つのアドレス カウンタも、必要になります。そこで、FIFOの状態を、フル、エンプティ、ハーフフルのいずれであるかを判定するために、コンパレータ ロジックも必要になってきます。

図6では、データ パス幅 (Din) の各ビットに対して1つのSRL16Eを使用し、1個のFIFOをインプリメントしています。SRL16Eは、デュアルポート動作を提供しますが、実際のデュアルポート メモリの半分のスペースを使用します。また、2つのアップ

カウンタの代わりに、アップ/ダウンカウンタが1つだけ必要ですが、これもスペースは半分ですみます。さらに、カウンタ ステータスは、FIFOにワードがいくつ格納されているかを正確に示してくれます。当然、最上位ビットは、非常に有用なハーフフルの状態を示します。

Spartan-3ファブリックで使用可能なエンベデッド乗算器は、さまざまなDSPアプリケーションで役立ちます。各乗算器は、乗算機能のインプリメントに通常必要とされる450ものロジックセルに相当します。

有限インパルス応答 (FIR: Finite Impulse Response) フィルタの多数のインプリメンテーション（基地局、デジタル ビデオ機器、ワイヤレスLAN、xDSL、ケーブル モデム）は、乗算/累算機能を利用します。Spartan-3のファブリックでは、最小限のエリアを使用して、複数のMAC（乗算/累算器）を使用する高性能のFIRフィルタをインプリメントすることができます。このようなMAC集約型の機能は、エンベデッド乗算器を持たない競合他社のFPGAでは、通常、ロジックリソースを大幅に消費することになります。

図3 Spartan-3 FPGA内のLUTの半分は、16ビットシフト レジスタとしてコンフィギュレーション可能

## 結論

Spartan-3/3Eの機能は、最小限のシリコンエリアのみを使用し、その結果最小コストのデザインのインプリメンテーションを可能にすることで、コスト削減を図れるように設計されています。Spartanデバイスは、業界最先端の製造プロセスを採用し、最小サイズのFPGAにさらに多くの機能を集積できる機能を搭載しています。

図4 5サイクルの遅延を生成するようにコンフィギュレーションされたLUT

図5 デュアルポートRAMと2個のカウンタを必要とする従来のFIFO

図6 カウンタを1つ使用するSRL16Eモードで1個のFIFOをインプリメント可能

データバスは通常LUT数個分の幅になります

## 合成ツールでSRL16Eモードをサポート

以下のコードはSRL16Eのフル機能を記述したもので、しかし、合成ツールを使用すると自動的に1つのSRL16Eになります。したがって、全コードは1つのルックアップ テーブルを使用してインプリメントされます。

```

storage: process (clk)

begin

if clk' event and clk=' 1' then

—enable only applies to the input path

if input_enable = '1' then

store0_data <= data_in;

store1_data <= store1_data;

store2_data <= store2_data;

store3_data <= store3_data;

store4_data <= store4_data;

store5_data <= store5_data;

store6_data <= store6_data;

store7_data <= store7_data;

store8_data <= store8_data;

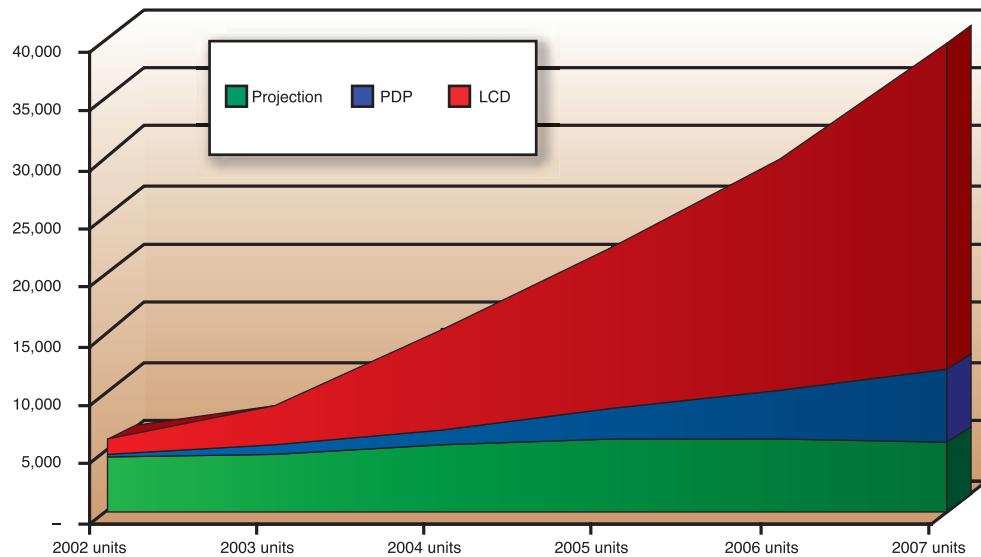

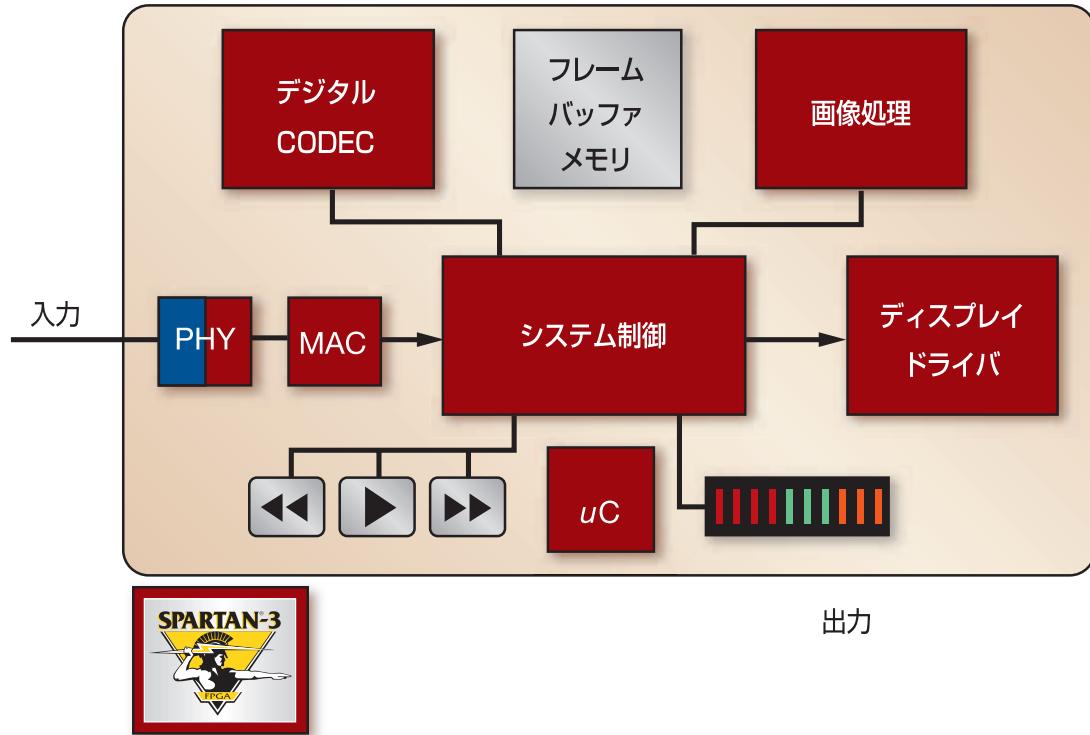

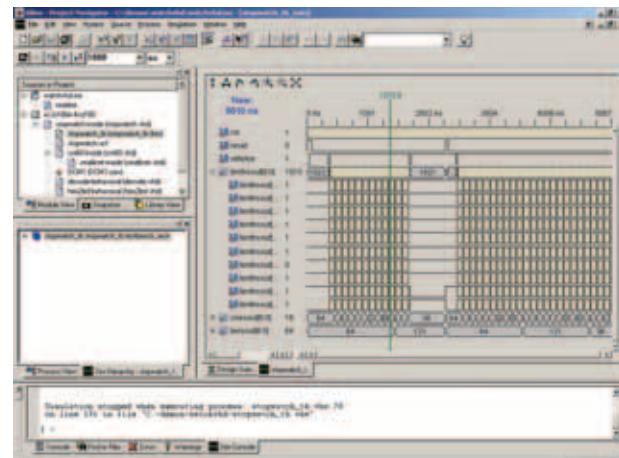

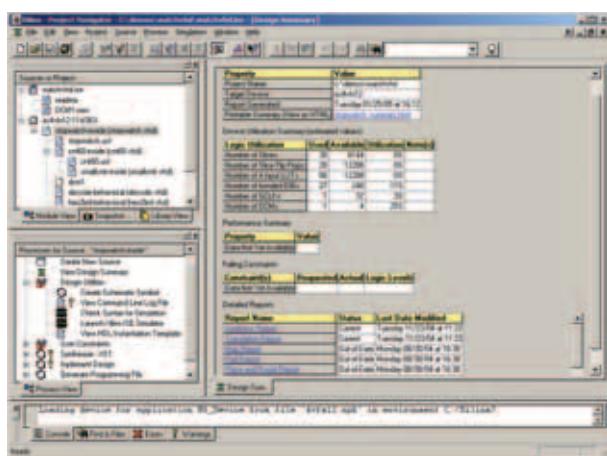

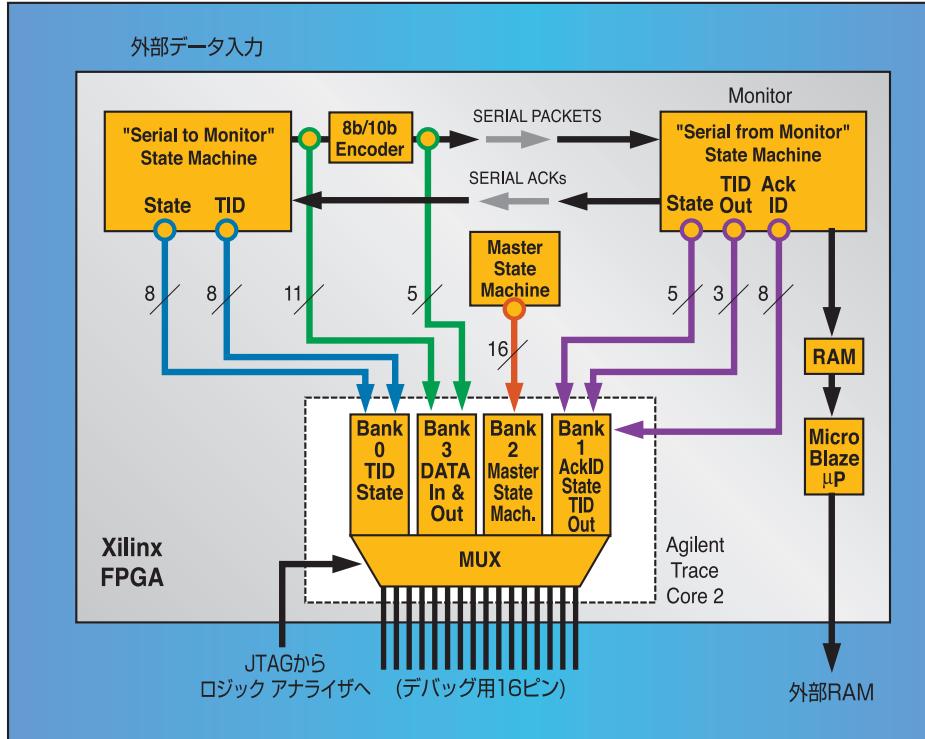

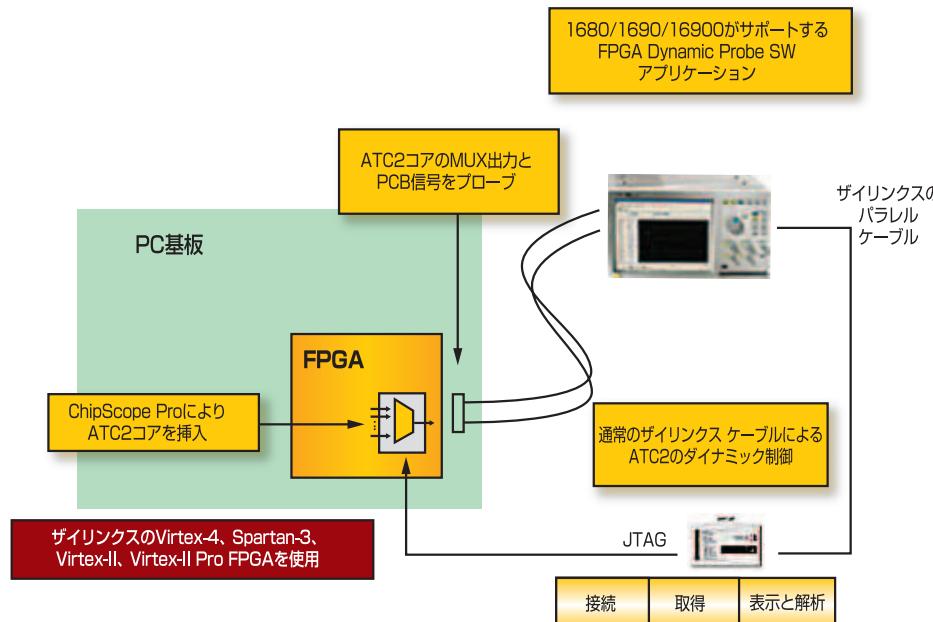

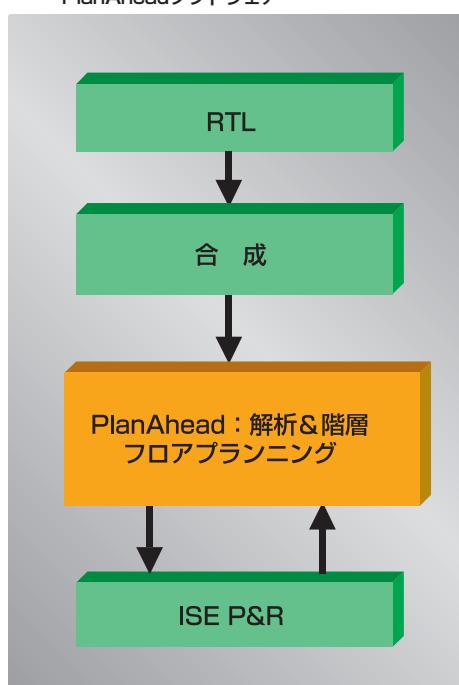

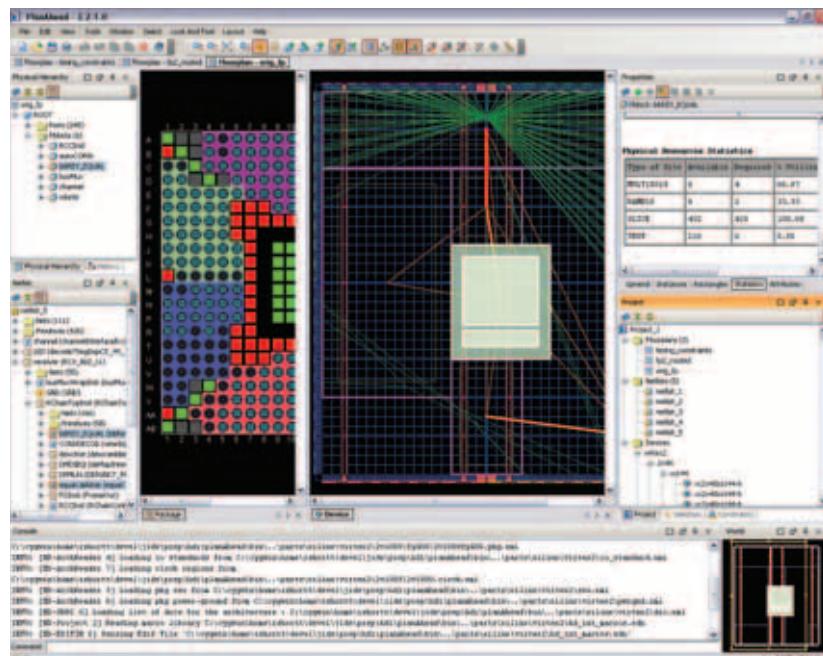

store9_data <= store9_data;