# Xcell journal

SOLUTIONS FOR A PROGRAMMABLE WORLD

61 & 62 号

2008 Winter

## コネクティビティ および XtremeDSP ソリューション 特集号

### Connectivity

PCI Express と FPGA

Aurora IP を用いた

高速シリアル コネクティビティ

ソリューション

変化し続ける

ビデオ放送シーンに対応する

ザイリンクス FPGA

### Digital Signal Processing

明らかになった FPGA の

DSP 性能

宇宙空間からの信号処理

XILINX®

[japan.xilinx.com/xcell/](http://japan.xilinx.com/xcell/)

# インクリメンタル設計フロー

Roger Do

Technical Marketing Manager

Design Creation & Synthesis Division

Mentor Graphics Corporation

FPGA設計プロセスには、元々繰り返しが伴いがちな面があり、設計規模の拡大と複雑性の高まりはこの状況をますます深刻にしています。設計者は設計プロセスの様々な段階で、機能上、性能上の問題に直面します。1カ所の機能上の不具合やタイミング違反を修正することにより、設計の別の部分に問題が生じることもあります。このような修正により何度も設計の繰り返しが発生し、設計プロセスの収束をコントロールすることは困難です。

この問題を解決すべく、FPGA設計ツールを提供する多くの企業がパーティション（ブロック）ベースのインクリメンタルな設計フローを提供しています。パーティショニングにより設計変更の影響を受けない論理ブロックの性能を維持できるだろうと期待されてのことでした。

このアプローチでは、設計者は設計プロセスの早い段階でパーティショニングを行い、各ブロックにパーティショニング制約を設定することが必要とされます。これらの制約はその後の設計プロセスを

通して適用され、設計ブロックを分離しておくのに使用されます。このプロセスに従うことで、処理時間の改善やブロック毎のパフォーマンスの維持が可能になります。

パーティション・ベースのインクリメンタル・フローは効率的であり、デバッグや部分的な再構成ソリューションなど特定のアプリケーションでは必要とされています。しかしながら、このフローには限界があり、期待されたほど広範囲には使用されていません。

## パーティショニングを使わない インクリメンタル更新の必要性

FPGAユーザは設計プロセスが比較的簡単であり、短い設計サイクルで、簡単に目標性能を達成できることを期待しています。パーティション・ベースのインクリメンタル設計フローには人手による作業が多く、QoRも低下する傾向にあるため、広く受け入れられていません。

Precision RTL Plusには、パーティション・ベースのインクリメンタル設計フローがもたらす利点のすべてを人手によるパーティショニングを行わずに実現できる、インクリメンタル設計ソリューションがあります。ユーザが行うべき、人手が必要な事前作業は何もありません。合成と配置配線ツールは設計変更を自動的に判断し、前回のインプリメンテーションに基づいて設計ができるだけ維持しようとします。

RTLソース・ファイルのタイムスタンプの違いではなく、ユーザによる実際の変更に基づいて、適切なユーザ階層でのみリコンパイルが発生します。コメントの追加、スペースの追加、1つのファイルに異なるユーザ階層を組み合わせる、ファイルのタイムスタンプの違いなどは無視されます。RTLに対する機能的、あるいは構造上の変更が、対応するエリアのリコンパイルをトリガします。例えば、VHDLパッケージを変更すると、それに依存したモジュールのリコンパイルが行われます。

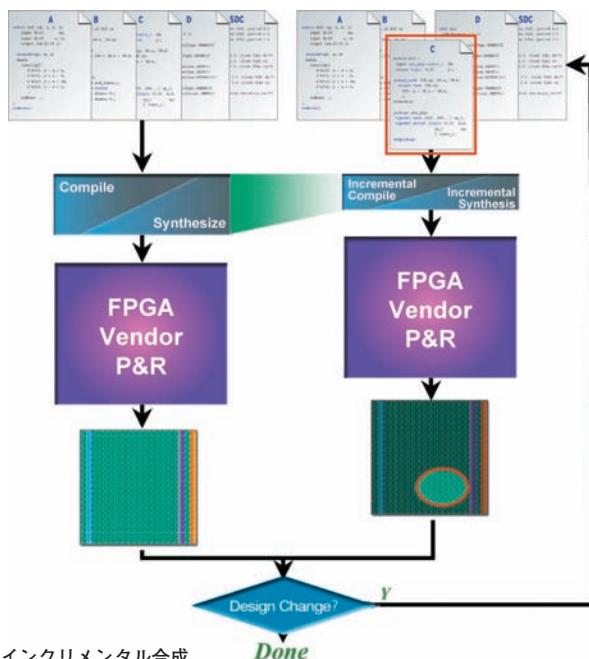

図1：全自动インクリメンタル合成

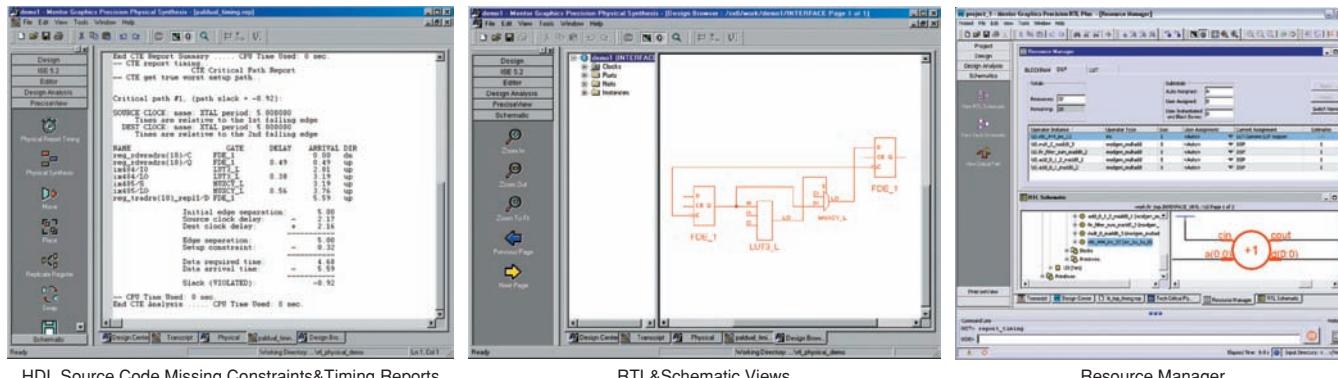

HDL Source Code, Missing Constraints & Timing Reports

RTL & Schematic Views

Resource Manager

図2：挑戦的なデザイン要求の達成

インクリメンタル合成は、RTLの中でユーザが直接変更した階層を自動的に特定します。また、ユーザの変更した階層が要因となり、階層をまたがった最適化により間接的に変更される階層についても特定します。

この点について、Precision RTL Plusは、デザイン内で発生した階層をまたがるすべての最適化をインクリメンタルに追跡しています。例えば：

```

module TOP (input in1, input in2, output out1, output out2);

assign out1 = in1 & in2;

M block_a (in1, 1' b1, in2, out2);

endmodule

```

が次のように変更されたとします。

```

module TOP (input in1, input in2, output out1, output out2);

assign out1 = in1 ^ in2;

M block_a (in1, 1' b1, in2, out2);

endmodule

```

モジュールTOPは、モジュールTOPのRTLが変更されているので、変更されたものとして識別されます。しかし、Mの内部に伝播される定数はこの定数に基づく最適化結果と同じであるため、Mは変更されていないものと識別されます。

次のような変更が行われた場合、インクリメンタル合成はTOPとMのどちらも変更されたと認識します。

```

module TOP (input in1, input in2, output out1, output out2);

assign out1 = in1 & in2;

M block_a (in1, 1' b0, in2, out2);

endmodule

```

TOPはユーザにより実際に変更され、その変更はM内部の最適化にも影響するためです。従って、ツールはどちらのモジュールも合成します。

ユーザのRTL変更により直接的、間接的に影響を受けるすべてのユーザ階層を特定した後、Precision RTL Plusはこれらの部分だけを選択的に合成し、変更のない部分については前回の実行結果を使用します。

Precision RTL Plusの柔軟なインクリメンタル設計フローは以下の機能を備えています。

- タイムスタンプではなくパース・ツリー比較に基づいて実際の設計変更を認識し、間違った更新を防止。コメントやスペース、インデントの追加等の変更は自動的にフィルタリング処理

- インクリメンタル設計フローでは、境界を超えた最適化を適切に行うことにより高い結果品質を維持

- ユーザ定義の属性セットを必要とせずに実際の設計変更を自動的に認識

- ネットリストのオブジェクト名を維持することにより、配置配線ツールでの名前のマッチングが可能。合成ツールから出力されるネットリストは、配置配線ツールでインスタンスレベルの更新を行うことが可能

- ユーザが簡単にパーティションを指定し、必要な制約を作成するための機能

- ベンダが必要とする、適切なプロパティを備えた單一あるいは複数のネットリストを作成する機能

THE

EDA

TECHNOLOGY

LEADER

最新の製品情報はこちらから

[www.mentorg.co.jp/precision](http://www.mentorg.co.jp/precision)

# コネクティビティの改善と 信号処理の新時代

## Xcell journal

|                   |                                           |

|-------------------|-------------------------------------------|

| 発行人               | Forrest Couch<br>forrest.couch@xilinx.com |

| 編集                | Charmaine Cooper Hussain                  |

| アートディレクター         | Scott Blair                               |

| デザイン/制作           | Teie, Gelwick & Associates                |

| テクニカル<br>コーディネーター | Alex Goldhammer<br>Larry Caputo           |

| 日本語版統括            | 澤田 修<br>osamu.sawada@xilinx.com           |

| 制作進行              | 竹腰 美優紀<br>miyuki.takegoshi@xilinx.com     |

| 制作                | 株式会社ロール                                   |

| 広告                | 有限会社エイ・シー・シー                              |

| 印刷                | ノップス株式会社                                  |

japan.xilinx.com/xcell/

Xcell Journal 61・62 合併号

2008年2月15日発行

Xilinx, Inc.

2100 Logic Drive

San Jose, CA 95124-3400

**ザイリンクス株式会社**

〒141-0032

東京都品川区大崎 1-2-2

アートヴィレッジ大崎セントラルタワー 4階

©2008 Xilinx, Inc. All Right Reserved.

XILINX や、Xcell のロゴ、その他本書に記載の商標は、米国およびその他の国 Xilinx 社の登録商標です。PowerPC は、米国またはその他の国における IBM 社の商標です。ほかすべての名前は、各社の登録商標または商標です。

本書は、米国 Xilinx, Inc. が発行する英文季刊誌を、ザイリンクス株式会社が日本語に翻訳して発行したものです。

米国 Xilinx, Inc. および Xilinx, Inc. 株式会社は、本書に記載されたデータの使用に起因する第三者の特許権、他の権利、損害における一切の責任を負いません。

本書の一部または全部の無断転載、複写は、著作権法に基づき固く禁じます。

Printed in Japan

ザイリンクスの FPGA が、非常に厳しい条件を求める今日のシステムのデザイン/開発にますます重要な役割を果たしているのは、単なる偶然ではありません。卓越したパフォーマンスや、システム レベルのコスト削減、電力効率、迅速な Time-to-Market、そして柔軟性が要求される今日のシステム デザインにおいて、FPGA がもつ柔軟性や、各種の機能・性能が高い評価を得ております。

本誌 Xcell Journal 日本語版 61・62 合併号では、ザイリンクスのコネクティビティと高性能 DSP ソリューションを取り上げ、その重要ポイントにスポットを当てるとともに、インプリメンテーションの例を紹介します。

### コネクティビティ

コネクティビティは優れたシステム デザインを作るうえでいっそう重要な要素になっており、その形態はさまざまです。チップ間接続、ボード間接続、ボックス間接続のいずれのデザインでも、ザイリンクスのコネクティビティ ソリューションを使用することによりターゲット市場における製品の差別化を図り、Time-to-Market をできる限り短縮し、コストを最小限に抑えることができます。ザイリンクスのコネクティビティ ハード ブロックは、ASSP の利点と FPGA の柔軟性を併せ持っているのです。

ターゲット市場の例としては、航空宇宙、オートモーティブ、放送機器、民生機器、サーバー/ストレージ、産業/科学分野や医療機器、ワイヤード/ワイヤレス通信市場などがあります。ザイリンクスは、シグナル インテグリティや電源管理、エリア、パフォーマンスなど、これら市場におけるデザイン チャレンジを明確に理解したうえで、一方にユビキタスな PCI Express、もう一方にギガビット イーサネットというように、システム 階層の各コンポーネントに対して適切なプロトコルを提供します。

### DSP デジタル信号処理

FPGA をベースとする高性能な DSP システムが要求される代表的なアプリケーションであるワイヤード/ワイヤレス通信では、より高い品質とバンド幅、音声、コンピュータ、ビデオ データ通信の低価格化が世界的に求められるなか、新たな通信規格が指数的に増え、内容も以前より格段に複雑化しました。その主な理由は、レガシー ネットワークと次世代ネットワークの多数のレイヤ間で相互運用性とデータ交換が不可欠なことがあります。各規格とそれぞれの価格/性能/消費電力比を満たすために、システム ベンダは多大な労力を投じてきました。このようなダイナミックな市場では、FPGA 特有の柔軟性は次のような利点を発揮します。

- ・最先端のアルゴリズム ソリューションと新規格の採用によりスピーディな Time-to-Market を実現

- ・環境や機能の変化に容易に適応できるため、オペレーション コストを低減

- ・既存デザインのライフサイクルを延命させることによる投下資本の低減

- ・顧客と市場ニーズの変化に容易に対応

たとえば興味深いアプリケーションとして、宇宙で使われているものもあります。たとえば、本誌記事「宇宙空間からの信号処理」で紹介するように、UC Berkeley (カリフォルニア大学バークレー校) の天文学者らは、Linux、ザイリンクス System Generator for DSP、ザイリンクス EDK からなるプログラミング環境を用いて、最新鋭の無線望遠鏡用に BEE2 プラットフォームを開発しました。BDTI 社の Jeff Bier 社長は、「今日、FPGA は広範な DSP アプリケーションで以前にも増して大きな役割を担っている。この傾向は今後数年にわたって続くと思う」と語っています。

ザイリンクスでは、市場での各種アプリケーションにおけるチャレンジ・課題を解決するために、先進の FPGA デバイス、ハードウェアおよびソフトウェアの開発ツール、開発キット、評価プラットフォーム、さらには包括的なトレーニングやサポートにいたるまで、デザイン完成までのあらゆるステップをサポートいたします。

*Forrest Couch*

Forrest Couch

発行人

澤田 修

日本語版統括

# Xcell journal

## VIEWPOINT

最適なインターフェクトの選択 ..... 4

## CONNECTIVITY

PCI Express と FPGA ..... 6

MGT 高速シリアル リンクを最適化する方法 ..... 12

Aurora IP を用いた

高速シリアル コネクティビティ ソリューション ..... 16

変化し続けるビデオ放送シーンに対応するザイリンクス FPGA ..... 21

NXP/PLDA によるプログラマブルな

PCI Express ソリューション ..... 25

## INTELLECTUAL PROPERTY

車の中のマルチメディア ..... 29

## DIGITAL SIGNAL PROCESSING

明らかになった FPGA の DSP 性能 ..... 32

宇宙空間からの信号処理 ..... 35

Spartan-3A DSP スターターブラットフォームを用いた

プロトタイプ製品の開発 ..... 41

System Generator for DSP 用 IP ブロックを

生成するための MATLAB 活用法 ..... 45

## INFORMATION

ザイリンクス トレーニング スケジュール ..... 10, 15

ザイリンクス販売代理店オリジナル トレーニング ..... 24

ザイリンクス イベント カレンダー & ウェブ セミナー ..... 50

## 広告索引

メンター・グラフィックス・ジャパン株式会社 ..... 表 2-1

株式会社ミッシュインターナショナル ..... 11

シンプリシティ株式会社 ..... 34

アルデック・ジャパン株式会社 ..... 39

株式会社コンピューテックス ..... 44

株式会社図研 ..... 49

有限会社ヒューマンデータ ..... 51

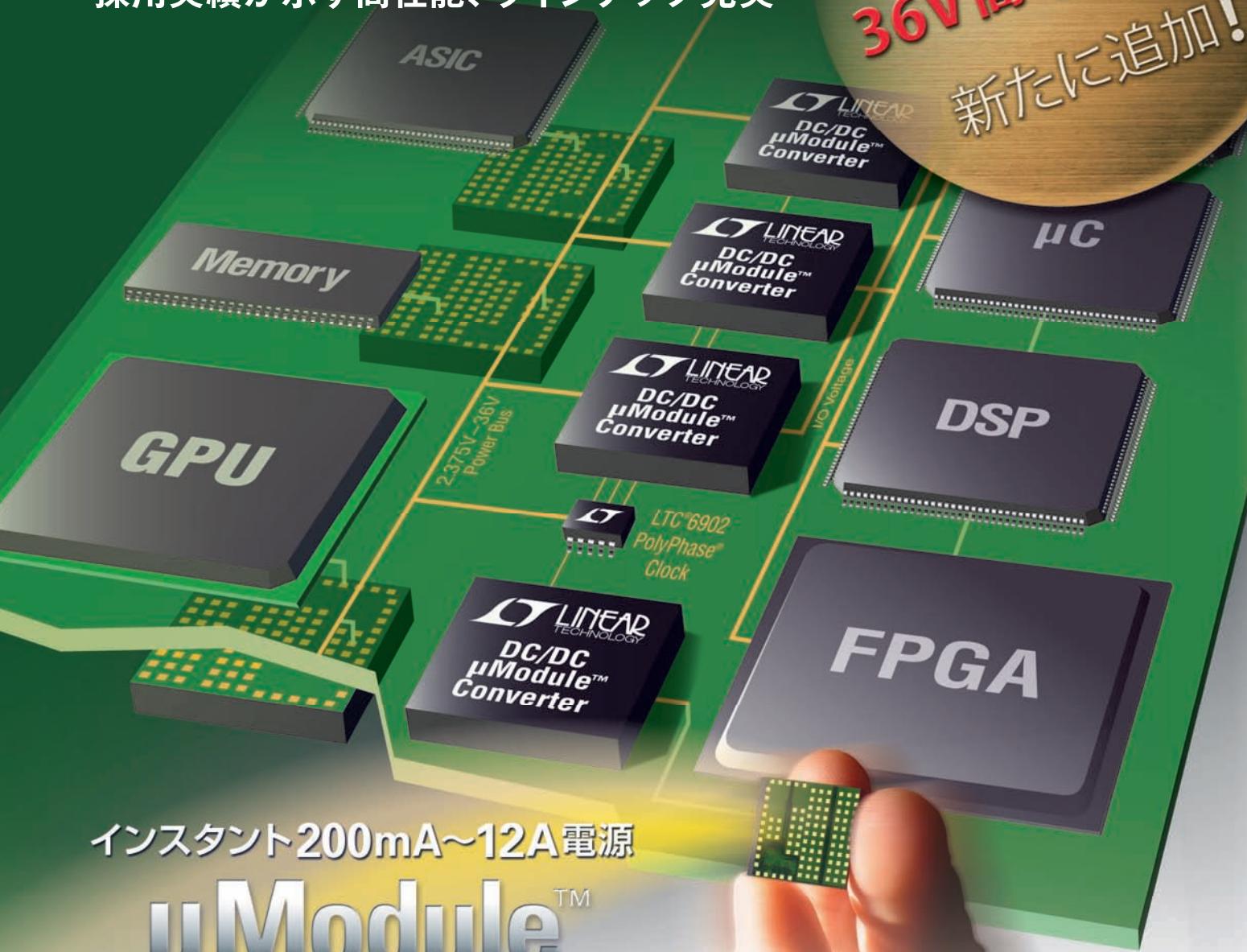

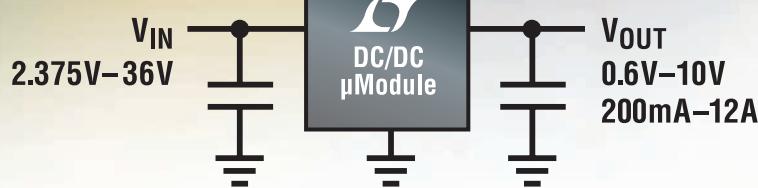

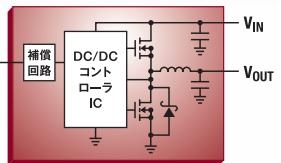

リニアテクノロジー株式会社 ..... 52-表3

ザイリンクス株式会社 ..... 表4

## TABLE OF CONTENTS, 61・62 合併号

### CONNECTIVITY

## PCI Express と FPGA

PCI Express 対応デバイスの開発に、

FPGA はなぜ

ベスト ブラットフォームか

6

### CONNECTIVITY

## Aurora IP を用いた 高速シリアル コネクティビティ ソリューション

ポイント ツー ポイントの接続を

要求するアプリケーション向け

ハイ スケーラビリティ プロトコル

Aurora の活用法

16

### INTELLECTUAL PROPERTY

## 車の中の マルチメディア

自動車用ネットワーク規格の

普及によって注目を集める

車載インフォテイメント

29

### DIGITAL SIGNAL PROCESSING

## 宇宙空間からの 信号処理

UC Berkeleyの天文学者らによる

最先端の電波望遠鏡システム BEE2

- Linux やザイリンクス

System Generator for DSP、

EDK を活用して開発

35

Xcell Journal 日本語版のご送付先住所等の変更は：

<http://japan.xilinx.com/xcell/henko/>

Xcell Journal 日本語版の新規定期購読のお申込みは：

<http://japan.xilinx.com/xcell/toroku/>

# Selecting the Right Interconnect

## 最適な インターフェクトの 選択

インターフェクトは多種多様。

その選択の前に、

開発システムの要件を明確に定義しよう

Jag Bolaria

Sr. Analyst

The Linley Group

jag@linleygroup.com

インターフェクトはパラレルからシリアルへと進化し、通信の効率改善と混雑緩和を実現するため、以前よりも複雑になりました。昨今のインターフェクトは、単にエンドポイントを接続するだけでなく、エンドポイントのネットワーク全体でデータを効率よく伝送するため、広範なプロトコルを定義しています。

したがって、ネットワークとエンドポイントを相互接続する際は、インターフェクトに対して一定の要件を満たす必要があります。たとえば、データレート、レイテンシ、リンクの欠落に対する許容度、スケーラビリティ、冗長性などです。これら要件を考慮したうえでネットワー

クに対する適切なインターフェクトを選択する必要があります。

インターフェクトを選択する際、もう 1 つ重要な要素は、インターフェクト技術に対する既存のエコシステムです。エコシステムがしっかりとしていれば、開発費の削減と Time-to-Market の短縮につながります。本稿では、主なインターフェクトをいくつか取り上げ、それぞれの対象アプリケーションや市場セグメントの位置づけについて解説します。各種インターフェクトとその対称なる主要アプリケーションに関する詳細レポートは、Linley Group 社の Web サイト <http://www.linleygroup.com> をご覧ください。

### PCI Express とイーサネット

Linley Group 社の調査結果から、現在主流となっているインターフェクトは量産プラットフォームに採用されていることが分かります。プラットフォームの数が増えるほど、経済効果により、構築ブロックの低価格化と普及が進みます。さらに、大規模展開されることで技術としての信頼性が高まり、最小限のリスクで他のプラットフォームに流用できるのです。

2 大プラットフォームとは PC とネットワーク機器です。PC プラットフォームは PCI Express とイーサネットの普及に、ま

たネットワーク機器はイーサネットの普及に寄与します。とはいえ、これらのインターフェクトは特定アプリケーションを目的として開発されたため、他の市場にそのまま適用することはできません。半導体業界やシステム ベンダは、新しいアプリケーションの要件を満たすため、これらインターフェクトを改良しています。

たとえば、現在の PCI Express は以前より高いデータレートと多くのレーンをサポートします。また、IOV (I/O 仮想化) によって仮想化に対応し、ストレージ システムやブレード サーバにも展開できるようになりました。

イーサネットについては、IEEE802.3ar と BCN (Backward Congestion Notification) に対応することで、フロー制御の改善、混雑管理機能やリンクが欠落しやすい性質を解決しようとする機能を備えています。これらの改善により、イーサネットをストレージ システムやデータセンタ、バックプレーンに利用しやすくなります。

現在、イーサネットと PCI Express のアプリケーションは格段に増えましたが、技術面、ビジネス面とも、まだすべてのシステム要件を満たすにはいたっていません。たとえば、ブレード サーバーにはイーサネットとファイバーチャネル (FC) が両方使われています。OEM の立場からするとこれらファブリックを一本化したいところですが、エンド ユーザーはすでに FC に多額の投資をしており、将来にわたる長期的なサポートを望んでいます。

また、PCI Express とイーサネットは、高性能コンピューティング (HPC) アプリケーションのスケーラビリティ、レイテンシ、ゼロ欠落の要件を満たしていません。HPC はレイテンシとスケーラビリティを改善するインフィニバンドなどの専用インターフェクトを使います。この場合、OEM はプラットフォームの共通化を図ることで多彩なユーチューズに応えられるよう、柔軟なインターフェクト ソリューションを必要とします。

## 他のインターフェクト

エンドポイントと個々のシステム要件を満たすため、専用インターフェクトを開発することが少なくありません。RapidIO はその好

例です。RapidIO は、ワイヤレス インフラストラクチャ特有の要件を満たすことを目的に、システム ベンダやチップ ベンダが主導で開発してきました。RapidIO は、他のインターフェクトと比較して、ライン カードとネットワーキング/ワイヤレス インフラストラクチャ システムにおける分散コンピューティングに大変優れています。また、RapidIO は Texas Instruments 社の DSP と Freescale 社の PowerPC CPU に組み込まれています。

基地局は膨大な DSP ファームを使うことから、こうしたアプリケーションでインターフェクトに RapidIO を選ぶのはごく自然なことです。将来、RapidIO は複数のデータ ストリームでデジタル信号処理を行う他のプラットフォームにも普及していくものと思われます。

専用インターフェクトとしては、他に XFI、SFI、XAUI、SPAUI、Interlaken、SPI-S、KRがあります。これらのインターフェクトは、各アプリケーションに極めて特有な必須要件を満たすために開発されています。すべてのインターフェクトを解説することは本稿の目的ではありませんが、各インターフェクトがどのような問題を解決するのか、またシステムにどのような影響を与えるのかを理解するため、いくつか見ていきましょう。

XFI と SFI は、10Gbps で光モジュールを接続するために使われます。このデータレートでは、光ファイバに対する電子分散補償、およびボード レースとコネクタに対するイコライゼーションといったシグナル コンディショニングが大きな課題です。このため、信号の伝送路であるチャネルの特性に即した専用コンポーネントが必要になります。

このレートで伝送されるデータはチャネル化、つまり 1 本の物理リンクに複数のストリームを含むことがあるため、トラフィック管理を追加する必要があります。Interlaken、SPI-S、SPAUI といった仕様は、高データレートとトラフィック管理の両方に対応しています。標準規格がないため、システム設計者は現在だけでなく将来のニーズまで見据えて柔軟なソリューションをデザインする必要があるでしょう。

ネットワークとマルチポート ライン カードで 10Gbps のデータレートを利用する場合、

より高いバンド幅が必要となることから、バックプレーンのデータレートを高める必要があります。IEEE 802.3ap は、10Gbps のシリアル リンクを定義する 10GBase-KR 仕様によってこの問題に対処しています。イコライゼーションとプリエンファシスに加え、バックプレーン内の 2、3 個のコネクタと最長 40 インチのトレースにわたって許容可能なパフォーマンスを得るために、フオワード エラー訂正 (FEC) を含める必要がある場合があります。さらに、これらシステムが古いライン カードとの互換性を要する場合には、バックプレーンを 1Gbps または 3.125Gbps に動作させる必要があるでしょう。この場合も、システムの要件を満たすため柔軟なソリューションが不可欠です。

## 結論

インターフェクトを使用するアプリケーションは多種多様で、またシステム設計者にとってインターフェクトの選択肢は実に多彩です。Linley Group 社は、PCI Express とイーサネットが独占的なインターフェクトになるとと考えています。この 2 つのインターフェクトは、サーバーやネットワーキング、ストレージ システム、ワイヤレス ネットワーク、その他多数のシステムに採用されることでしょう。しかし、1 つか 2 つのインターフェクトですべてのシステムの要件を満たすのは不可能です。半導体業界がさまざまなアプリケーション用に専用インターフェクトを開発し、将来にわたりサポートし続けていくのは、まさにそういう理由からです。

独占的インターフェクトと専用インターフェクトは、いずれもより高いデータレート、低いレイテンシ、高いスケーラビリティをサポートしていくことでしょう。これに加え、システムはレガシー カードをサポートする必要があります。

システム設計者の方々には、最適なインターフェクトを選択すると共に、さまざまなインターフェクトとその進化に対応するため、デザインに柔軟性を持たせることをお勧めします。FPGA は、システム設計者にこの柔軟性を提供するだけでなく、幅広いインターフェクトをサポートするうえで重要な役割を果たします。

# PCI Express and FPGAs

# PCI Express と FPGA

PCI Express 対応デバイスの開発に、

FPGA はなぜベスト プラットフォームか

Alex Goldhammer

Technical Marketing Manager, Platform

Solutions

Xilinx, Inc.

alex.goldhammer@xilinx.com

PCI Express は、クロック データ リカバリ (CDR) テクニックを採用する高速シリアル I/O のインターフェクトです。PCI Express Gen1 の仕様は、ラインレートが 1 レーン当たり 2.5Gbps と定義されており、シングルレーン (x1) リンクに対する 2Gbps (8B/10B エンコーディング後) から 32 レーンに対する 64Gbps まで、幅広いスループットのアプリケーションを構築できます。このため、スループットを維持、もしくは改善しつつ、ピン カウントの大大幅な低減を実現します。また、PCB のサイズや、トレースとレイヤの数が減り、レイアウトとデザインが簡素化されます。ピンの数が減るということは、ノイズと電磁干渉 (EMI) が低減されるということです。CDR は、幅の広いパラレル バスにありがちなクロック-データ スキューの問題を解消し、インターフェクトのインプリメンテーションを容易にします。

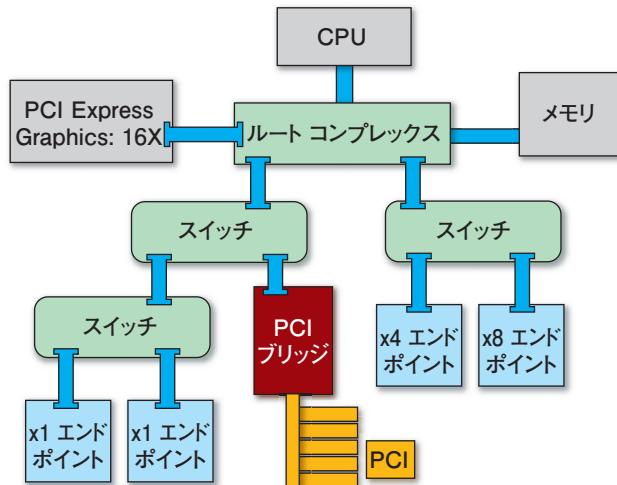

PCI Express のインターフェクト アーキテクチャは、主にデスクトップやラップトップといった PC システムを対象にしています。しかし、PCI と同様、PCI Express はエンベデッド システムをはじめとする他のシステムに急速に採用されつつあります。PCI Express は、ルート コンプレックス、スイッチ、エンドポイントという 3 つのデバイスを定義します (図 1)。CPU、システム メモリ、グラフィックス コントローラは、PCI ホストに相当するルート コンプレックスに接続します。PCI Express はポイント ツー ポイントの性格を持つことから、システム ファンクションの数を拡張するためスイッチ デバイスが必要です。PCI Express のスイッチ デバイスは、アップストリーム側のルート コンプレックス デバイスをダウンストリーム側のエンドポイントに接続します。

エンドポイントの機能は PCI/PCI-X デバイスに似ています。一般的なエンドポイント デバイスとしては、イーサネット コントローラやストレージ HBA (ホストバス アダプタ) があります。FPGA はデータ処理とブリッジング機能に使われることが最も多いため、その最大のターゲットファンクションはエンドポイントです。FPGA のインプリメンテーションは、ビデオ、医療画像処理、産業、

試験／測定、ストレージ アプリケーションに理想的です。

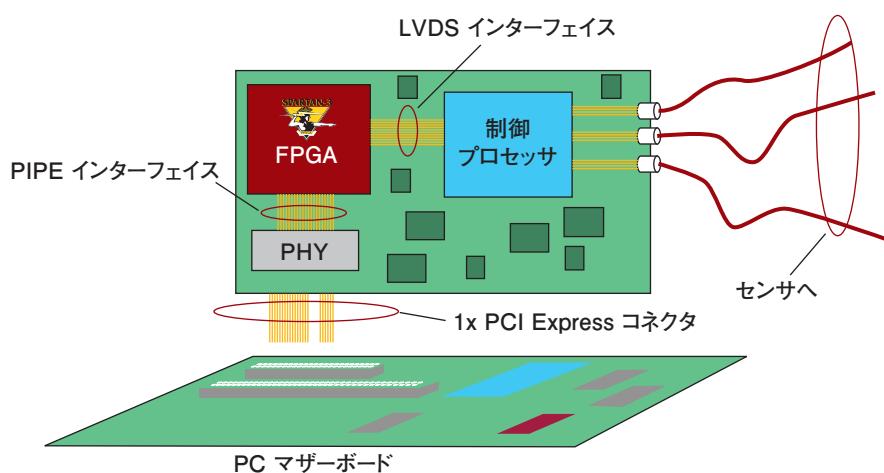

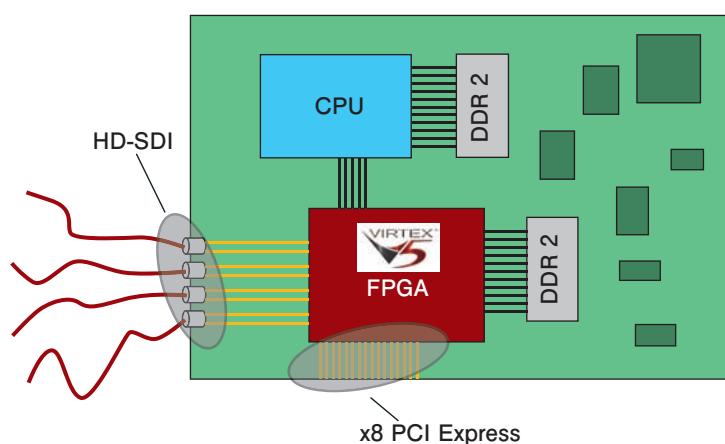

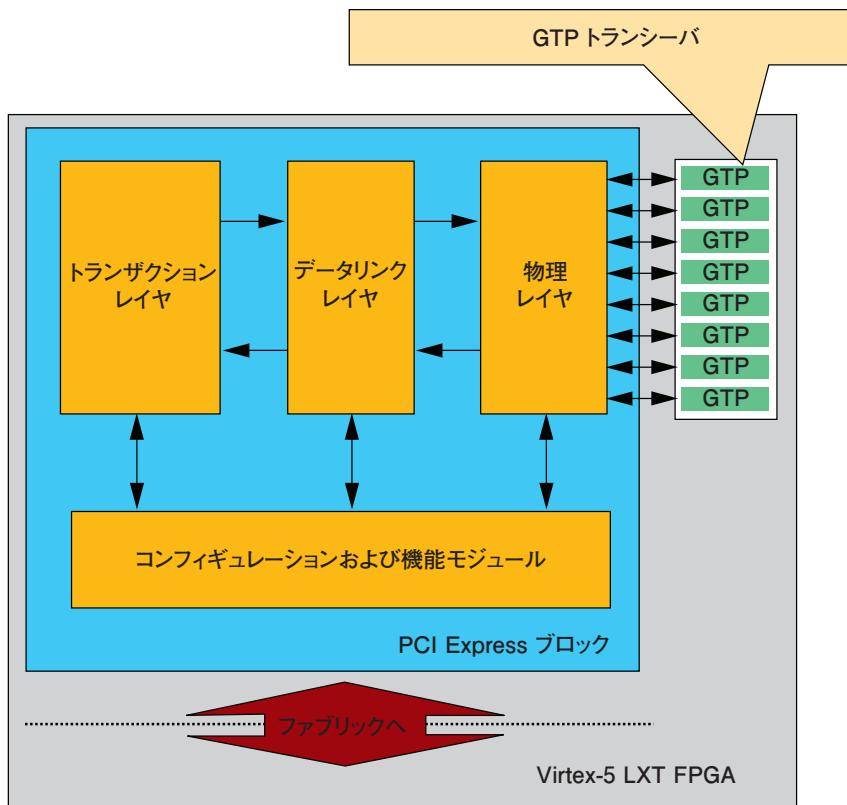

PCI-SIG により策定、管理されている PCI Express 仕様は、PCI Express デバイスに物理レイヤ、データリンク レイヤ、トランザクション レイヤの 3 種類のプロトコル レイヤを定義しています。PCI Express エンドポイントは、1 チップまたは 2 チップのソリューションを用いて構築できます。たとえば、ザイリンクス Spartan™-3 などの低価格な FPGA を使うことで、市販のディスクリート PCI Express PHY を用いてデータリンク レイヤとトランザクション レイヤを構築できます（図 2）。この方法は、バス コントローラ、データ アクイジション カード、パフォーマンスを改善する PCI 32/33 デバイスなど、x1 レーンのアプリケーションに最適です。また、Virtex™-5 LXT/SXT FPGA など、あらかじめ PCI Express PHY が統合されているシングルチップ ソリューションを使う方法もあります。この方法は、より高性能な x4（8Gbps スループット）または x8（16Gbps スループット）リンクを必要とする、通信や高精細オーディオ／ビデオのエンドポイント デバイスに最適です。

PCI Express のデザインをインプリメントするためのテクノロジを選ぶ前に、IP の選択、リンク効率、コンプライアンス テスト、そのアプリケーションに対するリソースの有無について慎重に検討する必要があります。本稿では、最新の FPGA テクノロジを用いて、シングルチップの x4 と x8 レーンの PCI Express デザインを構築するための留意点を説明します。

## IP の選択

ソフト IP は、独自に構築するか、サードパーティもしくは FPGA ベンダから購入できます。IP を独自に構築する場合、デザインをゼロから作成するだけでなく、検証、認証、コンプライアンス、ハードウェア評価についても考える必要があります。サードパーティや FPGA ベンダから購入する場合は、すでに厳しいコンプライアンス テストやハードウェア評価に合格しているため、プラグ アンド プレイで利用できます。動作が保証

図 1 PCI Express のトポロジ

図 2 Spartan-3 FPGA ベースのデータ アクイジション カード

図 3 Virtex-5 LXT FPGA ベースのビデオ アプリケーション

図 4 Virtex-5 LXT FPGA の PCI Express エンドポイント ブロック図

表 1 Virtex-5 LXT FPGA の PCI Express 機能

| パフォーマンス |               |                  |            |

|---------|---------------|------------------|------------|

| レーン     | インターフェイスのデータ幅 | インターフェイスの速度      | バンド幅 (各方向) |

| x1      | 64            | 62.5/125/250 MHz | 2 Gbps     |

| x2      | 64            | 62.5/125/250 MHz | 4 Gbps     |

| x3      | 64            | 125/250 MHz      | 8 Gbps     |

| x4      | 64            | 250 MHz          | 16 Gbps    |

| PCI Express 仕様 v1.1 |                                                    |

|---------------------|----------------------------------------------------|

| 仕様                  | サポート (有／無)                                         |

| クロック トレランス (300ppm) | 有                                                  |

| スプレッド スペクトラム クロッキング | 有                                                  |

| エレクトリカル アイドル生成／検出   | 有                                                  |

| ホット プラグ             | 有                                                  |

| デエンファシス             | 有                                                  |

| ジッタ仕様               | 有                                                  |

| CRC                 | 有                                                  |

| 自動リトライ              | 有                                                  |

| QOS                 | 2 VC/ ラウンド ロビン、加重ラウンド ロビン、または SP (Strict Priority) |

| MPS                 | 129 ~ 4096 バイト                                     |

| BAR                 | メモリまたは I/O にコンフィギャブルな 6 X 32 ビットまたは 3 X 64 ビット     |

| パワー マネージメント ステート    | 有                                                  |

され、仕様に準拠する市販の PCI Express インターフェイスを利用すれば、設計者はデザイン上の最も付加価値を付けやすい部分、つまりユーザー アプリケーションの設計に専念できるのです。ソフト IP を使う際の課題は、アプリケーションに対するリソースの確保です。PCI Express MAC、データリンク、ソフト IP コア内のトランザクション レイヤは、プログラマブル ファブリックを用いてインプリメントされるため、ブロック RAM やルックアップ テーブル、ファブリック リソースがどれだけ残っているかに細心の注意を払う必要があります。

もう 1 つの方法は、最新技術を採用している FPGA を使うことです。Virtex-5 LXT と SXT には、専用ゲートに x8 レーンの PCI Express コントローラがあらかじめ統合されています (図 4)。このような FPGA では、デザインをハード シリコンにインプリメントすることから、FPGA ロジック リソースが最小限で済みます。たとえば、Virtex-5 LXT FPGA では、x8 レーンのソフト IP コアは最高 10,000 ロジック セルを消費することがあります。ハード インプリメンテーションは主にインターフェイス用として約 500 のロジック セルを必要とする程度です。こうしたリソースの節約により、比較的安価な小型のデバイスを選択できる場合があります。また、統合型のインプリメンテーションは一般的に高いパフォーマンスと幅広のデータバスを持ち、ソフトウェアでコンフィギュレーションできます。

ソフト IP によるインプリメンテーションでもう 1 つ課題となるのが機能の数です。通常、ソフト IP コアは、パフォーマンスやコンプライアンスの目標を満たすため、仕様に定められている最低限の機能しかインプリメントしません。一方、ハード IP は顧客のニーズとフル コンプライアンスに基づきながら包括的な機能をサポートします (表 1)。パフォーマンスやリソースに関連する大きな問題もありません。

## レイテンシ

PCI Express コントローラのレイテンシがシステム全体のレイテンシに大きな影響を与

図 5 Virtex-5 LXT FPGA の PCI Express コンプライアンス ワークショップ結果

えることはありませんが、インターフェイスのパフォーマンスには影響があります。レイテンシの問題は、より幅の狭いデータパスを使うことで軽減できます。

PCI Express の場合、レイテンシとは物理レイヤや論理レイヤ、トランザクションレイヤでパケットを受け渡すためにかかるサイクル数のことです。x8 レーンの代表的な PCI Express エンドポイントのレイテンシは 20~25 サイクルです。250MHz では、これは 80~100ns です。125MHz のように、タイミングを簡単にするためにインターフェイスを 128 ビットのデータパスでインプリメントしている場合、レイテンシは 160~200ns に倍増します。最新の Virtex-5 LXT および SXT デバイスでは、ソフト IP、ハード IP とも、x8 インプリメンテーションに対して 250MHz で 64 ビットデータパスをインプリメントします。

## リンク効率

リンク効率は、レイテンシやユーザー アプリケーションのデザイン、ペイロード サイズ、オーバヘッドの相関関係で決定します。ペイロード サイズ（一般に「最大ペイロード サイズ」という）が増えるほど、有効リンク効率は高まります。これは、パケットのオーバヘッドが一定であるため、ペイロードが大きければ効率が向上するためです。通常、ペイロードが 256 バイトだと理論上の効率は 93% です（256 ペイロード バイト + 12 ヘッダ バイト + 8 フレーミング バイト）。PCI Express の最高パケット サイズは 4KB ですが、ほとんどのシステムは 256 または 512 バイト以上のペイロード サイズにしてもパフォーマンスの改善は見られません。Virtex-5 LXT FPGA で x4 または x8 PCI Express をインプリメントした場合、リンク プロトコルのオ

ーバヘッド（ACK/NAK、再送パケット）とフローリミットプロトコル（クレジット レポート）により、リンク効率は 88~89% となります。

PCI Express のインプリメンテーションに FPGA を使うことで、エンドポイントインプリメンテーションに対応する受信バッファ サイズを選択でき、リンク効率をより管理しやすくなります。両方のリンク パートナーがデータパスを同じようにインプリメントしなければ、2 つのリンクの内部レイテンシが異なることになります。たとえば、リンク パートナー #1 がレイテンシ 80ns の 64 ビット、250MHz のインプリメンテーションを使い、リンク パートナー #2 がレイテンシ 160ns の 128 ビット、125MHz インプリメンテーションを使う場合、そのリンクの合計レイテンシは 240ns になります。ここで、リンク パートナー #1 の受信バッファがレイテンシ 160ns 用としてデザインされ、リンク

パートナー #2も 64 ビット、250MHz のインプリメンテーションだと仮定した場合、当然リンク効率は下がります。ASIC インプリメンテーションの場合、受信バッファのサイズを変更することは不可能で、効率は永久に失われたままです。

ユーザー アプリケーションのデザインもリンク効率に影響を与えます。ユーザー アプリケーションをデザインする際は、PCI Express インターフェイスの受信バッファを定期的にモニタし、伝送バッファを常にフルに保つよう留意しなくてはなりません。ユーザー アプリケーションが受信したパケットをすぐに使わない、あるいは伝送要求にただちに応じない場合、インターフェイスのパフォーマンスにかかるわらず全体的なリンク効率が悪化します。

数個のプロセッサでデザインする際、それらプロセッサが 1 DWORD より長いバーストを実行できない場合、DMA コントローラをインプリメントする必要があります。その場合、当然リンクの利用率と効率は悪化します。ほとんどのエンベデッド CPU は 1 DWORD より長いバーストを伝送できるた

め、このようなデザインに対してはしっかりした FIFO デザインにすることでリンク効率を効果的に管理できます。

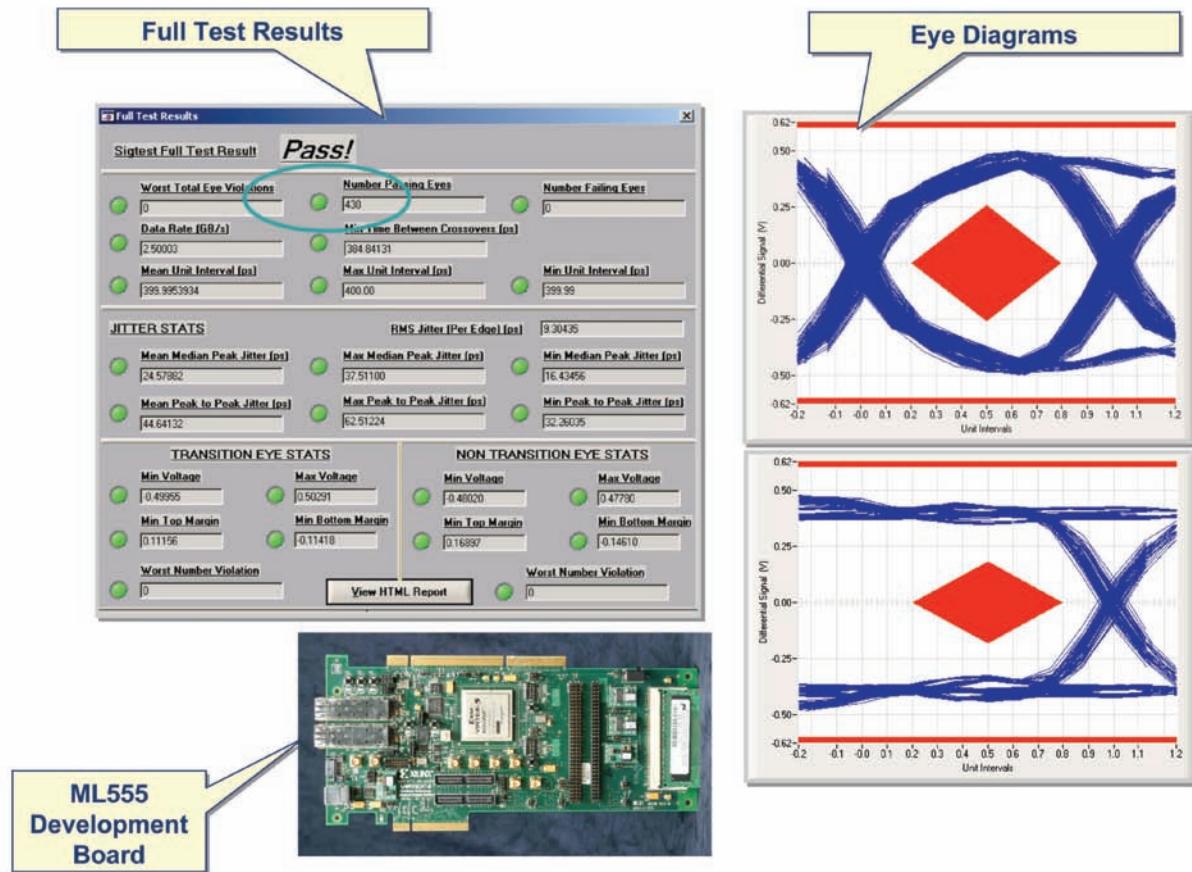

## PCI Express のコンプライアンス

コンプライアンスは重要な点ですが、仕様に準拠しなかったり、過小評価されたりすることが少なくありません。PCI Express のアプリケーションを構築していく、他のデバイスやアプリケーションと連動させる必要がある場合、仕様を満たすデザインにすることが絶対条件です。

コンプライアンスは、IP だけでなく、ユーザー アプリケーションやシリコン デバイス、ハードウェア ボードを含むソリューション全体に必要なことです（図 5）。PCI-SIG の PCI Express コンプライアンス ワークショッピング（通称「プラグ フェスト」）でソリューション全体が認証されれば、そのデザインの PCI Express 部分は正常な動作が保証されます。

## 結論

PCI の後継である PCI Express は、システム インターコネクトの事実上の標準となり、PC のみならず、エンベデッド システム デザインを含む他のシステム市場にまで普及してきました。FPGA は、エンベデッド ユーザーが望む追加のカスタマイズ機能を用いて仕様に準拠する PCI Express デバイスを構築できることから、PCI Express のエンド ポイント デバイスを構築するのに最適です。

Virtex-5 LXT や SXT ファミリといった新しい 65nm FPGA は、PCI Express 仕様 v1.1 に完全に準拠し、ユーザー アプリケーションに豊富なロジック リソースとデバイス リソースを提供します。また、Spartan-3 ファミリの FPGA に外部 PHY を利用することで、低コスト ソリューションを実現できます。これらの要素に加え、プログラマブル ロジック特有の利点である柔軟性、リプログラマビリティ、リスク低減により、FPGA は PCI Express に最善のプラットフォームと言えるでしょう。

# ザイリンクス トレーニング スケジュール [2~3月]

4~5 月のスケジュールは 15 ページをご覧ください。

ザイリンクスでは、大規模、高速 FPGA を対象にした FPGA 設計のための各種トレーニングを各地で開催しております。是非ご利用ください。

| コース名                                    | 日 程                                          | 主 催    | 開 催 地 |

|-----------------------------------------|----------------------------------------------|--------|-------|

| ISE デザイン入力                              | 3月 11 日 (火)                                  | ザイリンクス | 東京会場  |

| FPGA 設計導入                               | 3月 12 日 (水)                                  | ザイリンクス | 東京会場  |

| FPGA 設計実践                               | 2月 26 日 (火)~27 日 (水)<br>3月 13 日 (木)~14 日 (金) | ザイリンクス | 東京会場  |

| アドバンスド FPGA 設計                          | 2月 28 日 (木)~29 日 (金)<br>3月 18 日 (火)~19 日 (水) | ザイリンクス | 東京会場  |

| エンベデッド システム開発                           | 2月 20 日 (水)~21 日 (木)<br>3月 4 日 (火)~5 日 (水)   | 新光商事   | 大阪会場  |

| アドバンスド エンベデッド システム開発                    | 3月 6 日 (木)~7 日 (金)                           | ザイリンクス | 東京会場  |

| System Generator for DSP を使用した DSP デザイン | 2月 19 日 (火)~20 日 (水)<br>3月 13 日 (木)~14 日 (金) | ザイリンクス | 東京会場  |

| MGTシリアル I/O デザイン                        | 2月 21 日 (木)~22 日 (金)<br>3月 25 日 (火)~26 日 (水) | ザイリンクス | 東京会場  |

\*すべてのトレーニングは、ザイリンクス認定インストラクターによるオフィシャル トレーニングです。

\*日程および会場は、都合により変更となる場合もございます。最新情報はザイリンクス トレーニング Web サイトをご覧ください。

詳細とご登録はこちらから ▶▶ <http://japan.xilinx.com/support/education-home.htm>

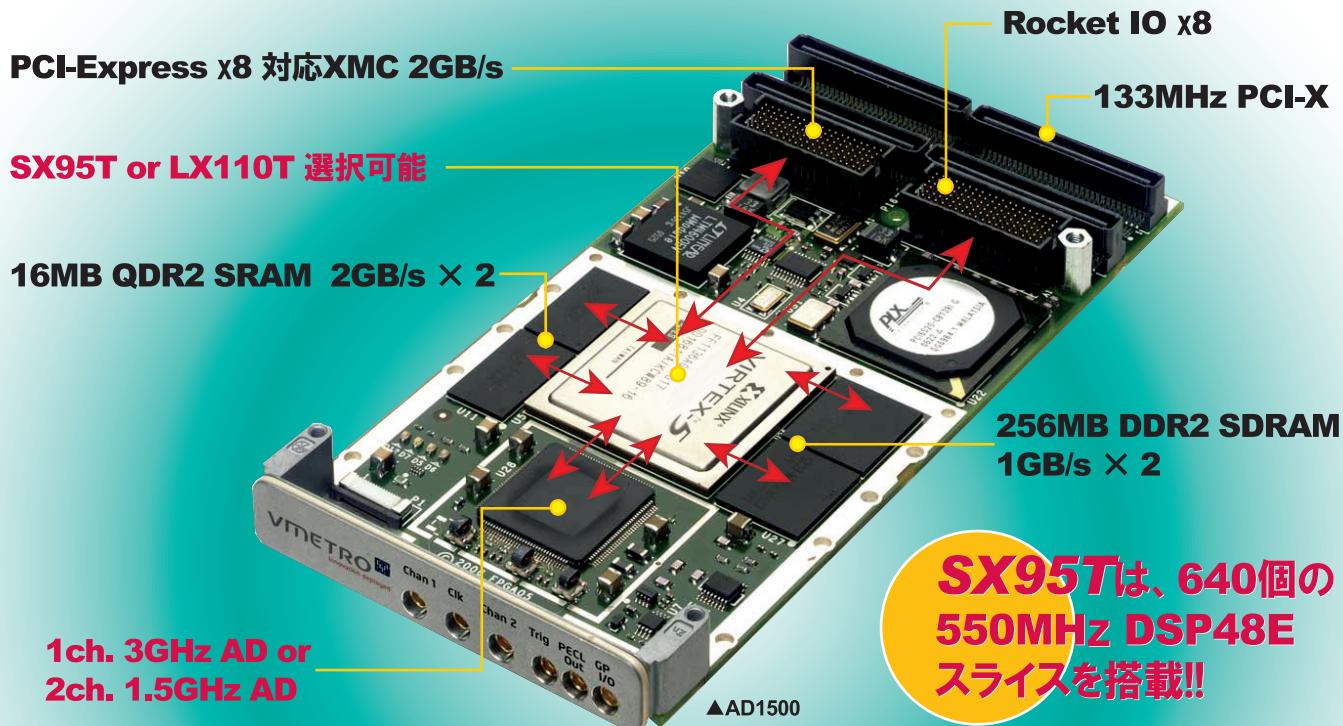

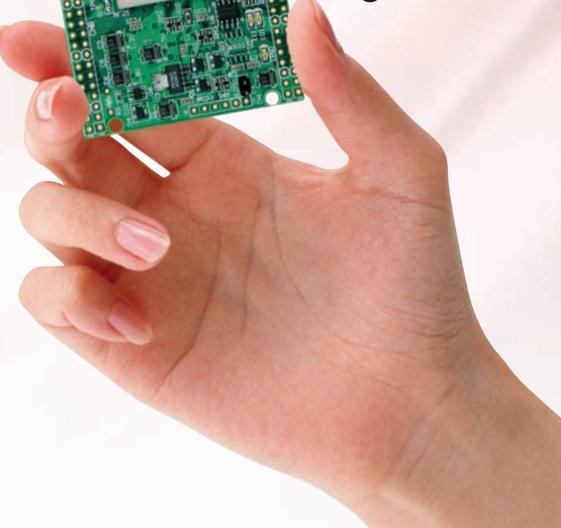

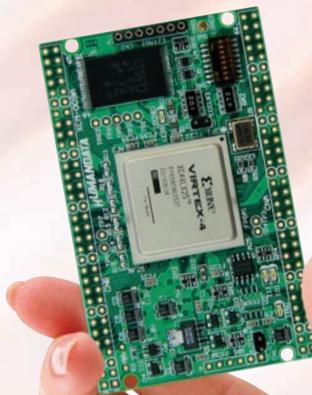

# Xilinx Virtex-5 SX95T搭載 DSP対応FPGAボード

以下のI/Oも対応予定(PMC仕様は発売中)

- 2ch. Mini Cameralink

- 2ch. 14bit 105MHz AD

- 2ch. 14bit 210MHz DA

- LVDS/FPDP/RS422/FC

**V5+C Kit** (別途販売)

C言語による

VHDLコード生成が可能

VHDL開発なしでもA/D使用可能！耐温度・振動等の環境仕様有！

(お問い合わせは)

sales@mish.co.jp

<http://www.mish.co.jp/>

**MISH**

INTERNATIONAL

株式会社ミッシュインターナショナル

TEL 042-538-7650 FAX 042-534-1610

〒190-0004 東京都立川市柏町4-56-1

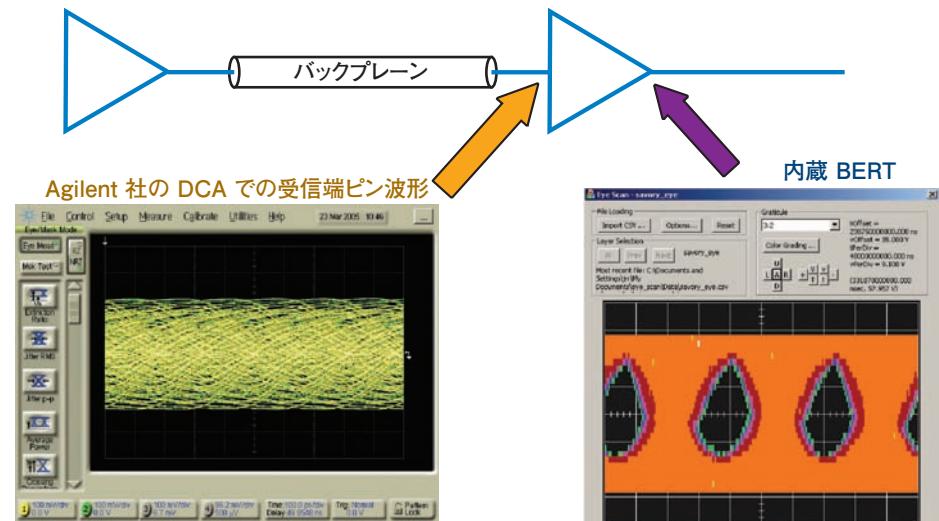

# Automated MGT Serial Link Tuning Ensures Design Margins MGT 高速シリアル リンクを 最適化する方法

ザイリンクス IBERT 測定コアと

Agilent シリアルリンク オプティマイザの併用による

シリアルリンク最適化プロセスの検証

Brad Frieden

Applications Development Engineer

Agilent Technologies

brad\_frieden@agilent.com

FPGA に高速シリアルリンクをインプリメントする際、伝送ラインのシグナルインテグリティの影響を考慮し、対策を講じる必要があります。トランスマッタ プリエンファシスとレシーバ イコライゼーションを併用すれば、チャネルの物理的制約はあるものの、アイダイアグラムを開いて高速シリアルデータの転送レートを向上させることができます。

ザイリンクスの内部ビットエラー テスター (IBERT : Internal Bit Error Ratio Tester) 測定コアを使えば、内部レシーバ ポイントでシリアル信号を見ることができます。また、Agilent 社のシリアルリンク オプティマイザと併用することで、ユニットインターバル全体にわたって BER のグラフィカル ビュ

ーを見られると共に、チャネルを最適化するためプリエンファシスとイコライゼーションの設定を自動調節できます。

本稿では、このプロセスに従って Virtex™-4 MGT 高速シリアルリンクを最適化する方法と、その結果について解説します。

## 信号劣化の課題

3.125Gbps と 6Gbps のデータレート、130ps 以下の立ち上がり時間では、ほとんどのアプリケーションが物理チャネルでシグナルインテグリティに多大な影響を受け、レシーバ入力で信号のひずみが生じます。ひずみはインピーダンスの不連続性に起

因する複数の反射によって起こることがありますが、エッジスピードを遅くするのは、もっと根本的な影響、特に FR4 素材の PCB 誘電体における影響です。周波数に依存する表皮効果はパルスに「スロー テール」を招きます。これを補正するには、伝送パルスにプリエンファシスという時間ドメインのテクニックを適用することで、レシーバ側の波形を大幅に改善できます。

さらに、チャネルはハンド幅に制限があることから、チャネル周波数のロールオフを補正するためレシーバ側にイコライゼーションという周波数ドメインのテクニックを適用できます。チャネルのロールオフと組み合わせれば、ピーク周波数の応答はよりフラット

な応答になります。レシーバ入力側のイコライゼーションは劇的な効果を発揮しますが、これはチップ内の実際のレシーバ入力にしか表われません（イコライゼーション後）。

## リンク性能の測定

リンク性能を検証し、トランスマッタのブリエンファシスとレシーバのイコライゼーションを調節して性能を最適化することは重要です。残念ながら、レシーバが配置されている FPGA のピンで測定した場合、ブリエンファシスだけが適用されたイコライゼーションを適用していない信号を観察することになり、信号に非常に大きなひずみが生じます。

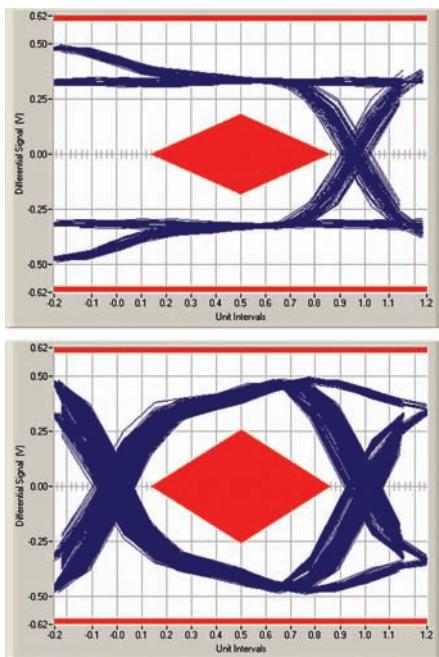

図 1 は、ASIC 技術でインプリメントした 6Gbps チャネルに、Agilent 社のデジタル通信アナライザを用いて測定した例です。チップ内のレシーバ入力には良好な信号があるのに、受信ピン端ではアイ ダイアグラムは完全に閉じて見えることに注目してください。

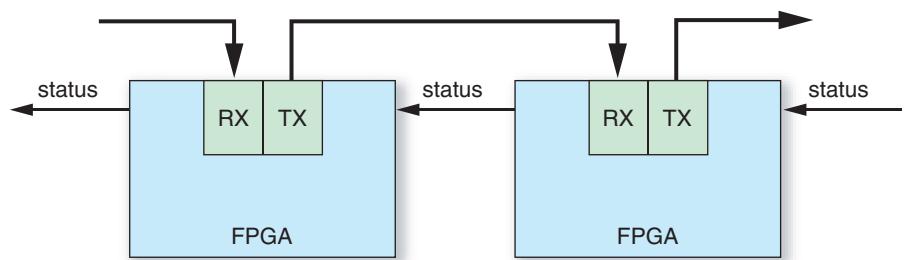

## IBERT 測定コア

ザイリンクスの ChipScope™ Pro Serial I/O ツールキットに用意されている IBERT 測定コアを使うことで、FPGA のレシーバ入力で何が起こっているのかを確認できます。通常の FPGA デザインは、トランスマッタからスティミュラスを与えてレシーバでの BER を測定するデザインに一時的に置き換えられています。これらのスティミュラス/レスポンス コアペアは、デザインにコア生成プロセスを用いて配置されます。これで、チップ内のレシーバで BER を測定できるようになりました。あとはその基本的な測定機能を使い、ブリエンファシスとイコライゼーションをいろいろ組み合わせて適用し、チャネルのレスポンスを最適化します。

## 基本的な BERT 測定

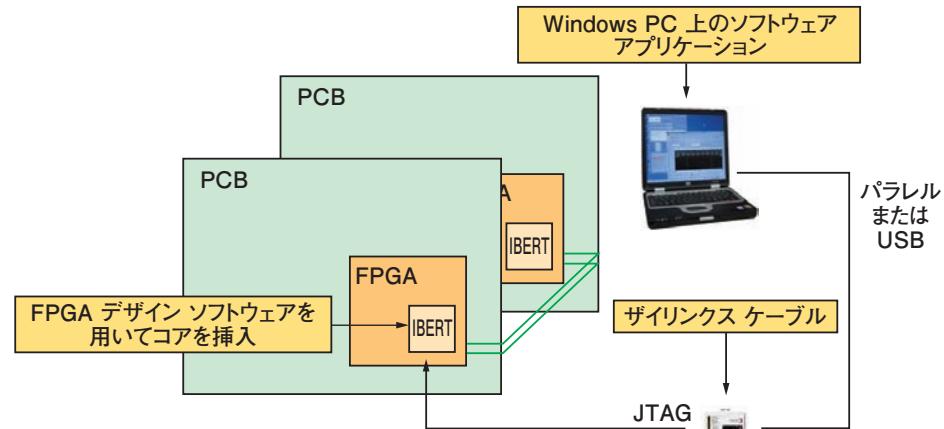

リンク性能を理解するには、ビット エラー レート (BER) を測定できることが条件です。これを測定するには、Agilent 社のシリアル リンク オプティマイザという新しいツールでシリアル リンク内の IBERT コア

スティミュラス/レスポンスを制御します。このようなテストは、図 2 に示す測定システムで行われます。ここでは、2 つの Virtex-4 FPGA がリンクを構成しており、1 つはトランスマッタ、もう 1 つはレシーバをインプリメントします。両方の FPGA はシリアル リンク オプティマイザ ソフトウェアから JTAG の管理下に置かれ、FPGA 内のレシーバ入力ポイントで BER を測定します。

次の測定属性を選択できます。

- ループバック モード（内部、外部、なし）

- テスト パターン タイプ

- ユニット インターバル全体にわたる各ポートの滞留時間

- 手作業でのエラー注入

ここでは、一方のザイリンクス ML405 ボードにある Virtex-4 XC4VFX20 マルチギガビット トランシーバ (MGT) 113A トランスマッタと、もう一方の ML405 ボードにある 2 つめの Virtex-4 XC4VFX20 FPGA 内の MGT 113A レシーバを SATA ケーブルで接続したシリアル リンクで測定しました。1 番目の FPGA とトラン

図 1 FPGA シリアル I/O ピンでの DCA 測定とレシーバ入力でのオンチップ測定

トランスマッタ イコライザ付きトランシーバ

図 2 シリアル リンク オプティマイザのブロック図

スミッタに関連する IBERT コアには USB JTAG で接続し、レシーバに関連する 2 番目の IBERT コアにはパラレル JTAG で接続しました。物理チャネルは、これらのコアと ML405 ボードのトポロジーで決まります。

IBERT コアが既に作成されており FPGA にロードしてあると仮定して、この測定をセットアップするには次のステップに従います。

1. ツールを起動し、TX に対して USB JTAG をコンフィギュレーションし、接続を確認する。

2. RX に対してパラレル JTAG をコンフィギュレーションし、接続を確認する。

3. USB ケーブル上の MGT 113A トランシスミッタを選択する。

4. パラレル ケーブル上の MGT 113A レシーバを選択する。

5. ロープパック（外部）を選択する。

6. テスト パターンのタイプを選択する（PRBS7）。

7. TX と RX のライン レートをセットアップする（リファレンス クロック 150MHz、ライン レート 6Gbps）

8. [BERT] タブを選択し、[Run] をクリックする。

リンク上で測定したところ、1E+12 ビット後にゼロ エラーとなりました（測定時間は ~3 分）。チャネル上の BER 測定はチップ内のレシーバ入力で行い、外部の測定ハードウェアは必要ありませんでした。こうしてシリアル リンク オプティマイザ ツールに追加の機能を用意する基礎が整いました。

## BER のグラフィカル ビュー

リンク性能を理解するための次のステップは、BER をユニット インターバルのファンクションとしてグラフ化する機能を用意することです。グラフを作成するには、Agilent 社のシリアル リンク オプティマイザでシリアル リンク内の IBERT コア スティミュラス/レスポンスを制御します。

測定システムは基本的な BER テストと同じですが、エラーのない性能がどこで達成さ

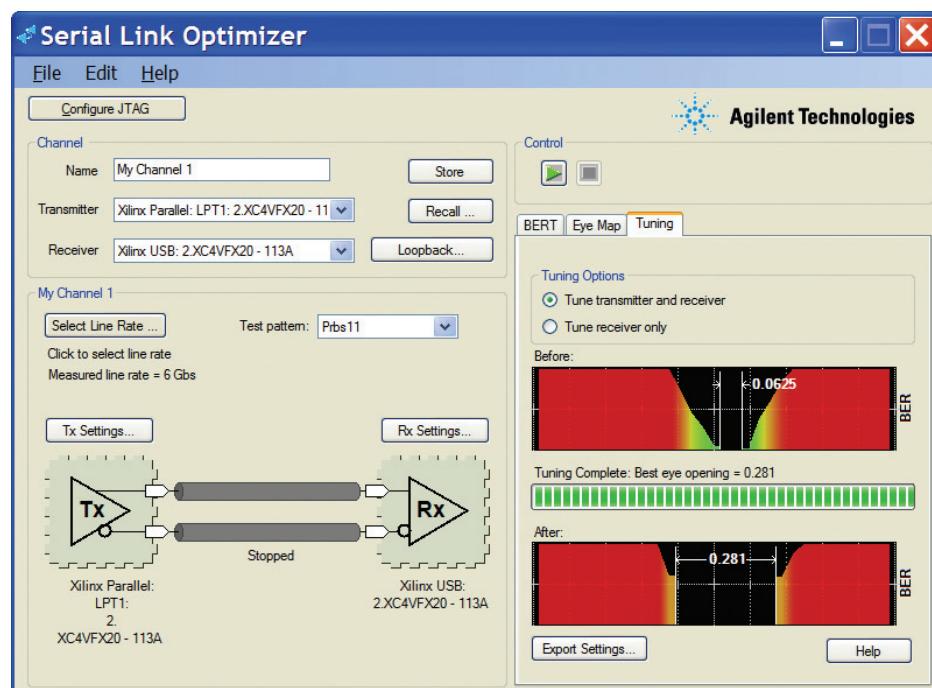

れるかを示すため、ユニット インターバルにおける 32 の各ステップで測定されます。この結果、図 3 の上に示す BER プロットになります。Virtex-4 MGT マクロは、これら 32 の個別ポイントでサンプリング ポジションを調節する機能を備えており、シリアル リンク オプティマイザは IBERT コアとサンプリング ポジションの制御機能を併用して測定を行います。MGT のプリエンファシスとイコライゼーションをデフォルト設定にした場合、リンク性能のゼロ エラーはユニット インターバルの 0.06 (6%) です。これはかなり狭く、ほとんどマージンがありません。このシステムは適切なリンク チューニングを施すことで改善できるはずです。

## リンク チューニングの自動化

次に、ユニット インターバル内のエラー フリー ゾーンが最大化され、スピードとマージンの点から最高のリンク性能が得られるまで、プリエンファシスとイコライゼーションの設定を自動的に組み合わせることで、この測定プロセスをもう一度拡張していきましょう。

シリアル リンク オプティマイザはまさにそのためあります。リンクのコンフィギュレーション オプションとしては、1 個の FPGA の I/O リング内の内部ループバック テスト、1 個の FPGA からの送信と受信、2 個の異なる FPGA 同士での送信/受信ペア テストがあります。また、外部の BERT 装置から信号を注入し、FPGA 内のレシーバでそれら信号をモニタリングすることもできます。

この例では、MGT 113A/B TX/RX ペアを持つ 2 個の Virtex-4 FPGA 間に同じシリアル チャネルを使うことにします。シリアル リンク オプティマイザのインターフェイスで、図 3 のように [Tuning] タブを選択して [Run] ボタンをクリックしてください。デフォルトの FPGA 設定では、エラーフリー ゾーンは 0.06 ユニット インターバルでした。プリエンファシスとイコライゼーションの組み合わせを 141 通り試した結果、図 3 に示すとおり、エラーフリー ゾーンは 0.281 (28%) ユニット インターバルに増加しました。6Gbps のスピードでリンク デザインにおけるマージンが大幅に改善したことになります。

図 3 シリアル リンクをチューニングするためプリエンファシスとイコライゼーションを自動調節する前（上）と後（下）の BER プロット

## リンク デザインの制約をエクスポート

次に、これらプリエンファシスとイコライゼーションの新しい設定値を、最終的にシリアル リンクを使う実際のデザインに取り込む必要があります。これまで、プリエンファシスとイコライゼーションの最適な組み合わせを決めるため、各 FPGA に一時的なテスト デザインを配置しました。最適な組み合わせが決定したため、シリアル リンク オプティマイザは MGT に対応するプリエンファシス/イコライゼーション設定値を出力します。MGT のパラメータは VHDL、Verilog、UCF 形式で表され、[Export Setting] ボタンをクリックすると出力されます。これらのパラメータをソース デザインに再びカット & ペーストすることで、最終的なデザインが FPGA にプログラミングされたときに最適なリンク設定を取り込むことができます。

たとえば、最初のトランシーバに対する

Verilog の設定値は次のようにになります。

```

// Verilog

//— Rocket IO MGT Preemphasis and Equalization —

defparam MGTx.RXAFEEQ = 9'b1111;

defparam MGTx.RXSELDACFIX = 5'b1111;

defparam MGTx.RXSELDACTRAN = 5'b1111;

```

## 結論

FPGA 内のレシーバ入力で BER をモニタリングすると同時にプリエンファシスとイコライゼーションを自動調節することで、MGT ベースのシリアル リンクを自動的に最適化できるようになりました。

3.125Gbps レートでは、こうした最適化は良好なマージンを得るために役立ちます。しかし、6Gbps レートでデータを高い信頼性で転送できるリンク性能を達成するには、最適化が不可欠です。このプロセスは、目的とするデザイン マージンに到達するまでの時間を大幅に短縮し、従来の手作業でのチューニングより優れた結果を得られる可能性が高まります。

詳細は、[www.agilent.com/find/serial\\_io](http://www.agilent.com/find/serial_io) または [www.agilent.com/find/xilinxfpga](http://www.agilent.com/find/xilinxfpga) をご覧ください。

## 必要なコンポーネント

これらの測定値を利用するには、次のコンポーネントが必要です。

1. Windows XP SP2 以上の PC

2. ザイリンクスのプログラミング ケーブル (パラレルまたは USB、もしくはその両方)

3. ザイリンクスのChipScope Pro Serial I/O ツールキット (IBERT コア用)

4. Agilent 社の E5910A シリアル リンク オプティマイザ ソフトウェア

# ザイリンクストレーニング スケジュール [4~5月]

2~3 月のスケジュールは 10 ページをご覧ください。

| コース名                                    | 日 程 |                     | 主 催     | 開 催 地 |

|-----------------------------------------|-----|---------------------|---------|-------|

| FPGA 設計実践                               | 4 月 | 8 日 (火) ~ 9 日 (水)   | ザイリンクス  | 東京会場  |

|                                         |     | 23 日 (水) ~ 24 日 (木) | ザイリンクス  | 東京会場  |

|                                         | 5 月 | 8 日 (木) ~ 9 日 (金)   | ザイリンクス  | 東京会場  |

|                                         |     | 15 日 (木) ~ 16 日 (金) | 菱洋エレクトロ | 大阪会場  |

|                                         | 5 月 | 21 日 (水) ~ 22 日 (木) | ザイリンクス  | 東京会場  |

|                                         |     |                     |         |       |

| アドバンスド FPGA 設計                          | 4 月 | 10 日 (木) ~ 11 日 (金) | ザイリンクス  | 東京会場  |

|                                         | 5 月 | 26 日 (月) ~ 27 日 (火) | ザイリンクス  | 東京会場  |

| Virtex-5 LX および LXT デザイン                | 4 月 | 11 日 (金)            | ザイリンクス  | 東京会場  |

|                                         | 5 月 | 13 日 (火)            | ザイリンクス  | 東京会場  |

| エンベデッド システム開発                           | 4 月 | 15 日 (火) ~ 16 日 (水) | ザイリンクス  | 東京会場  |

|                                         | 5 月 | 8 日 (木) ~ 9 日 (金)   | ザイリンクス  | 東京会場  |

| アドバンスド エンベデッド システム開発                    | 4 月 | 24 日 (木) ~ 25 日 (金) | ザイリンクス  | 東京会場  |

|                                         | 5 月 | 29 日 (木) ~ 30 日 (金) | ザイリンクス  | 東京会場  |

| System Generator for DSP を使用した DSP デザイン | 4 月 | 22 日 (火) ~ 23 日 (水) | 新光商事    | 大阪会場  |

|                                         | 5 月 | 20 日 (火) ~ 21 日 (水) | ザイリンクス  | 東京会場  |

| MGTシリアル I/O デザイン                        | 4 月 | 22 日 (火) ~ 23 日 (水) | ザイリンクス  | 東京会場  |

|                                         | 5 月 | 22 日 (木) ~ 23 日 (金) | ザイリンクス  | 東京会場  |

| PCI Express システム <b>New</b>             | 5 月 | 12 日 (月) ~ 13 日 (火) | ザイリンクス  | 東京会場  |

\*すべてのトレーニングは、ザイリンクス認定インストラクターによるオフィシャル トレーニングです。

\*日程および会場は、都合により変更となる場合もございます。最新情報はザイリンクス トレーニング Web サイトをご覧ください。

詳細とご登録はこちらから ►► <http://japan.xilinx.com/support/education-home.htm>

# A High-Speed Serial Connectivity Solution with Aurora IP

## Aurora IP を用いた 高速シリアル コネクティビティ ソリューション

ポイント ツー ポイントの接続を要求するアプリケーション向けの

ハイスケーラビリティ プロトコル Aurora の活用法

Mrinal J. Sarmah

Hardware Design Engineer

Xilinx, Inc.

mrinal.sarmah@xilinx.com

Hemanth Puttashamaiah

Hardware Design Engineer

Xilinx, Inc.

hemanth.puttashamaiah@xilinx.com

通信技術の進歩に伴い、データ インテグリティを犠牲にすることなく、シリアル リンクでギガヘルツ単位のデータ転送率を達成できるようになりました。シリアル コネクティビティは、パラレル通信と比べて次の点が優れているため広く普及しました。

- ・システム スケーラビリティの向上

- ・柔軟な薄型ケーブル

- ・最小限の追加リソースで回線上のスループットを向上

- ・より確定的な障害の切り離し

- ・予想しやすく信頼性の高いシグナリングスキーム

- ・ユーザーのニーズに合わせてスケーリング可能なトポロジー

- ・スキーに対する免疫性が非常に高く、ピ

ンあたりのバンド幅が高い

- ・フォーム ファクタが小さく、PCB トレースとレイヤ、ピン/ワイヤの数が低減されることによるシステム コストの削減

シリアル I/O には多くの利点がある半面、マイナス面もあります。シリアル インターフェイスは、チップ内における高バンド幅の管理や、特別な初期化とモニタリング、複数レーンの集合チャネルにおけるレーン ボンディング（結合）、データ アライメントのためのエラスティック バッファ、そしてデスキーを必要とします。また、フロー制御が複雑であり、高レベルな機能と総チップ エリアの適切なバランスを保つ必要があります。

### マルチギガビット トランシーバ

業界全体がパラレル インターフェイスからシリアル インターフェイスに移行した後、ザイリンクスは 6.5Gbps という高バンド幅の要件を満たすため、マルチギガビット トランシーバ (MGT) を発表しました。

MGT に共通するファンクション ブロックとして、8B/10B エンコーダ/デコーダ、伝送バッファ、SERDES、受信バッファ、同期消失有限ステート マシン (FSM)、カンマ検出、チャネル結合ロジックがあります。これらのトランシーバは、ギガヘルツ レートで実行

できるクロック データ リカバリ (CDR) 回路を内蔵しています。また、内蔵のフェイズ ロック ループ (PLL) は、ファブリックとトランシーバのクロックを生成します。

トランシーバには次の利点があります。

- ・自己同期型のタイミング モデルを採用しているため、ボード上のトレースを削減し、クロック-データ スキューを排除します。

- ・複数の MGT を使用することによりさらに高いバンド幅を達成できます。

- ・複数の MGT をポイント ツー ポイントで接続することで、スイッチド ファブリック アーキテクチャが実現できます。

- ・MGT に用意されているエラスティック バッファは、チャネル結合レーンに対し高いスキー トランクスを提供します。

MGT は、複数のプロトコルに対するサポートをコンフィギュレーションできることから、コントロールが非常に複雑です。MGT を用いて高速コネクティビティ ソリューションをデザインしたり、それらソリューションにデザインを統合するときは、MGT の初期化、アライメント、チャネル結合、アイドル シーケンス生成、リンク管理、データ デリニエーション (delineation : 輪郭の決定)、クロック スキー、クロック補正、エ

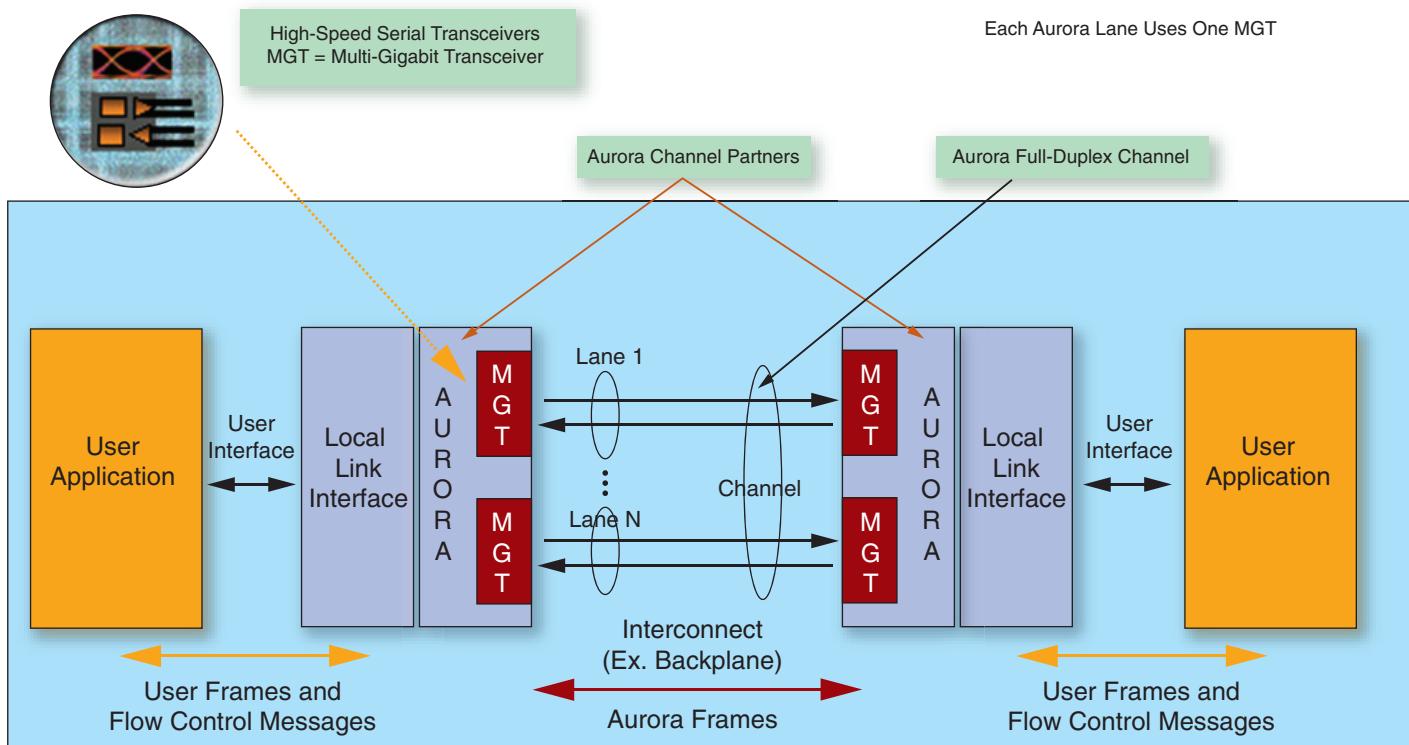

図 1 Aurora を使用するコネクティビティ シナリオ

ラー検出、データストライピング/デストライピングを考慮する必要があります。特定のアプリケーション向けにトランシーバをコンフィギュレーションするには、200 以上の属性をチューニングする必要があります。それは決して容易な作業ではありません。

## Aurora ソリューション

ザイリンクスの Aurora プロトコルとその関連デザインは、MGT のコントロールインターフェイスを管理することでこれらの課題を解消します。Aurora は、コンパクトでスケーラブル、カスタマイズ可能な無償のプロトコルです。また、低いオーバヘッドにより、プロトコルにとらわれない軽量リンク レイヤ プロトコルとしてどのようなシリコン デバイス/テクノロジにでもインプリメント可能です。

Aurora を使用すると、1 つ以上の MGT を接続して通信チャネルを構成できます。Aurora プロトコルは、データ パケットの構造に加え、フロー制御やデータストライピング、エラー処理、さらに MGT リ

図 2 シンプレックスのトーカン リング構造

ンクを有効にするための初期化のプロシージャを定義します。

Aurora は、MGT への透過的なインターフェイスを提供することで MGT をシールドクラップし、プロプライエタリなプロトコルや、イーサネットまたは TCP/IP などの業界標準プロトコルの上位レイヤをそのインターフェイス上に置くことで、容易にアクセスできるようにします。

この使いやすい定義済みプロトコルは、既存のユーザー デザインにすぐに統合できます。軽量な Aurora はアドレス指定方式を持たず、スイッチングをサポートしません。また、

データペイロード内の訂正を定義しません。

Aurora は、Open Systems Interconnection (OSI) モデルにおける物理レイヤとデータリンク レイヤに対して定義され、既存のネットワークに簡単に統合できます。

## 代表的なコネクティビティ シナリオ

図 1 は、代表的な Aurora アプリケーションの概略図です。Aurora インターフェイスは、ユーザーインターフェイスを通してユーザー アプリケーション ファンクション

図 3 Aurora におけるデータフロー

図 4 伝送側 Aurora におけるフレームのカプセル化

との間でデータをやり取りします。ユーザーインターフェイスは Aurora プロトコルの仕様に含まれていません。

Aurora プロトコル エンジンは、任意の長さのジェネリック データをザイリンクスの LocalLink ユーザー インターフェイスから Aurora プロトコルで定義されたフレームへと変換し、1 本以上の高速シリアルリンクからなるチャネル パートナー全体に転送します。チャネル パートナー間のリンク

ク数はコンフィギュブルであり、デバイスに依存します。

ザイリンクスのほとんどの IP は従来の LocalLink インターフェイスをベースに開発されています。また、LocalLink をベースとする他の IP 向けにデザインされたユーザー インターフェイスは、Aurora に直接プラグインできます。LocalLink インターフェイスの詳細は、[http://japan.xilinx.com/products/design\\_resources/conn](http://japan.xilinx.com/products/design_resources/conn)

central/locallink\_member/sp006.pdf

をご覧ください。

Aurora は、LocalLink インターフェイスと MGT を橋渡しするプロトコルと考えればよいでしょう。

Aurora の LocalLink インターフェイスは、2 バイトまたは 4 バイトのデータに対してカスタマイズ可能です。2 バイトと 4 バイトのどちらのインターフェイスを選ぶかは、必要とするスループットとレイテンシを基準に判断します。4 バイトのデザインは 2 バイトのデザインよりレイテンシこそ長いものの、2 バイトと比較してスループットは高く、消費するリソースも少なくて済みます。Aurora チャネルは单方向（シンプレックス）または双方向（全二重）として機能できます。全二重のモジュール初期化データはリバース パスを通してチャネル パートナーから届き、シンプレックスの場合、初期化は 4 つのサイドバンド信号を通して行われます。Aurora は、シンプレックス TX のみ、RX のみ、もしくはその両方で利用できます。「両方」での動作は、伝送側と受信側が独立して通信することを除けば、全二重とほぼ同じです。Aurora のシンプレックスはトークンリングのように使用できます。図 2 に、Aurora-S（シンプレックス）のリング構造を示します。

## Aurora のデータ フロー

データは Aurora のチャネル パートナー間をフレームとして転送されます。データ フローの主な内訳は、ユーザー アプリケーションと Aurora インターフェイス間でのプロトコル データ ユニット (PDU) の転送、ならびにチャネル パートナー間でのチャネル PDU の転送です。

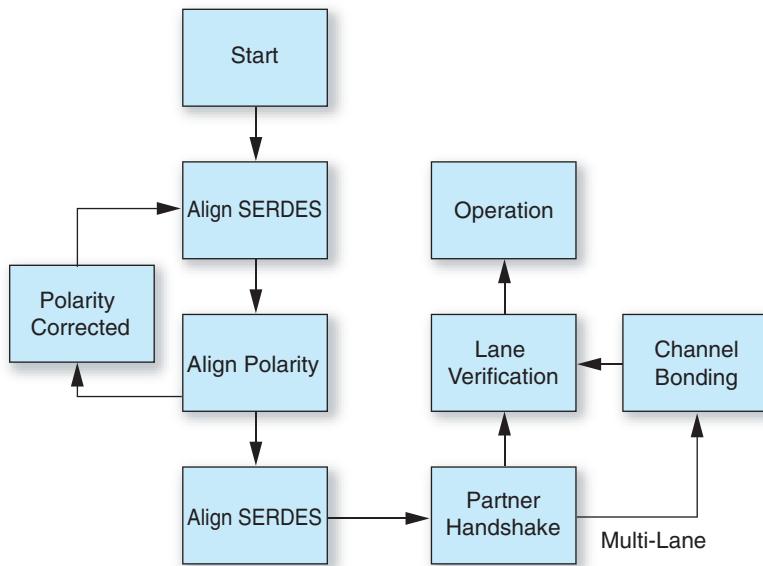

起動後まもなくしてコアがすべてリセット状態から出ると、トランスマッタは初期化シーケンスを送ります。リンクが良好で、リンク パートナーがこれらのパターンを認識した場合、そのリンクはアクノリッジメント パターンを送信します。十分なアクノリッジメント パターンを受信したら、トランスマッタはリンクアップ状態に遷移し、チャネル パターン間の各トランシーバが正しく接続され

図 5 Aurora での NFC オペレーション

たことを知らせます。リンクが立ち上がると、Aurora プロトコル エンジンは、シングル レーン チャネルの場合はチャネル検証段階、またマルチレーン チャネルの場合はチャネル結合段階（検証段階の前）に進みます。チャネルの検証が完了したら、Aurora はチャネルアップ信号を送り、その後実際のデータ伝送が始まります。リンク初期化プロセスは図 3 のとおりです。

#### フレームの種類

前述のとおり、データは Aurora のチャネルをフレームとして送信されます。次に、5 種類のフレームを優先順位別にリストします。

- クロック補正 (CC)

- 初期化シーケンス

- ネイティブ フロー制御 (NFC)

- ユーザー フロー制御 (UFC)

- チャネル PDU

- アイドル

Aurora を使えば、チャネル パートナーが定期的に CC シーケンス挿入することで別々のリファレンス クロックを使用できるようになります。

また、トランシッタとレシーバ間で、最高 200 ppm (parts per million) の差動クロック レートまで対応できます。

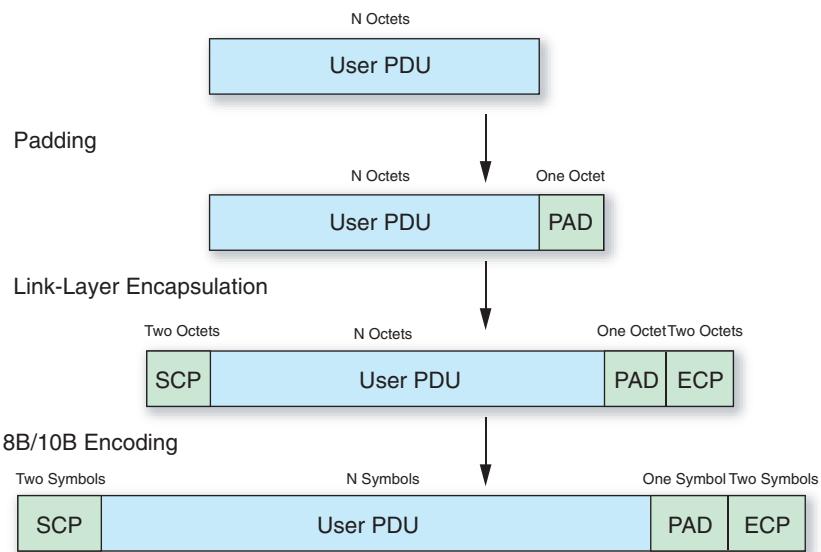

Aurora のフレームは、シンボルという 2 バイト単位でデータを送信します。PDU 内のバイト数が奇数の場合、パッドという追加バイトが付加されます。データは、受信側でパッドが受信ロジックによって除去された後、LocalLink インターフェイスに送信されます。

LocalLink の伝送フレームは、図 4 に示すように、Aurora フレームにカプセル化されます。Aurora は、スタート チャネル PDU (SCP) とエンドチャネル PDU (ECP) シンボルを用いてフレームをカプセル化します。受信側では、これとは逆のプロセスが行われます。フレームの 8B/10B キャラクタへのエンコーディング/デコーディング、シリアル化/デシリアル化、そしてデータ消去を防ぐため、オプションのフロー制御

御メカニズムをサポートしています（図 5）。

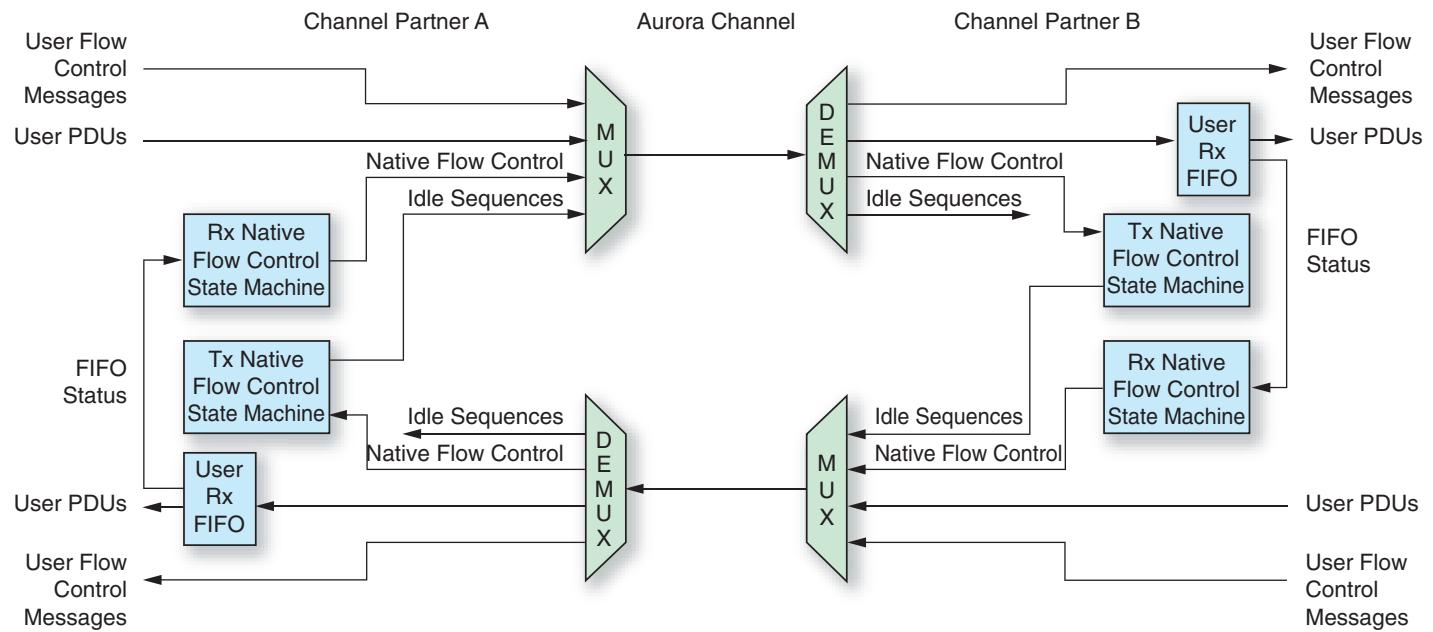

#### ネイティブ フロー制御

NFC とは、データリンクのレイヤーを制御するという意味です。NFC の動作は、RX と TX という 2 つの NFC FSM によって管理されます。

RX NFC FSM は RX FIFO の状態をモニタリングします。オーバーフローのリスクがある場合、NFC PDU を生成し、チャネル パートナーに一定時間、ユーザー PDU の伝送を中断するよう要求します。TX NFC ステート マシンは、RX FIFO がオーバーフロー状態から抜け出すまで、要求された時間待機します。

NFC の要求を送っている間、TX NFC FSM はラウンドトリップ遅延を除去しなければなりません。NFC の要求は、この遅延を考慮に入れ、受信 FIFO がオーバーフローする前に送られるのが理想的です。NFC のポーズ (pause) 値は 0~256 にプログラミングでき、最大値は無限です。NFC のポーズ値は累積的ではなく、新たな NFC が要求されると、その値が古い値をオーバーライドします。

#### フロー制御

Aurora は、チャネル パートナー間のソース レートとシンク レートの違いによるデータ消失を防ぐため、オプションのフロー制

図 6 各種 Aurora に対する性能曲線

NFC の要求には、即時モードと完了モードの 2 通りのタイプがあります。即時モードの場合、NFC の要求は優先度の低い要求が停止されている間に処理されます。完了モードの場合は、先に現在のフレームが伝送され、NFC の要求が処理されるのはその転送が完了した後です。

#### ユーザー フロー制御

UFC は任意のレイヤでユーザー定義のフロー制御をインプリメントするために使われます。UFC メッセージの数は、1 つのフレームあたり 2~16 バイトまでです。UFC メッセージはユーザー アプリケーションによって生成、解釈されます。

#### アプリケーション

Aurora はシリアル I/O 用のシンプルでスケーラブルなオープン プロトコルであり、FPGA または ASIC にインプリメントできます。このプロトコルは、リソースをほとんど消費せずに安価で高性能なリンク レイヤを必要とするアプリケーションに適しており、MGT プロトコルの独自開発を検討しているユーザーにとって、作業時間の大幅な短縮になります。

Aurora には、次のようなさまざまなアプリケーションがあります。

- ・ビデオ

- ・医療

- ・バックプレーン

- ・ブリッジング

- ・チップ間およびボード間の通信

- ・複数の FPGA 間での機能の分割

- ・シンプレックス通信

Aurora は、より少ないリソースで高いスループットを提供します。また、顧客のニーズに応じて、Aurora 上に追加のファンクションを用意できます。シンプレックス通信では、ユーザーが単方向で高いスループットを要求する場合に、最小限のリソースで最大の柔軟性を達成できます。シンプレックスは、ストリーミングビデオなど、非データ通信に理想的です。

#### パフォーマンス統計

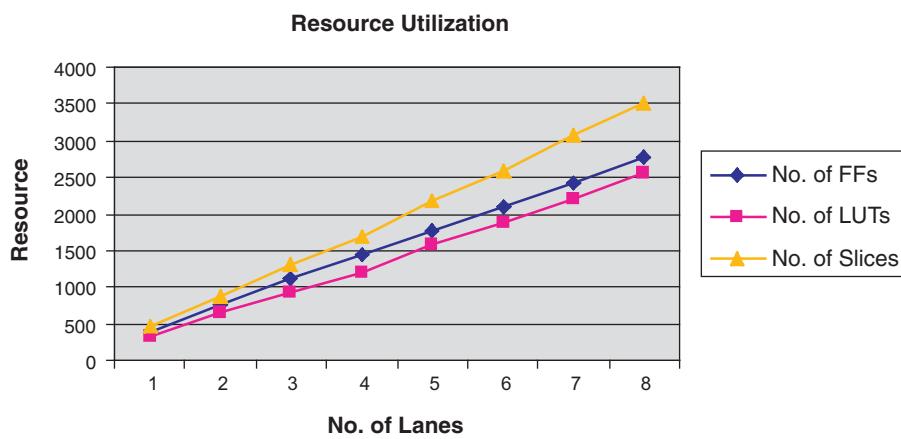

Aurora は FPGA リソースを最小限に抑えるようにデザインされています。シングルレーンの 2 バイト フレーミング デザインは、約 383 のルックアップ テーブルと 374 のフリップフロップを消費します。図 6 の曲線は、Virtex™-5 LXT デバイスにおける、各レーン コンフィギュレーションに対するリソース利用率を表しています。

シングルレーンの 2 バイト デザインに対するレイテンシは 10 サイクルです。トランシーバは固有のレイテンシを挿入します。したがって、RocketIO™ GTP トラン

シーバにおける Aurora デザインの総レイテンシは約 29 サイクルとなります。

リファレンス クロックは幅広い範囲から自由に選択できます。総スループットは、リファレンス クロックの値と、選択したライン レートで決まります。

#### Aurora : CORE Generator IP

Aurora は CORE Generator™ ソフトウェアの一部としてリリースされており、約 10 のコンフィギュurable パラメータを備えています。Aurora コアは、ストリーミング／フレーミング インターフェイス、シンプレックス／全二重データ フロー、シングル／マルチ MGT、リファレンス クロック値、ライン レート、選択した MGT の数に基づく MGT ロケーション、およびリファレンス クロック ソースを選択することでコンフィギュレーションできます。ライン レートは、選択した Virtex デバイスに応じて 0.1~6.5Gbps までの範囲でサポートされます。Aurora コアには MTI、NC-SIM、VCS シミュレータをサポートするシミュレーション スクリプトと、デザインの合成およびビット生成を容易にするビルト スクリプトが用意されています。

#### 結論

Aurora は非常に使いやすく、レガシープロトコルのトランスポートとプロプライエタリ プロトコルのインプリメンテーションに十分な効率、スケーラビリティ、融通性を備えた IP です。また、Aurora には下位互換性があり、Virtex-5 デバイスの Aurora デザインから Virtex-4 デバイスの Aurora デザインにトーカーできるなど、IP がその土台である MGT 技術から独立しています。ザイリンクスの IP とソフトウェア ツールを使えば、Aurora の改善された機能セットを活用できます。将来的には、リンクの信頼性を高めるパケット リトライ機能を提供するため、現在研究を進めています。

詳細は、<http://japan.xilinx.com/aurora> をご覧ください。

# Xilinx FPGAs Adapt to Ever-Changing Broadcast Video Landscape

# 変化し続ける ビデオ放送シーンに対応する ザイリンクス FPGA

新しいデジタル放送のスタンダードを具現化するザイリンクス FPGA の

先進シリコン技術とソフトウェア、無償リファレンス デザイン

Tim Hemken

Marketing Director

Xilinx, Inc.

themken@xilinx.com

Motion Picture and Television Engineers) により策定され、1989 年に商用化された SMPTE 259M です。この規格が登場した当時、SDI に採用されていたチップは主に ASSP (特定用途向け汎用 IC) のチップメーカーによって製造されていました。SDI のデータレートは名目 270Mbps で、標準品位テレビ (SDTV) の解像度には十分でした。

2002 年、ザイリンクスは Virtex™-II Pro FPGA を発表しました。このデバイスは、最高 3.125Gbps の高速なビットレートで動作するマルチギガビット トランシーバ (MGT) を搭載していました。同じ頃、放送業界ではより高い解像度と高速なデータレートを必要とする新たな高品位テレビ (HDTV) の規格が採用され始めました。これに対応するため、SMPTE は SMPTE 292M という規格を作り、名目 1.5Gbps のデータレートで非圧縮 HDTV ビデオコンテンツをシリアル伝送するインターフェイス、HD-SDI をサポートしました。

ザイリンクスの技術者である John Snow は、1 つの Virtex™-II Pro MGT で 2 通りのデータレートをサポートできないかと考え、複数の ASSP チップ機能を 1 つのザイリンクス FPGA に統合する可能性を模索しました。統合することにより、特に複数のビデオ ストリームが存在するビデオスイッチャとマスター コントローラのデザインにおいて、これらインターフェイスのコス

同軸伝送ケーブルのインフラ設備を全面的に入れ替えることなく、アナログ音声/ビデオをデジタル音声/ビデオに変換したいという放送業界の要望に応えるため、非圧縮の標準画質ビデオを伝送するシリアル デジタルインターフェイス (SDI) プロトコルが発達し

てきました。そして今日、解像度とデータレートがいっそう向上したことから、同軸ケーブルの再使用という同じ目標を持つ新たなシリアルデータ通信方式が生まれました。

SDI に対する最初の規格は、米国映画テレビ技術者協会 (SMPTE : Society of

トを大幅に削減できるからです。

Snow は、FPGA を用いたこれら 2 つのインターフェイス規格に関する初のアプリケーション ノートを作成しました。アプリケーション ノートは、Verilog と VHDL ソースコードで書かれた無料のリファレンス デザインも提供していました。これにより、コードやドキュメンテーションを参考しながら、完全な機能の SDI と HD-SDI レシーバ／トランシミッタ、またビデオ テスト パターン ジェネレータなどの関連ファンクションを Virtex-II Pro FPGA にインプリメントすることが可能になりました。その翌年、Virtex-II Pro FPGA は複数の ASSP チップ 機能を統合し、世界中の放送機器に採用されるようになりました。

HDTV はその後も普及し、この優れた技術によって視聴者はよりリアルな画像を楽しめるようになり、高画質コンテンツの量は増

える一方です。今日、HD 対応受信機は十分普及できる価格まで下がり、HDTV の売れ行きに拍車がかかっています。マルチレートの SDI および HD-SDI リファレンス デザインは、放送業界においてデジタル オーディオ／ビデオ コンテンツを配信するためのますます重要な存在になりつつあります。

SMPTE は、現状に留まることなく、より高いバンド幅を必要とするビデオ フォーマットを扱うための新規格を発表し続けています。最新規格の デュアルリンク HD-SDI (SMPTE 372M) と 3G-SDI (SMPTE 424M および SMPTE 425M) は、いずれも 3Gbps の総バンド幅を必要とします。

デュアルリンク HD-SDI 規格は、より豊かな色彩（ピクセルのカラー データ量の増加）や、より高速なアップデート レート（30Hz のフレーム レートではなく 60Hz のプログレッシブ フレーム レートで 1,080 ライン）を実

現するため、HD-SDI レートのリンクを 2 本組み合わせて使用します。デュアルリンク HD-SDI インターフェイスを形成する 2 本の同軸ケーブルは、3G-SDI を用いて 1 本の同軸ケーブルに置き換えることができます。

データレートの向上を必要としているアプリケーションの例としては、現在デジタル データに移行中の映画産業があります。デジタル シネマの規格は、一般に HDTV フォーマットに使われているビデオ サンプルあたり 20 ビットのデータではなく、36 ビットのデータを使用します。ビデオ サンプルあたりのビット数の増加に加え、解像度も高まるから、3Gbps のデジタル インターフェイスに対する市場ニーズが生まれています。

1 つの SMPTE 規格でも、FPGA の将来性を実感できます。3G-SDI は実際には SMPTE 424M と SMPTE 425M の 2 つの規格によって定義されています。SMPTE 424M はシリアル インターフェイス自体の物理的、電気的特性を定義し、SMPTE 425M はインターフェイスにさまざまなビデオ フォーマットをマッピングする方法を定義しています。SMPTE 425M は 2006 年に発表されたばかりですが、SMPTE は追加のビデオ フォーマットに対応するため、早くも改訂作業に着手しています。

また、SMPTE はすでに 10Gbps で動作するインターフェイスを定義済みであり、現在はさらに高速なインターフェイスを検討中です。これらのインターフェイスをザイリンクスの FPGA でデザインすれば、出荷開始直前でも突然の規格変更によるビデオ機器が陳腐化するリスクを排除できるのです。

ビデオ コネクティビティに HD-SDI を使う最近のアプリケーションをいくつか紹介しましょう。

## CCD カメラ

薄暗い環境でも滑らかなスローモーションビデオを鮮明に記録できる超高速、高感度の放送用カメラは、プロ野球のナイター戦などを撮影するのに非常に便利です。CCD カメラは、ボールがバットに当たる瞬間など、肉眼でははっきり認識できない高速な瞬間をとらえることができます。撮影したビデオをス

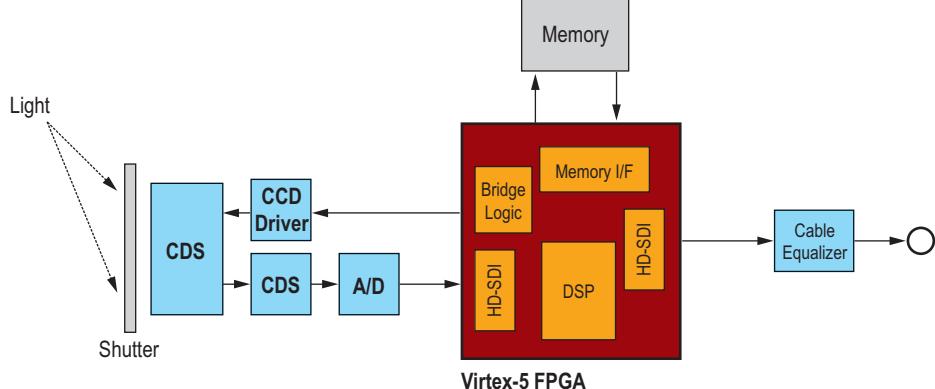

図 1 CCD カメラ

図 2 Video over IP

ローモーションで再生すれば、従来見られなかった貴重なシーンを確認できるのです。

図 1 の CCD (電荷結合素子) カメラは、信号合成処理と色処理を実行すると共に、CCD ドライバへのインターフェイスを取るため、FPGA を使用しています。CCD ドライバは、CCD と機械式のシャッターリード・トライガ制御を駆動します。入力のビデオ信号はアナログ-デジタル コンバータによりデジタル フォーマットに変換され、その後外付けメモリに格納されます。フレーム全体に対するデータ転送が完了すると、そのメモリからのデータは FPGA により合成され、HD-SDI を用いてネットワーク上へ送信されます。トライガから HD-SDI 出力に必要な処理時間は 1 秒以下です。また、FPGA はメモリと ADC も制御します。

## Video over IP

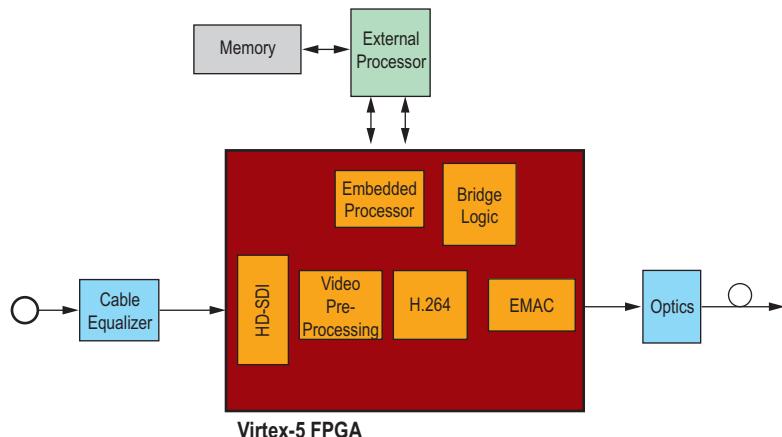

一部のビデオ制作センタでは、ネットワークを介して鮮明な HD ストリームを伝送するため、イーサネットを使い始めています。画像は、低レイテンシで画質をリアルタイムに改善するため前処理／後処理が施され、さまざまなエンコーディング／デコーディング規格（コーデック）を用いてネットワークで転送されます。ストリームのサイズとレートが非常に高いことから、データを圧縮する必要があります。たとえば、30fps で 1920 X 1080 ピクセルを伝送するには、非圧縮で 1.5Gbps のデータレートが必要です。これに複数チャネルを加えれば、データレー

トはさらに高くなります。

エンベデッド DSP ブロック、オンチップとオフチップ メモリ、ブリッジング ファンクションを構築するための豊富なロジック、そしてイーサネットと HD-SDI コネクティビティを備える、アプリケーションに最適化された FPGA は、こうしたシステムを構築するのに理想的なソリューションです。図 2 は、Video over IP システムのブロック図です。FPGA は HD-SDI リンクを介してデータを読み取り、そのデータを処理します。データの圧縮には、H.264 などのコーデックが使われます。データはその後、受信側でデコードするため所定のヘッダ情報といっしょにイーサネット パケットに変換され、最終的に MAC を用いてイーサネット リンクを介して送信されます。

## HDTV 画質モニタ

従来、消費者は DVD でしか高品質な画像と多重音声を楽しむことができませんでした。高画質テレビが一般化したこと、DVD に匹敵する画質を得られるようになりました。この結果、視聴者の間で HDTV の画質に対する意識が高まりました。今後は画質がサービス プロバイダを差別化する大きな要因になるでしょう。現在は、画質を客観的、主観的にテストすると共に、明らかなエラーを測定するための画質モニタが必要とされています。

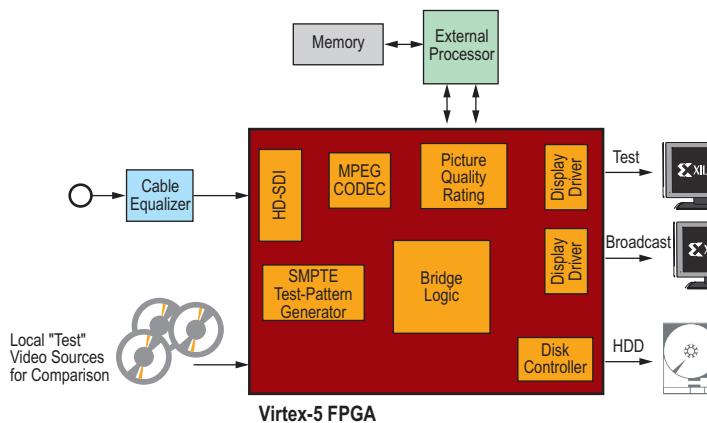

図 3 に、ザイリンクスの Virtex-5 FPGA にインプリメントされている画質モニタを示

します。客観的テストは、SMPTE RP 198 によって定義されている一般的なテストパターン フォーマットを使って実行されます。主観的テストは、放送後の画質をローカルなテスト ビデオ ソースと比較して行われます。FPGA は各ソースからデータを収集し、前処理（プリプロセッシング）したうえで、解析のため外部プロセッサに送ります。

## リアルタイム HD AVC

アドバンスド ビデオ コーディング (AVC : Advanced Video Coding) は、ビデオ伝送に必要なビットレートの半分で伝送が可能なビデオ圧縮技術です。AVC は当初、標準品のビデオに使われていましたが、HD のサービス プロバイダにとっても魅力的なソリューションです。AVC はモーション補正による予測プロセスを大幅に改善することで、MPEG-2 と比較して非常に大きなゲインを達成しています。AVC はモーション予測の精度を 2 倍にし、オブジェクトをより正確に追跡するため比較的小さなブロック サイズを使うと共に、モーションと予測の適切なマッチを探すため多数のリファレンスフレームを持ちます。このため、リアルタイムの高品位 AVC ビデオ エンコーダは、MPEG-2 の半分のバンド幅で放送品質の画像を提供できるのです。

FPGA は、図 4 に示すように、膨大な演算を必要とするモーション エスティメーションを実行します。モーション エスティメーションは差分絶対値の総和を反復することで実行さ

図 3 HDTV 画質モニタ

図 4 リアルタイム HD AVC

れます。データは何度も繰り返し比較され、多くの演算は再使用されます。CPU ベースのインプリメンテーションでは、キャッシュから算術論理ユニットへのデータ伝送で不可が大きくなる傾向があり、FPGA デザインはカスタム レジスタ パイプライン内のすべての値を保持するようにカスタマイズ可能です。

結論

## Virtex-5 FPGA をはじめとするザイリンク

この最新デバイスは、膨大な量のロジックを持ち、ASIC に匹敵するパフォーマンスを提供します。FPGA は、放送機器の設計者が求めるあらゆる機能を備えているのです。

- SDI、HD-SDI、デュアルリンク HD-SDI、3G-SDI、DVB-ASI、AES デジタル オーディオ、イーサネット、PCI Express など、複数の規格をサポートする 3.2Gbps の低消費電力エンベデッドトランシーバ

- ・ 高速 DSP ブロック

- ・ エンベデッド プロセッサ

- ・ イーサネット MAC

- ・ PCI Express コア

- ・ 多数のビデオ IP コア

ザイリンクスのシリコン製品を用いてビデオ コネクティビティ アプリケーションをデザインすることで、放送機器のメーカーはコスト削減や、自社製品の差別化、規格の変化に伴うリスク低減を実現できます。

# ザイリンクス販売代理店オリジナル トレーニング

東京エレクトロンデバイス <http://ppg.teldevice.co.jp/>

\* 3月以降開催のトレーニングスケジュールはWebにてご確認ください。

| コース名                                      | 開催日                           | 開催地               |

|-------------------------------------------|-------------------------------|-------------------|

| FPGA 設計導入コース (ISE コース)                    | 2/21(木)<br>2/22(金)            | 横浜／立川<br>大 阪      |

| 初めてでも使える! Spartan-3 (Virtex-II) 設計コース     | 2/19(火)                       | 大 阪               |

| 初めて作る!! Virtex-4 による高性能 FIR フィルタ設計実践 コース  | 2/22(金)                       | 横 浜               |

| 動かす! わかる! Virtex-5 + DDR2 SDRAM 高速設計手法コース | 2/19(火)                       | 立 川               |

| 動かす!! 高速シリアル IO 体験セミナ                     | 2/20(水)                       | 大 阪               |

| ベーシック Verilog-HDL 記述コース                   | 2/19(火)<br>2/20(水)<br>2/21(木) | 横 浜<br>立 川<br>大 阪 |

| SUZAKU-S を使用した MicroBlaze 開発フローコース        | 2/26(火)                       | 横 浜               |

アヴネット ジャパン <http://www.avnet.co.jp/services/Training/index.asp>

\* 開催日程はWebにてご確認ください。

新光商事 <https://xilinx.shinko-sj.co.jp/training/index.html>

\* 4目以降開催のトレーニングスケジュールはWebにてご確認ください。

| 開催日             | 開催地 |

|-----------------|-----|

| 3/27(木)         | 東京  |

| 2/26(火)         | 大阪  |

| 3/5(水)          | 東京  |

| 3/13(木)         | 東京  |

| 2/27(水)、3/12(水) | 東京  |

| 3/25(火)         | 大阪  |

| 3/4(火)、3/7(金)   | 大阪  |

菱洋エレクトロ <http://www.rvovo.co.jp/xilinx/>

| コース名                    | 開催日                                                       | 開催地      |

|-------------------------|-----------------------------------------------------------|----------|

| ISE デザイン入力コース           | 2/21(木)、3/27(木)、4/24(木)、5/29(木)<br>3/5(水)、4/10(木)、5/15(木) | 東京<br>大阪 |

| FPGA 設計導入コース            | 2/22(金)、3/28(金)、4/25(金)、5/30(金)<br>3/6(木)、4/11(金)、5/16(金) | 東京<br>大阪 |

| アドバンスド FPGA 設計コース       | 2/14(木)～15(金)                                             | 大阪       |

| HDL 入門／VHDL 入門コース       | 2/20(水)、4/23(水)<br>2/13(水)、5/14(水)                        | 東京<br>大阪 |

| HDL 入門／VerilogHDL 入門コース | 3/26(水)、5/28(水)<br>4/9(水)                                 | 東京<br>大阪 |

PALTEK <http://www.paltek.co.jp/seminar/index.htm>

\*4目以降のトーナメントスケジュールはWebにてご確認ください

| コース名                    | 開催日                       | 開催地       |

|-------------------------|---------------------------|-----------|

| 初級者のための ISE ハンズオントレーニング | 1/25(金)、3/27(木)<br>2/8(金) | 新横浜<br>大阪 |

| 初級者のための EDK ハンズオントレーニング | 2/20(水)、3/26(水)<br>2/6(水) | 新横浜<br>大阪 |

| 初級者のための DSP ハンズオントレーニング | 2/19(火)                   | 新横浜       |

| VHDL 初級 ハンズオントレーニング     | 1/24(木)、3/5(水)<br>2/7(木)  | 新横浜<br>大阪 |

| Verilog-HDL 初級トレーニング    | 2/14(木)                   | 新横浜       |

# The NXP/PLDA Programmable PCI Express Solution

# NXP/PLDA による プログラマブルな PCI Express ソリューション

Spartan-3 FPGA ベースの PHY コントローラによって実現する

容易な統合性

Ho Wai Wong-Lam

Marketing Manager

NXP Semiconductors

ho.wai.wong-lam@nxp.com

Martin Gallezot

Marketing and Sales Director

PLDA

mgallezot@plda.com

今日の開発者は、膨大なデータを扱うアプリケーションに対して絶えずスループットを向上させながら、短縮化する製品ライフサイクルにも対応しなければならないという非常に辛い立場に立たされています。たとえば、科学、医療、産業の広範なアプリケーションを対象に、画像データを取り込んで処理、格納する画像処理を行うフレーム グラバ製品（画像取り込みボード）を例に取ってみましょう。画像検知技術の進歩に伴い、1 つのフレーム グラバで多くのピクセル数とフレーム レート、カメラの数に対応するようになったことから、インターフェクトのバンド幅に対する要求は厳しくなる一方です。アプリケーションによっては、1 Gbps を超えるスループットを要求するものさえあります。

今日の開発環境のニーズに応えるため、次

世代の I/O インターコネクト技術である PCI Express を採用すると共に、統合リスクを低減し製品の Time-to-Market を短縮する FPGA ベースの相互運用可能な実証済みソリューションに依存するようになっています。

PCI Express は PCI と PCI-X インターコネクト技術の後継であり、x1 で 2.5Gbps から x32 で 80Gbps まで幅広いバンド幅に

対応します。v2.0 仕様は、v1.1 仕様における 1 レーンのデータレートを 2.5Gbps から 5Gbps へと 2 倍にすることでバンド幅をさらに高めています。PCI Express はスループットの向上に加え、PCI/PCI-X より小さなコネクタを利用することから、コストの低減につながると共に、PCB の配線を容易にします。また、PCI/PCI-X から簡単に移行でき

るよう、PCI Express はソフトウェア パフォーマンスの点で PCI との下位互換性を持っています。

NXP PHY/PLDA IP コントローラなどの相互運用可能なソリューションは、PCI Express の利点と PCI-SIG により実証されたソリューションのセキュリティを兼ね備えているため、設計者はアプリケーション固有の機能に専念できます。

## NXP の PX1012A

NXP Semiconductors 社（旧社名：Philips Semiconductors 社）は、FPGA またはデジタル ASIC のコンパニオン チップとして利用できる、シングルレーンの 2.5Gbps PCI Express PHY デバイス、PX1012A を提供しています。PX1012A は、PLDA の XpressLite PCI Express IP コアで使用するのに最適です。

PX1012A は低価格 FPGA で使用するよう最適化されています。このデバイスは非常に小型のパッケージでありながら卓越した送受信性能を誇り、PCI Express 仕様 v1.0a と v1.1 に準拠しています。PX1012A は、スペースに制約がある低消費電力の ExpressCard モジュールからデスクトップ アドオン カード、さらには PCIe テスト装置のラック アドオン モジュールにいたるまで、あらゆるフォーム ファクタの PCI Express アプリケーションに対応します。NXP 社の PCI Express PHY デバイス、PX1012A の主な特長は次のとおりです。

- PCI Express の基本仕様 v1.0a と v1.1 に準拠しています。NXP の PHY は、2006 年 12 月に米国 PCI-SIG v1.1 電気コンプライアンス テストに合格した初のデバイスです。

- ザイリンクスの Spartan™-3 FPGA は、SSTL\_2 I/O をベースに、ソース 同期の 250MHz PXPIPE 規格を使って PX1012A PHY と通信します。ソース 同期クロッキングを採用したことで、送信データと受信データの両方に 1 つのクロックしか使わないオリジナルの PIPE 規格に比べ、FPGA デバイスと PHY

デバイス間のデータ トランザクションがより堅牢になり、PCB を容易にレイアウトできます。

- 2 つのシグナル リングを持つ 9 × 9mm の小型 BGA パッケージで、内側 リングの 1 つの信号だけがボール間をエスケープします。事実、NXP の PHY は、実際のハードウェア デザインで実証済みの 2 つの PCB シグナル レイヤだけを用いてレイアウトできます。ご要望に応じて、リファレンス デザインの提供も可能です。

- ノーマルの LO モードで低消費電力(通常、I/O を含めて 300mW 未満)で動作します。消費電力をさらに低減させるには、PHY/FPGA インターフェイスと最適化した PCB レイアウト上の終端抵抗を取り除くことで、PX1012A の消費電力を 150mW 未満に低減できます。

- コマーシャル用温度グレード (0~70 °C) とインダストリアル用温度グレード (-40~85 °C) の両方があります。これは PCI Express PHY に対するユニークなインダストリアル用温度グレードのデバイスであり、NXP PHY をさまざまなインダストリアル アプリケーションに利用できます。

## PLDA の XpressLite IP コア

PLDA の XpressLite PCI Express IP

コアは、Spartan-3 FPGA 用に最適化された PCI Express デジタル コントローラです。このコアには、PCI Express 仕様の 3 つのレイヤ（物理、データ リンク、トランザクション）がすべて含まれているほか、EZ DMA インターフェイスという追加のアプリケーション レイヤがあります。

PLDA の EZ DMA インターフェイスは、PCI Express プロトコルの経験がほとんど、あるいはまったくない設計者や、堅牢かつシンプルな PCI Express インターフェイスを求めているベテラン設計者に適しています。EZ DMA インターフェイスは、設計者にシンプルなアドレス/データ バスを含むターゲット パスと、ホスト システム メモリへのデータ転送を扱う複数の DMA エンジンからなるマスタ パスを提供します。また、EZ DMA インターフェイスは、Virtex™-5 LXT デバイスの内蔵 PCI Express コントローラと一緒に使うこともできます。

XpressLite コントローラは、PCI Express プロトコルに完全に準拠する RTL レベルの IP コアです。必要に応じて、コンフィギュレーション レジスタや関連 ファンクションを、すべてトランザクション レイヤ内のコンフィギュレーション スペースにインプリメントすることができます。また、コンフィギュレーション スペースは、ルート コンプレックスの方向に流れるコンフィギュレーション リクエストから、すべてのメッセージ (PME#、INT、エラー、パワー

表 1 XpressLite コントローラによりサポートされる PCI Express の機能

| コア タイプ              | レガシーまたはネイティブ エンドポイント                                                                                                                                                        |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 最大ペイロード             | 最大 2KB                                                                                                                                                                      |

| バックエンド データ パス       | 64 ビット                                                                                                                                                                      |

| 仮想チャネル              | 1                                                                                                                                                                           |

| BAR、拡張 ROM          | ユーザー定義、XpressLite ウィザードにより設定                                                                                                                                                |

| PCI ID              | ユーザー定義、XpressLite ウィザードにより設定                                                                                                                                                |

| 従来の電源管理             | ミニマルまたはフル、XpressLite ウィザードにより設定                                                                                                                                             |

| メッセージ信号割り込み (MSI)   | <ul style="list-style-type: none"> <li>メッセージ カウント : 1~32、XpressLite ウィザードにより設定</li> <li>64 ビット アドレス : Yes</li> <li>ペクトルごとのマスキング : No</li> </ul>                             |

| EZ マルチ DMA インターフェイス | <ul style="list-style-type: none"> <li>DMA チャネル : 最大 8 つ、XpressLite ウィザードにより設定</li> <li>未処理要求の数 : 1~8 の同時要求、XpressLite ウィザードにより設定</li> <li>最大 DMA 転送サイズ : 最大 4GB</li> </ul> |

図 1 v1.1 PCI Express テンプレートを持つ PLDA XpressLite SP3 ボードのトランスマッタ アイ パターン (上: 非遷移アイ、下: 遷移アイ)

スロット制限)、MSI リクエスト、および完了パケットを生成します。

XpressLite はグラフィカル ウィザードを使用したコンフィギュレーションが可能で、最大ペイロード サイズやコンフィギュレーション スペースのレジスタ、バッファ サイズ、DMA チャネルの数といったパラメータを簡単にカスタマイズできます。ウィザードはコアのトップレベルをインスタンシエートしてポートを接続し、指定したオプションにしたがってパラメータを割り当てるラッパを生成します。未使用のコア機能は合成されません。

XpressLite は PCI Express の仕様 1.1 に準拠します。フットプリントは小さく、消費メモリは最小限です。一般的なインプリメンテーション例として、Spartan-3 デバイスに約 8,000 個の LUT と 7 つのブロック RAM を使用します。これには 2 つの DMA チャネルを用いてコンフィギュレーションされた EZ マルチ DMA アプリケーション レイヤが含まれます。表 1 に、XpressLite コントローラがサポートする PCI Express の機能概要を示します。

PLDA のコア パッケージには、RTL レ

ベルの PCI Express バス ファンクション モデル (BFM)、トランザクタ、モニタ、チャッカを備える完全なテスト ベンチがあります。

### 完全準拠の相互運用可能なソリューション

NXP と PLDA の両社合同ソリューションは、2005 年 12 月の PCI-SIG コンプライアンス ワークショップ #48 と、2006 年に継続して行われた数回のワークショップにおいて、PCI Express コンプライアンス テストを無事完了しました (図 1 のトランスマッタのアイ パターンの結果を参照)。

NXP と PLDA、および両社の顧客は、次のような多数の PC システムで広範なシステム テストを実施し、すべてに合格しました。

- ASUS A8NE (x16、2 つの x1 スロットと 1 つの x4 スロット)

- ASUS P5GP マザーボード (Intel 915G チップセット)

- ASUS P5LD2 DELUXE (Intel i945 チップセット)

- Dell Dimension 4700 の x1 および x16 スロット (Intel 915G チップセット)

- Dell Dimension 8400 (Intel 925 G チップセット)

- Dell Precision 370

- Dell Precision 470 の x8 と x16 スロット (Intel Turnwater E7525 チップセット)

- HP XW4200

- HP XW4300

- MSI (Intel i915 チップセット)

- Serverworks GC-SL

- Shuttle ATI Express 200 チップセット

- Supermicro X6DA8G (x16 と x4 スロット)

NXP と PLDA の両社は、標準的な PCI-SIG コンプライアンス テストに加え、社内開発したシステム テストとサーダパーティ テスト機器ベンダのシステム テストなど次に挙げる多くのテストを行いました。

- PCI スキャン診断ユーティティ

- トランスマッタの電気的コンプライアンス テスト v1.0a と v1.1

- PCI-SIG PCI-ECV v1.2

- Agilent 社のプロトコル テスト カード (PTC) テスト

- Agilent 社のレシーバ ビット エラー レート (BER) テスト

- NXP 社のレシーバ性能テスト

- PLDA 社のスループット測定テスト

### 高スループット

理論上の最大スループットはペイロード サイズと PCI Express プロトコルのオーバヘッドで決まります。実際のスループットは、ソフトウェア ドライバの効率、PCI Express IP コアの効率、ユーザーのアプリケーション デザイン、トランスマッタのジッタ、およびレシーバの BER パフォーマンスといった要因に左右されます。さらに、ACK/NAK パケット (アクノリッジ/ノンアクノリッジ)、再送パケット、フロー制御プロトコル (クレジット レポーティング) といった、リンクレイヤ プロトコルのオーバヘッドによっても影響されます。

### 理論上の最大スループット

1 レーンの PCI Express のラインスピードは 2.5Gbps です。ただし、8B/10B エンコーディング オーバヘッドにより、PXPIPE の最大データ スループットはそ

表 2 スループット測定結果

| PCI Express PHY | IP コア | コンピュータ プラットフォーム                | ペイロード     | スループット              | スループット               |

|-----------------|-------|--------------------------------|-----------|---------------------|----------------------|

|                 |       |                                |           | DMA Read (Card->PC) | DMA Write (PC->Card) |

| PX1012A         | PLDA  | ASUS A8NE<br>Supermicro X6DA8G | 128 bytes | 200 Mbps            | 175 Mbps             |

れより低くなります ( $2.5\text{Gbps} \div 10\text{ ビット/バイト} = 250\text{Mbps}$ )。オーバヘッドのパフォーマンスコストにより、スルーブットはある時点までペイロードサイズと共に高くなっているのが一般です。たとえば、128バイトのペイロードでは、理論上の効率は86% (128B (バイト) ペイロード + 12B ヘッダ + 8B フレーミング) であり、理論上の最大スルーブットは 216Mbps です。PCI Express 仕様では、最大ペイロードサイズは最高 4KB までとされていますが、ほとんどの既存アプリケーションは 128B または 256B の最大ペイロードサイズしかインプリメントしません。表 2 に、NXP/PLDA ソリューションに対するスルーブット測定値を示します。

## レシーバの性能

NXP 社と PLDA 社は、長時間にわたり回復可能なレシーバ エラーが発生しないことを確認するため、多数の PC システムで独自の広範なシステム テストを実施しました。テストの結果、BER は  $1 \times 10^{-12}$  でした。

PCI Express 仕様 v1.0a と v1.1 は、0.6UI (ユニット インターバル) のレシーバ ジッタ トレランスを必要としますが、いずれの仕様もジッタ コンポーネントの構成については具体的に示していません。NXP 社は Agilent 社の BER テスタを用いてレシーバの BER テストを実施しました。

- Agilent J-BERT N4903A

- TJ = 総ジッタ ; RJ = ランダム ジッタ ; PJ = 周期ジッタ ; DDJ = データ依存ジッタ ; UI = ユニット インターバル ; ISI = シンボル間干渉 ; BER

- $0.60\text{UI TJ} = 0.25\text{UI RJ} + 0.25\text{UI PJ}$  ( $15\text{MHz}$ ) +  $0.1\text{UI DDJ}$

- $0.1\text{ UI DDJ} = 9$  インチの PCB トレイスをスティミュレートし、約  $0.1\text{UI}$  のジッタと大幅な振幅劣化を招く ISI モジュール

NXP 社は、Agilent 社のビット エラーテスタを用いて素晴らしいレシーバ性能を得ました。

図 2 PLDA XpressLite SP3 はザイリンクスの Spartan-3 FPGA をベースとし、NXP社の PCIe PX1012A PHY と PLDA 社の XpressLite IP コントローラを備えています。

- PX1012A は、PCI Express 仕様の最小伝送出力レベルである 800-mVdiff. p-p 入力信号で  $1 \times 10^{-12}$  BER 未満を達成しました。800-mVdiff. p-p 信号は PHY レシーバに届く前にパターン ジェネレータから BERT ISI モジュールに送られます。

- ISI モジュールなしの場合、PX1012A は 400-mVdiff. p-p 入力信号で  $1 \times 10^{-12}$  BER 未満を達成できます。

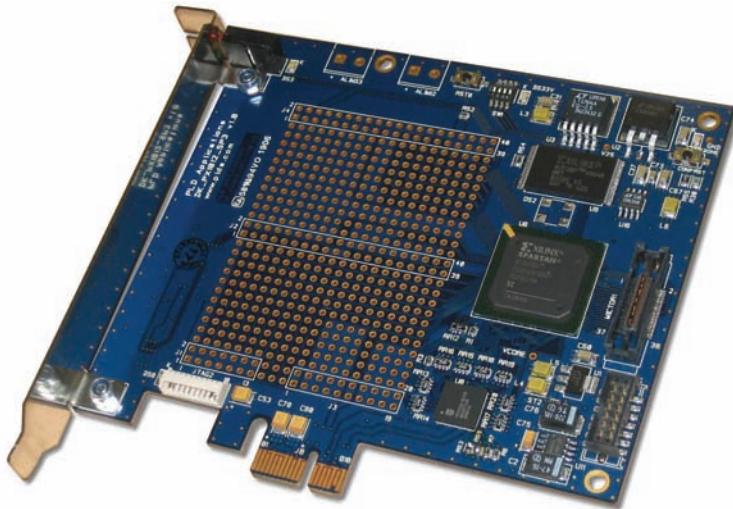

## PLDA XpressLite SP3 デザイン キット

PLDA XpressLite SP3 デザイン キット (図 2 を参照) は、Spartan-3 FPGA (XC3S2000 デバイス) をベースとし、NXP PX1012A を統合したものです。デザイン キットには、PLDA XpressLite IP コアの Protocore (ボードのみ) ライセンスが含まれています。

このデザイン キットに含まれている Protocore ライセンスは、完全な機能を備える RTL レベルの恒久的に有効なライセンスです。また、C ソースコード ファンクションのライブラリとドライバを収めたソフトウェア開発キットも用意されています。Protocore ライセンスにより、XpressLite IP コアに接続されている独自デザインを自由にシミュレート、合成し、それ

に従って FPGA デバイスをリプログラミングできます。

この完全なデザインは広範な検証テストを終え、ハードウェアで実証済みであり、いつでもお客様のプロトタイピングに利用できます。

XpressLite SP3 デザイン キットは、PCI Express を用いてデザインをプロトタイピングするための低コスト ソリューションです。また、PCI Express ボードを独自にデザインする際の手間を省くため、最終製品の一部として使用することができます。プロトタイピングとプローブング用に 400 ホールのマトリックス (2.54mm ステップ) も用意されています。

## 結論

PLDA XpressLite SP3 デザイン キットは、ザイリンクスの Spartan-3 FPGA のパワーと、実証済みの PCIe NXP PHY/PLDA IP コントローラ ソリューションを組み合わせたものです。このようなプロトタイピング ボードは、製品ライフサイクルがますます短縮化するなか、より高いデータ スルーブットをサポートするアプリケーションを作るという今日の開発課題にお応えします。詳細は、[www.standardics.nxp.com/products/pciexpress/](http://www.standardics.nxp.com/products/pciexpress/) と [www.plda.com/products/board\\_pciesp3.php](http://www.plda.com/products/board_pciesp3.php) をご覧ください。

# Driving Home Multimedia

# 車の中のマルチメディア

自動車用ネットワーク規格の普及によって注目を集める

車載インフォテイメント

Carl Rohrer

Senior Design Engineer

Xilinx, Inc.

carl.rohrer@xilinx.com

マルチメディアの数は、1 平方フィートあたりで換算すると、自宅より車の中のほうが多いでしょう。一部の高級車には、後部座席に子ども用として DVD プレイヤからビデオゲームのコンソールで制御する液晶画面 (LCD)、オーディオ システムには最新の MP3 プレイヤを使い、ナビゲーション システムはもちろんのこと、テレビさえ装備されています。さらに、人によっては自宅の高級サラウンド サウンド システムより車内スピーカのほうが多いことがあります。これではわき見運転をするドライバーが多いのは当然です。今ドライバーに必要なのは、1 力所で集中制御できるシンプルなインターフェイス

です。また、メーカーは高度なネットワークを必要としています。

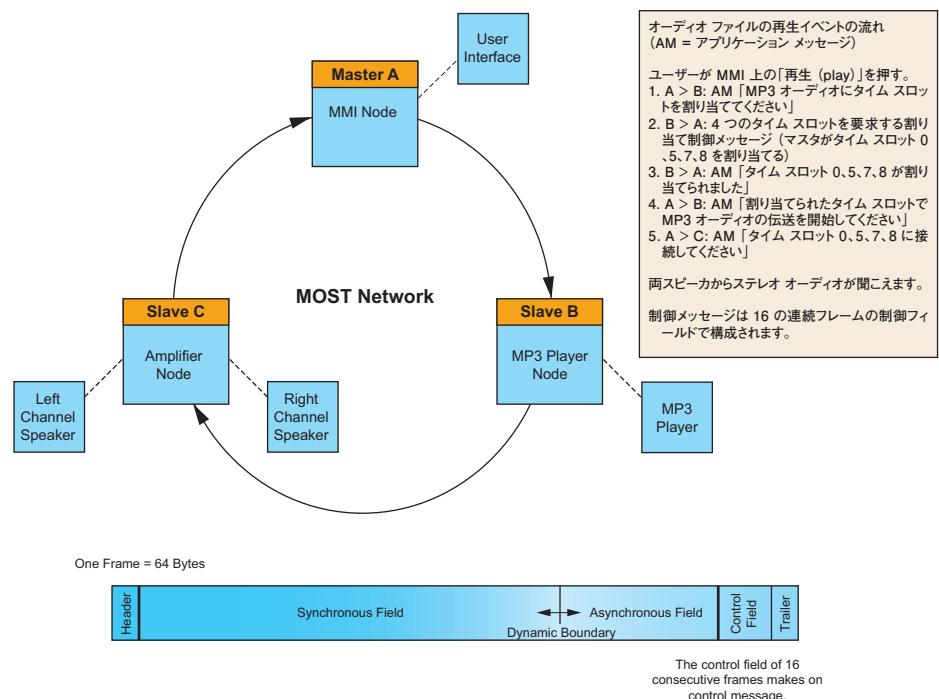

MOST (Media Oriented Systems Transport) は、自動車メーカーとサプライヤの間で採用が進んでいるネットワーク規格です。MOST は、すべてのマルチメディアデバイスを一元的に管理するためのインターフェイスを提供します。これにより、全体の調和を損なうことなく、ターゲットの異なる複数のデータ ストリームを扱うことができます。自宅のネットワークでさえ難しい「オンラインデータ」を実現するわけです。

本稿では、MOST ネットワークを詳しく見ていくと共に、ザイリンクスの MOST ソリューションの柔軟性について解説します。

## MOST の仕組み

MOST ネットワークには、一般にリングトポロジの光ファイバを使います。クロックと

シリアル化されたデータは、バイフェーズエンコードされ、配線には 1 本のファイバしか使用しません。MOST の総帯域幅は、従来のオートモーティブ ネットワークをはるかに越える最高 25Mbps です。すなわち、15 のオーディオ ストリームを同時に再生できることになります。

各マルチメディア デバイスはリング内のノードとして表されます。一般的な MOST ネットワークは 3~10 のノードを持ちます。システム クロックを駆動して、フレーム、つまり 64 バイト シーケンスのデータを生成するタイミング マスターが 1 つあり、それ以外のノードはすべてスレーブとして働きます。そのうちの 1 つは、MMI (Man-Machine Interface) と呼ばれるユーザー制御インターフェイスです。このインターフェイスがタイミング マスターを兼ねることもあります。図 1 に、基本的な MOST リングを示します。

メインのペイロードは 64 バイト フレーム内の 60 バイトです。このペイロードは同期および非同期フィールドからなります。同期フィールドは、連続するデータをストリーミングするために使われます。オーディオとビデオはこのカテゴリに入ります。非同期フィールドは、インターネット アクセス、ナビゲーション データの転送、電話帳の同期化といったアプリケーションで、散発的なデータ転送に使われます。また、このチャネルは制御ユニットのファームウェア アップグレードに使用できます。

ノードは、割り当てられたタイム スロット中にデータを送信、もしくは受信することができます。タイム スロットはペイロード内の 1 同期バイトであり、要求側のノードとタイミング マスター間で動的に割り当てられます。

通常、1つのノードがタイムスロットにデータを伝送する間、他のノードはそのタイムスロットからデータを収集します。

同期と非同期の境界は、タイミングマスターにより動的に制御されます。どのフレームであれ、同期フィールドは4~60バイトを占め、60バイトのうち残りの部分を非同期フィールドに振り分けます。

どちらのフィールドにも使われない4バイトは、ヘッダ、トレイラ、制御情報に使われます。ヘッダにはフレーム調整のための前情報があります。トレイラはパリティチェックなどをを行い、制御フィールドはネットワーク関連のメッセージングに使われます。これらのメッセージは、タイムスロットの割り当てとその解除といった低レベルなものから、次のトラックの再生、音量調節、繰り返し再生など、オペレータから送られる高レベルなアプリケーションメッセージもあります。

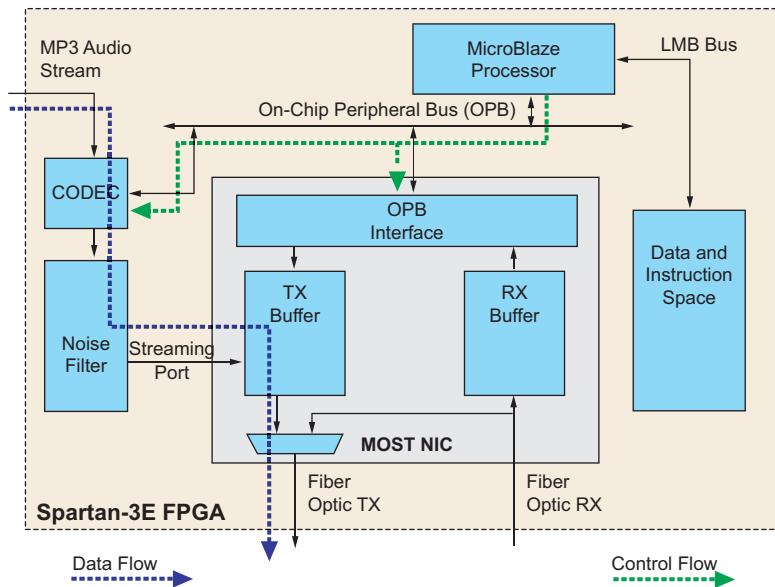

## MOSTの有効利用

マイクロコントローラやDSPに外部のMOSTコントローラチップを接続する代わりに、すべてのコンポーネントを1個のFPGAに統合できます。外部コンポーネントの数が減り、基板のスペースが縮小すれば、開発者にとってコストの節約になります。

ザイリンクスは、完全にパラメータ化できるMOST NIC(Network Interface Controller)IPコアを提供しています。このコアをカスタマイズすることで、タイミングマスターにしたり、スレーブのみのコンフィギュレーションでロジックを減らしたりできます。MOST NIC IPコアは、オンチップペリフェラル(OPB)インターフェイスからアクセスするフルスイートのレジスタによって制御されます。OPBインターフェイスは、ザイリンクスのPlatform Studioに含まれているザイリンクスのMicroBlaze™32ビットRISCプロセッサコアとシームレスに連携します。

また、Cソースコードで低レベルのドライバファイルのフルセットを既に用意しています。これらのドライバは、レジスタスペースにアクセスしたり、割り込みを処理したり、コアにデータをストリーミングするための一連のファンクションを提供します。Mocean

図1 MOSTオートモーティブリングの例

図2 理論上のMP3ノード

Laboratories社では、完全なネットワークスタックを構築できるよう、IPコア用のMOSTネットワークサービスを提供しています。これを用いることで、設計者はアプリケーションの開発に専念できます。

ザイリンクスのMOST NIC特有のインタ

フェイスとして、データをリアルタイムでプリプロセッシングできるストリーミングポートインターフェイスがあります。このインターフェイスは、データフィルタや暗号化/複合化モジュールに接続するのに理想的です。ザイリンクスの標準であるこの

LocalLink インターフェイスは、専用の処理手続きを行うことでプロセッサとプロセッサ バス上のトラフィックを大幅に低減させます。また、多目的に利用することが可能で、受信または送信方向のどちらでもデータを読み書きすることができます。なかでも優れた点として、その機能を使用しない場合はザイリンクスのインプリメンテーション ツールが不要なロジックを取り除くため、リソースを節約し、デザインをより小型のデバイスに収めることができます。

同期データは、ストリーミング ポートまたは OPB インターフェイスのいずれかで送受信できます。どの方法を選択するかや、タイム スロットをいくつ割り当てるかにかかわらず、コアはこれらインターフェイスに対してデータを 32 ビット ワードにフォーマットします。また、コアはレジスタの定義を通して、16 の論理チャネルのうち 1 つのチャネルを通して受信したタイム スロット データを蓄積します。送信はその逆です。これらの論理チャネルを使うことで、16 の異なるデータ ストリームをそれぞれの方向に送ることができます。

ザイリンクスの MOST NIC コアは柔軟性に優れています。もう一度、図 1 の MOST リングを見てください。この図は、ザイリンクスの MOST NIC を用いて各ノードをデザインする方法を示したもので、設計者は、コアを MMI として動作するタイミング マスタとしてコンフィギュレーションできます。タイミング マスタとしてのコアは、リングの動作を調整する制御メッセージを送受信します。このノードは、ユーザーに代わり、制御フィールドを通してアプリケーション メッセージも送信します。また、イベント スケジューリングには、MicroBlaze 用のドライバ ファイルと Mocean Laboratories 社のネットワーク サービスを利用することができます。

ノイズ フィルタを追加することで、音声圧縮時の劣化を除去し、MP3 プレイヤをハイエンドな音源に変えることができます。ノイズ フィルタを通してコーデックからストリーミング ポートにペイロード データを直接伝送することで、OPB バスを回避できます。この場合も、MicroBlaze エンベデッド プロセッサを使用して、割り込み処理

とイベント スケジューリングを実行できます。図 2 に、これらデザインのブロック図を示します。

データを受信し、スピーカに転送するだけの最もシンプルなアンプのデザインを考えてみましょう。エンベデッド プロセッサを使用することなく、MP3 ノードのように、ネットワーク ネゴシエーションとデータ収集にフルに対応するコンパクトなユーザー デザインをインプリメントできます。このようなコンパクトなデザインは小型のデバイスに配置できることから、さらなるコスト削減につながります。

## 結論

ヨーロッパの一部の高級車には、すでに MOST ネットワークが採用されています。MOST ネットワークは、ヨーロッパの OEM メーカーの間で、オートモーティブ ネットワーキングに対する事実上のスタンダードになりました。近い将来、高級車以外にも広く搭載されるでしょう。最近ではメーカーの競争により、かつて 1 社の標準でしかなかった MOST は、コスト意識の高い自動車メーカーにとって調達しやすいものになってきました。

オーディオからビデオ、テレマティクス、ナビゲーション ベースのアプリケーションにいたるまで、大容量データに対する需要が増えるなか、MOST ネットワークの技術革新が進んでいます。次世代規格の MOST 50 はすでに完成しており、2 倍のバンド幅を提供することになります。本稿執筆時点では、MOST Cooperative がデータレート 150Mbps 以上の第三世代ネットワークを計画しています。これらのアップデートにより、最終的にアプリケーションのバンド幅は格段に増え、銅線と光ファイバの両方の物理 メディアをサポートするようになるでしょう。

現在、ザイリンクスの MOST NIC は CORE Generator™ ソフトウェアで利用いただけます。Spartan™-3E FPGA の中型 デバイスでは、6 つのブロック RAM と約 2,600 のスライスで構成でき、エンベデッド プロセッサやペリフェラル、バッファ、設計者独自のカスタム回路を収容する余裕もあります。

**パートナーの皆様

御社の製品・サービスを

Xcell journal 誌上で

PRしてみませんか？**

Xcell Journal は、プログラマブル ロジック ユーザーへ、ザイリンクス製品／ツールの最新 情報をはじめ、システム／アプリケーションの 解説、サービス／サポート情報、サードパーティ 各社のツール情報などをお届けしています。

現在では日本各地の 7,000 名を超える幅広い 分野のエンジニアの皆様に愛読いただいており、ザイリンクスが主催・参加するイベントでも広く配布しています。

貴社製品／ソリューションのプロモーションに 非常に効果的なメディアです。

広告掲載に関するお問い合わせ先

**有限会社 エイ・シー・シー**

Xcell 広告係まで e-mail でお願いいたします。

e-mail: t.sohyama@jcom.home.ne.jp

## DSP Performance of FPGAs Revealed

# 明らかになった FPGA の DSP 性能

BDTI Communications Benchmark (OFDM) による

最新のベンチマーク結果

Jeff Bier

President

BDTI - Berkeley Design Technology, Inc.

bdti@bdti.com

無線基地局などの高性能 DSP アプリケーションの処理エンジンとして、FPGA を検討する案件が増えています。このようなアプリケーションでは、FPGA と DSP プロセッサのいずれかを使うか、あるいは並行して使うかの選択を迫られます。

システム設計者は、選択肢の増加に伴い、各ハイエンド FPGA の信号処理性能を相互に比較すると共に、ハイエンド DSP プロセッサとの比較も行う必要があります。残念なことに、一般に使われている性能値は信頼性に欠け、誤解を招きやすく、場合によっては矛盾することさえあります。

たとえば、DSP アプリケーションは積和 (MAC) 演算に大きく依存するため、DSP プロセッサや FPGA のベンダは、デジタル信号処理の性能を比較するための単純なメトリックとして、ピーク時の MAC／秒を使うことがあります。しかし、MAC のスループットは、FPGA と DSP のいずれの性能も正しく予測できません。次にその理由のいくつかを紹介しましょう。

### 単純なメトリックの問題点

一般に、FPGA に対する MAC 性能値は、ハードウェイで接続された DSP 要素が最高クロック レートで動作することを前提に算

出されます。しかし、一般的な FPGA デザインは、実際にはそれより遅いスピードで動作します。また、ハードウェイで接続された要素を使うのは FPGA に MAC をインプリメントするための 1 つの方法にすぎず、プログラマブルロジックのリソースと分散演算を使用して MAC のスループットをさらに高めることができます。この方法は、ハードウェイされた要素だけを使う場合より高い MAC スループットを達成できます。

もう 1 つ考えなければならない点は、一般的な DSP アプリケーションが MAC 以外にも多くの演算に依存することです。たとえば、

Viterbi デコーディングは通信アプリケーションに使われる重要な DSP アルゴリズムですが、MAC をまったく使用しません。

信号処理性能を評価するためのもう 1 つの方法は、FIR フィルタなどの一般的な DSP ファンクションを使うことです。ただし、この方法には欠点もあります。このファンクションはベンダによってインプリメンテーションが異なり、データ幅、アルゴリズム、レイテンシなどのインプリメンテーション パラメータがそれぞれ異なることです。このため、各ベンダの性能値をそのまま比較することはできません。

さらに、FPGA のフル アプリケーション内

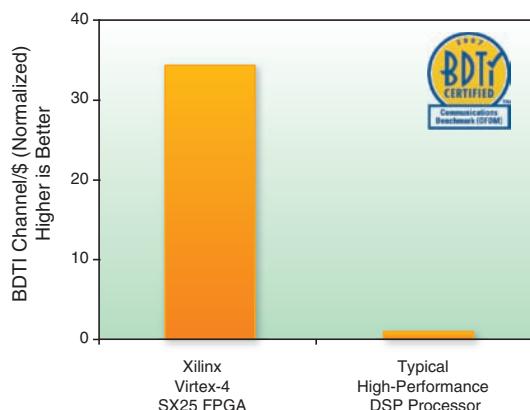

図 1 BDTI Communications Benchmark (OFDM)

BDTI 社認定のコストパフォーマンス最適化結果

でファンクションをインプリメントするのと、そのファンクションを単独でインプリメントするのとではやり方がかなり異なることから、小さなカーネル ファンクションは FPGA ベンチマークに有効ではないのが一般です。これとは対照的に、プロセッサの場合は、このような小さなベンチマークで DSP アプリケーションの総合的な性能をかなり正確に予測できます。また、プロセッサや FPGA のベンダがインプリメントしたベンチマークは、第三者によって検証されたものではないため、デバイスを比較するには困難です。

### ギャップを埋めるのは 第三者のベンチマーク

BDTI 社は信号処理のベンチマークで最も信頼されている会社です。当社のベンチマークは、半導体メーカー数十社と数千のチップ ユーザーが信号処理エンジンを評価、比較、選択するために利用しています。BDTI 社はプロセッサの信号処理性能を 15 年近くにわたってベンチマークしており、最近では FPGA やマルチコア チップといった他のテクノロジのベンチマークも手がけています。

BDTI 社は、数年前、DSP アプリケーションをターゲットとする FPGA とプロセッサの性能を第三者的な立場から正確に比較する必要があると考え、これを実現するため、直交周波数多重分割変調方式 (OFDM) レシーバをベースに、BDTI Communications Benchmark (OFDM) という新たなアプリケーション指向のベンチマークを開発しました。このベン

チマークは、DSL やケーブル モデム、ワイヤレス システムなどのアプリケーション向け通信システムで増えつつあるベースバンド信号処理のワークロードを測定するものです。このベンチマークは、FPGA や DSP プロセッサ、マルチコア チップ その他多数の信号処理エンジンへのインプリメントに適しており、同じ基準に基づくベンチマーク結果を提供します。

昨年、BDTI 社は、BDTI Communications Benchmark (OFDM) を使用して、新しい高性能 FPGA や DSP プロセッサの評価を行いました。解析結果の詳細は、BDTI 社のレポート「FPGAs for DSP : Second Edition」に掲載され、DSP システム設計者から大きな注目を集めました。このレポートには 2 セットのベンチマーク結果が掲載されています。1 つは、チップあたりにサポートするチャネルの数を最大化した大容量に重点を置いた場合の解析結果で、もう 1 つは、チャネルあたりのコストを最小化した低コストに重点を置いた解析結果です。図 1 に、ザイリンクスの Virtex™-4 SX25 FPGA と代表的な高性能 DSP プロセッサでのコストパフォーマンスを比較した結果を示します。

図 1 の BDTI 社のベンチマーク結果から、高性能 DSP アプリケーションには FPGA の方がいかにコスト面で優れているかがわかります。このベンチマークでは、Virtex-4 SX25 デバイスは、代表的な高性能 DSP プロセッサより 10 倍以上もコスト効果に優れています。この結果は、DSP よりも FPGA の方がアプリケーションによってはチップ レベルのコストパフォーマンスが優れて

いると考えてはいるものの、どれだけ優れているのか確信を持てなかったシステム設計者にとって極めて貴重な情報です。本レポートでは、ザイリンクス以外のベンダの FPGA についてもコストパフォーマンスの結果を比較しています。

新しいシステム デザインに FPGA を使うべきかどうかや、どの FPGA を使うべきかを、ベンチマークの結果だけで判断することはもちろん不可能です。設計者は、選択した処理エンジンが開発の流れやインプリメンテーション システム デザインにどう影響するかを理解する必要があります。このため、BDTI 社のレポートは、FPGA と DSP のどちらを使うべきか、あるいは両方使うべきかを判断するための質的要因を掘り下げると共に、いかに正しい情報を基に選択すべきかについてのガイドを提供しています。また、同レポートは、FPGA のエネルギー効率や FPGA に対する新たなハイレベルな合成の有効性など、ハイエンドな DSP アプリケーションで FPGA を長期にわたって成功させるための重要な点にもスポットを当てています。

### 結論

BDTI 社は、この分野におけるさらなる解析を行うと共に、新しい FPGA や DSP、および大規模並列プロセッサの信号処理能力を評価し続けています。信号処理エンジンの競争はますます激化しており、BDTI 社は設計者が自信を持って選択できるよう、データと解析結果の提供を続けていく予定です。

BDTI 社のレポート「FPGAs for DSP, Second Edition」は、客観的な立場から FPGA の信号処理ベンチマーク結果をまとめた信頼できる情報ソースです。「FPGAs for DSP, Second Edition」の詳細は、<http://www.BDTI.com/fpgas2006> をご覧ください。また、BDTI 社の詳細は <http://www.BDTI.com> をご覧ください。

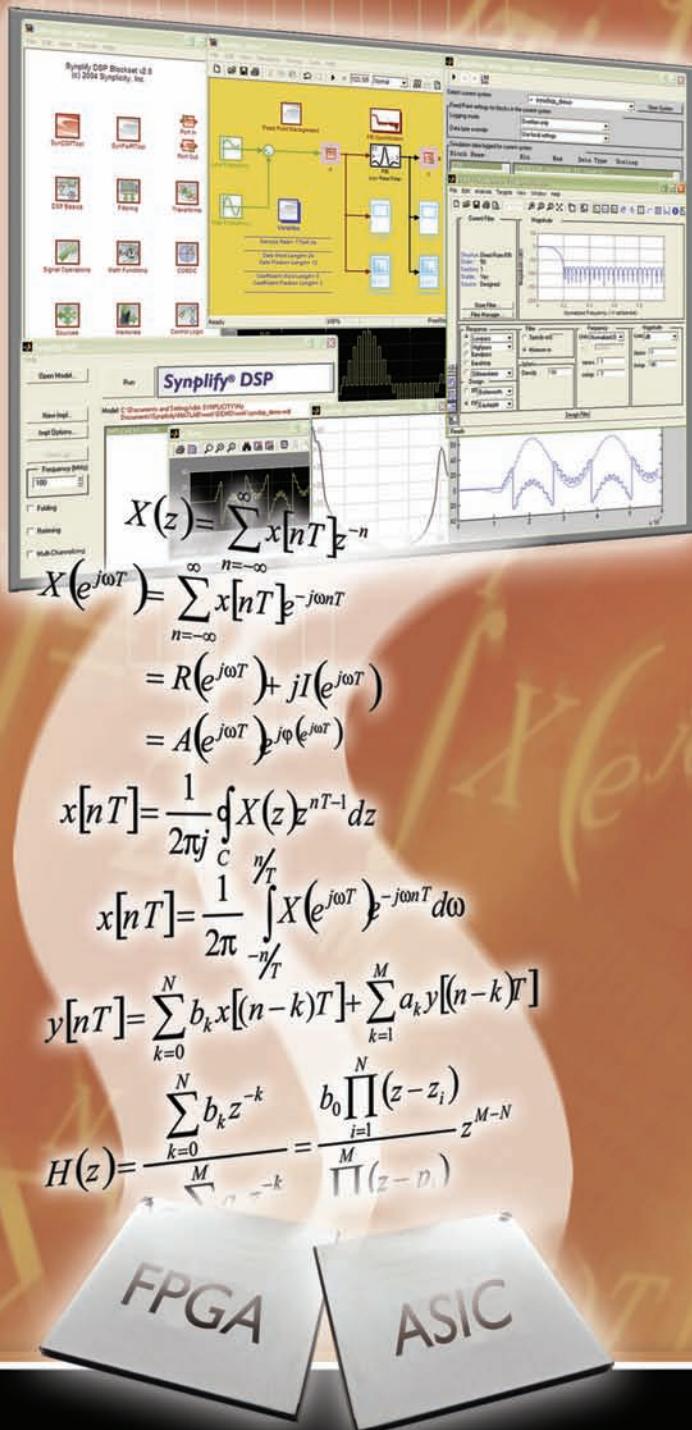

# Synplify® DSP

## ESLシンセシス・ソリューション

Synplify DSPソフトウェアはDSPアルゴリズムをFPGAあるいはASICへの高速かつ効率的なインプリメンテーションを実現するESLシンセシス・ソリューションです。パイプライン化やリソース・シェアリング、そしてマルチチャネル化などアーキテクチャの最適化を自動化することによって、エンジニアはRTLコード化を月単位で短縮し、デザイン・キャプチャをシンプルにし、検証工程の速度を上げ、そして効率的なIPを作成することができます。

### Synplify DSPソフトウェアのユニークな機能

- ・拡張可能なDSPブロックセット

- ・マルチレートおよびベクタ計算などを包括的にサポート

- ・固定小数点の量子化およびベクタ計算をサポート

- ・パワフルなDSPシンセシス・エンジン搭載

- ・アーキテクチャを最適化したVerilog/VHDLインプリメンテーションを実現

- ・ASICとFPGA双方の最新テクノロジをターゲットとして選択可能

- ・標準的なASICデザインフローも包括的にサポート

- ・メモリ抽出機能によって、サードパーティ ASIC メモリ・ベンダに柔軟に対応可能

Synplify DSPソリューションをはじめとするSynplicity製品の詳細については

[www.synplicity.jp](http://www.synplicity.jp)でご覧いただぐか、[info@synplicity.jp](mailto:info@synplicity.jp)にてご連絡ください。

**Synplicity®**

Simply Better Results

# Processing Signals from Outer Space with BEE2

# 宇宙空間からの信号処理

UC Berkeleyの天文学者らによる最先端の電波望遠鏡システム BEE2 – Linux や System Generator for DSP、EDK を活用して開発

Chen Chang

CTO

BEEcube

chen@beecube.com

Bob Brodersen

Professor Emeritus

UC Berkeley

rb@eecs.berkeley.edu

John Wawrynek

Professor

UC Berkeley

johnw@eecs.berkeley.edu

Dan Werthimer

SETI@home Chief Scientist

Director, Center for Astronomy Signal

Processing

UC Berkeley

danw@ssl.berkeley.edu

Kees Vissers

Principal Engineer

Xilinx, Inc.

kees.vissers@xilinx.com

図 1 電波望遠鏡の画像から収集したブラックホールについての情報

最近の電波望遠鏡は、0GHz 近くから 11GHz の周波数帯で宇宙を観測します。このような望遠鏡は、データを処理した後、図 1 に示すブラックホールへの衝突など、非常に興味深い現象について情報を提供できます。

従来、電波望遠鏡はペルトリコのアレシボ望遠鏡のように、巨大なシングルディッシュのアンテナで作られていました。しかしながら、望遠鏡を建造するための鋼材コストがあまりに巨額なことから、50 年以上にわたり、世界最大の集光面積を誇るアレシボ望遠鏡を超える望遠鏡は登場していません。

デジタル信号処理が発明されて以来、電波望遠鏡のデザインは、巨大な集光面積を使うものから、数百～数千の小径 (6～12m) アンテナアレイへと移り、鋼材と電子部品を併用することでコストのバランスを取るようになりました。アンテナは物理的に広い面積に分散して配置され、極めて長い可変長の基線と優れた角分解能を提供します。北カリフオルニアのハットクリーク近くに設置されている Allen Telescope Array はその代表です。本稿では、SETI (地球外知的生命体探査) Institute と UC Berkeley の Radio Astronomy Laboratory の望遠鏡に採用されている FPGA を用いた信号処理について解説します。

## 多数の小径アンテナアレイ相関器

アンテナアレイの信号処理は非常に難しい課題です。正しい画像を形成するには、アンテナからのすべての信号を相関処理し、 $O(N^2)$

という複雑な演算を行う必要があります。1 平方キロメートルの集光面積を得るには、それぞれ直径 12 メートルのアンテナを 8,000 本以上使う必要があります。

11GHz のバンド幅全体を相関処理するには、1 秒あたり 1,000 ペタ演算、つまり現在最速とされるスーパーコンピュータの 3,000 倍以上の計算能力が必要です。これほど演算スループットを妥当なコストで手に入れるには、まったく新しいコンピューティングアプローチが求められます。

さらに、電波望遠鏡は一般に 30 年以上稼働することを前提としてデザインされます。バンド幅の要件を満たすため最初からすべてのエレクトロニクスに投資する必要はなく、数年ごとにアップグレードし、観測可能なバンド幅を徐々に増やしていくべきです。こうしたアプローチで臨むことで、年々指数的に下落していく半導体価格をにらみながら最適な価格性能比を達成できるというわけです。

今日のデザインでは、専用のエレクトロニクスと特別なソフトウェアを併用するのが一般的です。本稿では、信頼性の高いハードウェアとコモディティルータからなる BEE2 システムと、ザイリンクスのプログラミング環境を活用したデザインを紹介します。バックエンドのコンピュータとシステムの表示部は汎用のコンピュータで問題ありません。近年、FPGA ベースのシステムは、ギガヘルツレンジのアナログ-デジタルコンバータ (ADC) とバックエンドコンピュータ間の信号処理ニーズに対応できます。これらの FPGA システムは信頼性とコスト効率に非常に優れています。

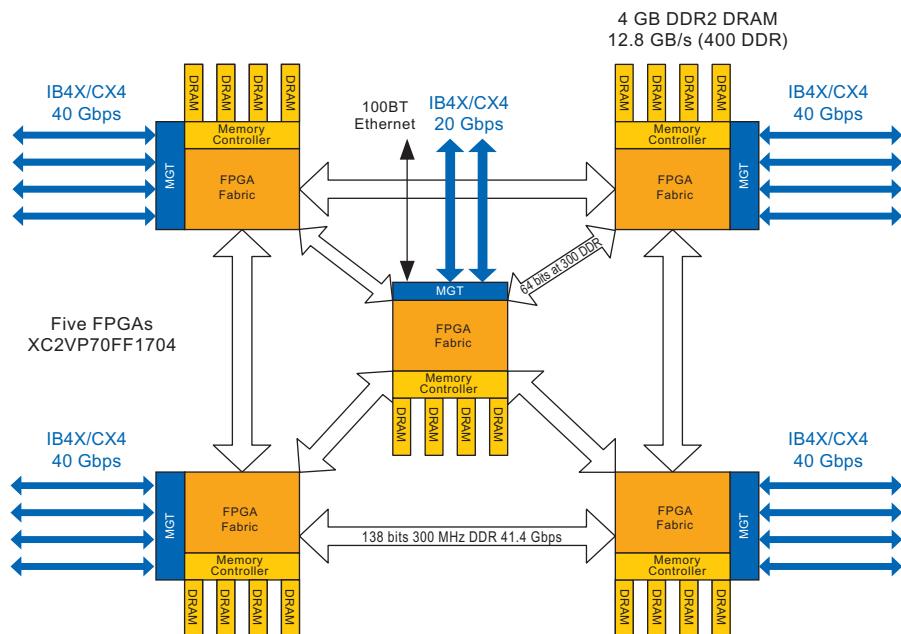

## BEE2 システム

BEE2 システム内の各演算モジュールは、240 ピンの DDR2 DRAM DIMM 4 個に直接接続されたザイリンクスの Virtex™-II Pro 70 FPGA チップを 5 個搭載しており、FPGA 1 個あたり 4GB の最大容量を保持します。このデザインは、それぞれ 72 ビットのデータインターフェイスを持ち 200MHz (400 DDR) で動作する 4 本の独立した DRAM チャネルに 4 枚の DIMM を接続したものです。したがって、総メモリバ

ンド幅は FPGA 1 個あたり最大 12.8 Gbps となります。各モジュールは演算に 4 個の FPGA、制御に 1 個の FPGA を使用します。制御用 FPGA は、各ユーザー FPGA における演算プロセスを管理するためエンベデッド PowerPC 405 上で Linux OS を走らせると共に、モジュールの動作全体をモニタリングします。

図 2 に示すように、4 個のユーザー FPGA は 2D グリッド上で直接接続されており、それぞれのリンクは 40Gbps 以上のデータスループットを提供します。制御用 FPGA から各演算 FPGA につながる 4 本のダウンリンクは、リンクあたり最大 20 Gbps です。モジュール外の接続はすべて FPGA 上の MGT を使い、10 ギガビットの Base-CX4 イーサネットインターフェイスに 4 チャネル結合されます。各 BEE2 モジュールには、制御用 FPGA から 2 つ、4 つの演算 FPGA からそれぞれ 4 つ、合計 18 の CX4 インターフェイスがあり、全部で 180Gbps の全二重バンド幅となります。多くの演算モジュール間でランダムに通信するため、高いバイセクションハンド幅を必要とするアプリケーションの場合、BEE2 システムを市販の 10 ギガビットイーサネットスイッチに直接接続できます。さらに、制御用 FPGA 上の 10 または 100 Base-T イーサネットは、ユーザーインターフェイス、低速のシステム制御、モニタリング、およびデータアーカイビング用として、アウトオブバンドの通信ネットワークを備えています。

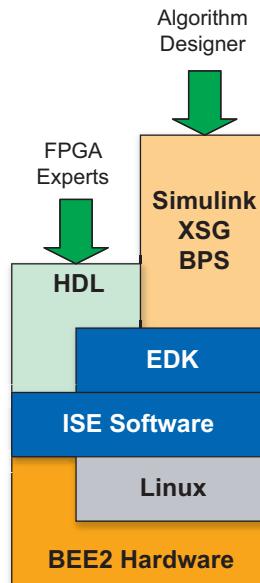

## BEE2 DSP プログラミング環境

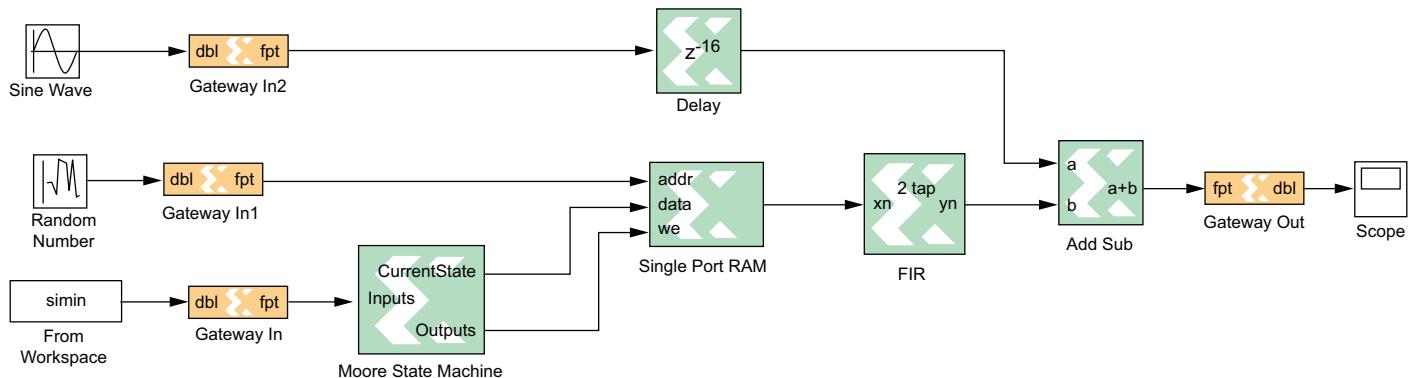

過去 10 年間で、特に DSP ドメインにおいて、ブロックダイアグラムをベースとするアルゴリズム記述メソッドが一般化してきました。The MathWorks Simulink などのソフトウェアシミュレーション環境は、DSP データフロー処理の特性にマッチする並列型のデータフロー実行モデルを提供します。ドメイン特有の高レベルなブロックライブラリが豊富に用意されていることから、アルゴリズム設計者は複雑な DSP システムと通信システムを簡単に構築できます。ザイリンクスの System Generator for DSP ツール

を使用することにより、Simulink の modeling とシミュレーションの機能を拡張して、コア DSP アルゴリズムを FPGA インプリメンテーションに直接マッピングできます。

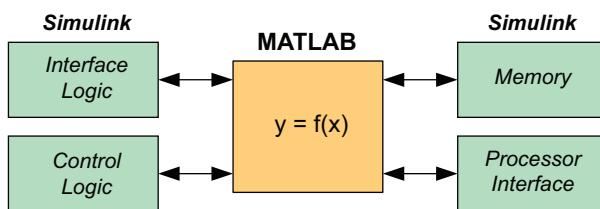

とはいっても、ほとんどの DSP デザインはコア アルゴリズムだけでは済まないのが現実です。最新世代のザイリンクス FPGA では、ネットワーク インターフェイスやエンベデッド マイクロプロセッサ、メモリ、I/O デバイスなど、多数のシステムレベル コンポーネントを 1 個の FPGA に直接集積化できます。FPGA のデザインは、こうしたハードウェア サブシステムからなる単なるハードウェア デザインではなく、ハードウェアとソフトウェアの両方からなるデザインになったのです。ここで言うソフトウェアとは、複雑な OS とアプリケーションを指します。

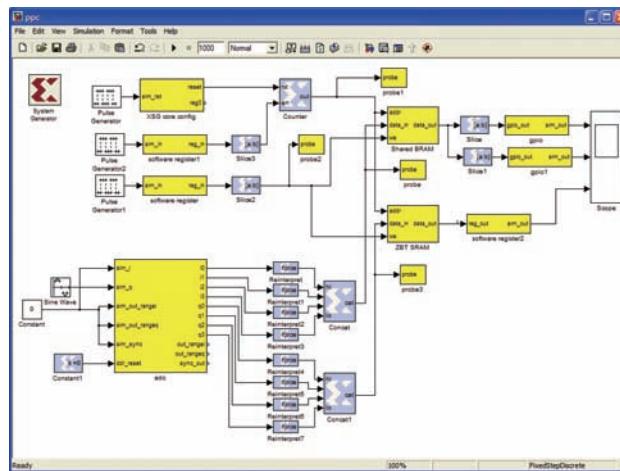

図 3 に示す、BEE Platform Studio (BPS) という BEE2 DSP プログラミング環境は、Simulink に先進の FPGA ハードウェア/ソフトウェア コデザインの複雑さを抽象化する統合型デザイン環境を提供します。この環境は、BEE2 プラットフォーム専用に作られています。BPS は複雑なハードウェア/ソフトウェア サブシステムに対するコードとビット ファイルを自動的に生成し、アルゴリズム設計者はコア DSP アルゴリズムに専念できます。BPS はザイリンクスの既存のツール フロー上に構築されています。ザイリンクスの System Generator for DSP は DSP アルゴリズムをマッピングするための卓越したブロック セットを提供し、Embedded Developers Kit (EDK) はマイクロプロセッサとシステムを統合し、ISE™ ソフトウェアはハードウェアに対するロジック合成、配置/配線、ビット生成のためのバックエンドを提供します。

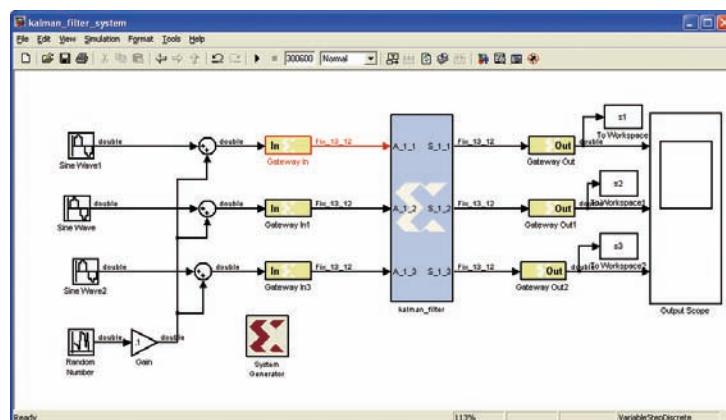

一般に、BPS デザイン環境で最初に着手するのは、ザイリンクスの System Generator for DSP を用いて Simulink でコア アルゴリズムをデザインすることです。エンドユーザーの視点から見ると、Simulink のデザインは同期的なデータ フロー実行モデルを持つ理想化されたサンドボックスに存在し、コア アルゴリズム以外の接続はすべて BPS インターフェイスのブロック セットを通して仮想マッピングされます。図 4 に代表的なデザインを示します。BPS ブロック

セットは、汎用の XSG「ゲートウェイ」を Simulink 内のコア アルゴリズム デザインとシステムレベル デバイス間のインターフェイスとして置き換えるため、FPGA の専門家が作成したものです。

プロセッサ コアは、ハード コア (PowerPC 405) またはソフト コア (MicroBlaze™ プロセッサ) のいずれかで、すべての BPS デザインに含まれています。プロセッサ コアは、ソフトウェア レジスタ、FIFO、共有メモリを通してユーザーの XSG デザインと通信できます。ユーザーは、Simulink で該当する BPS ブロックを選択することでいずれかの通信方法を指定できます。外部のネットワーク、I/O、およびメモリ デバイスは、シンプルな FIFO 抽象化を用いて、すべて Simulink のデータソースもしくはデータシンクに抽象化されます。

BPS フレームワークは、サポートされている各 FPGA ボード プラットフォームに対して、Xilinx Platform Studio (XPS) プロジェクトとしてベースシステム パッケージと、すべての外部デバイスに対して該当する Simulink BPS ブロック セットを提供します。各ベースシステム パッケージには、基本的なシステム デバイス IP コア、ハードウェア システムの初期構成、利用できるソフトウェア パッケー

ジが含まれています。ユーザーが選択する外部デバイス用のバックエンド インプリメンテーション ファイルは、BPS ツールによってベース パッケージ上に動的に生成されます。その後、これらのファイルを組み合わせて、必要なすべてのハードウェア接続およびソフトウェア デバイス ドライバにリンクさせます。

## アルゴリズムの概要

通常、電波天文学は宇宙で発生した大昔の現象を観測します。このため、地上に到達する電波は基本的に平面波です。お互いに離れた 2 台以上の電波望遠鏡で同じ現象を観測する場合、アンテナの場所によって入角が異なるため、各アンテナは同じ波面を別々のタイミングで受信することになります。相関処理による電波天文学の画像処理とは、異なる場所、つまり異なる遅延値で受信した電波信号を相関処理することで、波面を再構築するという考え方に基づいています。

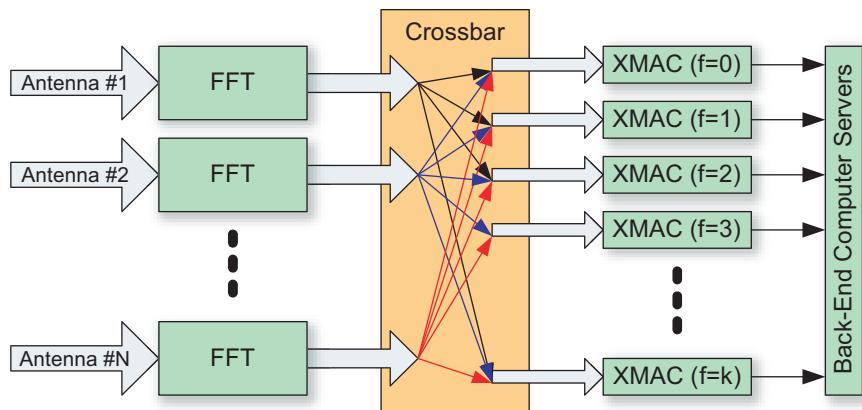

アンテナの数が膨大な場合、一般に演算効率に優れている FX 相関器が使われます。各アンテナの信号は最初に FFT (高速フーリエ変換) を通して周波数ドメインに変換されます。次に、いくつかのアンテナの信号がそれぞれの周波数チャネルに対して個別に積和

図 2 演算ノードのコネクティビティ

演算 (MAC) されます。図 5 に、この基本的な相関器システムを示します。MAC 演算の数は、周波数チャネルの総数にかかわらず、入力サンプルあたり 1 つです。FX 相関器における FFT 演算は、アンテナの総数に関連して  $N \log_2(N)$  として増加し、また MAC 演算は  $1/2 N (N \pm 1)$  として増加します。

相関アルゴリズムの最初のステップは、アンテナからのアナログ信号をデジタル化し、その後周波数がデジタル信号を周波数ドメインに変換します。これは F エンジンともいいます。1 GSPS での I/Q デジタル化後、デジタル信号の各入力を目的のバンドにチューニングするためデジタル ダウン コンバージョン (DDC) ブロックが使われ、さらにブリッジルタリングと FFT のためのポリフェーズ フィルタ バンク (PFB) へと続きます。入力信号の信号対ノイズ比 (SNR) が 1 未満であることから、相関演算とネットワーク バンド幅の利用効率を高めるため、PFB の出力は低精度の固定点数（この場合は実 4 ビットと架空 4 ビット）に量子化されます。最後に、パケット フォーマッタが各ビンに対する多数の周波数データを 1 つのパケットに収集し、10 ギガビットのイーサネット インターフェイスを通してタイム スタップが伝送されます。

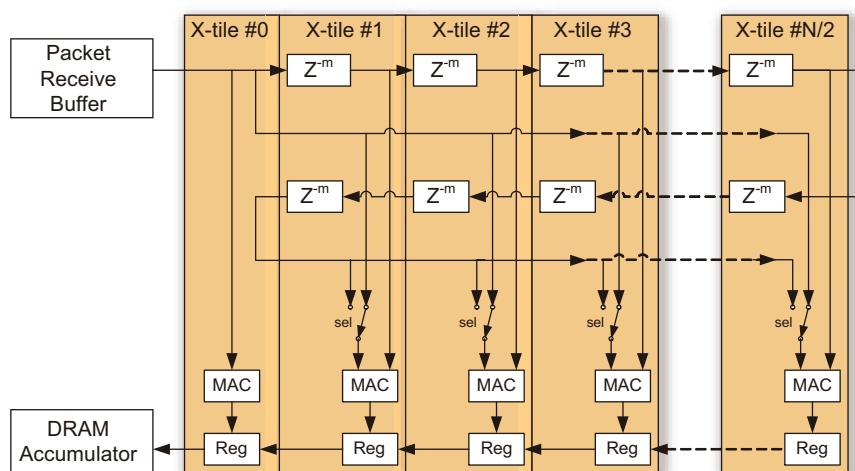

最も効率的な X エンジン インプリメンテーション スキームの 1 つは、図 6 に示すように、線形遅延チェーン上の各アンテナからのデータ パケットを相互相關処理するため、タイル構造を使います。N アンテナ システムでは、各 X エンジンはちょうど N 遅延素子を含んでおり、それぞれ深さは  $m$  データ サンプル、また各パケット内の  $m$  データ サンプルに対応します。MAC ユニットの  $N/2$  番は相互相關を演算し、自動相関用として 1 つの専用 MAC を備えています。各 MAC ユニット上の乗算器は、遅延チエーン上の最初と最後のデータ パケット間にある入力を 1 つ選択します。

データ パケットはアンテナ順にパケット受信バッファを離れ、遅延チエーンに沿ってシフトしながら MAC ユニット上で相関処理されま

図 3 BEE2 Platform Studio のデザイン抽象化

図 4 BPS のデザイン例

す。結果は DRAM コントローラへと左シフトされて長期にわたり蓄算されます。

すべての  $1/2 N (N \pm 1)$  相関処理は、データ パケット内の特定周波数チャネルに対して、ちょうど  $N$  タイム ステップ (各タイム ステップは  $m$  クロック サイクル) 単位で演算されます。タイル ベースの X エンジン デザインにより、1 つの X エンジンを複数の物理的 FPGA チップに簡単にパーティション化できます。また、複数の隣接するタイルを各 FPGA にグループ化できると共に、FPGA から別の FPGA へと単にデータ ストリームを流すこ

とができます。二重偏波アンテナを相關処理する場合、各 MAC ユニットは Stokes パラメータすべてをパラレル演算することから、クロック サイクルあたり 4 つの複素乗算器、つまり 16 の乗算と 8 つの加算が必要とします。最後に、長期的な累算のため DRAM にシフトされる前に、4 つの複素項 (8 つの実数項) が  $m$  回累算されます。

## スケーラビリティ

従来、FX 相関器のインプリメンテーションは、F エンジンから X エンジンまでクロスバーで接続するようバックプレーンとケーブルを直接配線していたため、ハードウェア システム全体をグローバルに同期化する必要がありました。システムのスケーラビリティが制限されました。新しいインプリメンテーションでは、各周波数データ パケット上のタイム スタップは

演算ハードウェア クロックから絶対サンプル時間を効果的に分離し、関連パケットが到着したときに X エンジンの演算をすべて処理できます。したがって、ハードウェアで接続したバックプレーンを使うことなく、仮想クロスバーとしてパケット レイテンシの異なる商用ネットワーク スイッチを使用できるのです。

LTX インプリメンテーションは、データレート 250MHz の BEE2 FPGA 1 個に 256 アンテナの X エンジン デザインを収容できます。グローバルな制御インターフェイスとメモリ インターフェイスを含むロジック スライスの総利

用率は、高クロックレートの配線用に十分な余裕を確保するため、最大スライスの 80% 程度に維持されます。それぞれ LTX タイルの 4 分の 1 をインプリメントする 4 つのユーザー FPGA チップをチエーン化することで、1 枚の BEE2 ボードに 1,024 アンテナの X エンジンをインプリメントできます。入力バッファは、外部 DRAM を用いて中央の制御 FPGA にインプリメントする必要があります。データ パケットにつき 256KB の場合、周波数ビンあたり 1 枚の 1GB DIMM に 4,096 の周波数ビンに相当するデータを格納

# 高価なEDAツールに 悩まされていませんか？

## アルデックで問題解決!!

- 高速RTL、ゲート、タイミングシミュレーション

- Verilog、VHDL、SystemVerilog、SystemC、C、EDIF、MATLAB

- 国内WANライセンス、サーバーフームテクノロジ

- STRAC RTLスタイルガイド準拠Lint機能

- 23年間の開発経験と30,000ライセンスの出荷実績

資料請求、無償評価ライセンスのお申込みは下記webから

アルデック・ジャパン株式会社

東京都新宿区新宿2-4-3 フォーシーズンビル8F

TEL:03-5312-1791 FAX:03-5312-1795 Email:info@aldec.co.jp

<http://www.aldec.co.jp>

**ALDEC**

*The Design Verification Company*

し、F エンジンから 10 ギガビット イーサネット スイッチを通して最大 2 秒以上の遅延変動が可能となります。

10 ギガビット イーサネット スイッチのバンド幅は、システム内のアンテナの本数に比例して増加します。X エンジンと F エンジンの数は同じであるため、クロスバー スイッチは、基本的に F エンジンから対応するそれぞれの X エンジンに、周波数ビンに従って出力データ パケットを再送します。一回のタイム ステップで、F エンジンの出力パケットを固有の X エンジンに 1 対 1 で個別に伝送できます。各アンテナから周波数ビンをラウンドロビン方式でローテーションすることで、クロスバー スイッチにおける長期的な混雑から保護できます。元々すべての F エンジンは ADC ボードで使われている同じサンプリング クロック

に同期化されるため、一時的なパケット混雑でもめったに起こることはありません。

## 結論

これまで、4 つの BEE2 モジュールを採用した Allan Telescope Array の 200 MHz バンド幅、32 アンテナの相関器など、このソリューションを用いていくつかの相関器を展開してきました。また、西バージニア州グリーン バンクをはじめとする世界中の電波天文プロジェクトでは、16 アンテナの相関器を使っている天文学者もいます。

相関器は全体を BEE Platform Studio 環境を用いてデザインしたため、今後、ザイリンクスの Virtex-5 FPGA を使う BEE3 システムなど、将来の FPGA ハードウェア プラ

ットフォームに移植する際、Simulink のデザインから新しいハードウェア プラットフォームを再コンパイルするだけで済みます。Virtex-5 FPGA は半分の価格で 4 倍以上の演算スループットを達成できることから、8,000 本以上のアンテナを持つ 1 平方キロメートルの集光面積を得るには、デザインを迅速にマイグレーションできることが重要です。

UC Berkeley での 6 年以上に及ぶ研究の末、高性能 DSP から他のバイオインフォマティクスにいたるまでさらに幅広いアプリケーションをサポートすべく、BEECube というベンチャー企業が BEE2 関連のソフトウェアとハードウェアの開発成果を商品化しました。プログラミング環境とハードウェア システム開発の詳細は、Chen Chang (chen@beecube.com) までお問い合わせください。

図 5 N アンテナ周波数分割 FX 相関器の概要

図 6 線形のタイル ベース X エンジン（概略図）

BEE2 プロジェクトの電波天文学を対象とする開発は、UC Berkeley Space Science Laboratory (Dan Werthimer, Aaron Parsons, Henry Chen) および UC Berkeley Radio Astronomy Laboratory (Melvyn Wright, Dave MacMahon, Matt Dexter, Don Backer) にて、SETI@Home および Serendip (Search for Extraterrestrial Radio Emissions from Nearby Developed Intelligent Populations) プロジェクトと共同で進められています。ザイリンクスはこの開発に、FPGA、ソフトウェア ツール、エンジニアリングの面で貢献しています。

BEE2 チームの学生およびスタッフの Pierre-Yves Droz, Greg Gibeling, Nan Zhou, Yury Markovskiy, Zohair Hyder, Adam Megacz, Alexander Krasnov, Hayden So, Kevin Camera, Brian Richards, Dan Burke, Ken Lutz, Susan Mellers の各氏には、この場を借りて謝意を表します。BEE2 プロジェクトは、FCRP の GSRC と C2S2 フォーカス センター、Semiconductor Research Corporation のプログラム、National Science Foundation の助成金 # CNS-0551739 と CNS-0403427、ならびに BWRC とそのスポンサー企業により資金供与されています。

# Prototyping Applications with the Spartan-3A DSP Starter Platform

# Spartan-3A DSP スタータ プラットフォーム を用いたプロトタイプ製品の開発

低コスト開発を容易にするEXP 拡張インターフェイスを備えた

ザイリンクスの新しいスタータ プラットフォーム

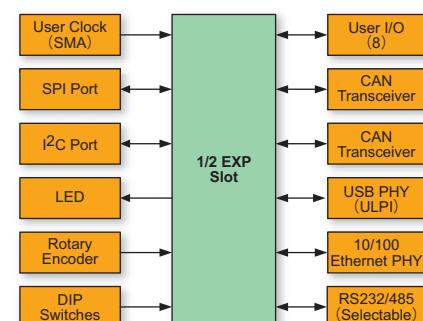

Jim Beneke

Vice President, Global Technical Marketing

Avnet

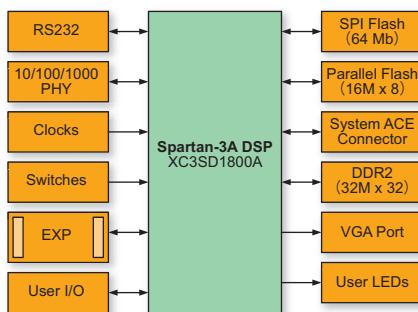

jim.beneke@avnet.com