DSP ソリューション

- テクノロジ

- DSP

柔軟性に優れた AMD アダプティブ SoC は、ハードウェアの並列性を利用する高性能/マルチチャネル デジタル信号処理 (DSP) アプリケーションに最適です。AMD アダプティブ SoC では、このプロセッシング帯域幅を実現できると同時に、ハードウェア設計者、ソフトウェア開発者、システム設計者が使いやすい設計ツールなどを含む包括的なソリューションを利用できます。

ハードウェアの並列性

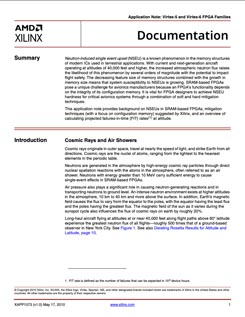

一般的なノイマン型 DSP アーキテクチャは、256 タップ FIR フィルターを実行するのに 256 サイクルが必要ですが、AMD アダプティブ SoC や FPGA では 1 クロック サイクルで同じ結果を達成できます。

この大規模な並列性により、非常に高いレベルの DSP 性能が実現します。

- 49.5 TeraMAC (固定小数点 8 ビット)

- 23.1TeraFLOP (単精度浮動小数点)

包括的な DSP ソリューション

AMD の DSP ソリューションには、ワイヤレス通信、データ通信、データセンター、航空宇宙/防衛など広範な市場のさまざまなアプリケーションをサポートするシリコン、IP、リファレンス デザイン、開発ボード、ツール、資料、トレーニングが含まれます。

包括的な開発フロー

異なる使用モデル、異なるデザインの抽象化レベルに対応するさまざまなツール フロー:

ハードウェア設計者は次の環境での設計が可能:

- Vivado™ Design Suite を使用する RTL およびシステム レベル デザイン

- C/C++

- Vitis™ Model Composer を使用する Matlab® および Simulink®

C/C++ を使用する開発環境に慣れているソフトウェア開発者は、次の環境での設計が可能:

システム アーキテクト は次の環境で新しいアルゴリズムの迅速な評価が可能:

- Matlab/Simulink 環境でのシステム モデリングに最適な Vitis Model Composer

- C または C++ でのアルゴリズムの評価に最適な Vitis HLS

AMD アダプティブ SoC および FPGA を利用する場合、DSP アプリケーションを運用するには設計アプローチやデザインの抽象化レベルに依存するさまざまなフローがあります。

ASIC クラスのアーキテクチャを採用している AMD の FPGA およびアダプティブ SoC は、Versal™ プレミアム シリーズでは 49 TeraMAC 以上の固定小数点 DSP 性能と数百 Gbps の I/O 帯域幅を提供します。最新世代 AMD FPGA で実現できる DSP 性能の鍵となるのは、AMD の DSP スライスとその並列性です。

DSP スライスのアーキテクチャ

Versal デバイス スライス DSP58 は、AMD アーキテクチャで 6 世代目の DSP スライスです。

業界一の消費電力と性能を実現するために、この専用 DSP プロセッシング ブロックがフルカスタムのシリコンにインプリメントされるため、乗算累算 (MACC)、乗算加算 (MADD)、または複素乗算などの一般的な DSP 機能を効率的に実装できます。

また、このスライスは、AND、OR、XOR などさまざまなロジック動作を実行する機能も提供します。

Versal デバイス DSP58 アーキテクチャは、実績ある UltraScale™ FPGA DSP48E2 をベースとして構築され、機能が強化されたものです。

- よりビット幅の広い乗算器 (27 x 24 ビット)

- 単精度浮動小数点乗算器

- 2 つの連続する DSP を使用した 18x18 複素乗算

- DSP58 の INT8 ベクター ドット積モード

これらの機能強化によって、DSP のパフォーマンスを重視するアプリケーションでは FPGA ファブリックの消費を抑えてDSP48E2 スライス内で多くの演算を実行できるため、結果的にリソースや消費電力を削減できます。

DSP48E2 (UltraScale) と DSP58 (Versal) スライスの機能比較

| 機能 | UltraScale | Versal |

|---|---|---|

| DSP タイル/スライスの種類 | DSP48E2 | DSP58 |

| 複数の加算/減算/累算動作 |  |

|

| 乗算/MACC | 27x18 | 27x24 |

| 2 乗: [(A or B) +/- D] |  |

|

| WMUX フィードバックを使用する超高効率な複素乗算 CMACC | 3 x DSP48E2 | 2 x DSP58 |

| SIMD サポート |  |

|

| 統合されたパターン検出回路 |  |

|

| ILU (Integrated Logic Unit) |  |

|

| ワイド MUX 機能 | 48 ビット | 58 ビット |

| ワイド XOR | 96 ビット | 116 ビット |

| 単精度浮動小数点乗算器 |  |

|

| オプションの 96 ビット出力 |  |

|

| カスケード配線 |  |

|

| パイプライン レジスタ |  |

|

| D 前置加算器 |  |

|

| シーケンシャル複素乗算、AB ダイナミック アクセス |  |

|

| AB レジスタのパイプライン バランシング向上 |  |

|

ツールとフロー

AMD は、ユーザーの好みに合わせて RTL、C/C++、およびモデルベースのデザイン入力に対応するさまざまなツールを提供しています。この柔軟な設計フローで広範な DSP IP カタログを活用することで、AMD のツールやデバイスの適用がよりスムーズになります。

詳細は、ツール、ライブラリ、フレームワークを参照してください。

DSP 性能の測定基準

次の表に 7 シリーズ、UltraScale、および UltraScale+ ファミリの主な DSP 性能の測定基準を示します。SoC デバイスのパフォーマンスは、ソフトウェア開発者のセクションを参照してください。

| Kintex UltraScale | Kintex UltraScale+ | Virtex UltraScale | Virtex UltraScale+ | Versal AI コア | Versal AI エッジ | Versal AI プライム | Versal AI プレミアム | |

|---|---|---|---|---|---|---|---|---|

| システム ロジック要素 (K) | 318–1,451 | 356–1,143 | 783–5,541 | 862–3,780 | 540 - 1,968 | 44 - 1,139 | 329 - 2,233 | 833 - 7,352 |

| DSP スライス | 768–5,520 | 1,368–3,528 | 600–2,880 | 2,280–12,288 | 928 - 1,968 | 90 - 1,312 | 464 - 3,984 | 1,140 - 14,352 |

| 27x18 乗算器 | 768–5,520 | 1,368–3,528 | 600–2,880 | 2,280–12,288 | 928 - 1,968 | 90 - 1,312 | 464 - 3,984 | 1,140 - 14,352 |

| INT8 GOPs (1) | 1,774–14,315 | 4,263–11,000 | 1,554–7,469 | 7,108–38,318 | 6,403 - 13,579 | 62 - 9,052 | 3,201 - 27,489 | 7,866 - 99,029 |

| INT16 GOPs | 1,014–8,180 | 2,436–6,286 | 888–4,268 | 4,062–21,896 | 2,134 - 4,526 | 21 - 3,017 | 1,067 - 9,163 | 2,622 - 33,010 |

| Complex INT18 GOPs | 676 - 5,453 | 1,624 - 4,191 | 592 - 2,845 | 2708 - 14,597 | 913 - 1,937 | 8 - 1,291 | 456 - 3,920 | 1,122 - 14,122 |

| 320–2,685 | 800–1,673 | 294–1,411 | 1,354–7,299 | 1,494 - 3,168 | 14 - 2112 | 747 - 6,414 | 1,835 - 23,107 |

注記 :

- WP486 – 『AMD デバイスでの INT8 に最適化した深層学習の実装』

- UltraScale+ DSP スライスを 3 つ使用する Floating Point Operator コアを使用した場合の半精度浮動小数点のパフォーマンス

AMD は、ソフトウェア開発環境と使い慣れた優れたツール、ライブラリ、設計手法を含む包括的なソリューションを提供しているため、ソフトウェア開発者は AMD FPGA および SOC をターゲットとする開発を簡単に始めることができます。Vitis™ 統合ソフトウェア プラットフォームの抽象レベルの高い開発環境を提供する AMD は、C、C++、OpenCL 開発に対応する GPU と同様の使い慣れたエデッド アプリケーション開発とランタイムを提供できます。

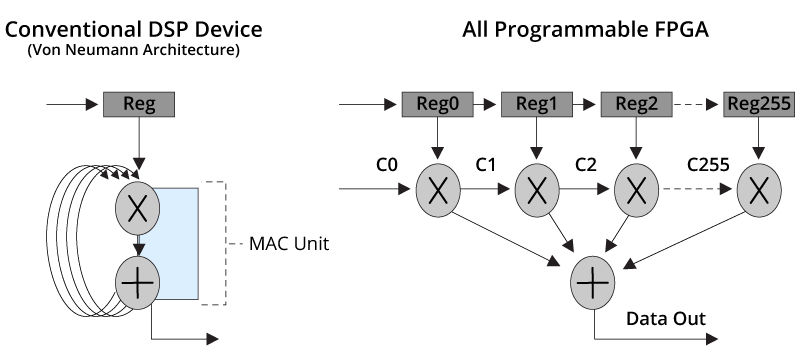

AMD の MPSoC および Versal デバイス

Zynq™ UltraScale+™ MPSoC および Versal アーキテクチャは、単一デバイスに ARM® Cortex® プロセッサとユーザー プログラマブル ロジック (PL) を統合したパワフルなプロセッシング システムを提供します。

アクセラレーションのアプリケーション プロファイリング

Vitis 統合ソフトウェア プラットフォームでは、指定したアプリケーションのプロファイリングが可能なため、プログラマブル ロジック (PL) で動作をより効率化させるためのハードウェア アクセラレータを作成できます。FPGA の柔軟性と並列性によって大幅な性能向上を期待できます。また、必要に応じて、プロセッシング システム (PS) でアプリケーションのほかの機能を同時に実行することもできます。

AMD の FPGA やアダプティブ SoC をターゲットにすることによって、多くの DSP およびエンベデッド アプリケーションで、アプリケーションの効率が向上し、消費電力が削減されます。

AMD SoC デバイスの機能および DSP 性能

次の表に、AMD の AMD Zynq UltraScale+ MPSoC ファミリおよび Versal デバイスの主な機能と DSP 性能の測定基準を示します。SoC 以外のデバイスのは、ハードウェア設計者のセクションを参照してください。

| プロセッシング システム | Zynq 7000 SoC | Zynq UltraScale+ MPSoC |

|---|---|---|

| アプリケーション プロセッシング ユニット (APU) |

|

|

| リアルタイム プロセッシング ユニット |

- |

|

| マルチメディア処理 | - |

|

| ダイナミック メモリ インターフェイス | DDR3、DDR3L、DDR2、LPDDR2 | DDR4、LPDDR4、DDR3、DDR3L、LPDDR3 |

| 高速ペリフェラル | USB 2.0、Gigabit Ethernet、SD/SDIO | PCIe® Gen2、USB3.0、SATA 3.1、DisplayPort、Gigabit Ethernet、SD/SDIO |

| セキュリティ | RSA、AES、SHA、Arm TrustZone® | RSA、AES、SHA、Arm TrustZone |

| 最大 I/O ピン数 | 128 | 214 |

| プログラマブル ロジック | Zynq 7000 SoC | Zynq UltraScale+ MPSoC |

|---|---|---|

| システム ロジック要素 (K) | 23–444 | 103–1,045 |

| 最大メモリ (Mb) | 1.8–26.5 | 5.3–70.6 |

| 最大 I/O ピン数 | 100–362 | 252–668 |

| DSP スライス | 60–2,020 | 240–3,528 |

| 18x18 乗算器 | 60–2,020 | 240–3,528 |

| 固定小数点のパフォーマンス (GMACs)(1) | 42–1,313 | 213–3,143 |

| 対称フィルターの固定小数点のパフォーマンス (GMACs) | 84–2,626 | 426–6,286 |

| INT8 GOPs (1) (3) | 84–2,626 | 745–11,000 |

| INT16 GOPs (1) | 84–2,626 | 426–6,286 |

| 単精度浮動小数点 (GFLOPs)(1) (4) | 23–716 | 142–1,673 |

| 単精度浮動小数点 (GFLOPs)(1) (5) | 17–537 | 106–1,571 |

| 半精度浮動小数点 (GFLOPs) | 34–1,074 | 212–3,142 |

注記 :

- すべてのパフォーマンス計算は、Zynq 7000 SoC で -2 スピード グレード、Zynq UltraScale+ MPSoC で -3 スピード グレード

- 前置加算器を使用した場合、対称フィルターの DSP 性能が 2 倍向上

- WP486 – 『AMD デバイスでの INT8 に最適化した深層学習の実装』を参照 (Zynq デバイス以外)

- DSP スライスを 3 つ使用する Floating Point Operator コアを使用した場合の半精度浮動小数点のパフォーマンス

- DSP スライスを 4 つ使用する Floating Point Operator コアを使用した場合の半精度浮動小数点のパフォーマンス

- DSP スライスを 2 つ使用する Floating Point Operator コアを使用した場合の半精度浮動小数点の

AMD SoC および MPSoC の詳細は次のリンクを参照:

プロセッシング サブシステムの DSP

プロセッシング システム (PS) は異なる ARM プロセッシング コアを使用して DSP 処理機能を提供します。

ARM プロセッサの DSP 機能の詳細は次のリンクを参照:

- Cortex-A シリーズ ファミリ

- SIMD および Advanced SIMD (NEON) テクノロジ

- ARM 浮動小数点アーキテクチャ

次のリンクから、役に立つ例を参照できます。

Zynq UltraScale+ MPSoC で、ARM NEON 命令セットを使用する FFT について説明しています。UG1211

Zynq 7000 SoC で、Cortex-A9 および ARM SIMD をターゲットとする場合、Xilinx Wiki で次のテクニカル ヒントを提供しています。

AMD のデータ タイプ サポート

AMD の デバイスでは非常に柔軟にデータ タイプがサポートされています。AMD ツールでは、固定小数点、浮動小数点、および整数のさまざまな精度がネイティブ サポートされており、浮動小数点演算子は、Floating Point Operator IP コアを使用して実装されます。

FPGA に実装される浮動小数点デザインは、固定小数点や整数の実装と比べて、リソースの使用量と消費電力が高くなります。可能であれば固定小数点ソリューションに変換することで、次のような大きなメリットが得られます。

- FPGA リソースが削減

- 消費電力が削減

- コスト削減

浮動小数点から固定小数点へデータ タイプを変換するメリットの詳細は、WP491 を参照してください。

ベンチマーク

以下の表は、AMD のデバイス、つまりプログラマブル ロジック (PL) のファブリックを使用してデザインを加速する場合の少ないアルゴリズムの選択肢とパフォーマンスの向上を示しています。

| アルゴリズム | CPU/GPU | Zynq UltraScale+ MPSoC | アドバンテージ |

|---|---|---|---|

| Stereo LocalBM @ 2K | ARM: 0.5 FPS/Watt nVidia: 3.5 FPS/Watt |

146 FPS/Watt | 292x 42x |

| オプティカル フロー (Lucas-Kanade) |

ARM: 0.1 FPS/Watt nVidia: 0.8 FPS/Watt |

7.1 FPS/Watt | 9.3x |

| GoogleNet (Batch=1) |

ARM: 0.1 Imgs/s/w Nvidia: 8.8 Imgs/s/w |

53 Imgs/s/w | 530x 6x |

注記 1: ARM: Quad-core A53 は 1200 MHz のRaspberry Pi で動作

注記 2: Nvidia ベンチマークは、Tegra X1 を使用して実行

注記 3: オプティカル フロー (LK) – ウィンドウ サイズ 11x1

| アルゴリズム | CPU/DSP | Zynq 7000 | アドバンテージ |

|---|---|---|---|

| フォワード プロジェクション (順投影) | ARM: 3 sec/view | 0.016 sec/view | 188x |

| 動き検出 | ARM: 0.7 FPS | 67 FPS | 90x |

| ノイズ除去 (ソーベル) | ARM: 1 FPS | 67 FPS | 60x |

| キャニー エッジ検出 | ARM: 0.66 FPS | 40 FPS | 45x |

| 3D 画像再構成 | ARM: 75k | 8k | 9x |

| DPD | ARM: 506 ms | 31.3 ms | 16x |

| FIR | TI DSP: 64020 ns | 1200 ns | 53x |

| FFT | TI DSP: 1036 ns | 128 ns | 8x |

注記 1: Cortex-A9 コアは、ARM をターゲットとする Zynq デバイスでのみ使用される

注記 2: TI ベンチマークは、C66 DSP コアを使用して実行

Vitis Model Composer for DSP や HLS (高位合成) などの AMD の高度な設計ツールは、システム設計者や各分野の専門家が新しいアルゴリズムをすばやく評価し、デザインの差別化に集中できるようサポートする、抽象レベルの高い環境を提供します。包括的な AMD DSP ソリューションは、これらのデザインツール、IP、リファレンスデザイン、メソドロジ、およびボードを組み合わせることで、できるだけ短期間にプロダクション デザインを完成させることができます。

Vitis Model Composer は、従来の RTL 開発にかかる数分の一の時間でプログラマブル ロジックの量産品質 DSP アルゴリズムを定義、テスト、および実装するために、MATLAB や Simulink 環境を利用するモデル ベースの設計ツールです。

ツールが提供するもの:

- 最適化された 100 以上の DSP ブロック (RTL よりシミュレーションが 2 ~ 3 倍高速化する C シミュレーション モデルがある)

- DSP システムの RTL、IP、Simulink、MATLAB、C/C++ コンポーネントが統合

- ビットおよびサイクル精度の高い浮動小数点/固定小数点シミュレーション

- シミュレーションを高速化し、実際のハードウェア上でアルゴリズムを評価するためのハードウェア協調シミュレーション

- Simulink モデルからパッケージ化された IP や低レベル HDL の自動コード生成

- HDL テストベンチの自動生成 (テスト ベクターを含む)

Vivado System Generator for DSP の詳細は、次のリンクを参照:

- Vitis Model Composer の概要 (ビデオ)

- Vitis Model Composer (資料)

高位合成

Vitis 統合ソフトウェア プラットフォームに含まれる HLS (高位合成) ツールを使用して、移植可能な C、C ++、および System C アルゴリズムの仕様を RTL を作成することなく AMD の FPGA やアダプティブ SoC に直接実装できます。C/C++ から異なるプロセッサ アーキテクチャへのコンパイラと同様に、HLS コンパイラは C/C++ から AMD FPGA およびアダプティブ SoCへ同等の機能を提供します。

Vivado HLS の詳細は、次のリンクを参照:

- Vitis 高位合成の入門ガイド (ビデオ)

- Vitis 高位合成ユーザー ガイド (資料)

ツール

AMD は、AMD の FPGA またはアダプティブ SoC 上でデジタル信号処理 (DSP) アプリケーションを効率的かつ低消費電力で実装するためのクラス最高のツールを提供しています。以下の AMD ツールは、RTL、C/C++/SystemC、または Matlab/Simulink のいかなる言語を使用する場合でも、DSP 設計を容易にし、市場投入までの時間を短縮します。

ライブラリとフレームワーク

AMD は、性能、リソースの利用率、使いやすさを考慮して最適化された豊富なライブラリを提供しています。

| ライブラリ & フレームワーク | 説明 |

アプリケーション |

|---|---|---|

| GitHub リポジトリ | AMD は GitHub リポジトリを作成し、DSP 関連機能を含むさまざまなアプリケーションに役立つサンプル コードを提供しています。 | |

| Vitis アクセラレーション ライブラリ | 既存のアプリケーションにわずかなコード変更を加えるだけですぐに高速化を実現できる、性能に最適化されたオープンソース ライブラリを多数提供しています。 | Vitis ライブラリ |

パートナーのボードおよびキット

AMD とパートナー企業は、さまざまな市場分野の DSP アプリケーションで AMD の FPGA/SoC を簡単に適用できるようにするためにツールやボードを提供しています。

| パートナー | 説明 | 選択 |

|---|---|---|

| Avnet 社の DSP 中心の開発キットとモジュール | MathWorks 社、および高速アナログ サプライヤーとの長年にわたる協力により、Avnet 社は DSP 中心の開発キットとエンベデッド ビジョン、ソフトウェア無線および高性能モータ制御向けのプロダクション対応システムオンモジュール (SOM) を提供しています。 |

アヴネット社 |

| Mathworks 社のコンピューティング ソフトウェア | Mathworks 社の MATLAB®/Simulink® は、アダプティブ SoC や FPGA ベースのシステム開発時間を大幅に短縮できます。ユーザーは次のことが可能になります。

|

Mathworks 社 |

| Analog Devices 社のアドオン ボード | AD-FMCDAQ2-EBZ FMC ボードは、操作が簡単な自己完結型のデータ アクイジションおよび信号合成プロトタイピング プラットフォームで、エンド システムの信号処理開発を迅速に行うことができます。

|

Analog Devices 社 |