適応性のあるハードウェア

ワークロードに合わせてプラットフォームを最適化し、

進化するアルゴリズムやアプリケーション要件に適応させることが可能です。

リアルタイム性能

超並列処理により、高スループット、高いワットあたりの性能、低レイテンシを実現できるため、リアルタイム アプリケーションに最適です。

すべての開発者が利用可能、

オンプレミスにもクラウドにも最適

従来型 FPGA フローとソフトウェア開発フローをサポートし、オンプレミスやクラウドで簡単に利用できます。

データセンター アプリケーション

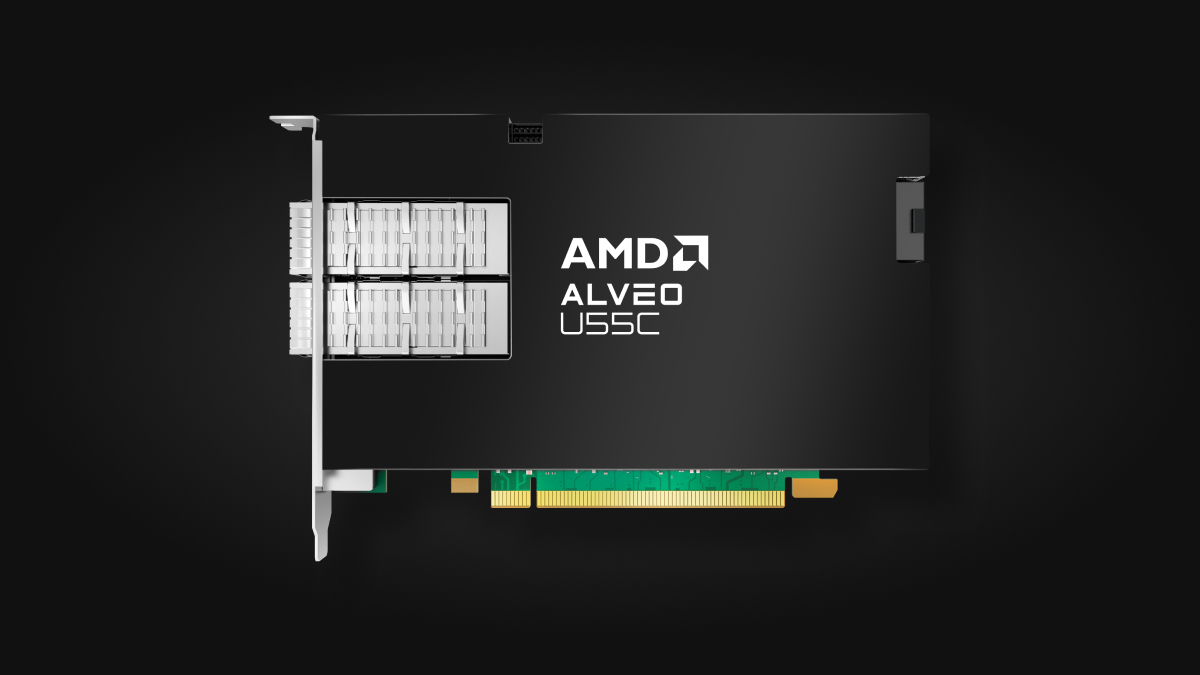

AMD Alveo アクセラレータ カードの製品ポートフォリオ

- 汎用コンピューティング

- FinTech

- ネットワーク

- メディア

- AI 推論

汎用コンピューティング アクセラレータ

ポートフォリオの中で最も汎用性の高いアクセラレータ カードであり、解析、HPC、パケット モニタリング、ネットワーク スイッチング、ストレージ、アルゴリズム取引などのワークロードに適しています。

開発者

FPGA 開発フロー

AMD Alveo アクセラレータ カードでは、AMD Vivado™ Design Suite を使用する従来型の FPGA 設計フローがサポートされています。Alveo ハードウェアに直接マッピングする検証済みの基本デザインを使用することで、簡単に設計を始められます。また、Vivado IP カタログ内の最適化済み構築ブロックを利用することも可能です。

クラウドで利用可能

FPGA アクセラレーションはクラウド上でも利用できるため、概念実証をすばやく行うことができます。クラウド オプションを評価や量産運用に利用でき、またオンプレミスとの併用も可能です。

サーバー サポート

OEM 認定サーバーのネットワークにより、Alveo アクセラレータ カードの幅広い運用オプションを提供します。認定サーバー リストをご覧いただき、要件を満たすプロバイダーと構成をお探しください。

お問い合わせ

サインアップすると、データセンターに関する最新情報の受信や、AMD の営業担当者へのお問い合わせが可能になります。