Overview

AMD Vitis™ HLS for Intuitive Design and Productivity

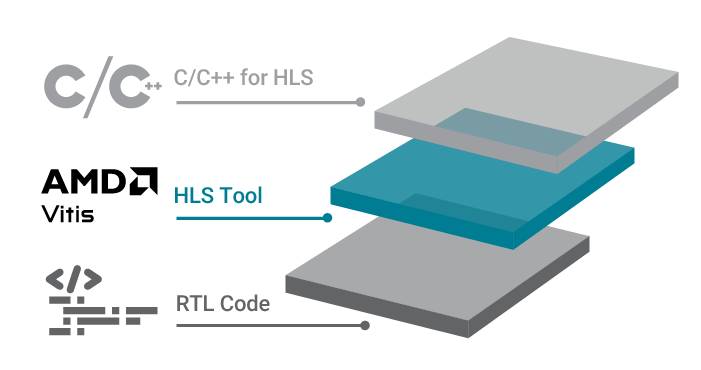

The AMD Vitis™ HLS tool allows users to easily create complex FPGA algorithms by synthesizing a C/C++ function into RTL. The Vitis HLS tool is tightly integrated with both the Vivado™ Design Suite for synthesis and place & route and the Vitis™ unified software platform for heterogenous system designs and applications.

- Using the Vitis HLS flow, users can apply directives to the C code to create the RTL specific to a desired implementation.

- Multiple design architectures can be created from the C source code and a path for high-quality, correct-by-construction RTL is enabled.

- C simulation can be used to validate the design and allows faster iterations than a traditional RTL-based simulation.

- The Vitis HLS tool features a rich set of analysis and debugging tools that facilitate design optimization.

Design Methodology

Vitis HLS Programming Model

Vitis HLS C code is geared towards taking advantage of the benefits and characteristics offered by the architecture of AMD adaptive SoCs and FPGAs.

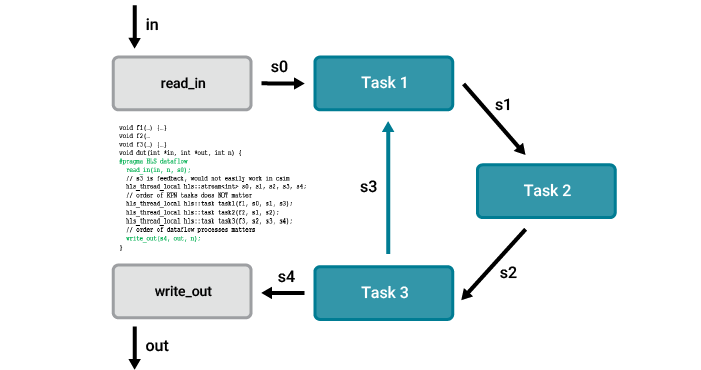

The Vitis HLS tool supports parallel programming constructs in order to model a desired implementation. These constructs include:

- HLS tasks that allow process-level concurrency

- HLS vectors that allow data-level parallelism

- HLS streams that allow communication between concurrent tasks

- Synthesis pragmas can be used to control the results. These pragmas include pipeline, unroll, array partitioning, and interface protocols.

- For additional details, see the "HLS Programmers Guide” section in the Vitis High-Level Synthesis User Guide.

C-to-RTL Conversion

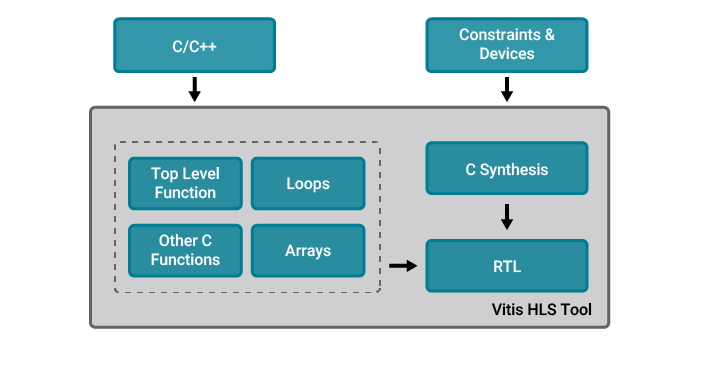

The Vitis HLS tool synthesizes different parts of C code differently:

- Top-level function arguments of the C/C++ code are synthesized into RTL I/O ports and are automatically implemented with an interface synthesis hardware protocol.

- Other C functions are synthesized to RTL blocks—maintaining the design hierarchy.

- C function loops are kept rolled or pipelined to improve performance.

- Arrays in the C code can be targeted to any memory resource, such as BRAM, LUTRAM, and URAM.

- Performance metrics, such as latency, initiation interval, loop iteration latency, and resource utilization, can be reviewed with synthesis reports.

- Vitis HLS tool pragmas and optimization directives allow for configuring the synthesis results for the C/C++ code.

Simulation and Verification

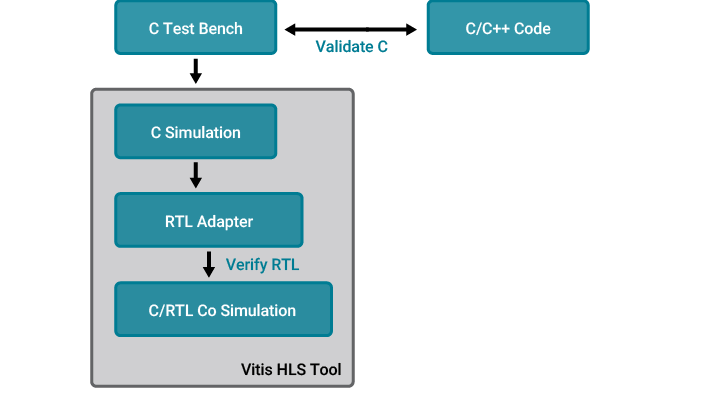

The Vitis HLS tool has built-in simulation flows to enable faster verification times:

- C simulation validates the functionality of the C code. This step is fast and uses a C test bench.

- C/RTL co-simulation reuses the C test bench to perform validation on the generated RTL—verifying that the RTL is functionally identical to the C source code.

- The flow has integrated analysis, debug, and waveform viewing capabilities as well as popular simulator support.

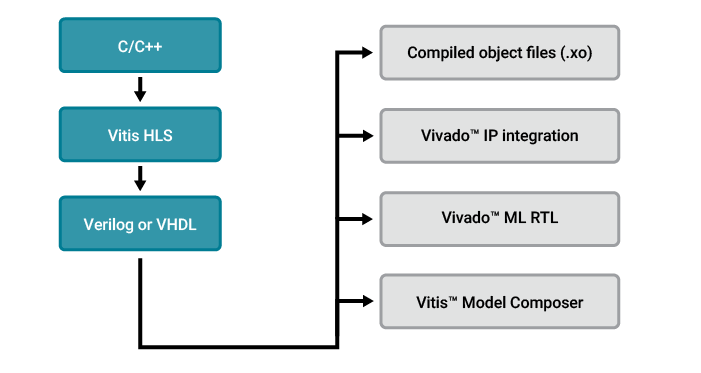

IP Export

The output of the Vitis HLS tool is an RTL implementation that can be either packaged into a compiled object file (.xo) or exported to an RTL IP:

- Compiled object files (.xo) is used to create hardware acceleration functions for use in the Vitis application development flow.

- RTL IP can be used in three ways:

- Added using the Vivado™ IP integrator tool

- Imported as an RTL block in the Vivado IDE

- Used as a single blockset in Vitis Model Composer for DSP applications

What's New

- 2024.2

- 2024.1

- 2023.2

- 2023.1

- 2022.2

- 2022.1

- 2021.2

- 2021.1

2024.2 Release Highlights

Vitis HLS version 2024.2 includes a host of features that make it easier for users to develop and debug an HLS design; these include

- Modeling scalar/wire inputs that change during execution (Direct I/O)

- Support for arbitrary precision floating-point types

- Mapping HLS code to DSP blocks

- User-determined sequence of code execution

- HLS debugger that shows data types in a user-friendly manner (using the prettyprint technology of GNU debugger)

Success Stories

Achieve Ultra-Low Latency in an Audio DSP-to-FPGA with Vitis HLS

The Emeraude Research Team from INSA Lyon, is working on developing new signal processing techniques for embedded audio systems. The team has implemented an ultra-low latency audio DSP program using the AMD Vitis HLS tool. Click here to learn more about how the Vitis HLS tool helped the team to achieve ultra-low latency in an audio DSP-to-FPGA compilation.

Customer Case Study

Faster Design Space Exploration with Vitis HLS

"The main advantage of the AMD Vitis™ HLS tool, from my perspective, is the design space exploration feature. You can generate different architectures and implementations in a reasonable amount of time by using optimization directives (pipelining, unrolling, etc.). This cannot be done if you code manually with VHDL/Verilog. A nice feature of Vitis HLS is the possibility to do a co-simulation and validation of the HDL-code in order to be sure that the HDL-code is functionally correct." Dr. Frank Kesel - Professor at the University of Pforzheim, Germany

Customer Case Study

Resources

脚注

- Based on testing on August 10, 2023, across 1000 Vitis L2/L3 code library designs, with Vitis HLS release 2023.2 vs. Vitis HLS 2023.1. System configuration during testing: Intel Xeon E5-2690 v4 @ 2.6GHz CPU, 256GB RAM, RedHat Enterprise Linux 8.6. Actual performance will vary. System manufacturers may vary configuration, yielding different results. -VGL-04

- The benchmark tests were performed on all 1208 Vitis L1 library C-code designs as of February 12th, 2023. All designs were run using a system with 2P Intel Xeon E5-2690 CPUs with CentOS Linux, SMT enabled, Turbo Boost disabled. Hardware configuration not expected to effect software test results. Results may vary based on software and firmware settings and configurations- VGL-03