- Overview

- Getting Started

Digital Signal Processing

AMD Vitis™ DSP Library contains:

- L1, L2, and L3 levels for digital signal processing

- AI Engine DSP Library

- Programmable Logic (PL) DSP Library

Vitis AI Engine DSP Library - Key Features

Vitis BLAS Library includes the following matrix and vector operation functions

Accelerator Binaries

Download Accelerator Binaries onto Platform

Benchmarks

Benchmarks and Quality of Results (QoR) are provided

Open-Source Library

Open-source library for DSP applications

Example Design

An example design is provided with this library

Kernels in C++

Kernels are coded in your familiar C++

Complex Designs

Combine kernels to construct graphs for complex designs

Vitis AI Engine DSP Library - Functions

Vitis AI Engine DSP Library is a configurable library of elements that can be used to develop applications on Versal® AI Engines. This is an open-source library for DSP applications. The user entry point for each library function is an L2 level graph. Each entry point graph will contain one or more L1 level kernels and may contain one or more graph objects. Direct use of L1 level kernels or any other graph class not identified as an entry point is not recommended.

Vitis AI Engine DSP Library consists of the following DSP elements:

- Filters:

- Single-rate FIRs

- Half-band interpolation/decimation FIRs

- Integer and fractional interpolation/decimation FIRs

- FFT/iFFT

- Single channel, decimation in time (DIT) implementation

- Matrix Multiply

- General matrix multiply

- Widget API Cast

- Flexibility when connecting other kernels

- Widget Real to Complex

- Utility to convert real data to complex or vice versa

- DDS / Mixer

- Direct digital synthesis only mode

- Mixer

For a full list of available DSP functions, please refer to DSP Library Functions.

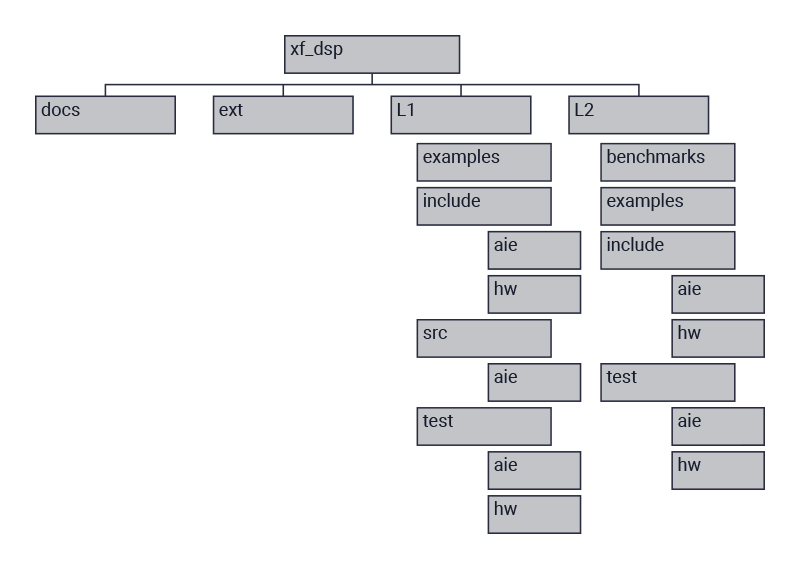

Vitis AI Engine DSP Library - Organization

Vitis AI Engine DSP Library consists of DSP algorithms optimized to take full advantage of the processing power of Versal devices, which contain an array of AI Engines.

The library is organized into three types of AI Engine designs:

- L1 AI Engine kernels

- L2 AI Engine graphs

- L3 software APIs

Note: L3 is not yet available

Vitis Programmable Logic (PL) DSP Library - Introduction

Vitis PL DSP Library implements a discrete Fourier transform using an FFT algorithm for acceleration on AMD Xilinx FPGAs. The library consists of three types of implementations:

- L1 PL primitives

- L2 PL kernels

- L3 software APIs

These implementations are organized in hardware sub-directories of the corresponding L1, L2, and L3 types.

| L1 PL Primitives | Can be leveraged by developers working on hardware design implementation or designing hardware kernels for acceleration. Particularly suitable for hardware designers. |

| L2 PL Kernels | HLS-based predesigned kernels that can be directly used for FPGA acceleration of different applications on integration with the Vitis Runtime Library. |

| L3 Software APIs | Provided in C, C++, and Python, which allow software developers to offload FFT calculation to FPGAs for acceleration. |

Vitis PL DSP Library - Functions

Vitis PL DSP Library provides a fully synthesizable PL-based SSR FFT as well as a 2-dimensional FFT version.

- 1-Dimensional (Line) SSR FFT L1 FPGA Module

- Provides a fully synthesizable SSR FFT with a systolic architecture to process multiple input samples every clock cycle

- Enables the number of samples processed in parallel per cycle by the SSR factor

- Implements as a C++ template function that synthesizes into a streaming architecture

- Can be parameterized through template parameters

- 2-Dimensional (Matrix) SSR FFT L1 FPGA Module

- Provides a fully synthesizable 2-Dimensional FFT as an L1 primitive

- Transforms into an L2 Vitis environment kernel by adding memory adapters

- Designed to have an array of stream interfaces as wide as device DDR memory widths on boards, e.g., Alveo™ U200, U250, and U280 cards

For detailed documentation, please refer to: 1-Dimensional (Line) SSR FFT L1 FPGA Module and 2-Dimensional (Matrix) SSR FFT L1 FPGA Module.