概要

Vitis Model Composer を使用する AI エンジン開発

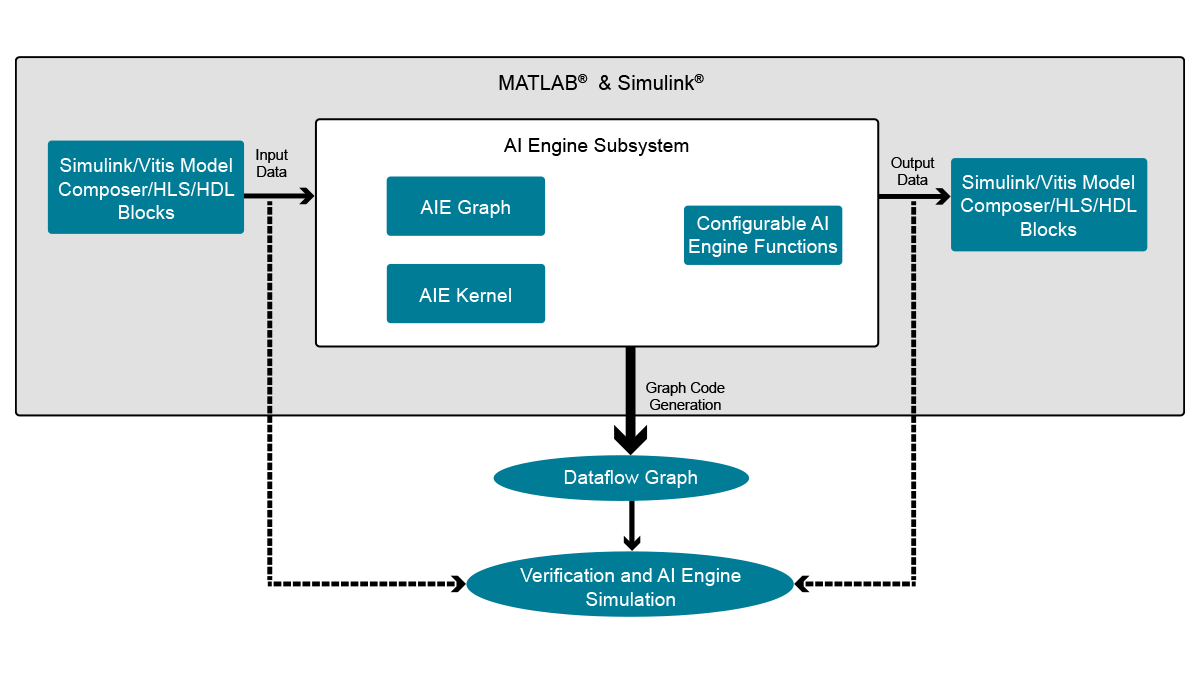

Vitis™ Model Composer は、Simulink 環境内で Versal AI エンジンをターゲットとするアルゴリズムの迅速なシミュレーション、探索、およびコード生成を可能にするツールです。AI エンジン ライブラリ ブロックを使用、またはカーネルとデータフロー グラフをブロックとして Vitis Model Composer にインポートして、ブロックの GUI パラメーターを設定してカーネルの動作を制御できます。このツールでは、AI エンジン ブロックとプログラマブル ロジック (HDL/HLS) ブロックを組み合わせてデザインを構築し、シミュレーションを実行することも可能です。シミュレーション結果は、Simulink ソースおよびシンク ブロックを Model Composer ブロックに接続して表示できます。

Vitis Model Composer は、Simulink 環境内で使用するための性能に最適化されたブロックを提供します。

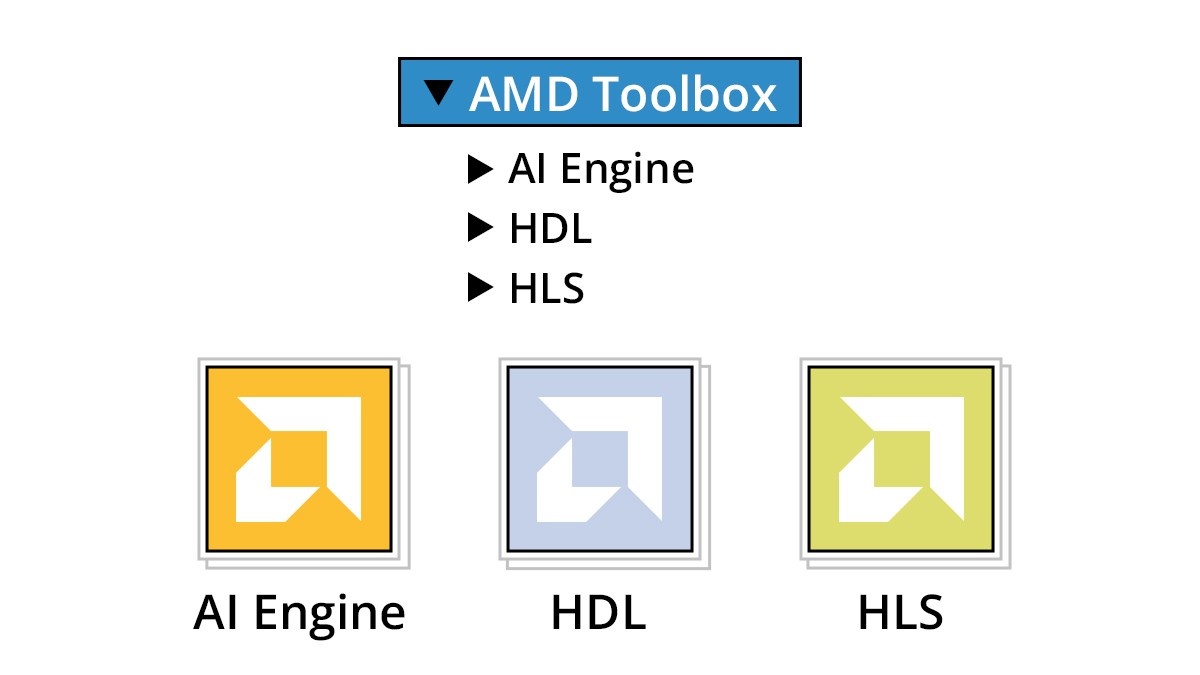

AI エンジン ブロック

- FIR、FFT、DDS、Mixer などの複雑な AI エンジン DSP 構築ブロックを含む。

- Versal デバイスの AI エンジンをターゲットとするカーネルおよびグラフをインポートするためのブロックを含む。

HLS (PL に最適化された HLS コードを生成)

- 数学演算、線形代数、論理演算、ビット演算などの定義済みブロックを提供。

- Versal デバイスの PL をターゲットとする HLS カーネルをインポートするためのブロック。

HDL (PL に最適化された RTL コードを生成)

- 論理回路、数学演算、DSP などのエレメントをモデル化し、FPGA 上で合成するためのブロック。

- Versal デザインの専用 DSP48E1、DSP48E2 ハードウェア リソースをターゲットとする FIR コンパイラ ブロックなど。

- AI エンジン と AMD HDL ブロックセットの接続をサポートするブロック。

ビデオ

Vitis Model Composer を使用した AI エンジンの設計方法を習得

Simulink および Vitis Model Composer を使用した Versal AI エンジンの設計

このビデオ (20 分間) では、Simulink ツールと Vitis Model Composer を使用して、AI エンジン アレイに FIR フィルターを構築してモデル化し、シミュレーション、最適化を実行する方法を紹介しています。

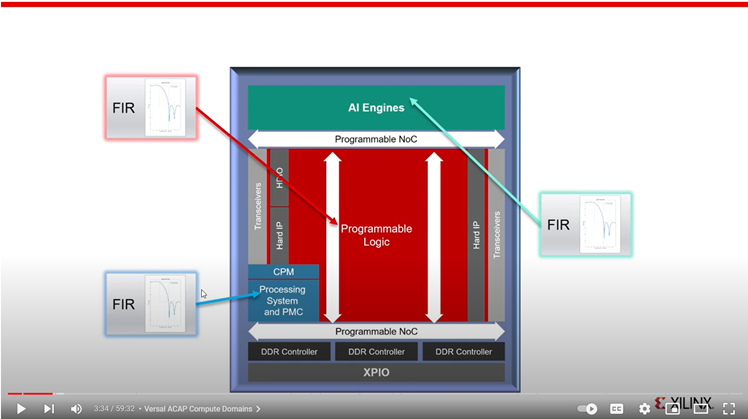

Versal アダプティブ SoC デバイスへの FIR フィルターの実装

このビデオでは、システム設計者およびエンジニア向けに Versal アダプティブ SoC デバイスに FIR フィルターを実装する手順を簡単に説明しています。

Vitis Model Composer を使用する AI エンジン開発

このビデオ (30 分間) では、Vitis Model Composer ツールの概要、および AI エンジン DSP ライブラリを使用して AI エンジン アプリケーションを設計する方法を紹介しています。

Simulink および Vivado シミュレータを使用した初期段階での FPGA/SoC デザイン検証

このビデオでは、Simulink® ツールと Vivado™ シミュレータを使用して FPGA/SoC デザインを検証する方法を紹介しています。

サンプル デザイン

サンプル デザインで Vitis Model Composer ブロックの活用方法を学ぶ

AI エンジン サンプル

| カーネルとグラフをインポート | ランタイム パラメーター (RTP) | DSP デジタル信号処理機能 |

|---|---|---|

| ブロックとしてカーネル クラスをインポート | スカラー RTP 入力を使用した設計 | 周波数ドメインのフィルター |

| ブロックとしてグラフをインポート | 非同期ベクトル RTP 入力を使用した設計 | 2 GSPS で実行するストリーム ベースの FFT |

| 4 Gsps スループットを使用した FIR | ||

| 16 GSPS でのデュアル ストリーム SSR FIR | ||

| ダイナミック ポイント FFT |

PL + AI エンジン デザイン例

| HLS + AI エンジン | HDL + AI エンジン |

|---|---|

| チャネライザー | マルチレート デザイン |

| 2D FFT | PL を使用したシングル ストリーム SSR FIR |

| 2D FFT |

Github チュートリアル

AI エンジン ライブラリ、HLS、および HDL のチュートリアル

リソース

Vitis Model Composer: MATLAB および Simulink ベースの製品

このコースでは、モデル ベースの設計に対応した Vitis™ Model Composer ツールの使用方法について学ぶことができます。

AI エンジン DSP ライブラリおよび Model Composer

このオンライン ライブ コースでは、モデルベースの設計に対応した Vitis™ Model Composer ツールの使用方法について学ぶことができます。

Vitis Model Composer GitHub リポジトリ

Github リポジトリを活用して、Vitis™ Model Composer で効率的な設計を行う方法を学ぶことができます。