AI およびワークロードの高速化向けにポートフォリオの中で最も高い演算性能を提供

主な特長

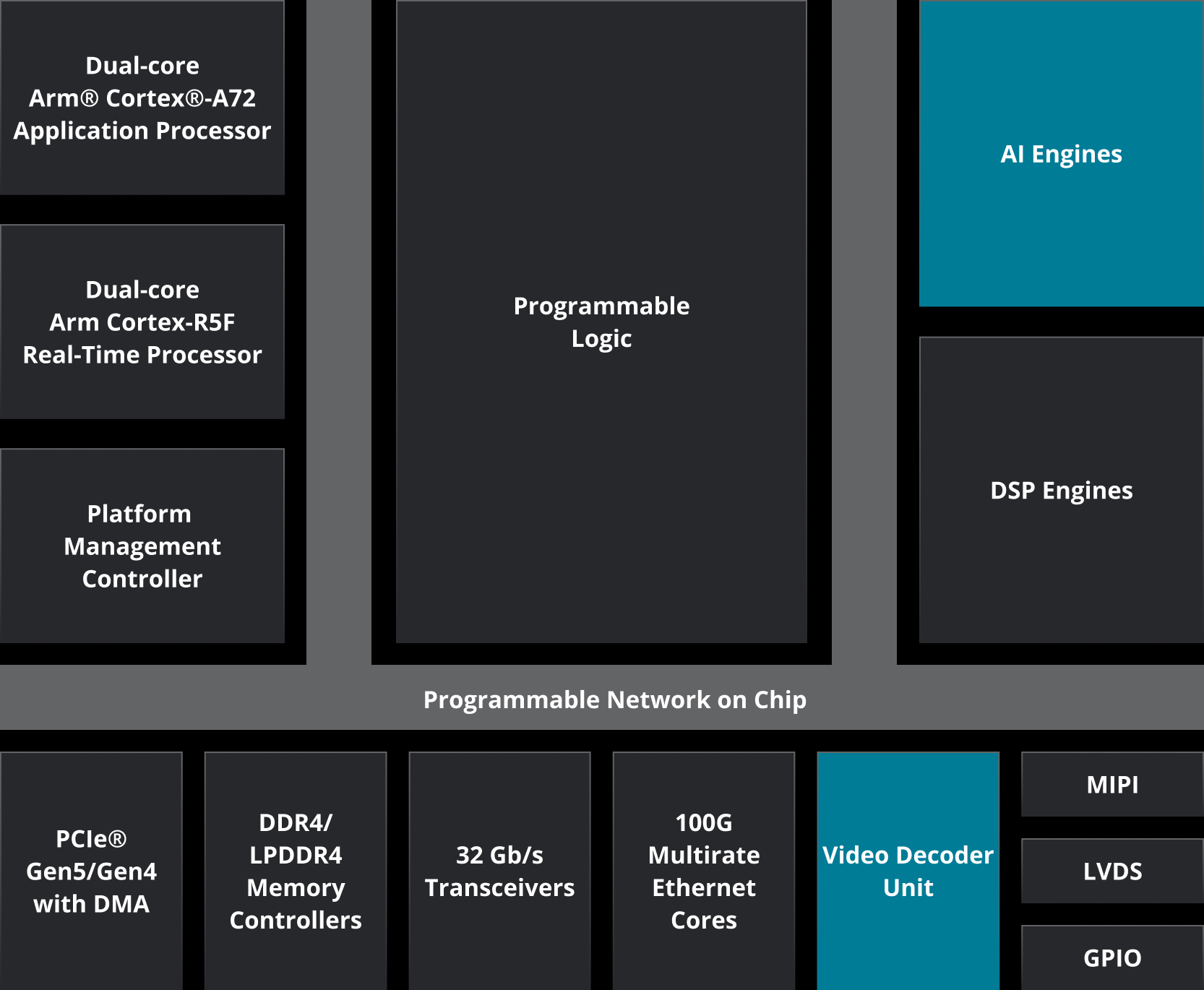

- プロセッシング システム

- プログラマブル ロジック

- AI エンジンおよび DSP エンジン

- 次世代 I/O

- ビデオ デコーダー ユニット

- プログラム可能なネットワーク オン チップ

プロセッシング システム

多様なアプリケーション要件に対応するために、Versal アダプティブ SoC は 3 つのタイプのスカラー プロセッサを備えています。アプリケーション プロセッシング ユニットは、OS でサポートされる複雑なアプリケーションに最適です。リアルタイム プロセッシング ユニットは、低レイテンシ、確定的動作、リアルタイム制御を必要とするアプリケーションに最適です。最後に、独立したプラットフォーム管理コントローラーは、システムの起動、セキュリティ、およびデバッグを管理します。

アプリケーションと業界

5G 無線/ビームフォーミング

ビームフォーミングは、膨大な信号データをリアルタイムに処理する必要があります。適応型エンジンがステータス制御とデータのフォーマット処理を実行している間、AI エンジンと DSP エンジンが固定/浮動小数点信号処理を実行することで、高性能な並列処理が実現します。

データセンターでの演算

たたみ込みニューラル ネットワーク (CNN) が進化し続ける中、演算密度の高い処理が求められるようになりました。この課題を解決できるソリューションは、コストと消費電力を最適化しながら演算密度を向上させることができる AI エンジンを備えた Versal AI コア シリーズ デバイスだけです。

スマート シティのビデオ処理

Versal AI コア シリーズ デバイスは、リアルタイムのナンバープレート認識や顔認識、またはオブジェクト分類を駆動する AI エンジン、ビデオ トランスコーディング用のビデオ デコーダー ユニット、さらにビデオ スケーリング/圧縮/カスタマイズ用の適応型エンジンを提供し、スマートシティのエッジで運用されるさまざまなビデオ処理アプリケーションを可能にします。

医療用画像処理

Versal AI コア シリーズは、並列ビームフォーミングやリアルタイム画像処理を高速化し、高品質の画像生成や機械ベースの画像分析を実現できるため、医師や放射線技師はより迅速かつ正確な診断が可能になります。

レーダー処理

小型フォーム ファクターで、強力なベクター ベースの DSP エンジンと AI エンジンを組み合わせることによって、アクティブ電子走査アレイなどの高度なレーダーを実現できます。AI コア シリーズ デバイスは、単一パッケージで 1 秒間にテラビット単位のデータ転送を可能にするアンテナ帯域幅を提供します。

ワイヤレス テスト装置

ワイヤレス テスト装置には、リアルタイム DSP が広く使用されています。Versal AI エンジンのアーキテクチャは、デジタル フロントエンドからビームフォーミングやベースバンドに至るまで、5G を含むあらゆるタイプのプロトコル実装に適しています。

製品仕様

プロセッサ サブシステムの機能

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| アプリケーション プロセッシング ユニット | デュアル コア Arm® Cortex®-A72、48 KB/32 KB L1 キャッシュ (パリティおよび ECC 付き)、1 MB L2 キャッシュ (ECC 付き) | |||||

| リアルタイム プロセッシング ユニット | デュアル コア Arm Cortex-R5F、32 KB/32 KB L1 キャシュ、および 256 KB TCM (ECC 付き) | |||||

| メモリ | 256 KB オンチップ メモリ (ECC 付き) | |||||

| 接続性 | イーサネット (x2)、USB 2.0 (x1)、UART (x2)、SPI (x2)、I2C (x2)、CAN-FD (x2) | |||||

AI エンジンと DSP エンジンの機能

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| AI エンジン | 198 | 304 | 300 | 400 | 0 | 0 |

| AI エンジン-ML | 0 | 0 | 0 | 0 | 152 | 304 |

| DSP エンジン | 1,032 | 1,312 | 1,600 | 1,968 | 984 | 1,312 |

プログラマブル ロジックの機能

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| システム ロジック セル (K) | 815 | 981 | 1,586 | 1,968 | 820 | 1,139 |

| LUT 数 | 372,352 | 448,512 | 725,000 | 899,840 | 375,000 | 520,704 |

基本的なプラットフォームの機能

| VC1502 | VC1702 | VC1802 | VC1902 | VC2602 | VC2802 | |

|---|---|---|---|---|---|---|

| NoC マスター/NoC スレーブ ポート | 21 | 21 |

28 | 28 | 21 | 21 |

| DDR メモリ コントローラー | 3 | 3 |

4 | 4 | 3 | 3 |

| DMA 内蔵 PCIe® (CPM) | 1 x Gen4x16 |

1 x Gen4x16 |

1 x Gen4x16 |

1 x Gen4x16 |

2 x Gen5x8 |

2 x Gen5x8 |

| PCI Express® | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen4x8 | 4 x Gen5x4 | 4 x Gen5x4 |

| 100G Multirate Ethernet MAC | 3 | 4 | 4 | 4 | 2 | 2 |

| ビデオ デコーダー エンジン (VDE) | - | - | - | - | 2 | 4 |

| GTY トランシーバー | 32 | 44 | 44 | 44 | 0 | 0 |

| GTYP トランシーバー | 0 | 0 | 0 | 0 | 321 | 321 |

1.16 GTYP トランシーバーは、PCI Express を使用する場合の CPM5 専用です。

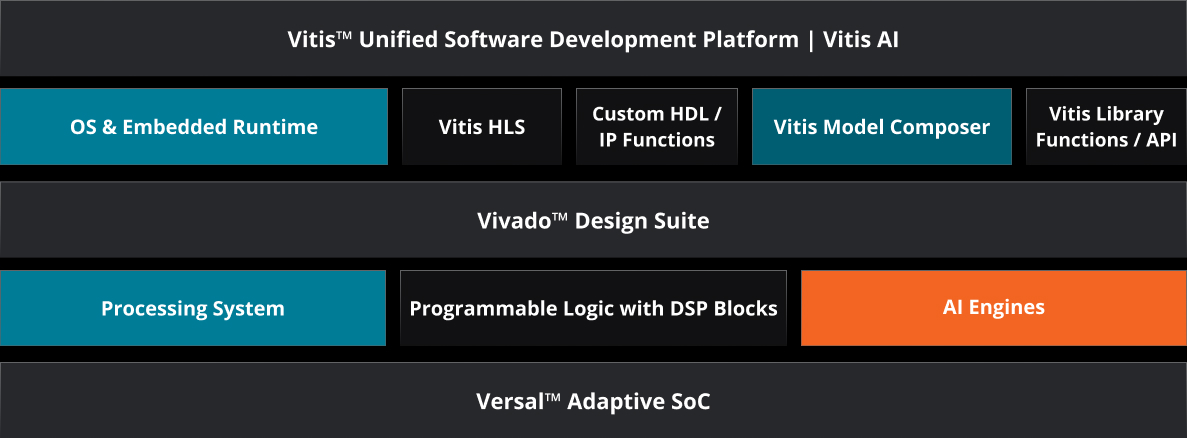

すべての開発者向け

AMD は、アダプティブ SoC および FPGA を使用した設計をサポートするソフトウェア開発環境を提供しています。これには、ツール (コンパイラ、シミュレータなど)、IP、およびソリューションが含まれます。

この環境を利用することで、ワットあたりの性能が高いデザインを短期間に構築できます。これらのツールは、AI サイエンティストから、アプリケーション/アルゴリズム エンジニア、エンベデッド ソフトウェア開発者、従来のハードウェア開発者に至るまで、あらゆる開発者が AMD アダプティブ コンピューティング ソリューションを活用できるようサポートします。

利用を開始

実証済みの HW/SW サポート、ツール、デザイン サンプル、およびキットに対応した関連資料を利用することで、すぐに設計を開始して製品の市場投入までの期間を短縮できます。

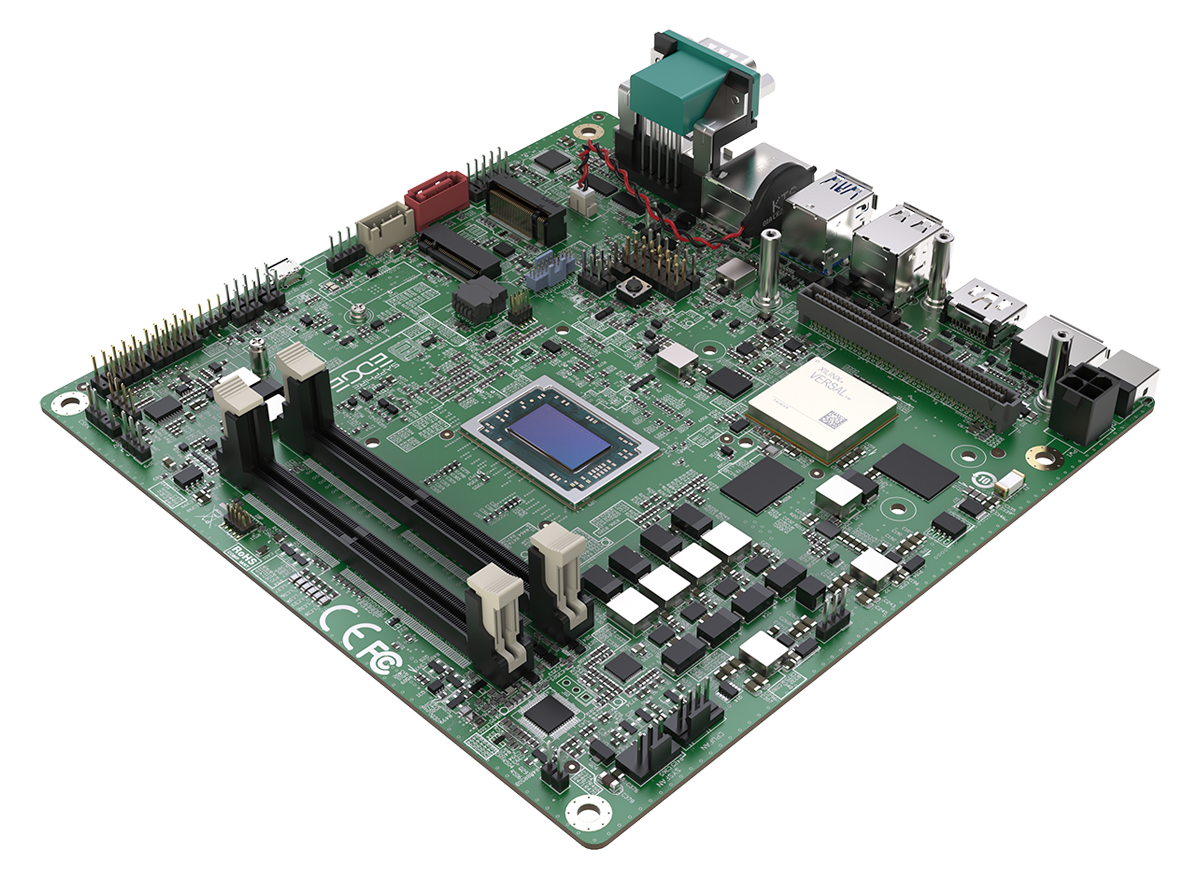

Versal AI コア シリーズ VCK190 評価キットで開発を開始

VC1902 デバイスを搭載した VPK190 評価キットを使用して、Versal AI コア シリーズの機能を評価できます。信号処理や ML 推論に最適化されたオンチップ AI エンジンを活用するこのプラットフォームは、計算負荷が高く、レイテンシに敏感な DSP および ML アプリケーションの開発に最適です。実証済みの HW/SW サポート、ツール、デザイン サンプル、およびキットに対応した関連資料を利用することで、すぐに設計を開始して製品の市場投入までの期間を短縮できます。

リソース

最新情報を入手

Versal アダプティブ SoC 通知リストに登録された方には、最新情報をいち早くお届けします。