Versal プレミアム VP1902 デバイス

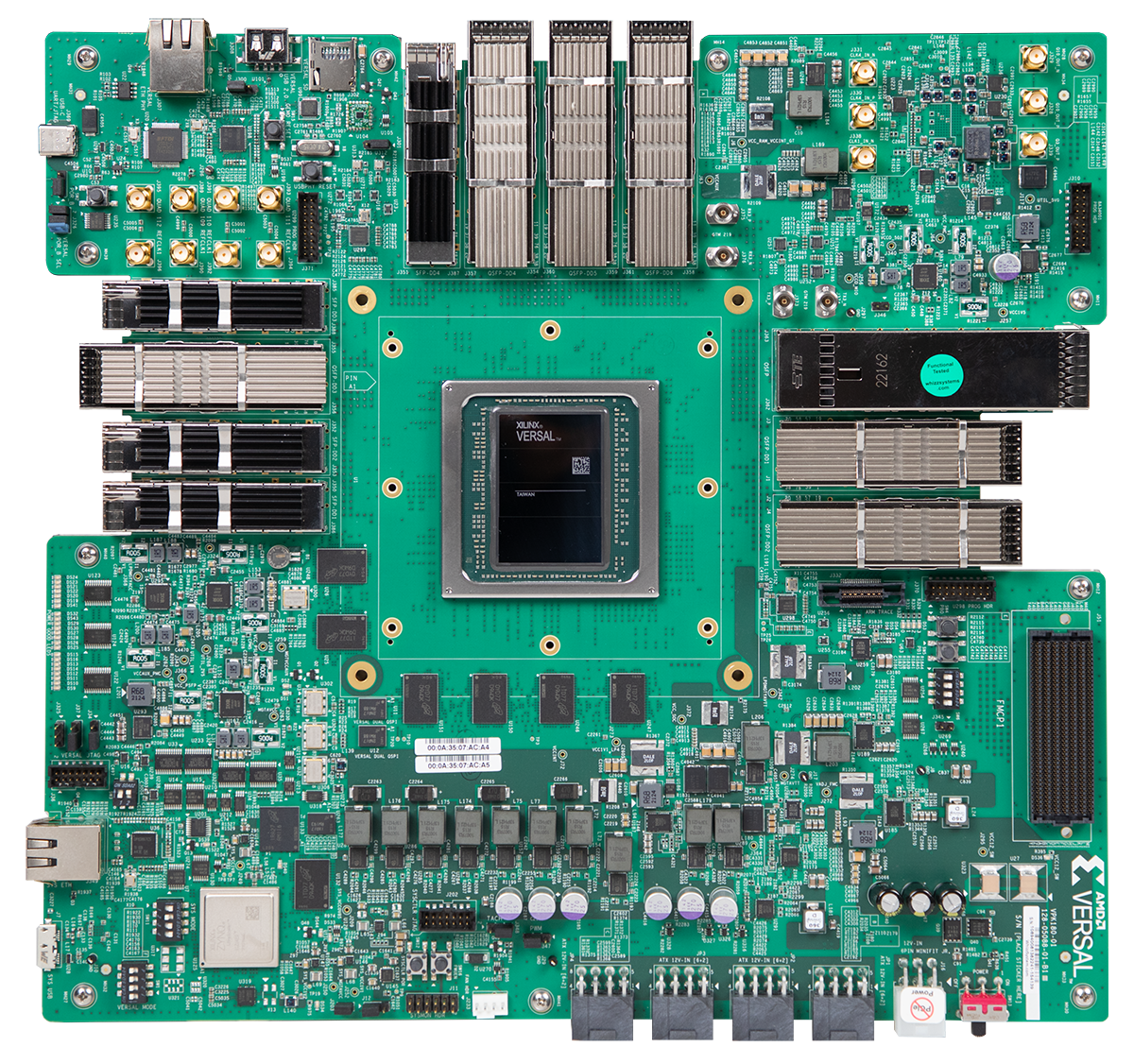

Versal プレミアム VP1902 アダプティブ SoC は、オンチップにスカラー プロセッシング サブシステムを搭載した初めてのエミュレーション クラス デバイスであり、SW/HW ファームウェアの開発やシステムの立ち上げにおいて多様な制御やスティミュラスの生成が可能なモードを提供します。

業界最高レベルの容量1 とコネクティビティ

- 2 倍2 の容量 (18.5M ロジック セル)*

- 2 倍3 の I/O 帯域幅 (チップ間インターフェイス)*

- 2.3 倍4 のトランシーバー帯域幅 (112G PAM-4)*

エミュレーションやプロトタイピングに最適

- 最大 2 倍5 のシステム レベル性能向上*

- Versal™ アーキテクチャにより、最大 8 倍6 のデバッグ性能を実現

- 60 億を超える7 ゲート設計にスケーラブルに対応可能

包括的なツールと IP

- Vivado™ Design Suite による同時最適化

- マルチ SLR デザイン対応の高度な配置配線機能

- デバッグおよびマルチデバイス デザインをサポートする IP

* Virtex™ UltraScale+™ VU19P FPGA と比較

革新への道を切り拓く

信頼できる技術で自信をもってエミュレーションを行う

17 年以上の経験を持つ AMD のエミュレーション クラス デバイスを使用することで、チップ メーカーは次世代 ASIC/SoC のデザイン、そしてそれらで実現する画期的な技術をすばやく市場に提供できることをご紹介します。

画期的なハードウェアを提供

世界最大容量のアダプティブ SoC1 を活用する

大容量で優れたコネクティビティを持つ Versal プレミアム VP1902 アダプティブ SoC は、デザインにスケーラビリティを提供し、配線性能とレイテンシを向上させ、デザイン プロセスの反復作業を効率化させます。

Versal プレミアム VP1902 製品パンフレット

Versal プレミアム VP1902 アダプティブ SoC は、Versal 製品ポートフォリオの中で最高レベルのロジック容量、インターコネクト、外部メモリ帯域幅を提供します。

アプリケーション

次世代 ASIC/SoC の設計には、さまざまな要件に柔軟に対応できるエミュレーションやプロトタイピング システムが必要です。世界最高容量1 で前世代デバイスの 2 倍のコネクティビティ3 を提供する VP1902 は、単一デバイスのデスクトップ プロトタイピング システムから、大手 EDA ベンダーが開発する大規模なエミュレーション プラットフォームまで、幅広いニーズに対応できる理想的なデバイスです。

設計開始

実証済みの HW/SW サポート、ツール、デザイン サンプル、およびキットに対応した関連資料を利用することで、すぐに設計を開始して製品の市場投入までの期間を短縮できます。

Versal プレミアム シリーズ VPK180 評価キットでプロトタイプ作成を開始

VP1802 デバイスを搭載した VPK180 評価キットを使用して、Versal プレミアム シリーズの機能を評価できます。ハード化され、消費電力に最適化されたコアを活用することで、このプラットフォームは複雑なコンピューティングおよびネットワーク アプリケーションの開発に最適です。実証済みの HW/SW サポート、ツール、デザイン サンプル、およびキットに対応した関連資料を利用することで、すぐに設計を開始して製品の市場投入までの期間を短縮できます。

リソース

Versal プレミアム シリーズの製品セレクション ガイド

営業に問い合わせ

AMD のセールス チームがお客様のニーズに合ったベストな技術的判断ができるようお手伝いいたします。

脚注

- AMD の社内解析に基づく (2023 年 5 月実施) - 6 入力 LUT を使用して、Versal プレミアム VP1902 デバイスとインテル Stratix 10 GX 10M FPGA を比較。(VER-002)

- AMD 社内解析に基づく (2023 年 5 月実施) - Versal プレミアム VP1902 デバイスと Virtex UltraScale+ VU19P デバイスのシステム ロジック セル数を比較。(VER-001)

- AMD のラボ テストに基づく - A6865 パッケージを使用して、AMD Versal プレミアム VP1902 デバイスの XPIO データレート パフォーマンスをシミュレーションし、AMD Virtex UltraScale+ VU19P FPGA の公表されているデータレートと比較。実際の結果は変動する可能性がある。(VER-003)

- AMD のラボ解析結果に基づく (2023 年 5 月実施) - GTY/GTYP が 32G で動作し、GTM が 56G で動作する場合を想定し、Versal プレミアム VP1902 デバイス B6865 パッケージと Virtex UltraScale+ VU19P デバイス B3824 パッケージのトランシーバーの総帯域幅を比較。(VER-005)

- AMD 社内で実施したシステム クロック性能解析に基づく (2023 年 5 月実施) - さまざまなデザイン サイズと配線で Versal プレミアム VP1902 デバイスと Virtex UltraScale+ VU19P デバイスの性能を比較。(VER-006)

- AMD 社内解析に基づく (2023 年 5 月実施) - AMD Versal アダプティブ SoC CFI インターフェイスと AMD Virtex UltraScale+ FPGA ICAP インターフェイスのリードバック/ライトバック性能を比較。実際のパフォーマンスは異なる可能性があります。(VER-004)

- AMD ラボの予測に基づく (2023 年 5 月実施) - 前世代の Virtex UltraScale+ VU19P FPGA エミュレーション/プロトタイピング プラットフォームと比較して 2 倍の容量。(VER-007)

- AMD の社内解析に基づく (2023 年 5 月実施)。(VER-009)