当社の設計チームは、製造容易性設計 (DFM) とテスト容易化設計 (DFT) の原則を利用することで、パッケージ化されたデバイスの製造性とテスト容易性を実現し、品質と信頼性を最初から一貫して確立しています。 当社では、シリコン、ボード、パッケージ技術を開発し、お客様の期待に応えるために検証および認定された最終製品に統合しています。

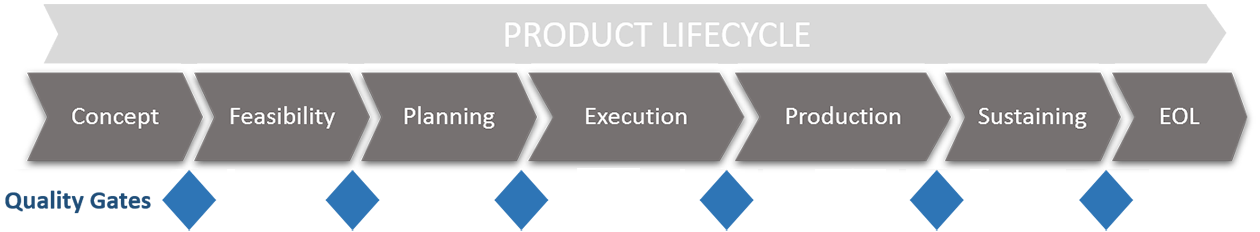

フェーズ ゲート プロセス

AMD では、厳格に管理されたフェーズ ゲート プロセスを活用し、コンセプトから製造まで高い品質を実現しています。各フェーズの最後にこれらの品質ゲートを使用し、製品を次の段階に進める前に、主要な基準を満たしていることを確認します。AMD の製品ライフサイクル管理プロセスにより、製品の製造開始から使用後に至るまでのライフサイクル全体が、業界標準のガイドラインに基づいていることを確認できます。

製品の検証

AMD では、プレシリコン検証およびポストシリコン実証を実施しています。プレシリコン検証には、チップの機能の検証や、チップ レベルの高度でさまざまなモデリングおよびシミュレーションの実行が含まれます。ポストシリコン実証では、パッケージ化されたチップの速度、機能、信頼性をテストします。製造前に、これらの包括的な試験で厳しい要件を満たす必要があります。ソフトウェア検証はハードウェア検証と並行して実施され、一体となって動作するハードウェアおよびソフトウェア コンポーネントの提供に役立ちます。

信頼性向上設計 (DfR)

AMD の信頼性設計手法は、最先端のプロセス ノードにおいて縮まる一方の信頼性マージンに対応できるよう考えられています。これまでの知見、専用ツールに関する深い経験、機械学習を活かすことで、AMD のエンジニアは開発プロセスを短縮し、データセンター、工業、オートモーティブ、航空宇宙、防衛などの業界で非常に高い信頼性が求められる用途の厳しい要件を満たしてきました。

AMD では、信頼性設計のためのルール、予算、ガードバンドなどの手法を導入して、ポストストレス劣化に対処し、長期的な信頼性を実現しています。

テスト容易化設計 (DfT)

AMD の設計エンジニアは、問題をすみやかに検出して根本原因を特定できる機能を重視しています。このアプローチはテスト容易化設計 (DfT) 手法と新製品導入 (NPI) プロセスに始まり、製品のライフサイクル全体をカバーしています。

これらの手法には、デジタル論理、IP、メモリ素子、I/O バウンダリスキャンなど、多彩な分野が関わっています。新たなテスト手法は、カスタマー リターンを基にした PPM 値で評価されます。

製造容易性設計 (DfM)

AMD の製造容易性設計 (DfM) エンジニアリング原理は、リスクの軽減とオペレーショナル エクセレンスの最適化に注力することで、品質、信頼性、タイム トゥ マーケットを促進します。その第一歩は、実験、テスト、製造に関わる次のような手法を厳格に設計することです。

- 性能優位性をもたらす DFM ルール

- 最先端のツールや技法を用いた、デバイスのより深い特性評価

- 電気、温度、機械の 3 要素をアセンブリ試験に加味することによるウェハー認定の強化

- 特性評価プロセスへのシステムタイミング チェック導入によるマルチダイ性能の確保