Why Choose Xilinx to Accelerate Your Applications in Diverse Industry?

Overview

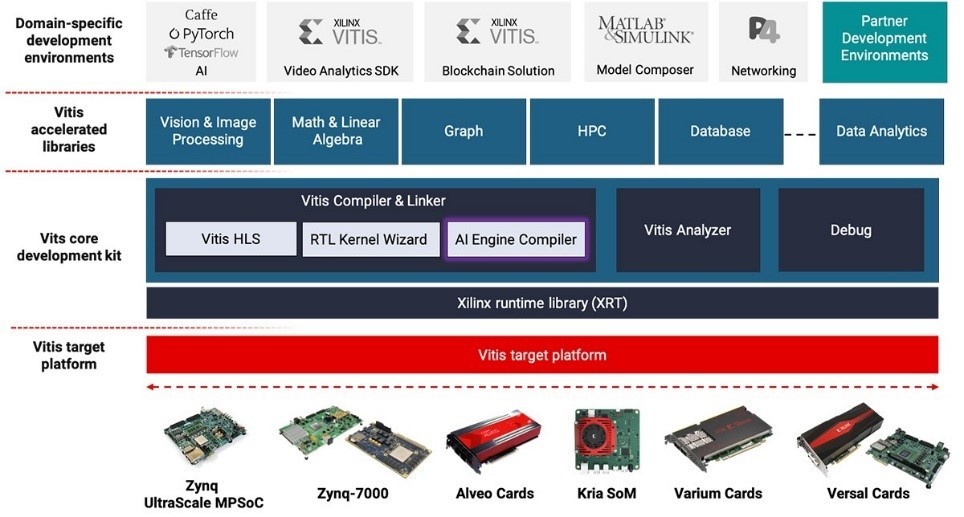

As all you know, in recent years, Xilinx announced and iterated a unified software platform called Vitis™, aiming to put all software in one platform. The platform of Vitis brings a revolution to FPGA developers, even the developers who lack hardware knowledge.

The architecture of Vitis™ Unified Software Platform includes:

- Comprehensive core development kit to seamlessly build accelerated applications

- Rich set of hardware-accelerated open-source libraries optimized for Xilinx FPGA and Versal ACAP hardware platforms

- Plug-in domain-specific development environments enabling development directly in familiar, higher-level frameworks

- A growing ecosystem of hardware-accelerated partner libraries and pre-built applications

- Vitis Model Composer, a Model-Based Design tool that enables rapid design exploration and verification within the MathWorks MATLAB® and Simulink® environment and accelerates the path to production on Xilinx devices.

- Vitis Networking P4 allows for the creation of soft-defined networks. VitisNetP4 data plane builder generates systems that can be programmed for a wide range of packet processing functions from simple packet classification to complex packet editing.

Vitis provides plenty of development kits and libraries to accelerate applications in many industries easier than traditional FPGA flow. Meanwhile, it is also very friendly to those developers who have a good software development experience based on CPU or GPU, using C/C++ and Python. Many CUDA-like libraries have been covered in Vitis libraries allowing developers to migrate their designs efficiently.

So, let's dive in why you choose Xilinx to accelerate your applications!

What are the Vitis Accelerated Libraries?

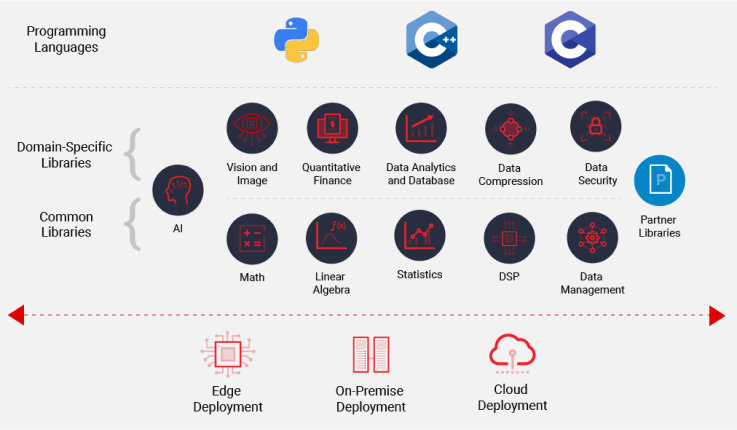

Vitis Accelerated Libraries are a series of open-source, performance-optimized libraries that offer out-of-the-box acceleration with minimal to zero-code changes to your existing applications, written in C, C++, or Python. Leverage the domain-specific accelerated libraries as-is, modify them to suit your requirements or use them as algorithmic building blocks in your custom accelerators.

As shown in the figure above, Vitis libraries include three parts, common libraries, domain-specific libraries, and partner libraries. There are many basic libraries provided by common Vitis accelerated libraries, including Math, Statistics, Linear Algebra, and DSP. It offers a set of the core functionality for a wide range of diverse applications.

Domain-specific libraries provide out-of-the-box acceleration for many specific applications, such as Vision and Image Processing, Quantitative Finance, Data Science (Database, Data Analytics, and machine learning), Data Compression, Data Security, and so on.

Benefiting from huge of third-party ecosystems, Vitis libraries contain many partner libraries as well that can make your product easier to build. Because of the Vitis Libraries, Xilinx can cover almost all industry applications and achieve a perfect algorithm acceleration.

Why Choose Vitis Accelerated Libraries?

Let's dive into the features and performance of Vitis Libraries!

Database Library

Introduction

Vitis Database Library is an open-sourced Vitis library written in C++ for accelerating database applications in a variety of use cases. The main target audience is SQL engine developers, who want to accelerate the query execution with FPGA cards. The highlight features are shown below.

Features:

- A powerful Generic Query Engine (GQE) supporting Aggregate, Join, Bloom-Filter, etc.

- Supports 64-bit keys to realize TB-level tables query.

- Paired database: Greenplum, Presto, etc.

Leveraging the database library, you can easily offload your applications from CPU to FPGA using your familiar programming language, C++. For more details regarding Vitis Database Library, see here.

Furthermore, you can also cooperate with Xilinx ecosystem partners to implement your application efficiently. The information about the partner is shown below.

Partner Introduction:

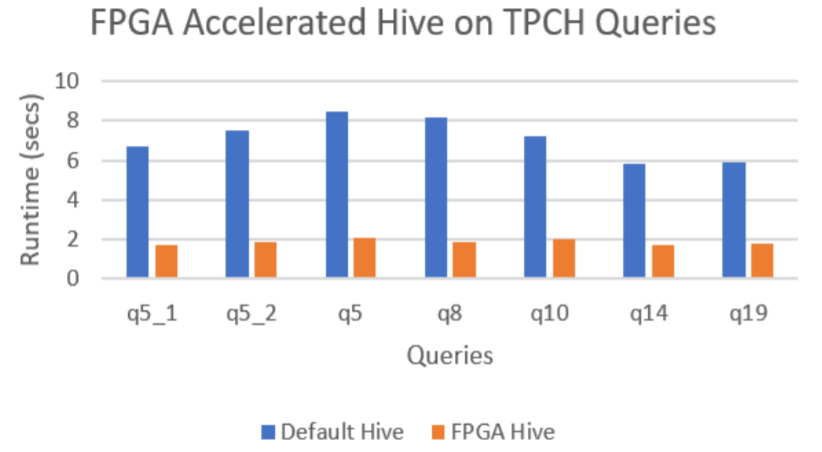

BigZetta is committed to providing acceleration for your mission-critical computations which will enable you to finish tasks quickly as well as save on hardware costs. BigZetta has augmented Hive with FPGA-based acceleration, which has demonstrated speedups of more than 4x over several TPCH benchmark queries. Several TPCH benchmark queries were run with default Hive and one augmented with bzQAccel (BigZetta FPGA solution) based on CPU and Xilinx Alveo accelerator cards.

As shown in the figure above, the performance across all queries accelerated by FPGA is more than 4 times better than the default Hive. For more details, see here.

Xilinx has offered a great ecosystem for Database solutions. Based not only on Vitis Database libraries but also on powerful partners, developers can realize your algorithms and applications with minimal to zero-code changes and get an impressive performance versus default platforms.

Data Analytics Library

Introduction

Vitis Data Analytics Library, an open-sourced library written in C++, provides plenty of APIs for accelerating data analytics applications. The key features are shown below.

Features:

- Data Mining: Classification, Clustering, and Regression.

- Text Processing: Regular expression match, Geo-IP, and Deduplication.

- Data Frame: Apache Arrow read-write, Parquet write, CSV, and JSON parse.

Data Mining is a famous application in the data analytics field. There are many relevant APIs covering machine learning algorithms, like decision tree, random forest, native Bayes and SVM, as well as Clustering algorithms, like K-means.

For unstructured information extraction and transformation, the Data Analytics library offers a series of Text Processing APIs to accelerate it. A complete demo has been provided to show batch transform Apache HTTP server log into structured JSON text.

Data Analytics library can also support many data frames to address data acquire and import. Apache Arrow, a popular data frame, has been supported along with CSV and JSON parse. For more details regarding the Data Analytics library, see here.

Quantitative Finance Library

Introduction

Vitis Quantitative Finance Library is an open-sourced library designed to provide a comprehensive FPGA acceleration library for quantitative finance. The key features are shown below.

Features:

- Supports many famous Pricing Models regarding the interest rates and financial market dynamics.

- Provided Numerical Methods and Closed-Form Solution Methods APIs.

- Python Module has been supported.

Xilinx also completed the STAC-A2 Benchmark tests on a stack consisting of Xilinx Vitis Unified Software Platform 2020.2 with eight Xilinx Alveo U250 FPGA cards in a BOXX GX8-M server. STAC-A2 is the technology benchmark standard based on financial market risk analysis. Designed by quants and technologists from some of the world's largest banks, STAC-A2 reports the performance, scaling, quality, and resource efficiency of any technology stack that is able to handle the workload (Monte Carlo estimation of Heston-based Greeks for a path-dependent, multi-asset option with early exercise). The highlight of the Xilinx STAC-A2 report are presented below.

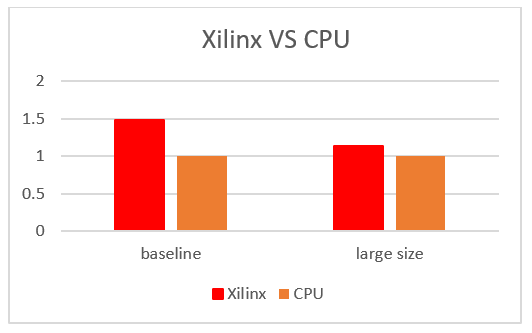

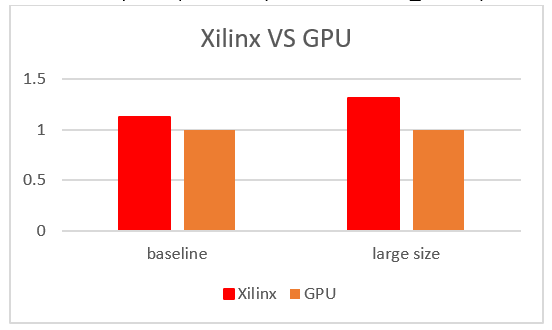

As shown in the chart above, compared to the benchmarked solution using CPUs (SUT ID INTC190903), Xilinx system:

- Had a 1.48x speed-up in the cold run of the baseline problem size (STAC-A2. β2. GREEKS.TIME. COLD).

- Was 14.1% faster in cold runs of the large problem size (STAC-A2. β2. GREEKS.10-100k-1260.TIME. COLD).

- Had 20% higher maximum paths (STAC-A2.β2.GREEKS.MAX_PATHS).

As indicated in the chart above, compared to the benchmarked solution using GPUs (SUT ID NVDA200909), Xilinx system:

- Was within 11.3% in the cold run of the baseline problem size (STAC-A2. β2. GREEKS.TIME. COLD).

- Was within 31.9% in the cold runs of the large problem size (STAC-A2. β2. GREEKS.10-100k-1260.TIME. COLD).

Because of Vitis Quantitative Finance Library, Xilinx achieved an impressive performance based on a series of Xilinx Alveo acceleration cards in STAC-A2 report. It shows that Xilinx could implement your Quantitative Finance applications efficiently. More details regarding Quantitative Finance library, see here.

Graph Library

Introduction

Vitis Graph Library is an open-sourced Vitis library written in C++ for accelerating graph applications in a variety of use cases, which now has supported many algorithms, such as Similarity analysis, Community Detection and Search. The key features are shown below.

Features:

Similarity analysis: Cosine Similarity, Jaccard Similarity, k-nearest neighbor.

- Connectivity analysis: Weekly Connected Components and Strongly Connected Components.

- Community Detection: Louvain Modularity, Label Propagation, and Triangle Count.

- Search: Breadth First Search, 2-Hop Search.

- Graph Format: Renumber, Calculate Degree and Format Convert between CSR and CSC.

All these supported algorithms can be accelerated by Xilinx Alveo acceleration cards. Using the Vitis Graph Library, you can realize algorithms with your familiar programming languages, C++, and achieve a great performance versus traditional CPU approaches.

Besides this, you can cooperate with the partners in the Xilinx ecosystem as well. The partner information is shown below.

Partner Introduction:

TigerGraph leading scale-out graph database provides a complete, distributed, parallel graph computing platform supporting web-scale data analytics in real-time and enables you to drill down deep into member data without sacrificing performance. The highlight features of TigerGraph solution are shown below.

Features:

- Ready-to-use Xilinx Cosine Starter Kit for use in Healthcare and Retail applications.

- 300x better performance vs CPU.

- 95% lower TCO vs CPU.

- Native parallel graph database supports loading terabytes of data.

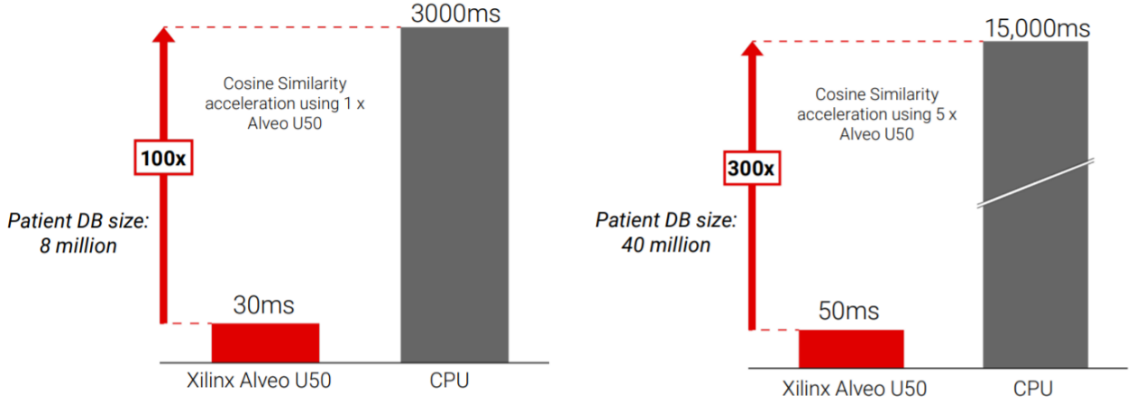

TigerGraph, accelerated with Xilinx Alveo U50 cards and based on the massively parallel processing capability of FPGA architecture, offers superior results for computing cosine similarity calculations.

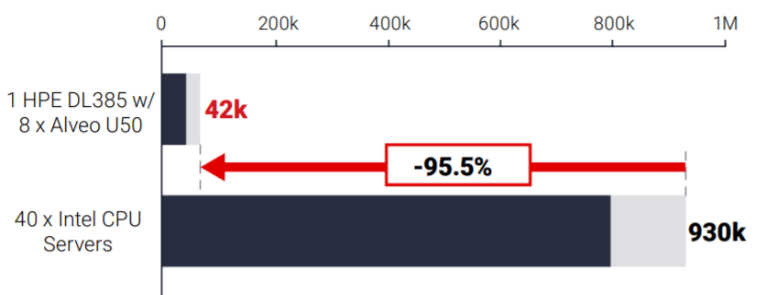

As shown in the figures above, eight Xilinx Alveo U50s, mounted in a single 2U HPE DL385 Gen10 Plus server featuring industry-leading EPYC CPUs, deliver the same performance as 40 Intel CPU based servers, with 95% lower TCO.

There is a series of comparisons shown by the above figures. When the database size is 8 million, one Xilinx Alveo U50 card has a 100 times better acceleration performance of Cosine Similarity than 2x Intel(R) Xeon(R) 48 cores CPU. Additionally, increasing database size to 40 million, there is 300 times upper of performance versus CPU based on 5 Xilinx Alveo U50 cards. This is because a bottleneck occurs when memory bandwidth is limited. More details, see here.

Codec Library

Introduction

Vitis Codec Library is an open-sourced Vitis library written in C++ for accelerating image applications in a variety of use cases. The key features are shown below.

Features:

- JPEG Decoder: “JPEG” stands for Joint Photographic Experts Group, the name of the committee that created the JPEG standard and other still picture coding standards.

- PIK Encoder: PIK is the prototype of JPEG XL, which is a faster graphics file format supporting both lossy and lossless compression. It is designed to outperform existing raster formats and thus to become their universal replacement.

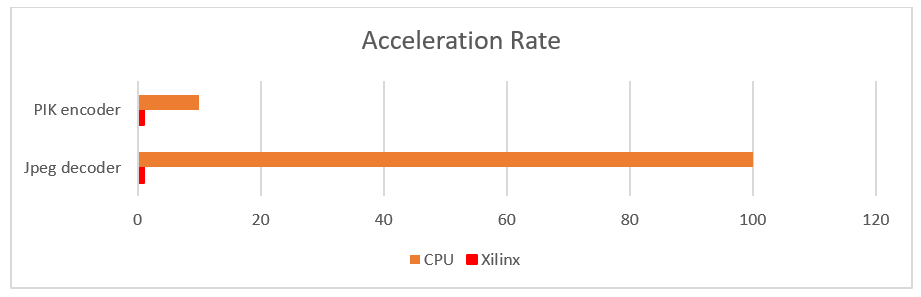

Vitis Codec Library provided a great acceleration performance compared to CPU. The below figure described a benchmark between Xilinx Alveo cards and 1 thread CPU.

The chart shows that the PIK encoder outperforms the CPU approach by more than 10 times, while the Jpeg decoder achieves an impressive more than 100 times acceleration rate. At this high performance, the throughput is also high quality. Based on Xilinx Alveo card U200, the throughput of PIK encoder is greater than 60 MB/s when input format is RGB444, while the throughput of Jpeg decoder is higher than 10 GB/s when input YUV444 format images.

Those high-level APIs included in the Vitis Codec Library are easy to use. You can build your design by coding C++ and get a great performance without any hardware and FPGA knowledge. More details, see here.

Xilinx Applications

Besides those Vitis acceleration libraries we mentioned above, which provide APIs to accelerate the industry algorithms, some solutions have been released, focusing on a certain application.

Blockchain Acceleration

Introduction:

Xilinx Vitis™ Blockchain Solution based on the Vitis Ethereum Mining Library which is an open-source Vitis Library written in C++ to mine coin of Ethereum using Xilinx Alveo cards. The highlight features are shown below.

Features:

- Hardware: 8 kernels and 32 HBM (High Bandwidth Memory) channels enabled to get the best random-access bandwidth.

- Software: Integrated with world popular open-source mining software Ethminer.

- Production: Mining rate recognized by top mining pool ethermine.org.

Leveraging the Ethereum Mining Library and the Xilinx Alveo cards, you can easily achieve superior performance compared to the most famous devices nowadays.

As shown in the figure above, compared with Nvidia HX series cards, the Xilinx U50C card gets an average of two times better performance per watt, which is an extremely competitive EThash acceleration effect. For more details regarding Xilinx Vitis™ Blockchain Solution, see here.

Anti-money laundering (AML)

Introduction:

Xilinx’s Anti-Money Laundering (AML) Watch List Management (WLM) Compute Solution enables financial institutions and government agencies to detect, enforce, and prohibit fraudulent transactions in real-time, minimizing risk and preventing revenue loss. The key features are shown below.

Features:

- Detect fraudulent transactions through SWIFT messages.

- Reduce Infrastructure Costs by more than 90%.

- Reduce Response Times by 650X.

- Watch List Management Screens Against.

- Simple Integration: AWS and on-premises are supported.

This application has shown its capabilities in multiple cases. In a POV with a European Bank, the Real-Time AML WLM Compute Solution was able to reduce infrastructure costs by more than 90% versus the best alternative solution.

In addition, reducing response time and hastening resolution is key for improving NPS. The Association of Certified Anti-Money Laundering Specialists (ACAMS) concluded that 30% of alerts take more than 30 minutes and 10% take more than an hour to close. Xilinx can reduce the response times by 650 times, leveraging Vitis accelerated libraries and FPGA devices. For more details regarding the Xilinx AML solution, see AWS and on-premises.

How to Get Started?

Let's get started!

- Visit the Vitis Unified Software Platform page and select any tag that interests you!

- For those mentioned libraries, click Vitis Libraries tag, then Vitis Libraries product page will pop up.

- You can click the tag top of the page to switch between overview, libraries, and documentation. In the documentation tag, you will find a button called documentation. Click it, then you will turn to all the library's documentation like below.

4. You can find all the libraries mentioned on the left of the page. Every Library has a separate page to show the details. As an example, if you click the Vitis Database Library button, you will find the page below.

5. You can see the information on the left of the page, including an overview, user guide, and benchmark results. Select any one to see the details.

If you are familiar with GitHub, you also can find the Vitis Libraries on GitHub.

6. Lastly if you need any help, visit the Xilinx forum to get further help, see the community forum.!

About Eddie Wu

Eddie Wu is a Sr. Product Marketing for Vitis SW Acceleration in AMD Software & AI marketing team. Eddie has been working in FPGA field for more than 8 years. He has a great experience of marketing and technical support in vertical industries, such as Automotive, ISM, Fintech, and Data center, as well as has expertise in AI, software acceleration and heterogeneous computing with AMD FPGA, GPUs, and ASIC.