第三章 FPGA をトライ

ここまで、FPGA と ASIC / ASSP との違いや FPGA の進化の様子、そして将来像を見てきました。FPGA の柔軟性、性能、機能など、ちょっと試してみたくなりますね。この第3章では、実際に FPGA を設計するとは「何」を「どう」すれば良いのか見てみましょう。ポイントは次の 4 点です。

- FPGA 開発フローを理解する

- FPGA 動作のしくみを知る

- 開発ソフトウェアで設計 (デザイン) する

- 開発ソフトウェアで設計し生成したファイルを FPGA にダウンロード

FPGA 開発フロー

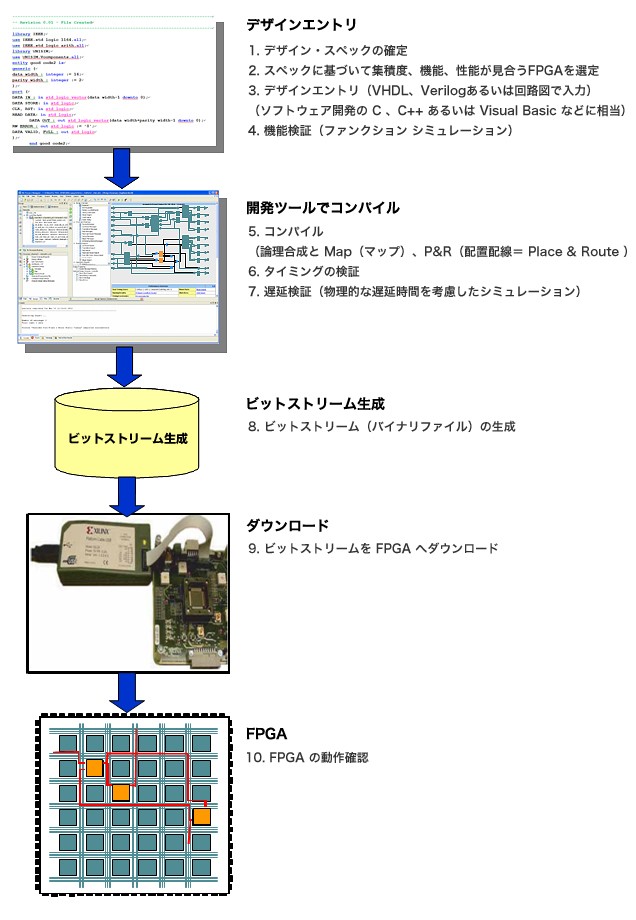

ここからは一般的な FPGA の設計フローを説明します。本講座では、最終目標が評価用の基板を用いてデザインを動かすことなので、基板を用いて試す時には、「ステップ 3 」以降の手順を踏んでいきます。

シミュレーションには「ステップ 4 」の機能検証と「ステップ 7 」の遅延検証があり、現実には重要ですが、今回はデモ デザインなので必要最小限の作業に注目します。

上記フローの「ステップ 8 」で得られるビットストリームは、ソフトウェア開発でのオブジェクトに相当します。

ビットストリームのデータが、FPGA 内部の制御ビットを ON したり OFF したりして、FPGA の内部構成をユーザー デザインと等価になるよう設定します。開発ソフトウェアが行う処理は、デザインに含まれる論理や演算処理の機能をターゲット FPGA のリソースに量的および遅延時間的にも最適に割り振ることといえます。

FPGA 動作のしくみ

電源投入直後の FPGA は、後述する各リソースがリセット状態で、各リソース間も配線接続されていないブランクの状態です。

FPGA は、ビット ストリームを保持するコンフィギュレーション メモリが SRAM をベースにしているので、電源立ち上げ時に外部記録メディアからビット ストリームをロードします。これは MPU や DSP プロセッサにおけるブートアップと同じです。

外部からビット ストリームをロードするということは、デザインを変更して別のビット ストリームを用意すれば、いつでも新しいデザインを試すことができるという利点をユーザーに提供します。

デザインに利用される FPGA リソースには大きく分類して次の 5 つのブロックがあり、アレイ状に並んでいます (FPGA モデル図 参照)。ブロックごとの基本構成は同じですが、デザインを反映させると異なるファンクションとして機能します。

- IOB (Input Output Block: 信号の入出力部)

- CLB (Configurable Logic Block) は LUT (Look Up Table) および FF (FlipFlop : 1 ビットのレジスタ) や高速キャリーチェインを含む

- 機能ブロック (DSPブロック、ブロック RAM、SERDES、埋め込みハードウェアなど)

- 配線要素とインターコネクト (配線接続ポイント)

- コンフィギュレーション メモリ (上記の 1 ~ 4 までのリソースを制御するビット ストリームの保持用 SRAM メモリで、ユーザーは意識しないで良い)

これらのブロックはアレイ状に並んでいるので、FPGA 誕生当初は、Logic Cell Array (LCA) と呼ばれていたこともありました。

開発ソフトウェアを使用したコンパイル作業により、デザインの論理やファンクションを FPGA 内のこれらのリソースに最適に割り振ります。

IOB は FPGA 外部とインターフェイスする部分です。デバイス ピン配置や電気的規格を開発ソフトウェアで指定し、コンパイル時にビットストリームに反映します。

CLB 内部のルックアップ テーブル (LUT) は、論理を扱う重要な要素です。任意の入力組み合わせに対して、どんな出力が必要かを「ルックアップ (参照)」するメモリで、デザイン要素を FPGA リソースにマップし各 LUT ごとに適切な参照値が計算され、ビットストリームに反映されます。 配線フェーズはナビゲーション システムの経路探索に似ています。ナビは、どの交差点で曲がって、どの道路を使うかを 表示してくれますが、P&R (配置配線) は曲がるポイントごとに (インターコネクト) に相当するビットストリーム中のビットが ON 状態になり。縦横に走る配線を接続して任意リソースから他の任意リソースへの接続が達成されます。また、DSP ブロック、ブロック RAM や SERDES など他の機能ブロックの動作もビットストリームの制御ビットによって制御されます。

このようにビットストリームが各リソースの動作とリソース間の接続を決定します。その結果、白紙状態の FPGA がユーザーの手もとで望む回路へと変貌するのです。

それでは実際に FPGA を開発する準備をしていきましょう。設計に必要なものは次の 3 つです。

- インターネットに接続可能な PC

- 開発ソフトウェア (デザインツールとも呼ばれます)

- FPGA が搭載された評価用基板

PC と評価用基板はご自身でご用意してください、開発ソフトウェアは、ISE Design Suite と呼ばれる製品で AMDの Web サイトからダウンロードできます。無償で利用できるのものとして、無期限に使用できる「ISE WebPACK 」と、評価版として 30 日間使用できる「ISE Design Suite 評価版」がありますが、ここでは、 ISE WebPACK を使用します。

開発ソフトウェア ISE WebPACK をダウンロード

ISE WebPACK をダウンロードするには、AMD Web サイトのアカウントが必要です。お持ちでない方は次の「AMD Web サイトのアカウント作成手順成」を参照して作成してください。すでにアカウントをお持ちの方は、「開発ソフトウェア ISE WebPAC のダウンロード手順」に進みましょう。

AMD Web サイトのアカウント作成手順

*アカウントの作成手順についてはこちらをご覧ください。

開発ソフトウェアをトライ

これまでの作業で、開発ソフトウェアのダウンロードが終了しました。次にセットアップして動かす準備をしましょう。

*セットアップの手順については、こちらをご覧ください。

参考資料:ISE Design Suite ソフトウェアマニュアルおよびヘルプ

評価用基板を準備する

次は、評価基板の選択ですが初心者用としては以下を考慮して準備しましょう。

- 最新の FPGA が搭載されている

- FPGA の動作確認には、 PC と評価基板以外の特殊な装置が不要である

- 付属するリファレンスデザインの設計が ISE WebPACK で設計できる

- ダウンロード ケーブルが付属されている

- 外部から FPGA の IO にアクセスでき、後で拡張できる

この FPGA 講座では特殊電子回路株式会社から販売されている、「Spartan 6 FPGA 評価ボード ( TKDN-SP6-16 ) 」を使用して、 ISE WebPACK でコンパイルして Spartan 6 FPGA を動かしてみます。詳細は第 3 章後半でお伝えします。

特殊電子回路(株)Spartan 6 FPGA 評価基板

サンプル デザインなどは特殊電子回路(株) のウェブサイトからダウンロード可能です。また、ユーザーがアクセスできる FPGA の IO が基板上に 64 本あるのでユニバーサル基板への搭載も可能です。