- デバイス

- FPGA および 3D IC

- 航空宇宙グレード Kintex UltraScale FPGA ファミリ

製品の特長

耐放射線 Kintex UltraScale の製品概要

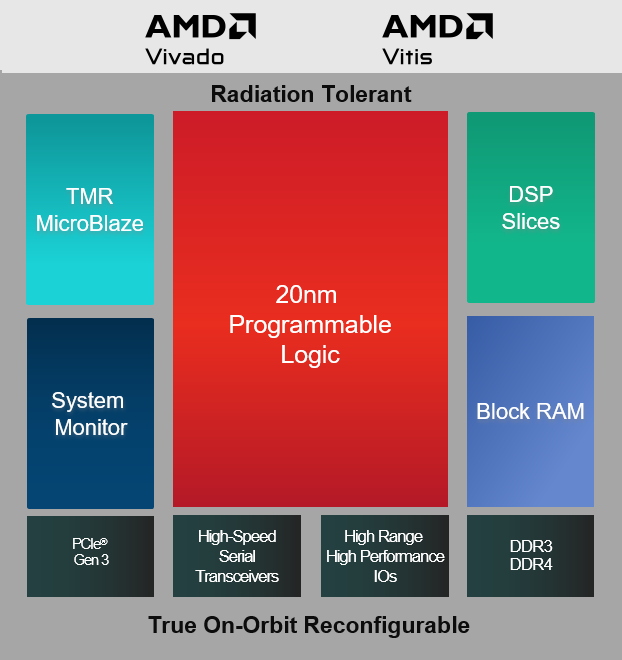

XQR Kintex™ UltraScale FPGA は、性能重視アプリケーション向けの高性能モノリシック FPGA です。DSP およびブロック RAM の対ロジック比率が高く、打ち上げ時や稼働時の振動に対応する航空宇宙グレードのパッケージに次世代トランシーバーを搭載しています。軌道上でもリコンフィギュレーション可能な次世代型の高密度 FPGA であるため、オンボード処理、デジタル ペイロード、リモート センシングなど多数のアプリケーションに最適です。

アプリケーション

RT Kintex UltraScale の主な利点:

- どこでも何度でもリコンフィギュレーション可能

- DSP 演算能力が 10 倍以上向上し、複雑なアルゴリズムや解析に対応できる

- 完全な放射線耐性

- 機械学習エコシステムにより、宇宙環境での高性能エッジ推論を実現できる

- Vivado および Vitis による設計サポート

- 現在プロトタイピングが可能!

製品一覧

製品一覧

| Virtex 4QV (90nm) XQRV4QV |

Virtex 5QV (65nm) XQRV5QV |

RT Kintex UltraScale (20nm) XQRKU060 |

|

|---|---|---|---|

| 耐放射線性 | Rad-Tolerant | Hard | Rad-Tolerant |

| メモリ (Mb) | 4.1 ~ 9.9 | 12.3 | 38 |

| システム ロジック セル (K) | 55 ~ 200 | 131 | 726 |

| CLB フリップ-フロップ (k) | 49.1 ~ 178.1 | 81.9 | 663 |

| CLB LUTs (k) | 49.1 ~ 178.1 | 81.9 | 331 |

| MGTs | なし | 18 (4.25Gbps) | 32 (12.5Gbps) |

| ユーザー I/O | 640 ~ 960 | 836 | 620 |

| DSP スライス | 32 ~ 192 | 320 | 2,760 |

| 放射線 (TID、SEL) | 300, >125 | 1,000, >125 | 100, >80 |

| 信頼性 (パッケージ、テスト) | CNA1509; V-Flow | CNA 1752; B-Flow & V-Flow | CNA 1509; B-Flow & Y-Flow |

資料

資料

デフォルト

デフォルト

タイトル

ドキュメント タイプ

日付

放射線

RT Kintex UltraScale の放射線特性

UltraScale™ アーキテクチャ ベースの航空宇宙グレード XQR デバイスは、独自の CCGA (Ceramic Column Grid Array) パッケージを採用することで、コマーシャ グレード シリコンより優れた性能を提供します。ザイリンクスの B、Y テスト フローなどの厳しい認定フローを通過 (QML 準拠) し、軍事防衛用の動作温度範囲に対応、シングル イベント効果 (SEE) の放射線テストを実施しています。RT Kintex UltraScale デバイスは、回路設計およびレイアウトに関して 40 を超えるザイリンクス独自の特許技術を導入して、SEU 断面積を減らしています。次の表に、RT Kintex UltraScale の放射線特性を示します。

| シンボル | 説明 | 最小 | 標準 | 最大 | 単位 |

|---|---|---|---|---|---|

| TID | 総電離線量 (GEO) | - | 100 | 120 | Krad (Si) |

| SEL | シングル イベント ラッチアップ (SEL) 耐性 | - | 80 | - | MeV-cm2/mg |

| SEUCRAM | コンフィギュレーション RAM におけるシングル イベント アップセット (GEO) | - | 1.0e-8 | - | アップセット/ビット/日 |

| SEUBRAM | ブロック RAM におけるシングル イベント アップセット (GEO) | - | 8.5e-9 | - | アップセット/ビット/日 |

| SEFICRAM | シングル イベント ファンクショナル インタラプトの軌道上アップセット頻度 - コンフィギュレーション RAM (GEO) | - | 4.5e-4 | - | アップセット/デバイス/日 |

次の表に、シングル イベント効果の種類と特長を示します。詳しい報告書については、宇宙グレード製品のラウンジ サイトをご覧ください。

| 放射線の種類 | 放射線の特長 | ターゲット/コメント |

|---|---|---|

| シングル イベント アップセット (SEU) | メモリ エレメントに格納された情報の破損 | メモリ、ロジック デバイスのラッチ。シングル ビット アップセット (SBU) やマルチビット アップセット (MBU) を含む。 |

| シングル イベント トランジェント (SET) | 特定の振幅と時間のインパルス応答 | アナログおよびミックスド シグナル回路。メモリ セルにラッチされている場合、SEU が生じる場合がある。 |

| シングル イベント ラッチアップ (SEL) | 大電流状態 | CMOS デバイス。ハード エラーが生じる可能性がある。 |

| シングル イベント ファンクショナル インタラプト (SEFI) | データパスが壊れて、正常な動作ができなくなる | ビルトインのステート マシン/制御セクション、またはシステムを含む複雑なデバイス。 |