アイソレーション デザイン フロー

安全性が重視されるアプリケーションにおけるフォルト トレランス

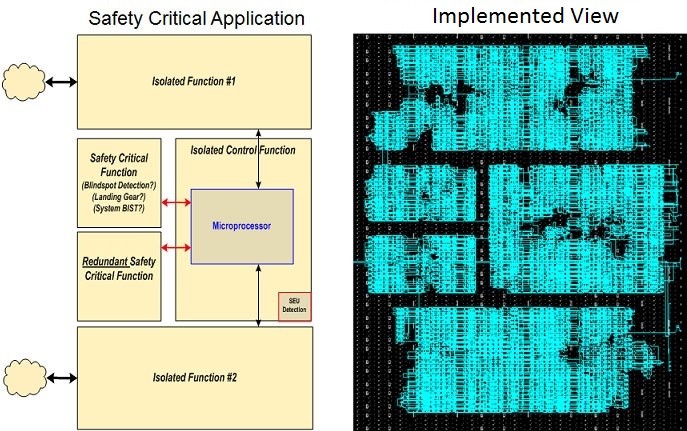

耐故障設計でシステムのエラー モードを制御するには、エラーの伝搬を確実に制御するインプリメンテーション方法が必要です。AMD の IDF (Isolation Design Flow) では、次に示すさまざまな方法でシングルチップでのフォルト耐性システムを構築して、FPGA モジュール レベルでエラーを抑制します。

- モジュールの冗長化

- ウォッチドッグ アラーム

- 安全性レベルで分離

- テスト ロジックを分離して安全に削除

政府の暗号化システム向けに開発された IDF は、航空電子機器、機能安全の電子機器、産業用ロボット、重要なインフラ、金融システムなど、そのほかにも高い保証、可用性、信頼性が求められるシステムにも用いることができます。IDF は、数ある信頼性技術のうちの一つであり、それらを適切に組み合わせて使用することによって、最高レベルの信頼性、性能、そしてコスト効果をもたらすことができます。

長年、政府レベルの暗号化システムに採用されてきた IDF は、IEC61508 (インダストリアル向け機能安全規格) に準拠した AMD ツール チェーンに欠かせない一部となります。 さらに、このフローは、ISO26262 仕様 (オートモーティブの機能安全) 要件を満たすのに役立っています。

デバイスおよびソフトウェア サポート

* 7S50 のみ

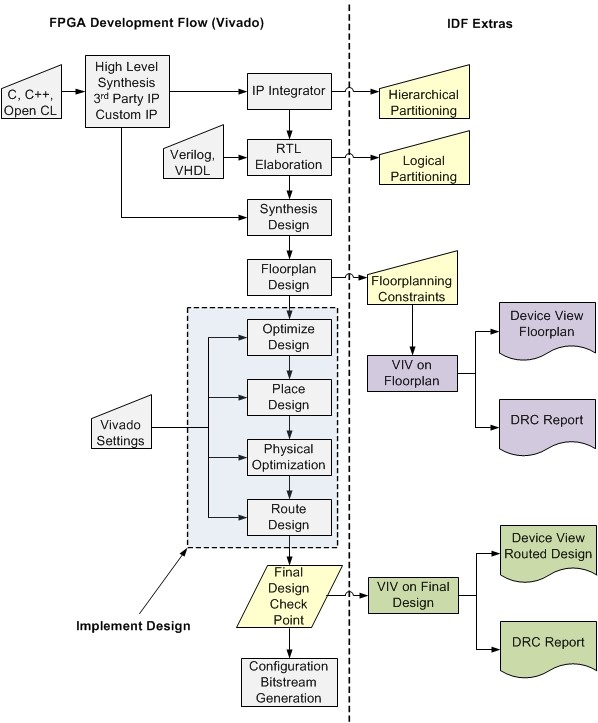

IDF の手順

資料およびリファレンス デザイン

Virtex 5 FPGA

- Virtex 5 用 SCC

XAPP1134:『Developing Secure Designs Using the Virtex 5 Family』では、FPGA で AMD の SCC テクノロジを実現する方法を説明しています。. - ISE 11.4 / 11.5 Design Suite を使用する SCC

XAPP1135:『Single Chip Crypto Lab Using PR/ISO Flow with the Virtex 5 Family』では、 FPGA 設計者用に ISE 11.4/11.5 Design Suite を使用して AMD の SCC テクノロジをインプリメントする方法を説明しています。 - ISE 12.1 / 12.4 Design Suite を使用する SCC

XAPP1105:『Single Chip Crypto Lab Using PR/ISO Flow with the Virtex 5 Family for ISE Design Suite 12.1』では、FPGA 設計者用に ISE 12.1/12.4 Design Suite を使用して AMD の SCC テクノロジをインプリメントする方法を説明しています。

Spartan 6 FPGA

- Spartan 6 のアイソレーション デザイン フロー (IDF)

XAPP1145:『Developing Secure Designs with the Spartan 6 Family Using the Isolation Design Flow』では、FPGA 設計者用に安全で確実なデザインを設計するためのガイドラインを示しています。 - XAPP1145 用リファレンス デザインおよびアプリケーション ノート

XAPP1145:『Developing Secure Designs with the Spartan 6 Family Using the Isolation Design Flow』では、FPGA 設計者用に安全で確実なデザインを設計するためのガイドラインを示しています。

7 シリーズ FPGA

ISE Design Suite

- 7 シリーズ用アイソレーション デザイン フロー (IDF) の規則/ガイドライン

XAPP1086:『Developing Secure and Reliable Single FPGA Designs with AMD 7 Series FPGAs Using the Isolation Design Flow』では、FPGA 設計者用に安全で確実なデザインを設計するためのガイドラインを示しています。 - Kintex 7: ISE 14.4 Design Suite を使用するアイソレーション デザイン フローのラボ

XAPP1085:『7 Series Isolation Design Flow Lab Using ISE Design Suite 14.4』では、FPGA 設計者用に実際にセキュアなデザインをインプリメントして、アイソレーション デザイン フローを実行する手順を示しています。

Vivado Design Suite

- 7 シリーズ用アイソレーション デザイン フロー (IDF) の規則/ガイドライン

XAPP1222:『Isolation Design Flow for AMD 7 Series FPGAs or Zynq 7000 AP SoCs (Vivado Tools)』では、FPGA 設計者用に安全で確実なデザインを設計するためのガイドラインを示しています。 - XAPP1256 用リファレンス デザインおよびアプリケーション ノート

XAPP1256:『Zynq 7000 AP SoC Isolation Design Flow Lab (Vivado Design Suite 2015.2)』では、FPGA 設計者用に安全で確実なデザインを設計するためのガイドラインを示しています。

UltraScale+ & Zynq UltraScale+

Vivado Design Suite

- アイソレーション デザイン フロー (IDF) の規則/ガイドライン

XAPP1335:『Zynq UltraScale+ 向けアイソレーション デザイン フロー』では、Vivado Design Suite でザイリンクスの IDF を使用して安全で確実なデザインを設計するためのガイドラインを示しています。- /content/dam/xilinx/support/documentation/application_notes/xapp1335-isolation-design-flow-mpsoc.pdfXAPP1335:『Zynq UltraScale+ 向けアイソレーション デザイン フロー』

- Vivado アイソレーション検証ユーザー ガイド

Vivado アイソレーション検証 (VIV) は、2018.3 以降の Vivado 設計環境に統合されており、UltraScale+ デバイス (Zynq UltraScale+ を含む) をサポートしています。この資料では、新しい Vivado アイソレーション検証 (VIV) を使用して FPGA/PL デザインのアイソレーション (隔離) を検証する方法を示しています。 - UG1291: 『Vivado アイソレーション検証ユーザー ガイド』

XAPP1336:『Isolation Design Example for Zynq UltraScale+』では、

1 チャネルの LPD (低電力ドメイン) と PL の TMR MicroBlaze を使用する、シングルチップで実現する汎用 2 チャネル システムの構築と実装について説明しています。

検証ツール

IDF 検証ツール (IVT および VIV) は、隔離された領域に分割された FPGA デザインがフェースセーフ デザインの厳しい要件を満たしているかを検証します。IVT および VIV は、FPGA デザイン プロセスの 2 つのステージで使用されます。初めは、初期の設計段階でフロアプランおよびピン割り当てに対して一連のデザイン ルール チェックを実行する際に使用します。そしてデザインが完成した後、これらのツールを使用して、デザインに有効なアイソレーション (隔離) が構築されているかを検証します。

ISE Design Suite 用 Isolation Verification Tool (IVT)

IVT は、ISE 環境の外で動作する実行ファイルですが、ISE 環境内に完全に組み込まれています。IVT は、動作しているデザインのアイソレーションを検証するのに必要な一連のデザイン ルール チェック (DRC) として機能します。そして、デザインをグラフィカルに表示し、テキストで詳細レポートを出力します。

- IVT.zip ファイルの内容は次のとおりです。

- IVT 実行ファイル

- リリース ノート、インストール ガイド

- ライセンス契約書

- 演習

IVT の現バージョンは、Virtex 5、Spartan 6、および 7 シリーズ ファミリ FPGA/SoC をサポートしています。

- IVT パッケージのダウンロード (ZIP)

Vivado Design Suite 用 Vivado Isolation Verifier (VIV)

VIV は、Vivado DRC エンジンに統合された Tcl ベース スクリプトです。基本的には、Vivado 内にロードされる一連の DRC であり、デザインのアイソレーションを検証するのに必要なすべてのチェックを実行します。ISE ベースの先行機能 IVT とは異なり、VIV はユーザー フレンドリーな Vivado GUI を利用する開発ツールに統合されていますが、独立した開発経路を維持しています。結果は、Vivado DRC エンジンによってテキスト出力されますが、Vivado DRC GUI ディスプレイにも組み込まれます。

- VIV.zip ファイルの内容は次のとおりです。

- VIV スクリプト

- リリース ノート、インストール ガイド

- ライセンス契約書

- 演習 (準備中)

VIV の現バージョンは、Vivado 2015.1 およびそれ以降で 7 シリーズ ファミリ FPGA/SoC をサポートしています。

- /content/dam/xilinx/publications/prod_mktg/idf/viv_v197.zipVIV パッケージのダウンロード (ZIP)

注記: Vivado アイソレーション検証は、2018.2 以降の Vivado Design Suite に含まれており、UltraScale+ デバイス (Zynq UltraScale+を含む) をサポートしています。詳細は、UG1291: 『Vivado アイソレーション検証ユーザー ガイド』を参照してください。