- デバイス

- FPGA および 3D IC

- Spartan UltraScale+ FPGA ファミリ

製品の特長

エッジ デバイスに多くの機器やセンサーが接続されるようになり、大量のデータを安全に処理できるセキュアなデバイスの需要が高まっています。AMD が新たに提供するコスト重視の高 I/O 数 Spartan™ UltraScale+™ FPGA ファミリは、低コストと省電力を実現しつつ、最先端のセキュリティ機能を備えることができるため、これらの問題を解決できます。

高 I/O 数、低消費電力、最先端のセキュリティ機能

- 28 nm 以下のプロセスで製造された FPGA の中で業界最高の I/O 対ロジック セル比1

- 16 nm FinFET プロセスは、前世代と比較した場合、総消費電力を最大 30% 削減を提供2

実績のあるデザイン ツールを使用してデザイン目標をすばやく達成

- 2012 年にリリースされた量産品質の高機能 Vivado™ Design Suite

- 単一ツールですべての FPGA ポートフォリオを対象にシミュレーションから検証までサポート

信頼できるサプライヤーの製品でデザインを構築

- FPGA 業界を約 40 年牽引し、数十億のデバイスを出荷

- 15 年以上の製品ライフサイクルを提供し、フィールド アップグレードでデザインを長寿命化

市場投入までの期間が短縮

その他の要素を妥協することなくコスト重視デザインを実現

AMD Spartan™ UltraScale+™ FPGA は、コスト、消費電力、機能性、サイズを最適なバランスですべて兼ね備えているため、ボード管理機能、I/O 拡張、IoT、ネットワーキングなど、さまざまなアプリケーションに対応できます。

エンベデッド システムに最適

I/O を多用するアプリケーションのパフォーマンス要件を満たす

豊富な I/O、低消費電力、最先端セキュリティ機能、高度な接続性をすべてコンパクトなパッケージで実現できます。AMD Spartan™ UltraScale+™ FPGA が選ばれる 5 つの理由について説明しています。

コスト重視 FPGA およびアダプティブ SoC 製品を活用してイノベーションを実現

エッジ デバイスでマシン ビジョンや AI などの最新技術を取り入れたイノベーションを実現するには、柔軟性、省電力、低コストを可能にする新しいアーキテクチャが必要です。この eBook では、アプリケーションに最適なアプローチを判断するために、FPGA、アダプティブ SoC、ASIC、およびその他の標準プロセッサの特長を説明しています。パフォーマンスや電力効率を犠牲にすることなく、複雑化するイノベーション要件に対応する方法を学び、今後の開発にお役立てください。

主な機能と利点

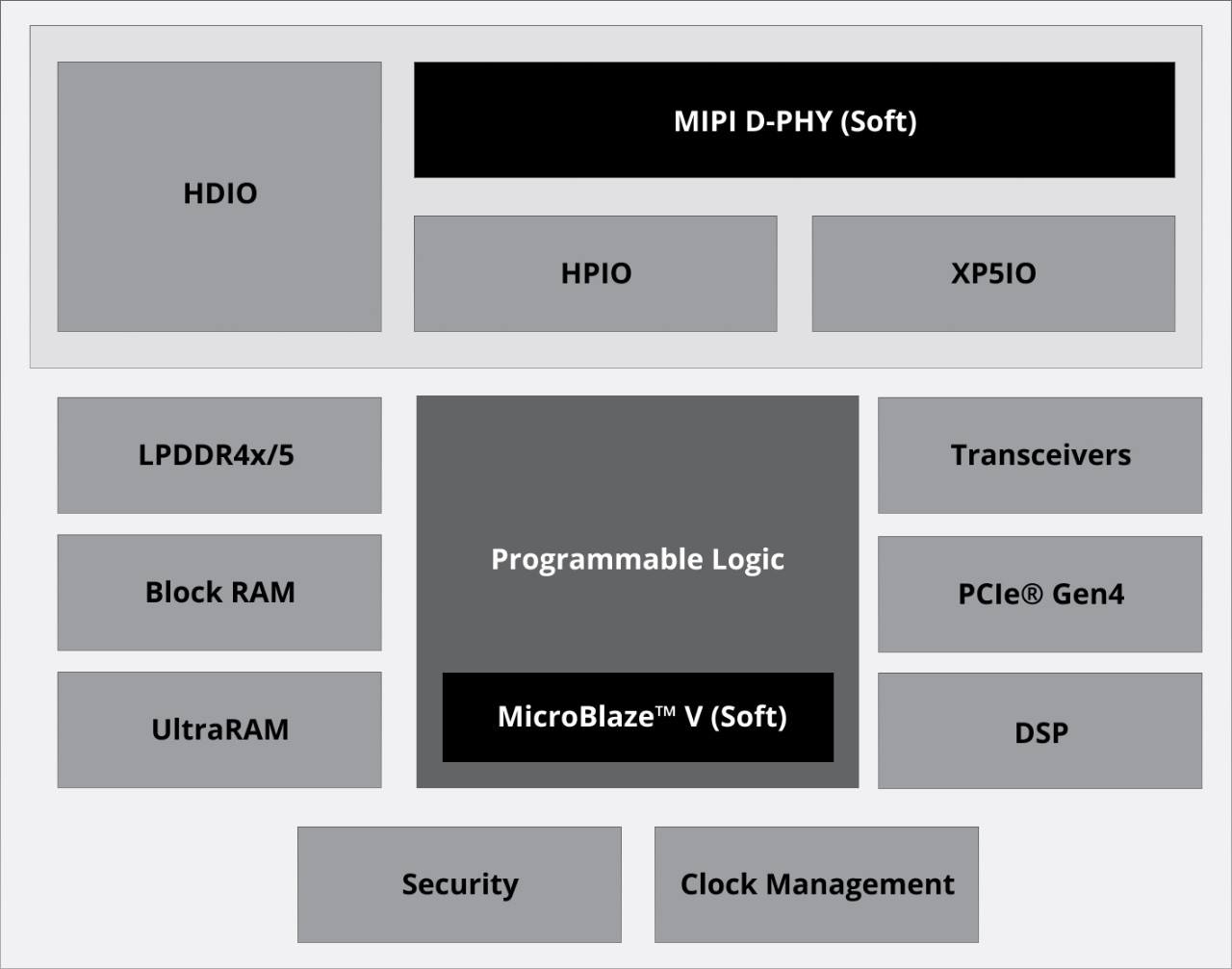

柔軟な I/O インターフェイス

AMD Spartan™ UltraScale+™ FPGA は、豊富な GPIO を提供し、レガシ プロトコルから最新のものまで、幅広い通信プロトコルをサポートしています。ネットワーキング、ビデオ、およびビジョン アプリケーションに対応した 16.3 Gb/s トランシーバーも搭載しています。また、これらのデバイスは、PCIe® Gen4、10GE Vision、CoaXPress 2.1、12G-SDI などの業界標準プロトコルに準拠しているため、市場投入までの時間を短縮できます。

低消費電力

AMD Spartan UltraScale+ FPGA は、16 nm アーキテクチャを採用しているため、前世代デバイス (28 nm) と比較した場合、総消費電力を最大 30% 削減3 できます。ハード実装された DDR と PCIe インターフェイス IP を統合したより高集積なデバイスは、前世代の 28 nm デバイスと比較した場合、最大 60% の電力効率向上4が可能となるため、システム全体のパフォーマンスを向上させることができます。

最先端のセキュリティ機能

AMD Spartan UltraScale+ FPGA は、NIST 承認のポスト量子暗号、PUF (Physically Unclonable Function) を使用する一意のデバイス ID、デバイス保護のための永久的な改ざん防止策、DPA によるサイドチャネル攻撃からの保護、進化する脅威に対応するための適応可能な AES-CGM 復号など、多層的なセキュリティを提供します。

ハード化されたメモリ コントローラー

一部のデバイスに搭載されている LPDDR4x/5 メモリ コントローラーなどのハード IP によって電力効率が向上し、システム全体のパフォーマンスを向上させることができます。ハード化されたメモリ コントローラーは、最大 4.2 Gb/s のメモリへ直接アクセスでき、高スループット処理を可能にします。また、解放された FPGA リソースを使用して、より高価値なデザインを構築できまます。

MIPI および LVDS パフォーマンス

最大 3.2 Gb/s の MIPI パフォーマンスを提供できる低コスト FPGA の Spartan UltraScale+ ファミリは、最先端のカメラ センサー キャプチャ/ディスプレイをサポートします。MIPI IP および関連するリファレンス デザイン ソリューションもこちらで提供しています。このファミリの LVDS パフォーマンスにより、SLVS-EC (CMOS イメージ センサー用) などのその他のプロトコルにも対応できます。

スケーラビリティ

TSMC 社の 16 nm 低消費電力 FinFET プロセスで構築された量産実績のある UltraScale™ アーキテクチャは、その他の 16 nm ファミリを含む幅広いポートフォリオに柔軟に対応する拡張性を備えています。開発者は、デザインへの投資を無駄にすることなく IP、ツール フロー、エコシステムを活用して、複数の製品ポートフォリオでプラットフォームを共有できます。

- 2024 年 2 月時点の AMD Spartan UltraScale+ FPGA と Efinix、Intel、Lattice、および Microchip の各製品のデータシートに基づいて、28 nm 以下の同等 FPGA の I/O 対ロジック セル比の比較を行いました。(SUS-11)

- AMD パフォーマンス ラボが 2024 年 1 月に実施した社内分析に基づいて予測したものです。この分析では、AMD Artix™ UltraScale+ AU7P FPGA のロジック セル数の差を考慮して合計消費電力 (スタティック + ダイナミック消費電力) を計算しています。Xilinx Power Estimator (XPE) ツールのバージョン 2023.1.2 を使用して、16 nm AMD Spartan™ UltraScale+™ SU35P FPGA と 28 nm AMD Artix 7 7A35T FPGA の消費電力を見積もりました。最終製品が市場にリリースされる際の実際の合計消費電力は、構成、使用状況、およびその他の要因によって異なります。(SUS-03)

- AMD パフォーマンス ラボが 2024 年 1 月に実施した社内分析に基づいて予測したものです。この分析では、AMD Artix™ UltraScale+ AU7P FPGA のロジック セル数の差を考慮して合計消費電力 (スタティック + ダイナミック消費電力) を計算しています。Xilinx Power Estimator (XPE) ツールのバージョン 2023.1.2 を使用して、16 nm AMD Spartan™ UltraScale+™ SU35P FPGA と 28 nm AMD Artix 7 7A35T FPGA の消費電力を見積もりました。最終製品が市場にリリースされる際の実際の合計消費電力は、構成、使用状況、およびその他の要因によって異なります。(SUS-03)

- AMD パフォーマンス ラボが 2024 年 1 月に実施した社内分析に基づいて予測したものです。この分析では、Artix UltraScale AU7P FPGA のロジック セル数を考慮した合計消費電力 (スタティック + ダイナミック消費電力) の計算を使用して、Spartan UltraScale+ SU200P FPGA と Artix 7 7A200T FPGA の合計消費電力を見積もりました。見積もりには、Xilinx Power Estimator (XPE) バージョン 2023.1.2 を使用しています。製品が市場にリリースされる際の実際の合計消費電力は、構成、使用状況、およびその他の要因によって異なります。(SUS-06)

アプリケーション

マシン ビジョン向けの柔軟な I/O

AMD Spartan™ UltraScale+™ FPGA は、産業および医療分野のマシン ビジョン システムに使用されるさまざまなセンサーや接続規格に対応するために、低レイテンシのインターフェイスと処理機能を提供します。また、この FPGA ファミリは、広範な通信プロトコルとの互換性を提供し、小規模デバイスや低電力デバイスでも利用可能です。

産業およびヘルスケア分野の多様なデータを収集

より高度なデータ収集技術が求められる中、AMD Spartan™ UltraScale+™ FPGA は柔軟な I/O とオンチップ メモリを提供し、エッジでの効率的な処理を可能にします。低消費電力、拡張可能なネットワーキング、高度なセキュリティ機能を実現できるため、センサー アグリゲーションや POC システムなどのアプリケーションに最適です。

低コストで実現できるデータセンター向けの I/O 拡張およびベースボード管理コントローラー (BMC)

サーバー メーカーのマザーボード設計がますます複雑化する中、Spartan™ UltraScale+™ FPGA は、電力管理や柔軟な I/O、一般的なボード管理コントローラーのリファレンス デザインを提供し、データセンター サーバーの I/O ニーズに迅速に応えることができます。Spartan UltraScale+ FPGA は、さまざまなサーバー ホスト プロセッサのマザーボードやボード管理コントローラー カードに応じて拡張できるデバイス ファミリです。

ビデオ キャプチャ カードのブロードキャスト効率向上

Spartan™ UltraScale+™ FPGA は高度なブロードキャスト技術を実現し、革新的な機能を提供します。PCIe® Gen4 とハード メモリ コントローラー LPDDR4x/5 を使用するこれらのカードは、高品質なベースバンド ビデオを効率的に伝送します。リアルタイム伝送と高効率処理が実現することで、ビデオ キャプチャ プロセスがシンプルになり、ブロードキャスト ワークフローが合理化します。

製品一覧

| SU10P | SU25P | SU35P | SU50P | SU55P | SU65P | SU100P | SU150P | SU200P | |

| システム ロジック セル (K) | 11 | 22 | 36 | 52 | 52 | 65 | 100 | 137 | 218 |

| DSP スライス | 24 | 36 | 48 | 96 | 96 | 144 | 144 | 384 | 384 |

| 総 RAM (Mb)1 | 1.77 | 1.84 | 1.93 | 2.91 | 2.91 | 4.31 | 5.89 | 11.65 | 26.79 |

| トランシーバー (16.375 Gb/s または 12.5 Gb/s) | 0 | 0 | 0 | 0 | 0 | 4 | 4 | 8 | 8 |

| PCI Express® | 0 | 0 | 0 | 0 | 0 | 1x Gen4x4 | 1x Gen4x4 | 1x Gen4x8 または 2x Gen4x4 | 1x Gen4x8 または 2x Gen4x4 |

| 最大 I/O ピン数 | 304 | 304 | 304 | 388 | 352 | 478 | 478 | 572 | 572 |

* 総 RAM = 最大分散 RAM + 総ブロック RAM

資料

開発を始めるにあたって

アーリー アクセス プログラム

2025 年上半期に Spartan™ UltraScale+™ FPGA シリコン サンプルを提供します。Vivado™ design suite で Spartan UltraScale+ ファミリにアーリー アクセスまたはサンプル シリコンの使用を希望される場合は、AMD の営業担当者にお問い合わせください。

ビデオ チュートリアル

チュートリアルでは、AMD FPGA のコンパイル、変更、構築、およびデバッグ方法を手順を追って説明します。

トレーニング コース

AMD の FPGA およびデザイン トレーニングでは、今すぐ設計をスタートするために必要な知識が身につくハンズオン コースを提供しています。各コースの概要については、こちらをご覧ください。

主なリソース

デザイン アドバイザリで既知の問題から解決法を見つけることができます。