- アプリケーション

- エミュレーションおよびプロトタイピング

- ASIC のエミュレーション

ASIC のエミュレーション

ASIC および SoC エミュレーション向けの優れた性能と統合性

ハードウェア エミュレーションは、開発過程にあるシステムのデバッグと機能検証をサポートする一連のプロセスです。包括的なハードウェア機能検証は、開発コストと市場投入までの時間を短縮するために重要です。エミュレーションは、デザインの変更に迅速に対応してターンアラウンド タイムを短縮します。また、デザインのアクセシビリティとデバッグの可視性も向上するため、ASIC 設計者はテープアウト前に潜在的なハードウェア エラーを見つけることができます。ソフトウェアの複雑化に伴い、コスト増加が問題視される現在、リスクを低減してシステム開発を加速するためには初期段階でのハードウェア検証が不可欠です。

AMD は、エミュレーションによってシステム性能を最大限に引き出し、迅速かつ予測可能な設計サイクルを実現するためにの包括的な設計手法と設計開発プラットフォームを提供しています。 Vivado™ Design Suite は、エミュレーション レベルのシステム設計をサポートする最先端開発環境で、AMD が提供する 3 世代目となるエミュレーション クラスのツール、IP、および設計フローです。

AMD エミュレーション プラットフォームの利点

- 大規模なデザインでも複数チップ分割が不要

- 高速配置配線により、大規模な ASIC/ASSP デザインの開発リスクを緩和

- システムレベルの消費電力削減

- ASIC のようなクロッキング/配線アーキテクチャにより、デバイス使用率が向上

- 高度なデバッグと迅速なエミュレーションが可能

主なアライアンス メンバー

AMD は、Virtex™ 7 2000T FPGA や Virtex UltraScale™ VU440 FPGA を通して、大容量 FPGA 市場を牽引してきました。16nm Virtex UltraScale+™ ファミリに世界最大容量を誇るVirtex UltraScale+ VU19P FPGA が追加されたことで、

Virtex 7 2000T

ASIC エミュレーション向け

- ロジック セル数: 200 万、トランジスタ数: 68 億

- 12.5Gb/s シリアル トランシーバー、36 個

- 46Mb ブロック RAM

- I/O 数: 1,200

- 第 1 世代目 SSI 技術

Virtex UltraScale VU440

20nm でデバイス集積度は 4 倍

- ロジック セル数: 550 万、トランジスタ数: 200 億

- 16.3Gb/s シリアル トランシーバー、48 個

- 89Mb ブロック RAM

- I/O 数: 1,456

- 第 2 世代目 SSI 技術

Virtex UltraScale+ VU19P

業界最大容量の FPGA

- ロジック セル数: 550 万、トランジスタ数: 200 億

- 28Gb/s シリアル トランシーバー、80 個

- 94.5Mb ブロック RAM

- I/O 数: 2,072

- 第 3 世代目 SSI 技術

資料

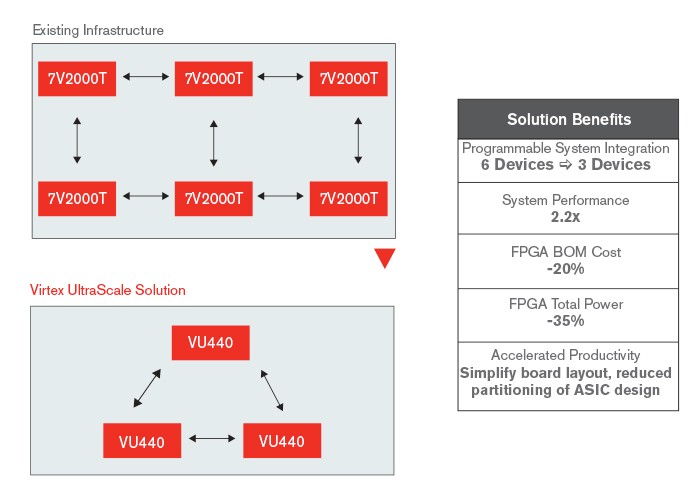

AMD の UltraScale™ アーキテクチャを使用することによって、ASIC プロトタイピング/エミュレーションの性能および統合性を飛躍的に向上させることができます。Virtex™ UltraScale デバイスは、高いロジック容量、90% 以上のデバイス使用率、ASIC のようなクロッキング分配、強化された配線、ピンの多重化を行うための高速トランシーバーを利用できるため、デザインの分割数を減らしてシンプルなレイアウトを可能にします。この画期的なアーキテクチャは、Vivado™ Design Suite で設計することで、最先端 ASIC および SoC プラットフォームのニーズに対応できる理想的なソリューションとなります。

ソリューションのまとめと利点

- デバイス容量が非常に高いため、デザインの分割数が減少し、ボード レイアウトがシンプルになる

- 強化された配線と Vivado Design Suite で相互に最適化することによって、90% 以上のデバイス使用率を達成できる

- ASIC のようなクロッキング分配により、複雑な ASIC および SoC のクロック ツリーを効果的にマップできる

- 高速トランシーバーが FPGA 間で効果的なピンの多重化接続を可能にし、次世代システムに求められる I/O インターフェイス要件をサポートする

UltraScale アーキテクチャの利点

- 広い I/O 帯域幅

- 1Tbps 以上のチップ間帯域幅が可能

- 低レイテンシ トランシーバーによるチップ間の相互接続

- 大容量データ フローおよび配線

- ASIC 特有の高性能なワイド バスをサポート

- ASIC 特有の高性能なワイド バスをサポート

- ASIC のようなクロッキング

- 複雑な SoC プロトタイピング向けに高い柔軟性を提供

- 複雑な SoC プロトタイピング向けに高い柔軟性を提供

- システム性能

- デバイスあたりの性能は 15~30% 向上

- 分割数の減少により、3 倍向上

- 電力管理

- 最大 35% システム電力低減