AMD UltraScale+ コスト重視デバイス

I/O、消費電力、セキュリティ機能を重視

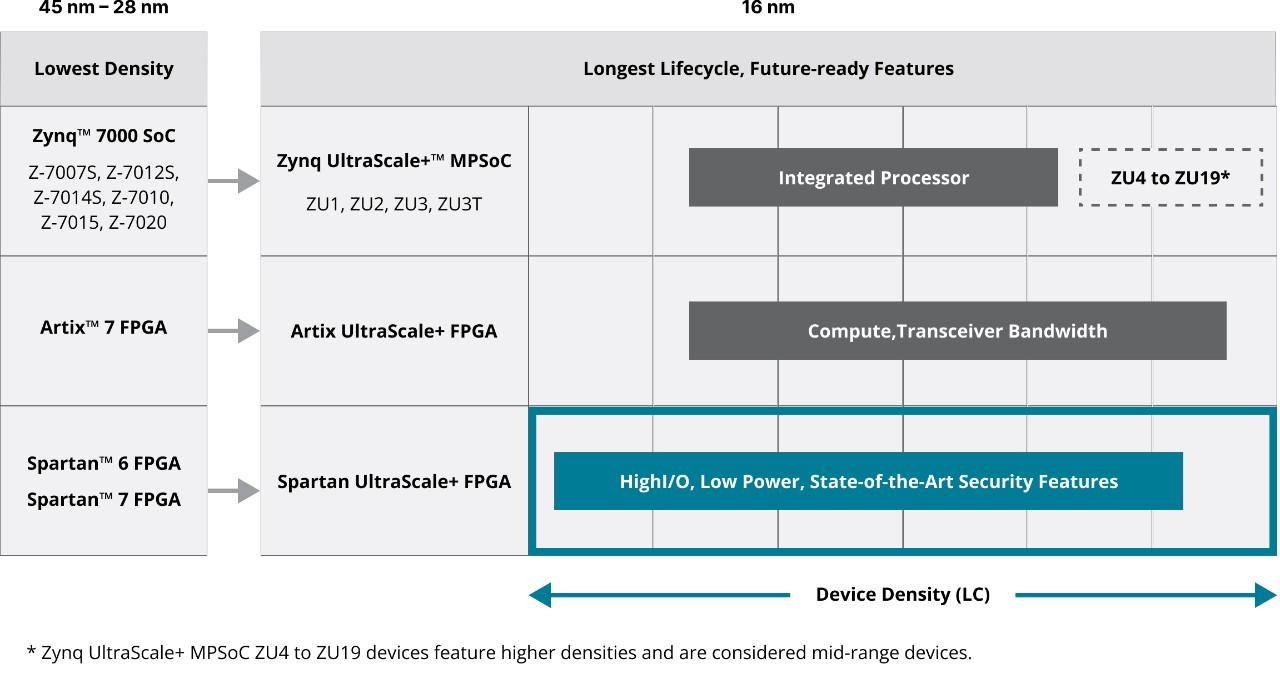

AMD Spartan™ UltraScale+™ FPGA は、豊富な I/O、低消費電力、最先端セキュリティ機能を必要とするコスト重視アプリケーション向けに最適化されています。11k ~ 218k のロジック セルを備え、最大 572 の I/O に対応している Spartan UltraScale+ FPGA は、I/O の拡張、ボード管理、さらにはセンサー データの処理および制御に至るまで幅広いアプリケーションで優れたパフォーマンスを発揮します。

トランシーバーと信号処理に最適化

Artix™ UltraScale+™ FPGA は、高スループットで優れた DSP 演算能力をもたらす、最大総帯域幅 192 Gb を実現します。主に、エンベデッド システムや映像処理、無線通信、先進運転支援システム (ADAS)、インダストリアル IoT (IIoT) などのアプリケーションに最適です。

エンベデッド処理に最適化

Zynq™ UltraScale+™ MPSoC は、Arm® プロセッサ サブシステムとプログラマブル ロジックの UltraScale+™ アーキテクチャを 1 つのデバイスに統合しています。主に、高速ネットワーキング、ハイパフォーマンス コンピューティング、5G 無線、自動車、航空電子機器、産業制御システムなどのアプリケーションに最適です。

AMD 7 シリーズのコスト重視デバイス

低集積の最小パッケージ

AMD Spartan™ 7 FPGA ファミリは、低集積のコンパクトなソリューションとして最適な選択肢を提供します。6K ロジック セルの少ないリソースでも充実した機能を構築することが可能です。Spartan 7 FPGA は、極めて小さい 0.5 mm ピッチの 8x8 mm パッケージで 100 本の I/O を使用できます。その他、0.8 mm および 1.0 mm のピッチ オプションもあります。主に、Any-to-Any コネクティビティ、プロトコル変換、ブリッジング、センサー フュージョン、エンベデッド ビジョンなどのアプリケーションに最適です。

トランシーバーと DSP 機能を搭載した低集積デバイス

AMD Artix™ 7 FPGA ファミリは、最大 16 個の 6.6 Gb/s トランシーバーを搭載し、高効率でセキュアなデータ通信を可能にします。DDR3 をサポートしているため、より高速なデータ帯域幅を実現できます。また、DSP 機能により、高スループットで信号処理が可能です。主に、ソフトウェア無線やローエンド ワイヤレス バックホールなど、適度な信号処理を必要とするアプリケーションに最適です。

ハード プロセッサを搭載した低集積デバイス

AMD Zynq™ 7000 SoC ファミリは、ハード化されたプロセッサ、エンベデッド メモリ コントローラー、および 7 シリーズのプログラマブル ロジックを備えた最小デバイスを提供します。23K ロジック セルで最大動作周波数 766 MHz のシングル コア Arm® Cortex®-A9 プロセッサを搭載したデバイス、または 28K ロジックセルで最大動作周波数 866 MHz のデュアル コア Arm Cortex-A9 プロセッサを搭載したデバイスを選択できます。Zynq 7000 SoC は、システム管理や柔軟性のあるコンピューティング アプリケーションの開発に最適です。

コスト重視 FPGA およびアダプティブ SoC 製品を活用してイノベーションを実現

エッジ デバイスでマシン ビジョンや AI などの最新技術を取り入れたイノベーションを実現するには、柔軟性、省電力、低コストを可能にする新しいアーキテクチャが必要です。この eBook では、アプリケーションに最適なアプローチを判断するために、FPGA、アダプティブ SoC、ASIC、およびその他の標準プロセッサの特長を説明しています。パフォーマンスや電力効率を犠牲にすることなく、複雑化するイノベーション要件に対応する方法を学び、今後の開発にお役立てください。

妥協なき設計が可能に

AMD は、製品ライフサイクルの延長を検討し、すべての 7 シリーズ デバイスのサポート期間を少なくとも 2035 年まで延長することを正式に発表します。対象デバイスは、Spartan™ 7、Artix™ 7、Kintex™ 7、Virtex™ 7 FPGA、および Zynq™ 7000 SoC のすべてのスピード/温度グレードが含まれます。

目的に合った製品ファミリを判断

パフォーマンスと柔軟性に関するさまざまな分野の問題を解決

FPGA コスト重視デバイス

| Spartan™ 6 FPGA | Spartan 7 FPGA | Artix™ 7 FPGA | Artix UltraScale+™ FPGA | Spartan UltraScale+ FPGA | |

| ロジック セル/システム ロジック セル (K) | 147 | 102 | 215 | 308 | 218 |

| 総 RAM (Mb)1 | 6.2 | 5.4 | 16.0 | 15.2 | 26.79 |

| DSP スライス | 180 | 160 | 740 | 1200 | 384 |

| トランシーバー数 @ スピード (Gb/s) | 8 @ 3.2 | - | 16 @ 6.6 | 12 @ 16.375 | 8 @ 16.375 |

| DDR インターフェイス @ スピード (Mb/s) | DDR3 @ 800 (ハード MC) |

DDR3 @ 800 (ソフト MC) |

DDR3 @ 1,066 (ソフト MC) |

DDR4 @ 2,400 (ソフト MC) |

LPDDR4x/5 @ 4,266 (ハード MC) および DDR4 @ 2,400 (ソフト MC) |

| PCI Express® インターフェイス | Gen1 x1 | - | Gen 2x4 | Gen4 x4 | Gen4 x8 |

| I/O ピン | 576 | 400 | 500 | 304 | 572 |

| プロセッシング システム | |||||

| アプリケーション プロセッサ ユニット | MicroBlaze™ | MicroBlaze V | MicroBlaze V | MicroBlaze V | MicroBlaze V |

| リアルタイム プロセッシング ユニット | MicroBlaze | MicroBlaze V | MicroBlaze V | MicroBlaze V | MicroBlaze V |

| グラフィックス プロセッシング ユニット | サードパーティ IP | サードパーティ IP | サードパーティ IP | サードパーティ IP | サードパーティ IP |

| メモリ インターフェイス | DDR3 @ 800 (ハード MC) |

DDR3 @ 800 (ソフト MC) |

DDR3 @ 1,066 (ソフト MC) |

DDR4 @ 2,400 (ソフト MC) |

LPDDR4x/5 @ 4,266 (ハード MC) および DDR4 @ 2,400 (ソフト MC) |

SoC コスト重視デバイス

| Zynq™ 7000 SoC Z-7007S、Z-7012S、Z-7014S、Z-7010、Z-7015、Z-70202 |

Zynq UltraScale+™ MPSoC ZU1、ZU2、ZU3、ZU3T2 |

|

| ロジック セル/システム ロジック セル (K) | 85 | 157 |

| 総 RAM (Mb)* | 5.9 | 21.2 |

| DSP スライス | 220 | 576 |

| トランシーバー数 @ スピード (Gb/s) | 4 @ 6.25 | 4 @ 6.0 および 8 @ 12.5 |

| DDR インターフェイス @ スピード (Mb/s) | DDR3 @ 1,066 (ハード MC) |

DDR4 @ 2,666 (ハード MC) |

| PCI Express® インターフェイス | Gen 2x4 | Gen3 x8 |

| I/O ピン | 328 | 466 |

| プロセッシング システム | ||

| アプリケーション プロセッサ ユニット | シングル/デュアル コア Arm® Cortex®-A9 | デュアル/クワッド コア Arm Cortex-A53 |

| リアルタイム プロセッシング ユニット | MicroBlaze および MicroBlaze V | デュアル コア Arm Cortex-R5F |

| グラフィックス プロセッシング ユニット | サードパーティ IP | Mali™-400MP2 |

| メモリ インターフェイス | DDR3、DDR3L、DDR2、LPDDR2、2x Quad-SPI、NAND、NOR | x16: DDR4 w/o ECC; x32/x64: DDR4、LPDDR4、DDR3、DDR3L、LPDDR3 w/ ECC 2x Quad-SPI、NAND |

- * 総 RAM = 最大分散 RAM + 総ブロック RAM + UltraRAM

- より大規模なデバイス (Z-7100 および ZU19 まで) も提供

デザインに最適なファミリを判断する際は製品セレクション ガイドを確認してください。

主なリソース

今すぐ評価

開発キットを使用して、今すぐデザインを始めましょう。